(12)

## EP 2 407 976 A8 (11)

## **CORRECTED EUROPEAN PATENT APPLICATION**

(15) Correction information:

Corrected version no 1 (W1 A3)

Corrections, see

INID code(s) 71 **Bibliography**

(48) Corrigendum issued on:

18.04.2012 Bulletin 2012/16

(88) Date of publication A3:

07.03.2012 Bulletin 2012/10

(43) Date of publication A2:

18.01.2012 Bulletin 2012/03

(21) Application number: 11173262.4

(22) Date of filing: 08.07.2011

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

**Designated Extension States:**

**BA ME**

(30) Priority: 13.07.2010 US 835588

(71) Applicant: NXP B.V.

5656 AG Eindhoven (NL)

(51) Int Cl.:

G11C 13/00 (2006.01) G11C 7/24 (2006.01)

G11C 7/04 (2006.01)

G11C 16/22 (2006.01)

(72) Inventors:

· Li, Yuan

Redhill, Surrey RH1 1DL (GB)

· Guogiao, Tao

Redhill, Surrey RH1 1DL (GB)

(74) Representative: Hardingham, Christopher Mark

NXP B.V.

IP & L

**Betchworth House**

57-65 Station Road

Redhill

Surrey RH1 1DL (GB)

## (54)Non-volatile re-programmable memory device

(57)A memory device including a non-volatile re-programmable memory cell is provided. In connection with various example embodiments, the memory cell is a single resistor located between a first and second node. The resistor stores different resistance states corresponding to different resistance values set by SiCr-facilitated migration. The SiCr-facilitated migration occurs in response to energy presented between the first and second nodes. The application of a signal to a first node of the memory

cell resistor forces the migration of elements along the memory cell resistor to set the resistance value of the memory cell resistor. The application of a second signal of approximately equal strength to the second node reverses the change and resistance and returns the memory cell to the previous resistance level. In some implementations the resistor is made of SiCr.

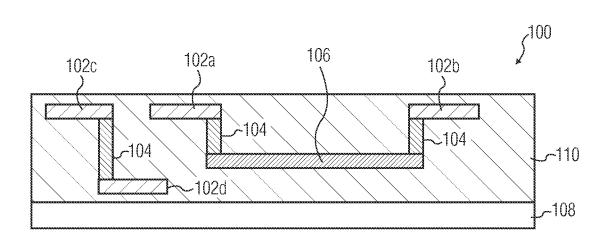

FIG. 1B