# (11) **EP 2 592 756 A1**

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

15.05.2013 Bulletin 2013/20

(51) Int Cl.: H03M 3/02 (2006.01)

(21) Application number: 11189057.0

(22) Date of filing: 14.11.2011

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

**Designated Extension States:**

**BA ME**

(71) Applicant: Telefonaktiebolaget L M Ericsson AB (Publ)

164 83 Stockholm (SE)

(72) Inventors:

Anderson, Martin SE-22471 Lund (SE)

Sundström, Lars SE-224 74 Lund (SE)

(74) Representative: Andersson, Karl Ola et al

Ericsson AB

**Patent Unit Mobile Platforms**

Nya Vattentornet 221 83 Lund (SE)

## (54) Analog-to-digital converter

(57) A continuous-time  $\Sigma\Delta$ -ADC (1) is disclosed. It comprises a sampled quantizer (5) arranged to generate samples y(n) of a digital output signal of the  $\Delta\Sigma$ -ADC (1) at sample instants nT, where n is an integer sequence index and T is a sampling period, based on an analog input signal to the quantizer (5). Furthermore, the  $\Delta\Sigma$ -ADC (1) comprises one or more DACs (10a-b), each arranged to generate an analog feedback signal based on the samples of the digital output signal generated by the sampled quantizer (5). Moreover, the  $\Delta\Sigma$ -ADC (1) comprises one or more DACs (1) comprises of the digital output signal generated by the sampled quantizer (5). Moreover, the  $\Delta\Sigma$ -ADC (1) comprises the comprise of the digital output signal generated by the sampled quantizer (5).

prises a continuous-time analog network (20) arranged to generate the analog input signal to the quantizer (5) based on the feedback signal(s) from the one or more DACs (10a-b) and an analog input signal to the  $\Delta\Sigma$ -ADC (1). At least one DAC (10b) of the one or more DACs (10b) comprises two switched-capacitor DACs (40, 50) arranged to operate on the same input but with a mutual delay in time. A corresponding radio receiver circuit (100), a corresponding integrated circuit (200), and a corresponding radio communication apparatus (300, 400) are also disclosed.

FIG. 8

35

40

45

1

### Description

#### **Technical field**

**[0001]** The present invention relates to the field of analog-to-digital converters, in particular to the field of continuous-time delta-sigma analog-to-digital converters.

#### **Background**

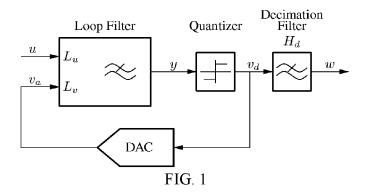

[0002] Fig. 1 shows a general depiction of a continuous-time delta sigma ( $\Delta\Sigma$ ) analog-to-digital converter (ADC). The conventional  $\Delta\Sigma$  ADC converts an analog input signal  $\boldsymbol{u}$  into a highfrequency serial bit sequence having a low resolution, often only 1 bit (0 or 1), here called  $\boldsymbol{v_d}$ . This coarsely quantized bit sequence  $\boldsymbol{V_d}$  is converted into a highly accurate digital signal  $\boldsymbol{w}$  with a lower sampling rate through subsequent digital low pass decimation filters,  $\boldsymbol{H_d}$ . This is possible since the energy of the quantization noise is distributed at frequencies outside the frequency band of interest.

[0003] The  $\Delta\Sigma$  ADC of Fig 1 comprises a coarse quantizer, a loop filter and a feedback DAC. The coarse quantizer comprises one or more comparators clocked at a clock rate a lot higher than the bandwidth of the analog input signal u. The digital-to-analog converter (DAC) provided in the feedback branch generates from the digital output signal of the quantizer,  $v_d$ , a sequence of quantized analog signals here called the feedback signal, va. The loop filter processes both the analog input signal **u** and the quantization errors,  $\varepsilon$ , injected into the system in the coarse quantizer. By selecting the transfer function of the loop filter,  $L_{ii}$  and  $L_{v}$ , in such a way that, in the band of interest, the transfer function for the quantization errors  $\boldsymbol{\epsilon}$  is many times smaller than the transfer function for the analog input signal u, the signal-to-quantization "noise" ratio (SQNR) in that particular frequency band can be made large.

[0004] Thus, by selecting  $L_{\nu}$  properly, the noise transfer function (NTF) can be made high-pass or band-pass:

$$NTF = \frac{v_d}{\varepsilon} = \frac{1}{1 - L_v} \tag{1}$$

whereas the signal transfer function (STF) is a function of both  $\mathbf{L}_{\mathbf{u}}$  and  $\mathbf{L}_{\mathbf{v}}$ :

$$STF = \frac{v_d}{u} = \frac{L_u}{1 - L_u} \tag{2}$$

**[0005]** The loop filter can be implemented using active discrete time (DT) filters or active continuous time (CT) filters or even passive loop filters. If the NTF is selected

having zeros at low frequencies (DC), the loop filter will be built up of integrators, which can be implemented using negative feedback amplifiers. The reason for using CT filters above their DT counterparts is that they provide anti-alias filtering, have no front-end sampling, no kT/C noise and theoretical speed advantages which lead to a lower power consumption at a given analog signal bandwidth.

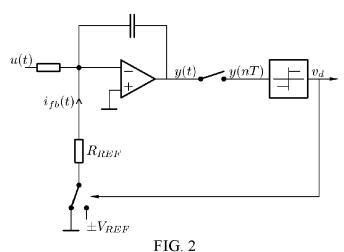

[0006] Prior art in the implementation of the feedback DAC in CT modulators is to use a switched current (SI), or a switched capacitor (SC) to inject a well defined amount of charge to the summing node of the integrator. [0007] Fig. 2 shows a possible implementation of a 1-bit SI feedback according to prior art. A logically high data bit of the digital output signal (HIGH), v<sub>d</sub>, is applied as a corresponding reference voltage (for example  $V_{REF+}$ = 1 volt) to the inverting signal input of the amplifier, and a logically low signal (LOW) of the digital output signal is fed back as a second reference voltage (for example  $V_{REF}$  = -1 volt). The reference voltage is converted to a reference current through the resistor between the V<sub>REF</sub> node and the virtual ground (summing node) at the amplifier input.

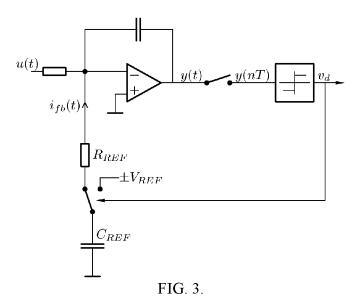

[0008] In the SC feedback according to prior art (e.g. Fig. 3) a capacitor C<sub>RFF</sub>, is switched using a set of switches between the reference voltage V<sub>REF</sub> and to the inverting input of the operational amplifier. A reference resistance R<sub>REF</sub> might be connected on either side of the capacitor to control the time constant of the switching RC circuit. The reference capacitor is charged with the reference voltage (V<sub>REF+</sub> or V<sub>REF-</sub>) corresponding to the digital output bit in a first clock phase, and then transfers a well defined charge packet  $Q = C*V_{REF}$  to the integrator in a second clock phase when the switch circuit switches the reference capacitor C<sub>REF</sub> to the inverting input of the amplifier. The discharge of the capacitor CREF will give an exponentially falling current pulse  $\tau = I_0 * \exp(-t/\tau)$ where  $\tau = R_{REF} * C_{REF}$  is the time constant. Because of the exponentially decreasing pulse shape the charge Q displaced in one clock cycle T varies only slightly when clock jitter occurs, and thus this technique is less sensitive to clock jitter than the  $\Delta\Sigma$  ADCs illustrated in Fig. 2.

#### Summary

**[0009]** In accordance with embodiments of the present invention, the inventors have provided for the design of continuous-time  $\Delta\Sigma$  ADCs using SC feeback with relatively low current consumption.

[0010] According to a first aspect, there is provided a continuous-time  $\Delta\Sigma$ -ADC. The continuous-time  $\Delta\Sigma$ -ADC comprises a sampled quantizer arranged to generate samples y(n) of a digital output signal of the  $\Sigma\Delta$ -ADC at sample instants nT, where n is an integer sequence index and T is a sampling period, based on an analog input signal to the quantizer. Furthermore, the continuous-time  $\Delta\Sigma$ -ADC comprises one or more digital-to-analog converters (DACs), each arranged to generate an analog

30

35

40

45

feedback signal based on the samples of the digital output signal generated by the sampled quantizer. Moreover, the continuous-time  $\Delta\Sigma\text{-ADC}$  comprises a continuous-time analog network arranged to generate the analog input signal to the quantizer based on the feedback signal(s) from the one or more DACs and an analog input signal to the  $\Delta\Sigma\text{-ADC}$ . At least one DAC of the one or more DACs comprises two switched-capacitor DACs (as subcomponents) arranged to operate on the same input but with a mutual delay in time.

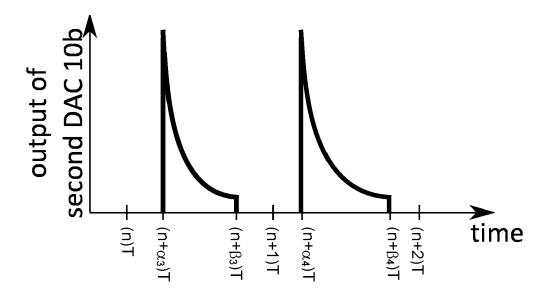

**[0011]** Each of the two switched capacitor DACs may be arranged to, for each n, be charged with a charge proportional to the sample y(n) of the digital output signal. Furthermore, a first of the switched capacitor DACs may be arranged to (again, for each n) be switched in to the continuous-time analog network for transfer of its charge to the continuous-time analog network in a time interval that lasts between the time instants  $(n+\alpha 3)T$  and  $(n+\beta 3)T$ . Moreover, a second of the switched capacitor DACs may be arranged to (again, for each n) be switched in to the continuous-time analog network for transfer of its charge to the continuous-time analog network in a time interval that lasts between the time instants  $(n+\alpha 4)T$  and  $(n+\beta 4)T$ . The following relations may apply:  $\beta 4 > 1$ ,  $0 < \alpha 3 < \alpha 4 < \beta 4 < 2$  and  $\alpha 3 < \beta 3 \le 1$ .

**[0012]** According to some embodiments,  $\alpha 4 \leq \beta 3$ .

**[0013]** According to some embodiments,  $\alpha 4 = \beta 3$ . For example, in some embodiments,  $\alpha 4 = \beta 3 = 1$ ,  $\alpha 3 = 0.5$ , and  $\beta 4 = 1.5$ .

[0014] Said one or more DACs may comprises one or more additional DACs, in addition to the at least one DAC comprising the two switched capacitor DACs. In other words, said one or more DACs may actually be two or more DACs. At least a first DAC of the one or more additional DACs may be adapted to generate a pulsed feedback signal that, for each n, comprises a pulse, the magnitude of which is proportional to the sample of the digital output signal at sample instant nT and which lasts between the time instants  $(n+\alpha 1)T$  and  $(n+\beta 1)T$ , wherein 0  $< \alpha 1 < \beta 1 < 1$ . Said first DAC may be located in a first feedback loop and the DAC comprising the two switchedcapacitor DACs may located in a second feedback loop, which may be an outer feedback loop relative to the first feedback loop (i.e. a loop that has a higher order of integration than the first feedback loop).

[0015] The continuous-time analog network may comprise a plurality of cascaded continuous-time integrators. A first one of the integrators may be arranged to receive a feedback signal from one of the DACs, connected to the first integrator, and the analog input signal of the  $\Delta\Sigma\text{-ADC}$  as input signals. Each of the other integrators may be arranged to receive a feedback signal from one of the DACs, connected to that integrator, and an output signal of a preceding integrator as input signals.

**[0016]** A last one of the cascaded continuous-time integrators may be arranged to generate the analog input signal to the sampled quantizer.

[0017] The continuous-time  $\Delta\Sigma$ -ADC may further com-

prise a memoryless feedback path from the output of the sampled quantizer to the input of the sampled quantizer.

[0018] According to a second aspect, there is provided

a radio receiver circuit comprising the continuous-time  $\Delta\Sigma\text{-ADC}$  according to the first aspect.

[0019] According to a third aspect, there is provided an integrated circuit comprising the continuous-time  $\Delta\Sigma$ -ADC according to the first aspect.

[0020] According to a fourth aspect, there is provided a radio communication apparatus comprising the continuous-time  $\Delta\Sigma$ -ADC according to the first aspect, the radio receiver circuit according to the second aspect, and/or the integrated circuit according to the third aspect.

**[0021]** The radio communication apparatus may e.g. be, but is not limited to, a mobile phone, a wireless data modem, or a radio base station.

**[0022]** Further embodiments are defined in the dependent claims. It should be emphasized that the term "comprises/comprising" when used in this specification is taken to specify the presence of stated features, integers, steps, or components, but does not preclude the presence or addition of one or more other features, integers, steps, components, or groups thereof.

#### Brief description of the drawings

**[0023]** Further objects, features and advantages of embodiments of the invention will appear from the following detailed description, reference being made to the accompanying drawings, in which:

Figs. 1-3 illustrate general continuous-time  $\Delta\Sigma\text{-AD-}\text{Cs}\cdot$

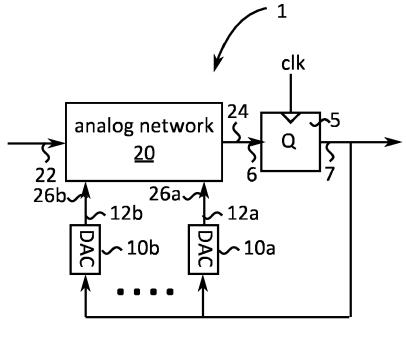

Fig. 4 illustrates a continuous-time  $\Delta\Sigma$ -ADC according to embodiments of the present invention;

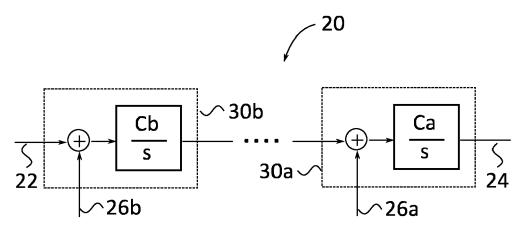

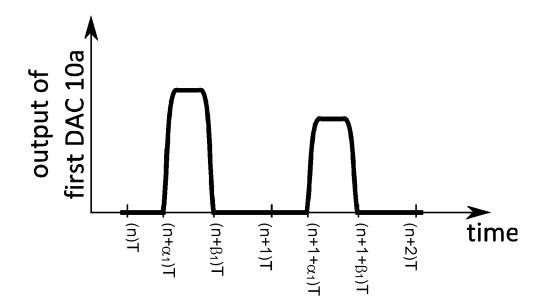

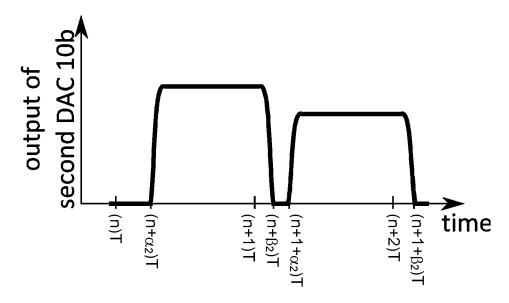

Fig. 5 illustrates a continuous-time analog network according to embodiments of the present invention; Figs. 6-7 illustrate examples of pulse waveforms;

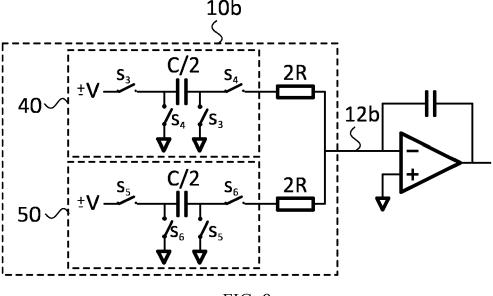

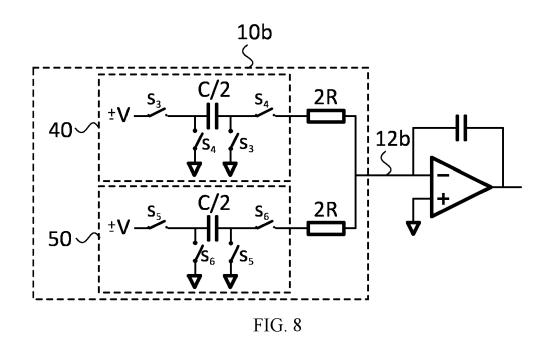

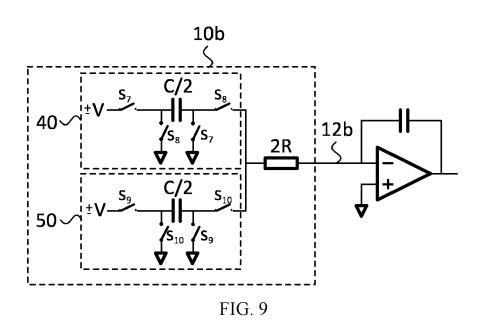

Figs. 8-9 illustrate digital-to-analog converters (DACs) according to embodiments of the present invention;

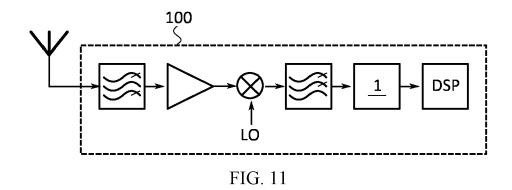

Fig. 10 illustrates an example of pulse waveforms; Fig. 11 schematically illustrates a radio receiver circuit:

Fig. 12 schematically illustrates an integrated circuit; and

Fig. 13 schematically illustrates a mobile phone in communication with a radio base station.

#### 50 Detailed description

[0024] The inventors have realized that a DAC, which is used for feedback in a continuous-time delta-sigma  $(\Delta\Sigma)$  analog-to-digital converter (ADC), can be advantageously implemented using two switched capacitor DACs (as subcomponents) that share a common output and operate on the same input but with a mutual delay in time. Hence, the two switched-capacitor DACs (sub-

20

25

40

45

components) are thus arranged to together act as a single combined DAC, which is different from e.g. two switched-capacitor DACs that have separate individual outputs and/or are arranged to operate on different inputs. Such DACs are described below e.g. in the context of Figs. 8-10. However, to simplify the understanding and to put these descriptions in a context, embodiments of a particular type of continuous-time  $\Delta\Sigma\text{-ADC}$ , developed by the inventors and for which such DACs are well suited, are first described. It should be remembered, though, that the DAC, comprising two switched capacitor DACs as subcomponents, may well be used in other types of continuous-time  $\Delta\Sigma\text{-ADCs}$  as well.

[0025] Fig. 4 is a simplified block diagram of a continuous-time  $\Delta\Sigma\text{-ADC}$  1 according to embodiments of the present invention. The  $\Delta\Sigma\text{-ADC}$  1 comprises a sampled quantizer 5. The sampled quantizer 5 is arranged to receive an analog input signal of the sampled quantizer 5 on an input terminal 6. The sampled quantizer 5 is arranged to generate samples of a digital output signal of the  $\Delta\Sigma\text{-ADC}$  1 at sample instants nT (where n is an integer sequence index and T is a sampling period of the clock signal clk), based on the analog input signal to the quantizer 5. The sample of the digital output signal at the sample instant nT is in the following denoted y(n). The digital output signal is generated on an output port 7 of the sampled quantizer 5. The sampled quantizer 5 may be a single-bit or a multibit quantizer.

[0026] In addition, the  $\Delta\Sigma$ -ADC 1 comprises two or more digital-to-analog converters (DACs) 10a-b, each arranged to generate an analog feedback signal based on the samples of the digital output signal generated by the sampled quantizer 5 on output terminals 12a-b. Each of said two or more DACs may e.g. be of switched-current (e.g. similar to the SI feedback discussed with reference to Fig. 2) or switched-capacitor (e.g. similar to the SI feedback discussed with reference to Fig. 3) type. One (or more) of them is of the type mentioned above, including two switched-capacitor DACs as subcomponents. Furthermore, the  $\Delta\Sigma\text{-ADC}$  1 comprises a continuous-time analog network 20. The continuous-time analog network 20 has an input terminal 26a-b for each of the two or more DACs 10a-b for receiving the feedback signals generated by the DACs 10a-b. The continuous-time analog network is arranged to generate the analog input signal to the quantizer 5, on an output terminal 24 of the continuous-time analog network 20, based on the feedback signals from the two or more DACs 10a-b and an analog input signal to the  $\Delta\Sigma$ -ADC 1, received on an input terminal 22 of the continuous-time analog network 20.

[0027] An example of how the continuous-time analog network 20 may be embodied is illustrated in Fig. 5. As illustrated in Fig. 5, the continuous-time analog network 20 may comprise a plurality of cascaded continuous-time integrators 30a-b. A first one of the integrators (in Fig. 5, the integrator 30b) may be arranged to receive a feedback signal from one of the DACs connected to the first integrator 30b, and the analog input signal of the  $\Delta\Sigma$ -ADC

1 as input signals. Furthermore, as illustrated in Fig. 5, each of the other integrators may be arranged to receive a feedback signal from one of the DACs, connected to that integrator, and the output signal of a preceding integrator as input signals. Moreover, as illustrated in Fig. 5, a last one of the cascaded continuous-time integrators (in Fig. 5, the integrator 30a) may be arranged to generate the analog input signal to the sampled quantizer 5. The integrators may e.g. be implemented as active RC integrators or Gm-C integrators. The design of such integrators with multiple inputs is well known and therefore not further described herein.

**[0028]** According to embodiments of the present invention, at least a first DAC (e.g. 10a, which is the reference sign used for the first DAC in the following) of the two or more DACs 10a-b is adapted to generate a pulsed feedback signal that, for each n, comprises a pulse (e.g. output electrical current pulse), the magnitude of which is proportional to the sample of the digital output signal at sample instant nT and which lasts between the time instants  $(n+\alpha 1)T$  and  $(n+\beta 1)T$ , wherein  $0<\alpha 1<\beta 1<1$ . This is schematically illustrated in Fig. 6 with a waveform diagram.

**[0029]** According to embodiments of the present invention, at least a second DAC (e.g. 10b, which is the reference sign used for the second DAC in the following) of the two or more DACs 10a-b is adapted to generate a pulsed feedback signal that, for each n, comprises a pulse, the magnitude of which is proportional to the sample of the digital output signal at sample instant nT and which lasts between the time instants (n+ $\alpha$ 2)T and (n+ $\beta$ 2)T, wherein  $0 < \alpha 2 < 1 < \beta 2$ . This is schematically illustrated in Fig. 7 with a waveform diagram.

[0030] The inventors have realized that the inner loop or loops (loops with relatively low order of integration) of continuous-time  $\Delta\Sigma$ -ADC contributes more to the sensitivity to excess loop delay of the  $\Delta\Sigma$ -ADC, because their impact on the impulse response of the cascade of feedback DAC and loop filter is the largest, and therefore changes the loop gain of the system the most. The inventors have realized that using a DAC such as the aforementioned first DAC 10a in such inner loop(s) alleviates this problem, since the impulse response of the cascade of feedback DAC and loop filter is less sensitive to a delay of such a feedback pulse. Thereby, the loop gain is affected less, making the closed loop performance of the  $\Delta\Sigma$ -ADC more robust to such delays. In some embodiments, a memoryless feedback path may be included, i.e. with one DAC whose output contributes directly (i.e. without integration) to the analog input signal of the sampled quantizer. Referring to Fig. 5, the output of such a DAC would thus be added to the output of the integrator 30a for forming the analog input signal to the sampled quantizer 5. Such a memoryless path can provide a further reduced sensitivity to loop delay. In some embodiments, further feedback or feedforward paths may also be provided between internal nodes of the continuoustime analog network 20.

[0031] In addition, the inventors have realized that the outer loop or loops (loops with relatively high order of integration) of continuous-time  $\Delta\Sigma$ -ADC may be sensitive to clock jitter and thermal noise since such errors from the outermost loops have less noise shaping than the inner loops when referred to the output of the  $\Delta\Sigma$ -ADC. The inventors have realized that using a DAC such as the aforementioned second DAC 10b in such outer loop (s) alleviates this problem, since they feed back the lowest average current and thereby gives the optimum thermal noise performance and clock jitter sensitivity. In combination, these measures provide reduced requirements on the gain bandwidth of the integrating amplifiers of the innermost loop and the best noise performance of the outermost loop. The present invention therefore facilitates increased sampling rates giving either increased bandwidth or dynamic range of the  $\Delta\Sigma$ -ADC at a low cost. Alternatively, the reduced sensitivity to loop delay can be utilized to reduce the power consumption by reducing the excess bandwidth of the integrating amplifiers commonly introduced to guarantee stability in presence of process variations and mismatch.

[0032] Accordingly, in some embodiments of the present invention, the first DAC 10a is located in a first feedback loop and the second DAC 10b is located in a second feedback loop, which is an outer feedback loop relative to the first feedback loop (i.e., which has a higher order of integration than the first feedback loop). For example, the first loop may be the innermost loop, i.e. a loop with first order integration. Furthermore, the second loop may be the outermost loop, i.e. the loop with the highest order integration.

**[0033]** Even though the timing of the feedback pulses can be chosen arbitrary in principal there are practical restrictions coming from the time required to avoid quantizer metastability, and the complexity of the clocking scheme.

[0034] The decision time of the quantizer requires us to choose the start point of all feedback pulses significantly after the quantizer sampling instant nT (nT  $\ll$  (n+ $\alpha_k$ )T for all k, for example  $\alpha_k > 0.1$ ). The exact timing depends on the clocking scheme. For a two phase (0, 180 degree) clocking scheme, a natural starting point (i.e. (n+ $\alpha k$ )T) is (n+0.5)T, while if a four phase clocking scheme is available, (n+0.25)T may be chosen, and eight phases would facilitate a starting point of (n+0.125)T.

[0035] While the inventors have not found any particular advantage of having different starting points for different feedback pulses, the selection of the endpoint on the other hand, has been found to influence the sensitivity to clock jitter and loop delay, as well as the thermal noise performance of the DAC. It yields the best noise performance to maximize the relative feedback pulse duration ( $\beta$ - $\alpha$ ). Therefore, according to some embodiments, in the outermost loops, which contribute a lot to the overall noise performance of the  $\Delta\Sigma$ -ADC, ( $\beta$ - $\alpha$ ) = 1 is chosen. Thus, depending on the available clock scheme, natural end points for the outermost loops would be (n+ $\beta$ 2)T =

(n+1+0.5)T, (n+1+0.25)T or (n+1+0.125)T. The inventors have further found that the sensitivity to loop delay is reduced if the innermost DAC pulse end point is significantly earlier than the succeeding quantizer sampling instant, i.e.  $\beta 1 \ll 1$ , for example  $\beta_1 < 0.9$ . A convenient choice for most RZ (return to zero) clocking schemes is to have 50% duty cycle for the innermost feedback pulses, resulting in end points of (n+ $\beta$ 1)T = (n+0.5+0.5)T, (n+0.5+0.25)T or (n+0.5+0.125)T, depending on the clock scheme. An important remark here is of course that (n+0.5+0.5)T equals the timing of the succeeding sampling instant and therefore yields no improved sensitivity to loop delay.

[0036] Alternatively, when any clocking scheme is used, arbitrary starting points may be accomplished by using delay elements, such as an inverter or a plurality of cascaded inverters (depending on what delay is desired) to generate delayed clock pulses of other delays than those naturally provided by the clock phases of a particular clocking scheme (e.g. four-phase or eight phase). However, such a delay would have to be relatively exact, or well defined, in order not to change the transfer function of the loop, and it is typically easier to get a high precision in the clock delay by using the already well defined clock phases naturally provided by the particular clocking scheme.

[0037] According to embodiments of the present invention, at least one DAC of the two or more DACs 10a-b comprises two switched-capacitor (SC) DACs (as sub components). Embodiments of such DACs are illustrated in Figs. 8-9. In Figs. 8-9, a first one of the SC DACs is labeled 40 and a second one of the SC DACs is labeled 50. For each n, each of the two switched capacitor DACs 40 and 50 is arranged to be charged with a charge proportional to the corresponding sample y(n) of the digital output signal. The first SC DAC 40 is arranged to be switched in to the continuous-time analog network 20 for transfer of its charge to the continuous-time analog network 20 in a time interval that lasts between the time instants  $(n+\alpha 3)T$  and  $(n+\beta 3)T$ . Furthermore, the second SC DAC 50 is arranged to be switched in to the continuous-time analog network 20 for transfer of its charge to the continuous-time analog network 20 in a time interval that lasts between the time instants  $(n+\alpha 4)T$  and  $(n+\beta 4)$ T. These parameters are related such that  $\beta 4 > 1$ , 0 < $\alpha 3 < \alpha 4 < \beta 4 < 2$  and  $\alpha 3 < \beta 3 \le 1$ . This is schematically illustrated with a waveform diagram in Fig. 10, further discussed below.

**[0038]** According to some embodiments, the aforementioned DAC comprising the two SC DACs (as subcomponents) is the second DAC 10b (in which case  $\alpha 3 = \alpha 2$  and  $\beta 4 = \beta 2$ ), as is also indicated with reference signs 10b used in Figs. 8-9. However, this use of reference signs should not be seen as limiting. Additionally or alternatively, in other embodiments, one or more other DACs may be implemented using two SC DACs (as subcomponents).

[0039] In some embodiments, the DAC comprising the

40

25

40

45

50

two SC DACs is located in a feedback loop, which is an outer feedback loop (i.e. a feedback loop of higher order) relative to the first feedback loop.

[0040] In the SC feedback according to Fig. 1 discussed in the background, a capacitor  $\mathbf{C}_{\text{REF}},$  is switched using a set of switches between the reference voltage V<sub>REF</sub> and to the inverting input of the operational amplifier. A reference resistance R<sub>REF</sub> might be connected on either side of the capacitor to lower the time constant of the switching RC circuit. The reference capacitor is charged with the reference voltage ( $V_{RFF+}$  or  $V_{RFF-}$ ) corresponding to the digital output bit (single-bit quantization is assumed) in a first clock phase, and then transfers a well defined charge packet  $Q = C^*V_{REF}$  to the integrator in a second clock phase when the switch circuit switches the reference capacitor C<sub>REF</sub> to the inverting input of the amplifier. The discharge of the capacitor C<sub>RFF</sub> will give an exponentially falling current pulse  $\tau$  I = Io\*exp(-t/ $\tau$ ) where  $\tau = R_{REF} * C_{REF}$  is the time constant. Because of the exponentially decreasing pulse shape the charge Q displaced in one clock cycle T varies only slightly when clock jitter occurs, and thus this technique is less sensitive to clock jitter than the  $\Delta\Sigma$  ADCs illustrated in Figs. 1-2. Furthermore, an advantage of using two switched capacitor DACs with mutually displaced output pulses has the advantage, compared with a single switchedcapacitor DAC, that the peak current is reduced, whereby the risk of slewrate limitations in the continuous-time analog network 20 is reduced. This can e.g. be exploited by implementing the continuous-time analog network 20 using components with less harsh slewrate requirements, which in turn enables a reduced current consumption.

[0041] Fig. 8 shows a 1-bit version of the DAC comprising the two SC DACs 40-50 according to an embodiment. Each SC DAC 40 and 50 comprises a capacitor and a set of switches as depicted in Fig. 8. Switches of the SC DACs 40 and 50 are controlled by non-overlapping switch phases s3-s4 and s5-s6, respectively. Below, the output bit of the quantizer 5 is assumed to be 1. If it is 0, then V shall be replaced by -V in the following discussion. When s3 is on (conducting) the first of the switched capacitor DACs 40 is charging to Q=V\*C/2. When s4 is on the first of the switched capacitor DACs 40 is discharging into the analog network 20. For proper operation s3 and s4 should not be on at the same time. When s5 is on the second of the switched capacitor DACs 50 is charging to Q=V\*C/2. When s6 is on the second of the switched capacitor DACs 50 is discharging into the analog network 20. For proper operation s5 and s6 should not be on at the same time.

**[0042]** A resistor (with resistance 2R) is connected in series with each one of the switched capacitors to control the time constant (RC) of its discharge and the peak of the output current I=V/(2R). In Fig. 9, the two SC DACs 40 and 50 are implemented as in Fig. 8. However, in Fig. 9, a shared resistor (with resistance 2R) is used for the two SC DACs 40 and 50.

**[0043]** For someone skilled in the art it is straightforward to extend the 1-bit switched capacitor DACs shown in Figs. 8 and 9 into multi-bit switched capacitor DACs by using e.g. binary weighted or thermometer coded switched capacitor banks controlled in the same way (for embodiments where the quantizer 5 is a multibit quantizer).

[0044] The first 40 and the second 50 SC DAC together generate an overall DAC impulse response as exemplified in Fig.10. Generally, the two discharge time intervals of the first 40 and second 50 of the switched capacitor DACs can be chosen arbitrary. In Fig. 10, they have been illustrated for  $\beta$ 3 <  $\alpha$ 4 for ease of illustration. However, in other embodiments these parameters may be such that  $\beta 3 > \alpha 4$  or  $\beta 3 = \alpha 4$  as well. The inventors have found that having  $\beta 3 = \alpha 4$  typically yields the best or close to the best implementation in practice. Also, it seems practical to have the same capacitor size in the first 40 and the second 50 of the switched capacitor DACs (letting them carry half of the charge from each of the sampling instants nT each), as shown in Fig. 8 and Fig. 9, even though any other ratio between the capacitor sizes could be used in principal. Having equal capacitor size also gives the same discharge time constants for the two segments of the impulse response.

[0045] Using a two-phase (0 and 180 degrees) clock scheme can yield the following timing of the feedback pulses:  $\alpha 3=0.5$ ,  $\beta 3=\alpha 4=1$ , and  $\beta 4=1.5$ . Since the charging of the switched capacitor DACs will take place from  $(n-1+\beta 3)T$  to  $(n+\alpha 3)T$  and  $(n-1+\beta 4)T$  to  $(n+\alpha 4)T$  the first of the switched capacitor DACs 40 will charge with a charge proportional to the sample of the digital output signal at sample instant nT in the same time interval as the second of the switched capacitor DACs 50 is discharging its charge proportional to the sample of the digital output signal at the preceding sample instant (n-1)T. [0046] Using a four-phase (0, 90, 180, and 270 degrees) clock scheme could e.g. yield the following timing of the feedback pulses:  $\alpha 3=0.25$ ,  $\beta 3=\alpha 4=1$ , and  $\beta 4=1.75$ . Since the sum of the discharge time intervals of the first and second of the switched capacitor DACs 40 is greater than the sampling interval T, there will be some overlap between the discharge time intervals of the first and second of the switched capacitor DACs 50, in this case from (n+0.25)T to (n+0.75)T, for all n.

**[0047]** When the discharge time intervals of the first and second of the switched capacitor DACs is not overlapping, as is the case for the two-phase clock scheme above, the series resistor can be shared between the first 40 and second 50 of the switched capacitor DACs, as shown in Fig. 9.

[0048] According to some embodiments, a radio receiver circuit comprises the continuous-time  $\Delta\Sigma$ -ADC 1. This is schematically illustrated in Fig. 11, where the continuous-time  $\Delta\Sigma$ -ADC 1 is placed in a radio receiver circuit 100 in between the analog signal processing domain domain (circuits to the left of the  $\Delta\Sigma$ -ADC 1) and the digital signal processing domain (block marked DSP).

15

20

25

30

40

45

50

55

[0049] According to some embodiments, an integrated circuit comprises the continuous-time  $\Delta\Sigma$ -ADC 1. This is schematically illustrated in Fig. 12, where the continuous-time  $\Delta\Sigma$ -ADC 1 is placed in an integrated circuit (IC) 200.

[0050] In some embodiments, a radio communication apparatus comprises the continuous-time  $\Delta\Sigma$ -ADC 1. For example, the radio communication apparatus may comprise a radio receiver circuit, such as the radio receiver circuit 100 and/or an integrated circuit, such as the integrated circuit 200, that in turn comprises the  $\Delta\Sigma$ -ADC 1. [0051] Non-limiting examples of such radio communication apparatuses are a mobile phone, a wireless data modem, and a radio base station. Fig. 13 schematically illustrates examples of radio communication apparatuses in the form of a mobile phone 300 and a radio base station 400 in communication with each other.

[0052] The present invention has been described above with reference to specific embodiments. However, other embodiments than the above described are possible within the scope of the invention. For example, as indicated in the beginning of this detailed description, the DAC comprising two SC DACs as subcomponents may be used in other types of continuous-time  $\Delta\Sigma$ -ADCs than the continuous-time  $\Delta\Sigma$ -ADC embodiments described above. For example, in some embodiments, the continuous-time  $\Delta\Sigma$ -ADC may comprise only a single DAC (which in turn comprises two SC DACs, acting on the same input signal and having a common output, as sub components). Furthermore, in addition to the types of DACs described, other types of DACs, e.g. using other pulse durations, may be used as well in some feedback loops of the  $\Delta\Sigma$ -ADC. The different features of the embodiments may be combined in other combinations than those described. The scope of the invention is only limited by the appended patent claims.

## Claims

1. A continuous-time delta-sigma,  $\Delta\Sigma$ , analog-to-digital converter, ADC, (1) comprising:

a sampled quantizer (5) arranged to generate samples y(n) of a digital output signal of the  $\Delta\Sigma$ -ADC (1) at sample instants nT, where n is an integer sequence index and T is a sampling period, based on an analog input signal to the quantizer (5);

one or more digital-to-analog converters, DACs, (10a-b), each arranged to generate an analog feedback signal based on the samples of the digital output signal generated by the sampled quantizer (5); and

a continuous-time analog network (20) arranged to generate the analog input signal to the quantizer (5) based on the feedback signal(s) from the one or more DACs (10a-b) and an analog

input signal to the  $\Delta\Sigma$ -ADC (1); wherein at least one DAC (10b) of the one or more DACs (10b) comprises two switched-capacitor DACs (40, 50) arranged to operate on the same input but with a mutual delay in time.

2. The continuous-time  $\Delta\Sigma$ -ADC (1) according to claim 1, wherein, for each n:

- each of the two switched capacitor DACs (40, 50) is arranged to be charged with a charge proportional to the sample y(n) of the digital output signal;

- a first of the switched capacitor DACs (40) is arranged to be switched in to the continuous-time analog network (20) for transfer of its charge to the continuous-time analog network (20) in a time interval that lasts between the time instants  $(n+\alpha 3)T$  and  $(n+\beta 3)T$ ; and

- a second of the switched capacitor DACs (50) is arranged to be switched in to the continuous-time analog network (20) for transfer of its charge to the continuous-time analog network (20) in a time interval that lasts between the time instants (n+ $\alpha$ 4)T and (n+ $\beta$ 4)T;

wherein  $\beta 4$  >1,  $0 < \alpha 3 < \alpha 4 < \beta 4 < 2$  and  $\alpha 3 < \beta 3 \leq 1$ .

3. The continuous-time  $\Delta\Sigma$ -ADC (1) according to claim 2, wherein  $\alpha 4 \le \beta 3$ .

**4.** The continuous-time  $\Delta\Sigma$ -ADC (1) according to claim 2, wherein  $\alpha$ 4 = β3.

5 **5.** The continuous-time  $\Delta\Sigma$ -ADC (1) according to claim 4, wherein  $\alpha$ 4=β3=1,  $\alpha$ 3 = 0.5, and β4=1.5.

6. The continuous-time ΣΔ-ADC (1) according to any preceding claim, wherein said one or more DACs (10a-b) comprises one or more additional DACs (10a), in addition to the at least one DAC comprising the two switched capacitor DACs, wherein at least a first DAC (10a) of the one or more additional DACs (10a b) is about the two switched to the content of the conte

DACs (10a-b) is adapted to generate a pulsed feed-back signal that, for each n, comprises a pulse, the magnitude of which is proportional to the sample of the digital output signal at sample instant nT and which lasts between the time instants  $(n+\alpha 1)T$  and  $(n+\beta 1)T$ , wherein  $0 < \alpha 1 < \beta 1 < 1$ ;

wherein the first DAC (10a) is located in a first feedback loop and the DAC (10b) comprising the two switched-capacitor DACs is located in a second feedback loop, which is an outer feedback loop relative to the first feedback loop.

7. The continuous-time  $\Delta\Sigma$ -ADC (1) according to any preceding claim, wherein the continuous-time analog network (20) comprises a plurality of cascaded

continuous-time integrators (30a-b).

8. The continuous-time  $\Delta\Sigma$ -ADC(1) according to claim 7, wherein

- a first one of the integrators (30b) is arranged to receive a feedback signal from one of the DACs (10b), connected to the first integrator (30b), and the analog input signal of the  $\Delta\Sigma$ -ADC (1) as input signals; and

- each of the other integrators (30a) is arranged to receive a feedback signal from one of the DACs (10a), connected to that integrator (30a), and the an output signal of a preceding integrator as input signals.

- 9. The continuous-time  $\Delta\Sigma$ -ADC (1) according to claim 7 or 8, wherein a last one of the cascaded continuous-time integrators (30a) is arranged to generate the analog input signal to the sampled quantizer (5).

- 10. The continuous-time  $\Delta\Sigma$ -ADC (1) according to any preceding claim, further comprising a memoryless feedback path from the output of the sampled quantizer (5) to the input of the sampled quantizer (5).

- 11. A radio receiver circuit (100) comprising the continuous-time  $\Delta\Sigma$ -ADC (1) according to any preceding claim.

- 12. An integrated circuit (200) comprising the continuous-time  $\Sigma\Delta$ -ADC (1) according to any of the claims 1-10.

- 13. A radio communication apparatus (300, 400) comprising the continuous-time  $\Delta\Sigma$ -ADC (1) according to any of the claims 1-10, the radio receiver circuit (100) according to claim 11, or the integrated circuit (200) according to claim 12.

- **14.** The radio communication apparatus (1) according to claim 13, wherein the radio communication apparatus is a mobile phone (1) or a wireless data modem.

- **15.** The radio communication apparatus (2) according to claim 13, wherein the radio communication apparatus is a radio base station (2).

5

15

25

30

35

40

45

50

55

FIG. 2

FIG. 4

FIG. 5.

FIG. 6

FIG. 7

FIG. 10

FIG. 12

FIG. 13

## **EUROPEAN SEARCH REPORT**

Application Number EP 11 18 9057

|                                                            | DOCUMENTS CONSID                                                                                                                                                                                                                                                                                                                                                  | ERED TO BE RELEVANT                                                                                                                             |                                                                                                                    |                                         |  |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|

| Category                                                   | Citation of document with in<br>of relevant pass                                                                                                                                                                                                                                                                                                                  | ndication, where appropriate,<br>ages                                                                                                           | Relevant<br>to claim                                                                                               | CLASSIFICATION OF THE APPLICATION (IPC) |  |

| X                                                          | Jitter Immunity Imp<br>SCR (FSCR) DAC and<br>IEEE JOURNAL OF SOU<br>SERVICE CENTER, PIS<br>vol. 46, no. 11,<br>1 November 2011 (20<br>2469-2477, XP011358<br>ISSN: 0018-9200, DO<br>10.1109/JSSC.2011.2<br>* page 2469, right-<br>2470, left-hand col<br>* page 2472, left-h<br>* page 2472, right-<br>2473, left-hand col<br>* table II *<br>* figures 1,2,4,5a, | yma-Delta Modulator With proved Full Clock Period High-Speed DWA", ID-STATE CIRCUITS, IEEE CCATAWAY, NJ, USA, USA, USA, USA, USA, USA, USA, USA |                                                                                                                    | INV.<br>H03M3/02                        |  |

| A                                                          | 20 MHz Band",                                                                                                                                                                                                                                                                                                                                                     | drature Cascaded BDR in a Near Zero-IF LID-STATE CIRCUITS, IEEE CCATAWAY, NJ, USA, 007-12-01), pages 036, 01:                                   | 1-15                                                                                                               | TECHNICAL FIELDS<br>SEARCHED (IPC) H03M |  |

| The present search report has been drawn up for all claims |                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                 |                                                                                                                    |                                         |  |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                   | Date of completion of the search                                                                                                                |                                                                                                                    | Examiner                                |  |

|                                                            | The Hague                                                                                                                                                                                                                                                                                                                                                         | 25 May 2012                                                                                                                                     | Roc                                                                                                                | ha, Daniel                              |  |

| X : part<br>Y : part<br>docu<br>A : tech<br>O : non        | ATEGORY OF CITED DOCUMENTS icularly relevant if taken alone icularly relevant if combined with anotument of the same category inological background-written disclosure mediate document                                                                                                                                                                           | E : earlier patent doc<br>after the filing date<br>her D : document cited in<br>L : document cited fo                                           | document cited in the application locument cited for other reasons nember of the same patent family, corresponding |                                         |  |

EPO FORM 1503 03.82 (P04C01)

3

## **EUROPEAN SEARCH REPORT**

Application Number EP 11 18 9057

| Category                                                                                                                                                                                                                                | Citation of document with ir<br>of relevant pass                                                                                                    | ndication, where appropriate,<br>ages                                                                                                | Relevar<br>to claim                                                                                                                                                                                                                                           |                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Α                                                                                                                                                                                                                                       | and 1.1-MHz Signal IEEE JOURNAL OF SOL SERVICE CENTER, PIS vol. 39, no. 1, 1 January 2004 (200 XP011105690, ISSN: 0018-9200, DC 10.1109/JSSC.2003.8 | <pre>&lt;\$Sigma Delta th 88-dB Dynamic Range Bandwidth", ID-STATE CIRCUITS, IEEE CATAWAY, NJ, USA, 4-01-01), pages 75-86, II:</pre> | 1-15                                                                                                                                                                                                                                                          |                                    |

| Α                                                                                                                                                                                                                                       | Feedback Technique<br>clock-jitter sensit                                                                                                           | ivity in ma-delta modulators", TS, AND SYSTEMS IEEE INTERNATIONAL 010-12-12), pages 9, 2010.5724570 55-2                             | 1-15                                                                                                                                                                                                                                                          | TECHNICAL FIELDS<br>SEARCHED (IPC) |

| X,P DEJAN RADJEN ET AL: "A contimodulator with reduced clock sensitivity through DSCR feed NORCHIP, 2011, IEEE, 14 November 2011 (2011-11-14) XP032092354, DOI: 10.1109/NORCHP.2011.6126 ISBN: 978-1-4577-0514-4 * the whole document * |                                                                                                                                                     | ced clock jitter<br>DSCR feedback",<br>011-11-14), pages 1-4,<br>2.2011.6126701                                                      | 1-15                                                                                                                                                                                                                                                          |                                    |

|                                                                                                                                                                                                                                         | The present search report has                                                                                                                       | oeen drawn up for all claims                                                                                                         |                                                                                                                                                                                                                                                               |                                    |

|                                                                                                                                                                                                                                         | Place of search                                                                                                                                     | Date of completion of the search                                                                                                     |                                                                                                                                                                                                                                                               | Examiner                           |

| The Hague 25 M                                                                                                                                                                                                                          |                                                                                                                                                     | 25 May 2012                                                                                                                          | Rocha, Daniel                                                                                                                                                                                                                                                 |                                    |

| CATEGORY OF CITED DOCUMENTS  X: particularly relevant if taken alone Y: particularly relevant if combined with another document of the same category A: technological background O: non-written disclosure P: intermediate document     |                                                                                                                                                     | E : earlier patent door after the filing date D : dooument cited in L : document cited for                                           | T: theory or principle underlying the invention E: earlier patent document, but published on, or after the filling date D: document cited in the application E: document cited for other reasons  S: member of the same patent family, corresponding document |                                    |

## **EUROPEAN SEARCH REPORT**

Application Number EP 11 18 9057

|                                                                                                                                                                                                                                     | DOCUMENTS CONSID                                                                         | ERED TO BE RELEVANT                                                                                                                 |                                                                                                                                                                                                                                                             |                                         |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|

| Category                                                                                                                                                                                                                            | Citation of document with ir of relevant passa                                           | ndication, where appropriate,<br>ages                                                                                               | Relevant<br>to claim                                                                                                                                                                                                                                        | CLASSIFICATION OF THE APPLICATION (IPC) |  |

| A                                                                                                                                                                                                                                   | WO 2008/071791 A1 (<br>[SE]; SUNDSTROEM LA<br>MARTIN [) 19 June 2<br>* the whole documen | 008 (2008-06-19)                                                                                                                    | 1-15                                                                                                                                                                                                                                                        |                                         |  |

| A                                                                                                                                                                                                                                   | WO 2006/067382 A1 ( KALE IZZET [GB]; MO SPICER) 29 June 200 * the whole documen          | RLING RICHARD CHARLES (<br>6 (2006-06-29)                                                                                           | 1-15                                                                                                                                                                                                                                                        |                                         |  |

|                                                                                                                                                                                                                                     |                                                                                          |                                                                                                                                     |                                                                                                                                                                                                                                                             | TECHNICAL FIELDS<br>SEARCHED (IPC)      |  |

|                                                                                                                                                                                                                                     |                                                                                          |                                                                                                                                     |                                                                                                                                                                                                                                                             |                                         |  |

|                                                                                                                                                                                                                                     | The present search report has I                                                          | peen drawn up for all claims                                                                                                        |                                                                                                                                                                                                                                                             |                                         |  |

|                                                                                                                                                                                                                                     | Place of search                                                                          | Date of completion of the search                                                                                                    |                                                                                                                                                                                                                                                             | Examiner                                |  |

|                                                                                                                                                                                                                                     | The Hague                                                                                | 25 May 2012                                                                                                                         | Roc                                                                                                                                                                                                                                                         | ha, Daniel                              |  |

| CATEGORY OF CITED DOCUMENTS  X: particularly relevant if taken alone Y: particularly relevant if combined with another document of the same category A: technological background O: non-written disclosure P: intermediate document |                                                                                          | T: theory or principle E: earlier patent docu after the filing date D: document cited in L: document cited for &: member of the sar | T: theory or principle underlying the invention E: earlier patent document, but published on, or after the filing date D: document cited in the application L: document cited for other reasons 8: member of the same patent family, corresponding document |                                         |  |

## ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 11 18 9057

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

25-05-2012

|               |    | date       |                                                          | Patent family<br>member(s)                                          |                                                       | Publication<br>date                                                                                                        |

|---------------|----|------------|----------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| WO 2008071791 | A1 | 19-06-2008 | AT<br>AU<br>CA<br>EP<br>ES<br>JP<br>JP<br>TW<br>US<br>WO | 2672698<br>2127087<br>2361954<br>4860760<br>2010514384<br>200838151 | T<br>A1<br>A1<br>A1<br>T3<br>B2<br>A<br>A<br>A1<br>A1 | 15-03-2011<br>19-06-2008<br>19-06-2008<br>02-12-2009<br>24-06-2011<br>25-01-2012<br>30-04-2010<br>16-09-2008<br>19-06-2008 |

| WO 2006067382 | A1 | 29-06-2006 | AT<br>CN<br>EP<br>GB<br>JP<br>VR<br>US<br>WO             | 1834407<br>2437025<br>4658140<br>2008526064<br>20070087157          | T<br>A<br>A1<br>A<br>B2<br>A<br>A<br>A1               | 15-04-2010<br>12-03-2008<br>19-09-2007<br>10-10-2007<br>23-03-2011<br>17-07-2008<br>27-08-2007<br>08-05-2008<br>29-06-2006 |

FORM P0459

For more details about this annex : see Official Journal of the European Patent Office, No. 12/82