# (11) **EP 2 685 629 A1**

(12)

# EUROPEAN PATENT APPLICATION

published in accordance with Art. 153(4) EPC

(43) Date of publication: 15.01.2014 Bulletin 2014/03

(21) Application number: 12767408.3

(22) Date of filing: 13.03.2012

(51) Int CI.:

H03D 7/18 (2006.01)

H04B 1/30 (2006.01)

H03D 7/00 (2006.01)

(86) International application number:

PCT/CN2012/072243

(87) International publication number:

WO 2012/136093 (11.10.2012 Gazette 2012/41)

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

(30) Priority: 02.04.2011 CN 201110083379

(71) Applicant: Huawei Technologies Co., Ltd. Shenzhen, Guangdong 518129 (CN)

(72) Inventors:

• CAI, Hua Shenzhen Guangdong 518129 (CN)  SHUAI, Songlin Shenzhen Guangdong 518129 (CN)

HE, Jia

Shenzhen

Guangdong 518129 (CN)

ZHANG, Yong Shenzhen Guangdong 518129 (CN)

(74) Representative: Körber, Martin Hans

Mitscherlich & Partner Patent- und Rechtsanwälte Sonnenstrasse 33 80331 München (DE)

# (54) FREQUENCY MIXING CIRCUIT AND METHOD FOR SUPPRESSING LOCAL OSCILLATOR LEAKAGE THEREIN

(57) Embodiments of the present invention disclose a frequency mixing circuit and a method for suppressing local oscillation leakage in the frequency mixing circuit, where a mixed input signal and a local oscillation signal are involved, and local oscillation leakage can be effectively reduced by using a frequency mixing circuit whose structure is simpler and is easier to be implemented. The

frequency mixing circuit includes a direct current bias circuit, where the direct current bias circuit includes a direct current bias voltage source used for reducing a local oscillation current. The frequency mixing circuit is mainly applied to frequency mixing, and especially to a case where an intermediate frequency signal is mixed with a local oscillation signal to output a radio frequency signal.

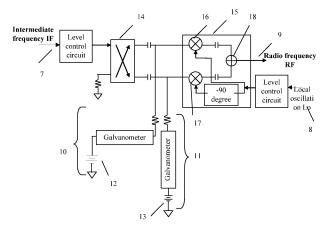

FIG. 7

#### Description

[0001] This application claims priority to Chinese Patent Application No. 201110083379.3, filed on April 2, 2011 and entitled "FREQUENCY MIXING CIRCUIT AND METHOD FOR SUPPRESSING LOCAL OSCILLATION LEAKAGE IN FREQUENCY MIXING CIRCUIT", which is incorporated herein by reference in its entirety.

#### **FIELD OF THE INVENTION**

**[0002]** The present invention relates to a mixed input signal and a local oscillation signal, and in particular, to a frequency mixing circuit and a method for suppressing local oscillation leakage in the frequency mixing circuit.

#### **BACKGROUND OF THE INVENTION**

**[0003]** Frequency mixing, which is also called frequency conversion in terms of engineering, is a process of converting one value of a frequency of a signal into another value. A circuit that implements this frequency mixing function is called a frequency mixing circuit or frequency conversion circuit, and is also called a frequency mixer or frequency converter.

**[0004]** The frequency mixing circuit has been widely applied to communications engineering and wireless technologies. Generally, every wireless communications apparatus has a transmitter and a receiver, where the transmitter is configured to convert user data into a radio frequency signal for data transmission, and the receiver is configured to convert a received radio frequency signal into user data for data receiving.

**[0005]** The frequency mixing circuit plays an important role in transmitting/receiving a radio frequency signal, no matter in a transmitter or a receiver. In the transmitter, the frequency mixing circuit mixes an input signal (a baseband signal or an intermediate frequency signal) with a local oscillation signal to generate a to-be-transmitted radio frequency signal. In the receiver, the frequency mixing circuit mixes a radio frequency signal received by an antenna with a local oscillation signal to generate a baseband signal or an intermediate frequency signal.

[0006] The frequency mixing circuit is more widely applied especially in a superheterodyne receiver, for example, converting an amplitude-modulated 535 KHZ-1605 KHZ signal into a 465 KHZ intermediate frequency signal by an AM broadcast receiver, converting a modulated 48.5 M-870 M image signal into a 38 MHZ intermediate frequency image signal by a television receiver, and one intermediate frequency and double intermediate frequency in mobile communications.

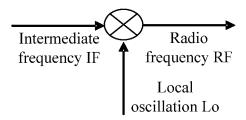

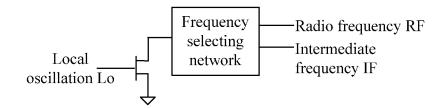

**[0007]** A superheterodyne architecture is a main frequency-conversion manner of a current microwave transmitter, as shown in FIG. 1, which mixes information or an intermediate frequency modulation signal IF with a local oscillation signal Lo whose frequency is higher, and

boosts a modulation signal carrier to a radio frequency RF.

**[0008]** A frequency of a signal carrier is converted from  $f_{IF}$  to  $f_{RF}$ , and their relation may be  $f_{RF} = f_{LO} + f_{IF}$  or  $f_{RF} = f_{LO} - f_{IF}$ . Due to nonlinearity of the frequency mixing circuit, frequency components of an output signal may be expressed as  $f_{RF} = n^*f_{LO} + m^*f_{IF}$ , where n and m are integers.

**[0009]** If  $f_{RF} = f_{LO} + f_{IF}$  is taken as an output signal of the frequency mixing circuit, generally, in addition to this signal, a spurious signal  $f_{LO}$  is further included at an RF outputting port of the frequency mixing circuit, that is, local oscillation leakage occurs.

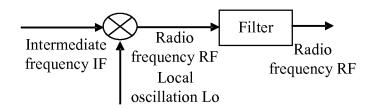

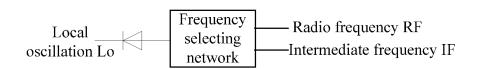

[0010] To reduce the local oscillation leakage of the frequency mixing circuit, a filter may be used in the frequency mixing circuit. As shown in FIG. 2, by using frequency selectivity of the filter, a radio frequency signal can pass, and a local oscillation frequency is suppressed. [0011] By adopting the foregoing solution to reduce the local oscillation leakage of the frequency mixing circuit, the filter needs to have better frequency selectivity, and the interconnection between the filter and a system is relatively complicated; and furthermore, performance of the filter is greatly affected by a process capability, so that implementability is poor. In addition, because the filter is an element that has frequency selectivity, and a frequency selectivity feature contradicts with wide area coverage of a frequency, this solution cannot satisfy a requirement of a broadband application of the frequency mixing circuit.

## **SUMMARY OF THE INVENTION**

**[0012]** Embodiments of the present invention provide a frequency mixing circuit and a method for suppressing local oscillation leakage in the frequency mixing circuit, so as to effectively reduce local oscillation leakage by using a frequency mixing circuit whose structure is simpler and is easier to be implemented.

**[0013]** To achieve the foregoing objective, the embodiments of the present invention adopt the following technical solutions:

**[0014]** A frequency mixing circuit includes: a direct current bias circuit, where the direct current bias circuit includes a direct current bias voltage source used for reducing a local oscillation current.

**[0015]** A method for suppressing local oscillation leakage in a frequency mixing circuit, where the frequency mixing circuit includes a direct current bias circuit, and the method includes the following steps:

calculating a value of  $V_b$  according to formulas

$$\frac{d |f_{Lo}(a_1, a_2, \dots, a_k, V_{Lo}, V_{IF}, V_b)|}{dV_b} = 0 \quad \text{and} \quad$$

50

25

40

50

55

$$\frac{d^2 \left| f_{Lo}(a_1, a_2, \dots, a_k, V_{Lo}, V_{IF}, V_b) \right|}{d^2 V_b} > 0$$

where  $V_b$  represents a voltage value of a direct current bias voltage source,  $a_1, a_2, ..., a_k$  represent coefficients of voltage values in a relation between a current and a voltage across a nonlinear resistor, k represents a non-zero natural number,  $V_{Lo}$  represents a voltage value of a local oscillation voltage source,  $V_{IF}$  represents a voltage value of an intermediate frequency voltage source, and  $f_{Lo}(a_1, a_2, ..., a_k, V_{Lo}, V_{IF}, V_b)$  represents a value of a local oscillation current; and

setting a voltage value of a voltage source of the

direct current bias circuit to  $V_h$ .

[0016] With the frequency mixing circuit and the method for suppressing local oscillation leakage in the frequency mixing circuit provided in the embodiments of the present invention, a direct current bias circuit that is simpler and is easier to be implemented is disposed in a frequency mixing circuit; when a voltage value of a bias voltage source of the direct current bias circuit changes, a value of a local oscillation current also changes correspondingly; and when the voltage value of the direct current bias voltage source is a certain specified value, the value of the local oscillation current can be decreased, thereby effectively reducing local oscillation leakage of the frequency mixing circuit.

## **BRIEF DESCRIPTION OF THE DRAWINGS**

[0017] To illustrate the technical solutions in the embodiments of the present invention or in the prior art more clearly, the following briefly introduces the accompanying drawings required for describing the embodiments or the prior art. Apparently, the accompanying drawings in the following description show merely some embodiments of the present invention, and a person of ordinary skill in the art may still derive other drawings from these accompanying drawings without creative efforts.

FIG. 1 is a schematic diagram of a superheterodyne architecture in the prior art;

FIG. 2 is a schematic diagram of a structure for reducing local oscillation leakage of a frequency mixing circuit by using a filter;

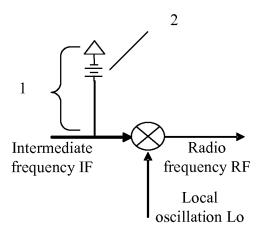

FIG. 3 is a structural diagram of a frequency mixing circuit according to an embodiment of the present invention:

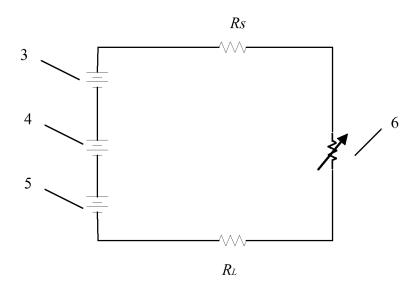

FIG. 4 is a diagram of a structure for implementing frequency mixing by using a field effect transistor FET:

FIG. 5 is a diagram of a structure for implementing frequency mixing by using a diode;

FIG. 6 is a principle diagram of the frequency mixing

circuit shown in FIG. 3:

FIG. 7 is a structural diagram of another frequency mixing circuit according to an embodiment of the present invention;

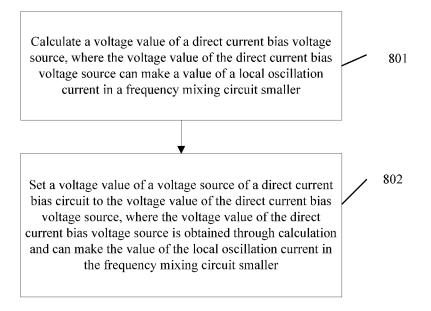

FIG. 8 is a flow chart of a method for suppressing local oscillation leakage in a frequency mixing circuit according to an embodiment of the present invention; and

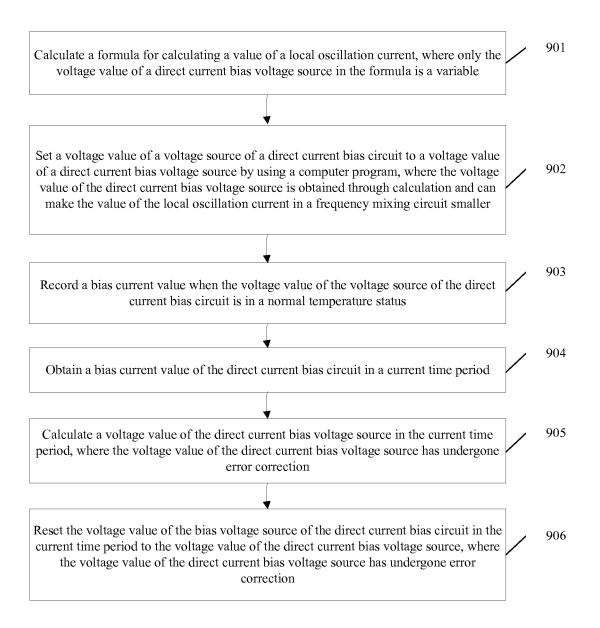

FIG. 9 is a flow chart of another method for suppressing local oscillation leakage in a frequency mixing circuit according to an embodiment of the present invention.

#### **DETAILED DESCRIPTION OF THE EMBODIMENTS**

**[0018]** The following clearly and completely describes the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Apparently, the embodiments to be described are merely a part rather than all of the embodiments of the present invention. All other embodiments obtained by a person of ordinary skill in the art based on the embodiments of the present invention without creative efforts shall fall within the protection scope of the present invention.

**[0019]** An embodiment of the present invention provides a frequency mixing circuit, and as shown in FIG. 3, the frequency mixing circuit includes a direct current bias circuit 1, where the direct current bias circuit 1 includes a direct current bias voltage source 2 used for reducing a local oscillation current.

**[0020]** This embodiment is applicable to a manner for implementing frequency mixing by using a field effect transistor FET shown in FIG. 4 and a manner for implementing frequency mixing by using a diode shown in FIG.

**[0021]** The field effect transistor FET may be equivalent to a nonlinear resistor. A principle of the frequency mixing circuit shown in FIG. 3 is analyzed in the following. First, according to an existing method, structures shown in FIG. 4 and FIG. 5 may be equivalent to a circuit shown in FIG. 6.

**[0022]** As shown in FIG. 6, the frequency mixing circuit includes a local oscillation voltage source 3, an intermediate frequency voltage source 4, a direct current bias voltage source 5, a nonlinear resistor 6, source impedance Rs for generating an excitation signal, and load impedance R1.

**[0023]** It is assumed that a relation between a voltage and a current across the nonlinear resistor 6 satisfies the following relation:

$$I = \sum_{n=1}^{n=k} a_n V^n$$

k  $\leq$  (1), where  $I$  represents a current

across the nonlinear resistor 6, V represents a voltage across the nonlinear resistor 6, and  $a_n$  represents a coefficient that indicates a device feature.

[0024] A total loop voltage source  $Va=V_{IO}^*\cos w_{IO}t+V_{IF}^*\cos w_{IF}t+Vb$ (2),where Va represents a voltage value of the total loop voltage source and includes a direct voltage and an alternating voltage,  $V_{Lo}$  represents a voltage value of the local oscillation voltage source 3,  $V_{IF}$  represents a voltage value of the intermediate frequency voltage source 4, and  $V_b$ represents a direct voltage value of the direct current bias voltage source 5.

**[0025]** Direct current values generated by the local oscillation voltage source 3, the intermediate frequency voltage source 4, and the direct current bias voltage source 5 may be obtained by substituting formula (2) to formula (1).

**[0026]** A direct current value generated by the direct current bias voltage source 5 is:  $I_{dc} = f_{dc}(a_1, a_2, ..., a_k, V_{Lo}, V_{IF}, V_b)$ , where  $I_{dc}$  represents the direct current value generated by the direct current bias voltage source 5, and  $a_1, a_2, ..., a_k$  represent coefficients of voltages across the nonlinear resistor 6 in formula (1).

**[0027]** A current generated by the local oscillation voltage source 3 is:  $I_{Lo} = f_{Lo}(a_1, a_2, ..., a_k, V_{Lo}, V_{IF}, V_b)$ .

**[0028]** Multiple different voltage values  $V_b$  are set for the direct current bias voltage source 5, and  $I_{dc}$ ,  $V_{Lo}$ , and  $V_{IF}$  that correspond to each voltage value  $V_b$  may be obtained through measurement. The coefficient  $a_n$  in the expression of the nonlinear resistor 6 may be obtained by using a data-fitting method.

**[0029]** The obtained coefficient  $a_n$  in the expression of the relation between the voltage and the current across the nonlinear resistor 6 is substituted to  $f_{Lo}(a_1, a_2, ..., a_k, V_{Lo}, V_{IF}, V_b)$ . A value of  $V_b$  is calculated according to

$$\label{eq:formulas} \begin{array}{cc} \frac{d\mid f_{{\scriptscriptstyle Lo}}(a_{\scriptscriptstyle 1},a_{\scriptscriptstyle 2},...,a_{\scriptscriptstyle k},V_{{\scriptscriptstyle Lo}},V_{{\scriptscriptstyle IF}},V_{\scriptscriptstyle b})\mid}{dV_{\scriptscriptstyle b}} = 0 \end{array}$$

and

$$\frac{d^2 \left| f_{Lo}(a_1, a_2, \ldots, a_k, V_{Lo}, V_{I\!F}, V_b) \right|}{d^2 V_b} > 0$$

where

the  $V_b$  that is obtained through calculation can make a value of  $|f_{Lo}|$  minimum. The  $|f_{Lo}|$  is minimum, that is, the local oscillation current is minimum. If a voltage value of an external direct current bias voltage source is set to the foregoing  $V_b$  that is obtained through calculation, suppression of the local oscillation leakage in the frequency mixing circuit can be implemented.

**[0030]** With the frequency mixing circuit provided in this embodiment, a direct current bias circuit that is simpler and is easier to be implemented is disposed; when a voltage value of a direct current bias voltage source changes, a value of a local oscillation current also changes correspondingly; and when the voltage value of the direct current bias voltage source is a certain specified value, the value of the local oscillation current can be reduced, thereby effectively reducing local oscillation leakage of the frequency mixing circuit.

[0031] As an implementation manner of this embodi-

ment, the frequency mixing circuit provided in this embodiment is also applicable to a case where a radio frequency signal is mixed with a local oscillation signal to output an intermediate frequency signal.

**[0032]** As another implementation manner of this embodiment, the direct current bias circuit 1 may also be disposed on a local oscillation signal side or a radio frequency signal side.

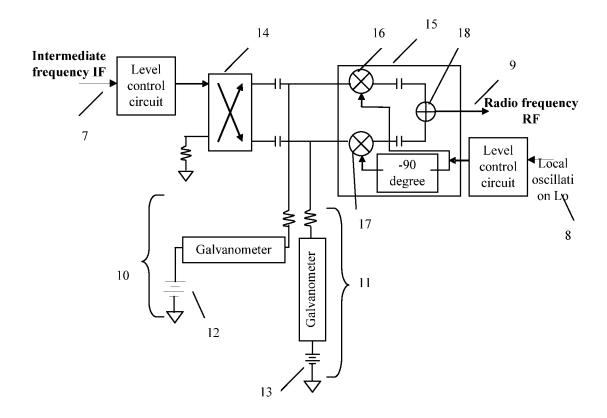

[0033] As an improvement to this embodiment, an embodiment of the present invention provides another frequency mixing circuit. As shown in FIG. 7, the frequency mixing circuit may include an intermediate frequency inputting port 7 used for inputting an intermediate frequency (IF, Intermediate Frequency) signal, a local oscillation inputting port 8 used for inputting a local oscillation (Lo, Local Oscillation) signal, and a radio frequency outputting port 9 used for outputting a radio frequency (RF, Radio Frequency) signal.

[0034] A first direct current bias circuit 10 and a second direct current bias circuit 11 are disposed on the side of the intermediate frequency inputting port 7, where the first direct current bias circuit 10 includes a direct current bias voltage source 12 that is used for reducing a local oscillation current and is marked as **Vb1**, and the second direct current bias circuit 11 includes a direct current bias voltage source 13 that is used for reducing the local oscillation current and is marked as **Vb2**.

**[0035]** Because two direct current bias circuits are disposed, a problem of local oscillation leakage in the frequency mixing circuit can be effectively solved.

**[0036]** The frequency mixing circuit further includes: a 90-degree bridge 14 and an orthogonal frequency mixer 15, where the orthogonal frequency mixer 15 includes a first frequency mixing unit circuit 16, a second frequency mixing unit circuit 17, and a combiner 18.

[0037] An input signal passes through the 90-degree bridge 14 to generate a first input signal and a second input signal, where the first input signal and the second input signal are transferred to the first frequency mixing unit circuit 16 and the second frequency mixing unit circuit 17 of the orthogonal frequency mixer 15, respectively; and each of the first input signal and the second input signal is mixed with a local oscillation signal, and an output signal is generated after the mixed signals pass through the combiner 18.

[0038] The frequency mixing circuit in this embodiment is applicable to a manner for implementing frequency mixing by using a field effect transistor FET shown in FIG. 4, and is also applicable to a manner for implementing frequency mixing by using a diode shown in FIG. 5.

[0039] The field effect transistor FET may be equivalent to a nonlinear resistor. A principle of the frequency mixing circuit shown in FIG. 3 is analyzed in the following,

**[0040]** It is assumed that a relation between a voltage and a current across a nonlinear resistor satisfies the following relation:

as shown in FIG. 6.

$$I = \sum_{n=1}^{n=k} a_n V^n, \quad k \le 7$$

(1),

where I represents a current across the nonlinear resistor, V represents a voltage across the nonlinear resistor, and  $a_n$  represents a coefficient that indicates a device feature. A total loop voltage source

$$Va = V_{Lo} * \cos w_{Lo}t + V_{IF} * \cos w_{IF}t + Vb$$

(2),

where Va represents a voltage value of the total loop voltage source,  $V_{Lo}^* cosw_{Lo}t$  represents a voltage value of a local oscillation voltage source,  $V_{IF}^* cosw_{IF}t$  represents a voltage value of an intermediate frequency voltage source, and Vb represents a voltage value of a direct current bias voltage source.

**[0041]** Current values generated by the local oscillation voltage source, the intermediate frequency voltage source, and the direct current bias voltage source may be obtained by substituting formula (2) to formula (1).

**[0042]** A current value generated by the direct current bias voltage source is:  $I_{dc} = f_{dc}(a_1, a_2, ..., a_k, V_{Lo}, V_{IF}, V_b)$ , where  $I_{dc}$  represents the current value generated by the direct current bias voltage source, and  $a_1, a_2, ..., a_k$  represent coefficients of voltages across the nonlinear resistor in formula (1).

**[0043]** A current generated by the local oscillation voltage source is:  $I_{Lo} = f_{Lo}(a_1, a_2, ..., a_k, V_{Lo}, V_{IF}, V_b)$ ,

**[0044]** Multiple voltage values  $V_b$  are set for the bias voltage source, and  $I_{dc}$  that corresponds to each voltage value  $V_b$  may be obtained through measurement. In combination with constants  $V_{Lo}$  and  $V_{IF}$ , the coefficient  $a_n$  in the expression of the nonlinear resistor may be obtained by using a data-fitting method.

**[0045]** The obtained coefficient  $a_n$  in the expression of the nonlinear resistor is substituted to  $f_{Lo}(a_1, a_2, ..., a_k, V_{Lo}, V_{IF}, V_b)$ .

**[0046]** A value of  $V_b$  is calculated according to formulas

$$\frac{d \mid f_{Lo}(a_1, a_2, \dots, a_k, V_{Lo}, V_{IF}, V_b) \mid}{dV_b} = 0 \qquad \text{and} \qquad$$

$$\frac{d^2 \left| f_{Lo}(a_1, a_2, \ldots, a_k, V_{Lo}, V_{I\!F}, V_b) \right|}{d^2 V_b} > 0 \quad \text{where the}$$

$V_b$  that is obtained through calculation can make a value of  $|f_{Lo}|$  minimum. The  $|f_{Lo}|$  is minimum, that is, a local oscillation current is minimum. If an external direct current bias is set to the foregoing  $V_b$  that is obtained through calculation, suppression of the local oscillation leakage

in the frequency mixing circuit can be implemented.

[0047] With the frequency mixing circuit provided in this embodiment, a direct current bias circuit that is simpler and is easier to be implemented is disposed; when a voltage value of a bias voltage source of the direct current bias circuit changes, a value of a local oscillation current also changes correspondingly; and when the voltage value of the direct current bias voltage source is a certain specified value, the value of the local oscillation current can be reduced, thereby effectively reducing local oscillation leakage of the frequency mixing circuit.

**[0048]** The frequency mixing circuit is implemented by adopting the foregoing implementation manner, and suppression of an image frequency is implemented by adopting an orthogonal phase cancellation technology, so that single-sideband up conversion may be implemented.

**[0049]** As an improvement to this embodiment, to make input power of an intermediate frequency port and input power of a local oscillation port of the frequency mixing circuit to be constants, as shown in FIG. 7, a level control circuit may further be disposed at each of the intermediate frequency port and the local oscillation port of the frequency mixing circuit, where output power of the level control circuit is a constant.

**[0050]** The foregoing solution can make the input power of the intermediate frequency port and the input power of the local oscillation port of the frequency mixing circuit to be constants, thereby making a value of  $V_{Lo}$  and a value of  $V_{IF}$  to be constants.

**[0051]** To facilitate measurement, as another improvement to this embodiment, the direct current bias circuit may further include a galvanometer used for measuring a bias current of the direct current bias circuit, as shown in FIG. 7.

**[0052]** Temperature drift may cause change of an internal junction potential of a device, which is equivalent to that an additional voltage source that drifts with temperature is added to Vb. The voltage source is set to Voffset. If an offset voltage at normal temperature is maintained in a high or low temperature environment, an actual equivalent bias voltage is Vb+Voffset, which may affect the effect of suppressing local oscillation leakage in the case of temperature drift.

**[0053]** Because a relation among a direct current bias current I, a direct current bias voltage Vb, and a local oscillation current Ilo remains unchanged while Vb is a variable, only if I is constant, the local oscillation current can be stable, and the effect of suppressing local oscillation leakage can remain unchanged.

[0054] As shown in FIG. 7, the frequency mixing circuit includes two direct current bias circuits provided in the foregoing embodiment, which are marked as a first direct current bias circuit and a second direct current bias circuit. A bias voltage source in the first direct current bias circuit is marked as Vb1, and a bias voltage source in the second direct current bias circuit is marked as Vb2. Values of direct current bias currents of the first direct current bias circuit and the second direct current bias

25

35

45

50

circuit at normal temperature are recorded as  $I1_{normal}$  and  $I2_{normal}$ . When temperature deviates from the normal temperature, that is, the temperature becomes high or low, direct current bias voltages Vb1 and Vb2 are adjusted, and differences between currents actually measured in cases of high and low temperature and direct current bias currents at the normal temperature, that is, a difference between I1 and  $I1_{normal}$  and a difference between I2 and  $I2_{normal}$  are negatively fed back to drive the direct current bias voltages Vb1 and Vb2, so that the impact imposed on the effect of suppressing local oscillation leakage due to the change of high or low temperature is reduced.

**[0055]** It is assumed that a time step of an adjustment interval is u, u, that is, a coefficient updating step, may be preset as required, an error of a direct current bias current is *error*, and an expression of the error of the direct current bias circuit may be:

$$error = I - I_{normal}$$

(4).

**[0056]** A feedback iterative formula of a direct current bias voltage is:

$$V_b(n) = V_b(n-1) + u * error$$

(5).

**[0057]** That is,  $V_b(n)=V_b(n-1)+u^*(I-I_{normal})$ , where  $V_b$  (n) represents a voltage value of the direct current bias voltage source in an  $n^{th}$  time period,  $V_b(n-1)$  represents a voltage value of the direct current bias voltage source in an  $(n-1)^{th}$  time period, u represents a coefficient updating step, I represents a bias current value measured in the  $n^{th}$  time period, and  $I_{normal}$  represents a bias current reference value.

**[0058]** As a preferred implementation manner of this embodiment, one capacitor may further be disposed between the 90-degree bridge and the first frequency mixing unit circuit, one capacitor may further be disposed between the 90-degree bridge and the second frequency mixing unit circuit, one capacitor may further be disposed between the first frequency mixing unit circuit and the combiner, and one capacitor may further be disposed between the second frequency mixing unit circuit and the combiner.

**[0059]** Coupling of direct currents between the first frequency mixing unit circuit and the second frequency mixing unit circuit that are orthogonal is avoided by using a feature that the capacitor can block a direct current.

**[0060]** To better suppress local oscillation leakage of the frequency mixing circuit, the first frequency mixing unit circuit and the second frequency mixing unit circuit may also be frequency mixers having the same resistivity.

[0061] The frequency mixing circuit in this embodiment

may also be equivalent to the circuit shown in FIG. 6, and therefore, a value of a local oscillation current can be reduced, thereby effectively reducing the local oscillation leakage of the frequency mixing circuit.

**[0062]** With the frequency mixing circuit provided in this embodiment of the present invention, that a microwave filter is used at an outputting port of an up converter is avoided, and the difficulty of implementation is lowered, so that a frequency mixer may be monolithically integrated with another device. Furthermore, in the solution of this embodiment of the present invention, a device with better frequency selectivity is not used, thereby improving the frequency extension capability of the up converter.

**[0063]** An embodiment of the present invention provides a method for suppressing local oscillation leakage in a frequency mixing circuit, where the frequency mixing circuit includes a direct current bias circuit, and as shown in FIG. 8, the method includes the following steps:

[0064] 801: Calculate a value of  $V_b$  by using a computer program according to formulas

$$rac{d \mid f_{Lo}(a_1, a_2, ..., a_k, V_{Lo}, V_{IF}, V_b) \mid}{dV_b} = 0$$

and

$$\frac{d^2 \left| f_{Lo}(a_1, a_2, \dots, a_k, V_{Lo}, V_{I\!F}, V_b) \right|}{d^2 V_b} > 0 \qquad \text{where}$$

$V_b$  represents a voltage value of a direct current bias voltage source,  $a_1, a_2, ..., a_k$  represent coefficients of voltage values in a relation between a current and a voltage across a nonlinear resistor, k represents a non-zero natural number,  $V_{LO}$  represents a voltage value of a local oscillation voltage source,  $V_{IF}$  represents a voltage value of an intermediate frequency voltage source, and  $|f_{LO}|$  represents a value of a local oscillation current.

**[0065]** 802: Set a voltage value of a voltage source of the direct current bias circuit to  $V_b$  by using a computer program.

**[0066]** With the method for suppressing local oscillation leakage in a frequency mixing circuit provided in this embodiment, a direct current bias circuit that is simpler and is easier to be implemented is disposed in the frequency mixing circuit; when a voltage value of a bias voltage source of the direct current bias circuit changes, a value of a local oscillation current also changes correspondingly; and when the voltage value of the direct current bias voltage source is a certain specified value, the value of the local oscillation current can be reduced, thereby effectively reducing local oscillation leakage of the frequency mixing circuit.

**[0067]** As an improvement to this embodiment, an embodiment of the present invention provides another method for suppressing local oscillation leakage in a frequency mixing circuit, where the frequency mixing circuit includes a direct current bias circuit, and as shown in FIG.

9, the method includes the following steps:

**[0068]** The frequency mixing circuit in this embodiment is applicable to a manner for implementing frequency mixing by using a field effect transistor FET, and is also applicable to a manner for implementing frequency mixing by using a diode.

**[0069]** The field effect transistor FET may be equivalent to a nonlinear resistor.

**[0070]** 901: Calculate a formula for calculating a value of a local oscillation current, where only the voltage value  $V_b$  of a direct current bias voltage source in the formula is a variable, that is, Calculate  $I_{Lo} = f_{Lo}(a_1, a_2, ..., a_k, V_{Lo}, V_{IF}, V_b)$ .

**[0071]** It is assumed that a relation between a voltage and a current across the nonlinear resistor satisfies the following relation:

$$I = \sum_{n=1}^{n=k} a_n V^n, \quad k \le 7$$

(1),

where I represents a current across the nonlinear resistor, V represents a voltage across the nonlinear resistor, and  $a_n$  represents a preset coefficient.

[0072] A total loop voltage source

$$Va = V_{Lo} * \cos w_{Lo}t + V_{IF} * \cos w_{IF}t + Vb$$

(2).

where  $V_a$  represents a voltage value of the total loop voltage source,  $V_{Lo}^* cos w_{Lo} t$  represents a voltage value of a local oscillation voltage source,  $V_{IF}^* cos w_{IF} t$  represents a voltage value of an intermediate frequency voltage source, and Vb represents a voltage value of a direct current bias voltage source.

**[0073]** Current values generated by the local oscillation voltage source, the intermediate frequency voltage source, and the direct current bias voltage source may be obtained by substituting formula (2) to formula (1).

**[0074]** A current value generated by the direct current bias voltage source is:  $I_{dc} = f_{dc}(a_1, a_2, ..., a_k, V_{Lo}, V_{IF}, V_b)$ , where  $I_{dc}$  represents the current value generated by the direct current bias voltage source, and  $a_1, a_2, ..., a_k$  represent coefficients of voltages across the nonlinear resistor in formula (1).

**[0075]** A current generated by the local oscillation voltage source is:  $I_{LO} = f_{LO}(a_1, a_2, ..., a_k, V_{LO}, V_{IF}, V_b)$ .

**[0076]** Multiple voltage values  $V_b$  are set for the bias voltage source, and  $I_{dc}$ ,  $V_{Lo}$ , and  $V_{IF}$  that correspond to each voltage value  $V_b$  may be obtained through measurement. The coefficient  $a_n$  in the expression of the nonlinear resistor may be obtained by using a data-fitting method.

[0077] The formula for calculating the value of the local

oscillation current  $I_{Lo} = f_{Lo}(a_1, a_2, ..., a_k, V_{Lo}, V_{IF}, V_b)$  may be obtained by substituting the obtained coefficient  $a_n$  in the expression of the nonlinear resistor to  $f_{Lo}(a_1, a_2, ..., a_k, V_{Lo}, V_{IF}, V_b)$ . Only the voltage value  $V_b$  of the direct current bias voltage source in the formula is a variable.

[0078] 902: Calculate a value of  $V_b$  according to

formulas ,

$$\frac{d \mid f_{Lo}(a_{1},a_{2},...,a_{k},V_{Lo},V_{I\!F},V_{b}) \mid}{dV_{b}} = 0$$

and

$$\frac{d^2 \left| f_{Lo}(a_1, a_2, ..., a_k, V_{Lo}, V_{I\!F}, V_b) \right|}{d^2 V_b} > 0$$

where  $V_b$  represents the voltage value of the direct current bias voltage source,  $a_1, a_2, ..., a_k$  represent coefficients of voltage values in a relation between a current and a voltage across the nonlinear resistor, k represents a non-zero natural number,  $V_{Lo}$  represents the voltage value of the local oscillation voltage source,  $V_{IF}$  represents the voltage value of the intermediate frequency voltage source, and  $f_{Lo}(a_1, a_2, ..., a_k, V_{Lo}, V_{IF}, V_b)$  represents the value of the local oscillation current.

**[0079]** This step may be implemented by using a computer program, a manual manner, or a single-chip microcomputer.

**[0080]** 903: Record a bias current value  $I_{normal}$  when the voltage value of the voltage source of the direct current bias circuit is set to  $V_b$ .

**[0081]** 904: Obtain a bias current value *I* of the direct current bias circuit in a current time period.

**[0082]** 905: Calculate  $V_b(n) = V_b(n-1) + u^*(I-I_{nomal})$ , where  $V_b(n)$  represents a voltage value of the direct current bias voltage source in an  $n^{th}$  time period,  $V_b(n-1)$  represents a voltage value of the direct current bias voltage source in an  $(n-1)^{th}$  time period, u represents a coefficient updating step, I represents a bias current value measured in the  $n^{th}$  time period, and  $I_{normal}$  represents a bias current reference value.

**[0083]** 906: Reset the voltage value of the bias voltage source of the direct current bias circuit in the current time period to  $V_b(n)$ .

[0084] With the method for suppressing local oscillation leakage in a frequency mixing circuit provided in this embodiment, a direct current bias circuit that is simpler and is easier to be implemented is disposed in the frequency mixing circuit; when a voltage value of a bias voltage source of the direct current bias circuit changes, a value of a local oscillation current also changes correspondingly; and when the voltage value of the direct current bias voltage source is a certain specified value, the value of the local oscillation current can be reduced, thereby effectively reducing local oscillation leakage of the frequency mixing circuit.

**[0085]** Through the foregoing description of the embodiments, persons skilled in the art may clearly understand that the present invention may be implemented by

45

50

15

20

25

30

35

40

45

software plus necessary universal hardware, and definitely may also be implemented by hardware, but in many cases, the software implementation manner is preferred. Based on such understanding, the technical solutions of the present invention essentially, or the part contributing to the prior art may be implemented in the form of a software product. The computer software product is stored in a readable storage medium, for example, a floppy disk, a hard disk, or an optical disk of a computer, and includes several instructions for instructing a computer device (which may be a personal computer, a server, a network device, and so on) to execute the methods described in the embodiments of the present invention.

**[0086]** The foregoing description is merely about exemplary embodiments of the present invention, but is not intended to limit the protection scope of the present invention. Any variation or replacement readily figured out by persons skilled in the art within the technical scope disclosed in the present invention shall all fall within the protection scope of the present invention. Therefore, the protection scope of the present invention shall be subject to the protection scope of the appended claims.

#### **Claims**

- A frequency mixing circuit, comprising: a direct current bias circuit, wherein the direct current bias circuit comprises a direct current bias voltage source used for reducing a local oscillation current.

- 2. The frequency mixing circuit according to claim 1, wherein a voltage value of the direct current bias voltage source is obtained through calculation according to formulas

$$\frac{d |f_{Lo}(a_1, a_2, \dots, a_k, V_{Lo}, V_{IF}, V_b)|}{dV_b} = 0 \quad \text{and} \quad$$

$$\frac{d^{2}\left|f_{Lo}(a_{1}, a_{2}, \dots, a_{k}, V_{Lo}, V_{IF}, V_{b})\right|}{d^{2}V_{b}} > 0$$

wherein  $V_b$  represents the voltage value of the direct current bias voltage source,  $a_1, a_2, ..., a_k$  represent coefficients of voltage values in a relation between a current and a voltage across a nonlinear resistor, k represents a non-zero natural number,  $V_{Lo}$  represents a voltage value of a local oscillation voltage source,  $V_{IF}$  represents a voltage value of an intermediate frequency voltage source, and  $f_{Lo}(a_1, a_2, ..., a_k, V_{Lo}, V_{IF}, V_b)$  represents a value of a local oscillation current.

3. The frequency mixing circuit according to claim 1, wherein the frequency mixing circuit further comprises an intermediate frequency inputting port, a local oscillation inputting port, and a radio frequency outputting port; and the direct current bias circuit is disposed at the intermediate frequency inputting port side, or the local oscillation inputting port side, or the radio frequency outputting port side.

- The frequency mixing circuit according to any one of claims 1 to 3, wherein the frequency mixing circuit further comprises: a 90-degree bridge and an orthogonal frequency mixer, wherein the orthogonal frequency mixer comprises a first frequency mixing unit circuit, a second frequency mixing unit circuit, and a combiner; and an input signal passes through the 90-degree bridge to generate a first input signal and a second input signal, wherein the first input signal and the second input signal are transferred to the first frequency mixing unit circuit and the second frequency mixing unit circuit of the orthogonal frequency mixer, respectively; and each of the first input signal and the second input signal is mixed with a local oscillation signal in the first frequency mixing unit circuit and the second frequency mixing unit circuit, and an output signal is generated after mixed signals pass through the combiner.

- 5. The frequency mixing circuit according to claim 4, wherein one direct current bias circuit is disposed at an intermediate frequency inputting port of the first frequency mixing unit circuit and one direct current bias circuit is disposed at an intermediate frequency inputting port of the second frequency mixing circuit.

- 6. The frequency mixing circuit according to claim 5, wherein a level control circuit is disposed at each of an intermediate frequency port and a local oscillation port of the frequency mixing circuit, the level control circuit is used to make input power of the intermediate frequency port and input power of the local oscillation port of the frequency mixing circuit to be constants.

- 7. The frequency mixing circuit according to claim 6, wherein the direct current bias circuit further comprises a galvanometer used for measuring a bias current of the direct current bias circuit.

- **8.** The frequency mixing circuit according to claim 1, wherein a voltage value of the direct current bias voltage source  $V_b(n) = V_b(n-1) + u^*(I-I_{normal})$ , wherein  $V_b(n)$  represents a voltage value of the direct current bias voltage source in an  $n^{th}$  time period,  $V_b(n-1)$  represents a voltage value of the direct current bias voltage source in an  $(n-1)^{th}$  time period, u represents a coefficient updating step, I represents a bias current value measured in the  $n^{th}$  time period, and  $I_{normal}$  represents a bias current reference value.

- 9. The frequency mixing circuit according to claim 4,

55

25

30

40

45

50

55

wherein one capacitor is disposed between the 90-degree bridge and the first frequency mixing unit circuit, one capacitor is disposed between the 90-degree bridge and the second frequency mixing unit circuit, one capacitor is disposed between the first frequency mixing unit circuit and the combiner, and one capacitor is disposed between the second frequency mixing unit circuit and the combiner.

- **10.** The frequency mixing circuit according to claim 4, wherein the first frequency mixing unit circuit and the second frequency mixing unit circuit are frequency mixers having same resistivity.

- 11. A method for suppressing local oscillation leakage in a frequency mixing circuit, wherein the frequency mixing circuit comprises a direct current bias circuit, and the method comprises the following steps:

calculating a value of  $V_h$  according to formulas

$$\frac{d | f_{Lo}(a_1, a_2, \dots, a_k, V_{Lo}, V_{IF}, V_b)|}{dV_b} = 0$$

and

$$\frac{d^2 \left| f_{Lo}(a_1, a_2, \dots, a_k, V_{Lo}, V_{IF}, V_b) \right|}{d^2 V_b} > 0$$

wherein  $V_b$  represents a voltage value of a direct current bias voltage source,  $a_1, a_2, ..., a_k$  represent coefficients of voltage values in a relation between a current and a voltage across a nonlinear resistor, k represents a non-zero natural number,  $V_{Lo}$  represents a voltage value of a local oscillation voltage source,  $V_{IF}$  represents a voltage value of an intermediate frequency voltage source, and  $f_{Lo}(a_1, a_2, ..., a_k, V_{Lo}, V_{IF}, V_b)$  represents a value of a local oscillation current; and setting a voltage value of a voltage source of the direct current bias circuit to  $V_b$ .

**12.** The method for suppressing local oscillation leakage in a frequency mixing circuit according to claim 11, wherein the method further comprises:

recording a bias current value  $I_{normal}$  when the voltage value of the voltage source of the direct current bias circuit is set to  $V_b$ ; obtaining a bias current value I of the direct current bias circuit in a current time period; calculating  $V_b(n) = V_b(n-1) + u^*(I-I_{normal})$ , wherein  $V_b(n)$  represents a voltage value of the direct current bias voltage source in an  $n^{th}$  time period,  $V_b(n-1)$  represents a voltage value of the direct current bias voltage source in an  $(n-1)^{th}$  time period.

riod, u represents a coefficient updating step, I represents a bias current value measured in the n<sup>th</sup> time period, and  $I_{normal}$  represents a bias current reference value; and setting the voltage value of the bias voltage source of the direct current bias circuit in the current time period to  $V_b(n)$ .

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

#### EP 2 685 629 A1

#### INTERNATIONAL SEARCH REPORT

International application No.

PCT/CN2012/072243

#### A. CLASSIFICATION OF SUBJECT MATTER

H03D 7/18 (2006.01) i

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC: H03D; H04B

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

CNPAT: CNKI: VEN: frequency conversion, local oscillator, intermediate frequency, mix+, bias, offset+, LO, local, oscillat+, reduc+, suppress+, limit+, leak+, send+, transmit+, IF, intermediate, frequency

#### C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category*                                                                               | Citation of document, with indication, where appropriate, of the relevant passages                                                                  | Relevant to claim No. |  |  |  |  |  |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|--|--|

| Y                                                                                       | EP 0528848 B1 (NORTHERN TELECOM LTD.), 19 January 1994 (19.01.1994), see description, column 3, line 32 to column 5, line 32, claim 1, and figure 1 | 1, 3-7, 9-10          |  |  |  |  |  |

| Y                                                                                       | CN 201113924 Y (CHENGDU HONGMING ELECTRONICS CO., LTD.), 10 September 2008 (10.09.2008), see description, page 3, lines 13-14, and abstract         | 1, 3-7, 9-10          |  |  |  |  |  |

| A                                                                                       | CN 101202533 A (FUDAN UNIVERSITY), 18 June 2008 (18.06.2008), see the whole document                                                                | 1-12                  |  |  |  |  |  |

| A                                                                                       | CN 101345537 A (ORISIL TECHNOLOGY INC.), 14 January 2009 (14.01.2009), see the whole document                                                       | 1-12                  |  |  |  |  |  |

| ☐ Further documents are listed in the continuation of Box C. ☐ See patent family annex. |                                                                                                                                                     |                       |  |  |  |  |  |

| k  | Special categories of cited documents:                      | "T" | later document published after the international filing date        |

|----|-------------------------------------------------------------|-----|---------------------------------------------------------------------|

|    | •                                                           |     | or priority date and not in conflict with the application but       |

| ۷" | document defining the general state of the art which is not |     | sited to an donaton d the main ainle on the cours an donly in a the |

"A' considered to be of particular relevance

"E" earlier application or patent but published on or after the international filing date

"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

"O" document referring to an oral disclosure, use, exhibition or

document published prior to the international filing date but later than the priority date claimed

cited to understand the principle or theory underlying the invention

document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

Date of mailing of the international search report Date of the actual completion of the international search 14 June 2012 (14.06.2012) 18 May 2012 (18.05.2012)

Name and mailing address of the ISA/CN: State Intellectual Property Office of the P. R. China No. 6, Xitucheng Road, Jimenqiao Haidian District, Beijing 100088, China Facsimile No.: (86-10) 62019451

Authorized officer

DONG, Xin

Telephone No.: (86-10) 62411860

Form PCT/ISA/210 (second sheet) (July 2009)

# EP 2 685 629 A1

# INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No.

| Information on patent family members    |                        | 1             | incinational a | photon ivo.      |

|-----------------------------------------|------------------------|---------------|----------------|------------------|

| 2011012012                              | on parent many memoris |               | PCT            | C/CN2012/072243  |

| ratent Documents referred in the Report | Publication Date       | Patent Family |                | Publication Date |

| EP 0528848 B1                           | 19.01.1994             | US 5033110 A  |                | 16.07.1991       |

|                                         |                        | WO 9118445 A  |                | 28.11.1991       |

|                                         |                        | JPH 05502358  | A              | 22.04.1993       |

|                                         |                        | EP 0528848 A1 |                | 03.03.1993       |

|                                         |                        | DE 69101063 I | Ξ              | 03.03.1994       |

|                                         |                        | CA 2069104 C  |                | 08.11.1994       |

| CN 201113924 Y                          | 10.09.2008             | None          |                |                  |

| CN 101202533 A                          | 18.06.2008             | None          |                |                  |

| CN 101345537 A                          | 14.01.2009             | None          |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

|                                         |                        |               |                |                  |

Form PCT/ISA/210 (patent family annex) (July 2009)

# EP 2 685 629 A1

### REFERENCES CITED IN THE DESCRIPTION

This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.

# Patent documents cited in the description

• CN 201110083379 [0001]