(19)

## (12) CORRECTED EUROPEAN PATENT APPLICATION

(15) Correction information:

Corrected version no 1 (W1 A1) Corrections, see

Bibliography INID code(s) 22

(48) Corrigendum issued on:

30.04.2014 Bulletin 2014/18

(43) Date of publication:

05.03.2014 Bulletin 2014/10

(21) Application number: 13179559.3

(22) Date of filing: 07.08.2013

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

Designated Extension States:

**BA ME**

(30) Priority: 27.08.2012 US 201213595282

(27) Previously filed application:

27.08.2012 US 201213595282

(71) Applicant: Freescale Semiconductor, Inc. Austin, TX 78735 (US)

(51) Int Cl.:

G06F 11/10 (2006.01)

G11C 11/00 (2006.01)

- (72) Inventors:

- Cunningham, Jeffrey C. Austin, TX 78739 (US)

- Gasquet, Horatio P. Austin, TX 78735 (US)

- Scouller, Ross S. Austin, TX 78737 (US)

- Cabassi, Marco A. Austin, TX 78703 (US)

- (74) Representative: Ferro, Frodo Nunes

Optimus Patent Limited

Grove House, Lutyens Close

Chineham Court

Basingstoke, Hampshire RG24 8AG (GB)

## (54) Adaptive error correction for non-volatile memories

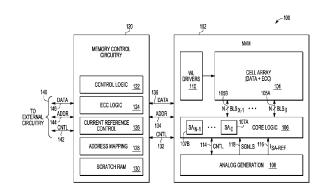

Methods and systems are disclosed for adaptive (57)error correction for non-volatile memories that dynamically adjust sense amplifier read detection windows. Memory control circuitry (120) uses error correction code (ECC) routines (124) to detect bit errors that are noncorrectable using these ECC routines. The memory control circuitry (120) then dynamically adjusts sense amplifier read detection windows (312) to allow for correct data to be determined. Corrected data can then be output to external circuitry. The corrected data can also be stored for later access when subsequent read operations attempt to access address locations that previously suffered bit failures. The disclosed methods and systems can also be used with respect to memories that are not non-volatile memories.

FIG. 1

EP 2 704 012 A8