(12)

(11)

EP 2 744 306 A1

## EUROPEAN PATENT APPLICATION

(43) Date of publication:

18.06.2014 Bulletin 2014/25

(51) Int Cl.:

**H05B 41/392** (2006.01)      **H05B 41/282** (2006.01)

(21) Application number: 13197196.2

(22) Date of filing: 13.12.2013

(84) Designated Contracting States:

**AL AT BE BG CH CY CZ DE DK EE ES FI FR GB

GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO

PL PT RO RS SE SI SK SM TR**

Designated Extension States:

**BA ME**

(30) Priority: 17.12.2012 IT BO20120672

(71) Applicant: **Schneider Electric Industrie Italia S.p.A.**

**02100 Rieti, Località Vazia (IT)**

(72) Inventor: **Bonzagni, Paolo**

**44042 CENTO FE (IT)**

(74) Representative: **Modiano, Micaela Nadia**

**Modiano & Partners (IT)**

**Via Meravigli, 16**

**20123 Milano (IT)**

### (54) Power supply oscillator circuit for light sources and other equivalent electrical user devices

(57) A power supply oscillator circuit (1) for light sources and other equivalent electrical user devices of the type comprising at least one capacitor (19) interposed between a direct-current power supply source (2) and an output transformer (3), two transistors (11, 12) being interposed between the direct-current power supply source (2) and the capacitor (19) and having their corresponding control pole (10, 9) connected to a respective, and different, branch (8, 7) that originates from the high electrical potential terminal of the power supply source (2), the corresponding high-level output pole (16, 15) connected to a respective, and different, terminal of the capacitor (19) and the corresponding low-level output poles (18, 17) connected to the ground, along the branches (7, 8) there being at least one respective resistor (14, 13) that is connected upstream, with the interposition of a switch (6), to the high electrical potential terminal of the power supply source (2), characterized in that it comprises a control

and management unit (22), which is interposed between the switch (6) and the branches (8, 7) provided with at least one respective resistor (14, 13), the unit (22) having at least one input terminal connected downstream to the line (5) affected by the switch (6) and at least two output terminals associated with the branches (8, 7) provided with at least one resistor (14, 13), the signal on the output terminals of the unit (22) being synchronized with the natural frequency of the circuit

$$f_0 = \frac{1}{2 \pi \sqrt{LC}}$$

where C is the value of the capacitance of the capacitor and L is the value of the inductance of the transformer (3).

Fig. 4

## Description

**[0001]** The present invention relates to a power supply oscillator circuit for light sources and other equivalent electrical user devices: the oscillator circuit according to the invention is particularly suitable and efficient for the supply of power to emergency light sources.

**[0002]** An important example of an oscillating circuit is the so-called RLC circuit (in relation to the electrical components that are present therein): such circuit is defined by a natural oscillation frequency  $f_0$ . In practice, such circuit is capable of generating an oscillating current in response to an external impulse, such as the rapid closing and opening of the switch.

**[0003]** The natural frequency  $f_0$  constitutes the resonance of the circuit, i.e., the circuit is capable of absorbing the maximum amount of energy from an external alternating voltage generator E when the voltage provided by the generator oscillates at a frequency that is very close to  $f_0$ .

**[0004]** When the system is balanced, no current circulates.

**[0005]** When charge accumulates at a terminal of the capacitor, the potential difference tends to redistribute the charge within the circuit: this generates a current.

**[0006]** The higher the charge accumulated on the capacitor C, the greater the potential difference across the circuit (capacitor property).

**[0007]** The charges of the circuit, subject to a potential difference, accelerate toward the balance condition.

**[0008]** Once the balance point has been reached, the current continues to flow in the circuit by inertia and the charge begins to accumulate on the other terminal of the capacitor.

**[0009]** After some time, the potential difference balances the accumulated charge. Its modulus is equal to the potential difference at the initial instant but has the opposite sign.

**[0010]** In the presence of a resistance R (potential drop proportional to the intensity of the current), the oscillations are damped exponentially over time.

**[0011]** The frequency of the free oscillations of the system (own, or natural or resonance frequency)

$$f_0 = \frac{1}{2 \pi \sqrt{LC}}$$

**[0012]** No current circulates in the circuit when the capacitor is charged to the limit of its capacitance. At this instant, the energy of the system is all electrostatic potential energy produced by the potential difference between the terminals of the capacitor.

**[0013]** The current that circulates in the circuit is instead greatest when the capacitor is discharged. At this instant, the energy of the system is all magnetic induction energy produced by the current that circulates in the in-

ductor L.

**[0014]** When, instead of leaving the circuit free to oscillate, it is forced to oscillate from the outside (by adopting for example a forcing frequency f) starting from the balance condition, the type of circuit normally termed self-oscillating is instead identified.

**[0015]** These circuits have the purpose of conveying energy that arrives from the external generator into the oscillator as a function of the value of the forcing frequency f.

**[0016]** The oscillating system reacts according to its own dynamics, i.e., over time, it stores the energy in a form that depends on its own natural frequency  $f_0$ . Since the system has its own "inertia", a certain time is in fact required for the energy to be converted from electric to magnetic and the oscillation to occur.

**[0017]** Therefore, the energy transfer from the generator to the oscillator is more effective as the frequency f of the generator (assuming that the generator that supplies the circuit is itself an electric generator of alternating values with a frequency f) approaches the natural frequency of the oscillator, because only in this manner the generator and the circuit do not hinder each other. When  $f = f_0$ , it is said that the generator and the oscillator are in resonance.

**[0018]** In this condition, the generator supplies energy to the circuit at each oscillation. In the absence of resistances, the amplitude of the oscillations would become infinite. Actually, although most of the energy of the generator is used to maintain the oscillations, a part is dissipated and the oscillations reach a finite maximum value. The effect of the resistance (in RLC resonant circuits) consists therefore in rendering the resonance less intense but also in softening the resonance condition; if the system dissipates energy, even frequencies that are not exactly identical to  $f_0$  but are comprised in an interval  $f_0 \pm \Delta f$  are in fact "in resonance".

**[0019]** When the frequency of the generator is very different from the natural frequency of the system, the action of the generator hinders the free oscillation of the circuit and the resulting oscillations are small. Most of the energy is dissipated instead of being transferred to the circuit.

**[0020]** If the current produced by the generator oscillates like a sinusoid, the current that flows through the circuit also oscillates like a sinusoid. In general, the oscillations of the system and of the energy source (the generator) do not occur with the same phase, i.e., for example, the maximum amplitude of the oscillation is not achieved in the same instant. The extent of the phase offset depends on the frequency of the oscillator.

**[0021]** The two properties of the system that determine the oscillating behavior are actually competing with each other in order to "acquire" the energy. Since the energy available at each instant is finite, when the energy is maximum in one form it must be minimum in the other form. This explains in qualitative terms why the energy must be supplied from the outside in a "targeted" manner, i.e.,

at the right moment.

**[0022]** In a circuit of this type, the generator provides a potential difference that is always of the same polarity (think of a battery that is connected and disconnected at regular intervals by means of a switch).

**[0023]** In resonance conditions ( $f=f_0$ ), the direct-current power supply source (for example a battery) is connected when the capacitor is completely charged with a polarity that matches the polarity of the terminals of the battery.

**[0024]** Whenever the capacitor is charged, an additional charge is carried by the generator and therefore the intensity of the current at the time of discharge becomes increasingly higher at each period.

**[0025]** In conditions that do not correspond to resonance ( $f$  different from  $f_0$ ), the power supply source is connected to the capacitor when it is fully charged with any polarity (i.e., independently of which of its plates is at high potential).

**[0026]** Out of every two times, the charge of the capacitor increases once and decreases once. This leads to a total charge that as a whole is smaller with respect to the resonance case.

**[0027]** With the onset of digital electronics, many of the analog oscillating circuits, such as the RLC circuit with direct-current power supply managed by a controlled switch, have been replaced by circuits based on transistors or operational amplifiers. Furthermore, the form of the oscillation used is often a square wave instead of a sinusoid.

**[0028]** Oscillation circuits of the known type are therefore suitable to provide the alternating power supply electric signal at a relatively high frequency, suitable for the power supply of different electrical user devices, receiving power from a direct-current electric power source.

**[0029]** The voltage available across the output terminals of the oscillator circuit can be calculated easily by knowing the values of the components that constitute it.

**[0030]** On the other hand, however, operations can occur in which the operating frequencies correspond to higher harmonics or to subharmonics of the desired frequency: of course, this condition compromises correct operation and provides the load connected to the output terminals of the circuit with electrical values that are not consistent with those needed to achieve the desired operation.

**[0031]** Moreover, the driving transistors are powered simultaneously, generating accordingly an irregularity of the signal that circulates in the primary winding of the output transformer (and accordingly at the output terminals).

**[0032]** Moreover, this irregularity can also be caused by the value of the winding (inductance) arranged upstream of said transistors, which, by having a fixed and predefined value, might not be suitable to tolerate some variations in the circulating electrical values.

**[0033]** It is fundamental, furthermore, to specify that the electrical values of the circulating signals depend

greatly also on the values of leakage inductance and parasitic capacitance, allowing to define with lower precision the actual voltage and current values that are available to the user device connected to the output terminals.

**5 [0034]** The aim of the present invention is to solve the problems described above, proposing a power supply oscillator circuit for light sources and other equivalent electrical user devices that avoids the simultaneous presence of a signal on the two transistors during starting.

**10 [0035]** Within this aim, an object of the invention is to propose a power supply oscillator circuit for light sources and other equivalent electrical user devices that prevents the circuit from operating at higher harmonic frequencies or at subharmonics of the desired frequency.

**15 [0036]** Another object of the invention is to propose a power supply oscillator circuit for light sources and other equivalent electrical user devices that has regular operation regardless of the variation of the electrical values that are present therein.

**20 [0037]** Another object of the invention is to propose a power supply oscillator circuit for light sources and other equivalent electrical user devices that operates independently of the parasitic parameters of said circuit.

**25 [0038]** A further object of the present invention is to provide a power supply oscillator circuit for light sources and other equivalent electrical user devices that has low costs, is relatively simple to provide in practice and is safe in application.

**30 [0039]** This aim, as well as these and other objects that will become better apparent hereinafter, are achieved by a power supply oscillator circuit for light sources and other equivalent electrical user devices of the type comprising at least one capacitor interposed between a direct-current power supply source and an output transformer, two

**35** transistors being interposed between said direct-current power supply source and said capacitor and having their corresponding control pole connected to a respective, and different, branch that originates from the high electrical potential terminal of the power supply source, the

**40** corresponding high-level output pole connected to a respective, and different, terminal of said capacitor, and the corresponding low-level output poles connected to the ground, along said branches there being at least one respective resistor that is connected upstream, with the

**45** interposition of a switch, to the high electrical potential terminal of the power supply source, characterized in that it comprises a control and management unit, which is interposed between said switch and said branches provided with at least one respective resistor, said unit having

**50** at least one input terminal connected downstream to the line affected by said switch and at least two output terminals associated with said branches provided with at least one resistor, the signal on the output terminals of said unit being synchronized with the natural frequency of the circuit

$$f_0 = \frac{1}{2 \pi \sqrt{LC}}$$

where C is the value of the capacitance of said capacitor and L is the value of the inductance of said transformer

**[0040]** This aim and these and other objects are also achieved by means of a method for the control and management of the frequency in an oscillator circuit for the power supply of light sources and other equivalent electrical user devices, of the type comprising at least one capacitor that is interposed between a direct-current power supply source and an output transformer, two transistors being interposed between said direct-current power supply source and said capacitor, their corresponding control pole being connected to a respective, and different, branch that originates from the high electrical potential terminal of the power supply source, the corresponding high-level output pole connected to a respective, and different, terminal of said capacitor, and the corresponding low-level output poles connected to the ground, along said branches that originate from the high electrical potential terminal of the power supply source there being at least one respective resistor that is connected upstream, with the interposition of a switch, to the high electrical potential terminal of the power supply source, which consists in

- setting, at the first closure of said switch, the frequency of the signal at the output terminals from a control and management unit, which is interposed between said switch and said branches provided with respective resistors, with a value that is substantially equal to the natural frequency

$$f_0 = \frac{1}{2 \pi \sqrt{LC}} ;$$

- detecting the value of the frequency f of the voltage that is present across the two terminals of said capacitor;

- comparing the value of the frequency f with the value of the natural frequency  $f_0$ ;

- increasing/decreasing the value of the frequency of the signal at the output terminals of said unit in order to modify increase/decrease the frequency f of the voltage that is present across the two terminals in order to render it substantially equal to the natural frequency  $f_0$ .

**[0041]** Further characteristics and advantages of the invention will become better apparent from the description of a preferred but not exclusive embodiment of the power supply oscillator circuit for light sources and other equivalent electrical user devices according to the invention, illustrated by way of nonlimiting example in the accompanying drawings, wherein:

5

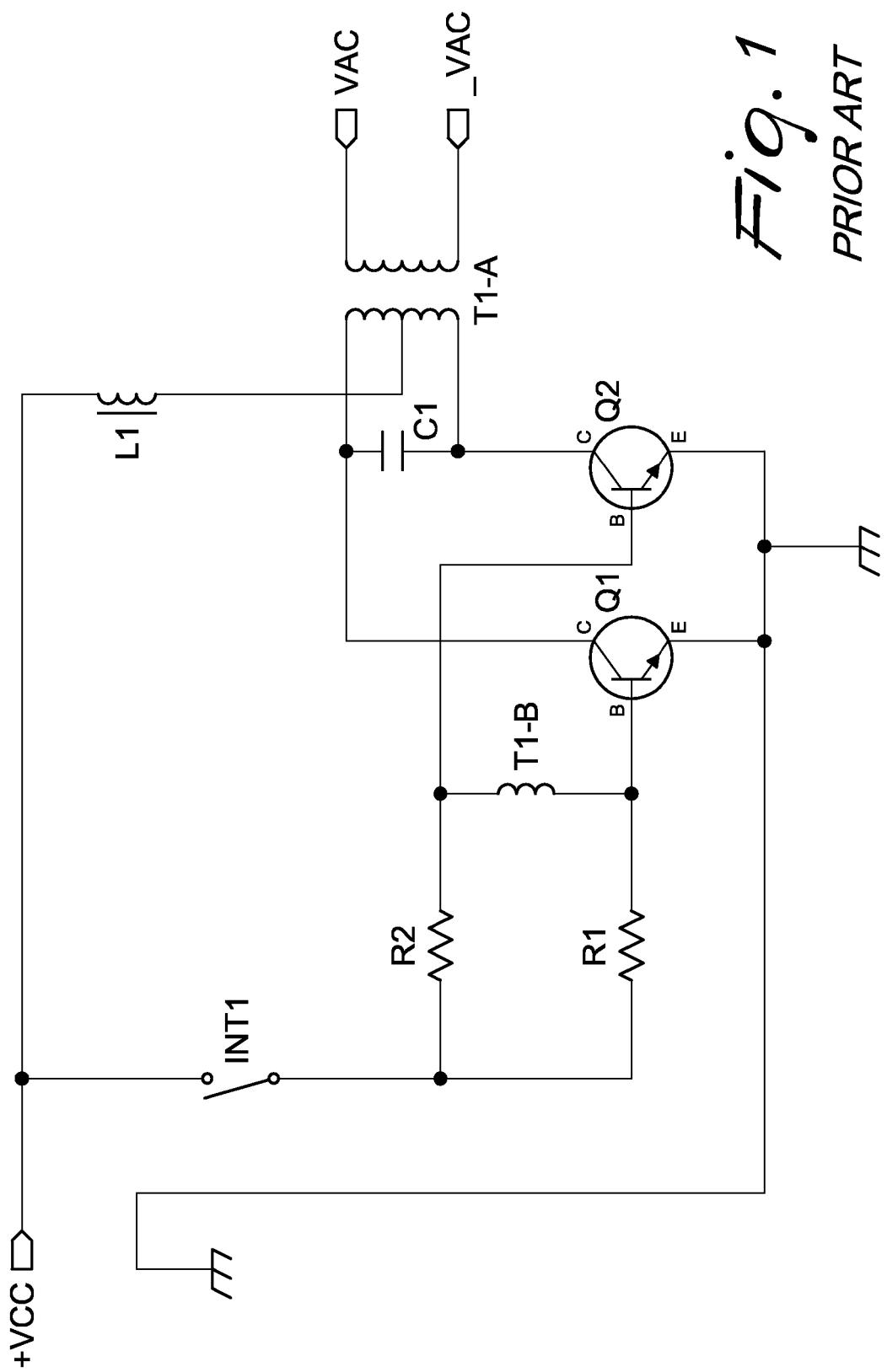

Figure 1 is a circuit diagram of a constructive solution of a known type;

10

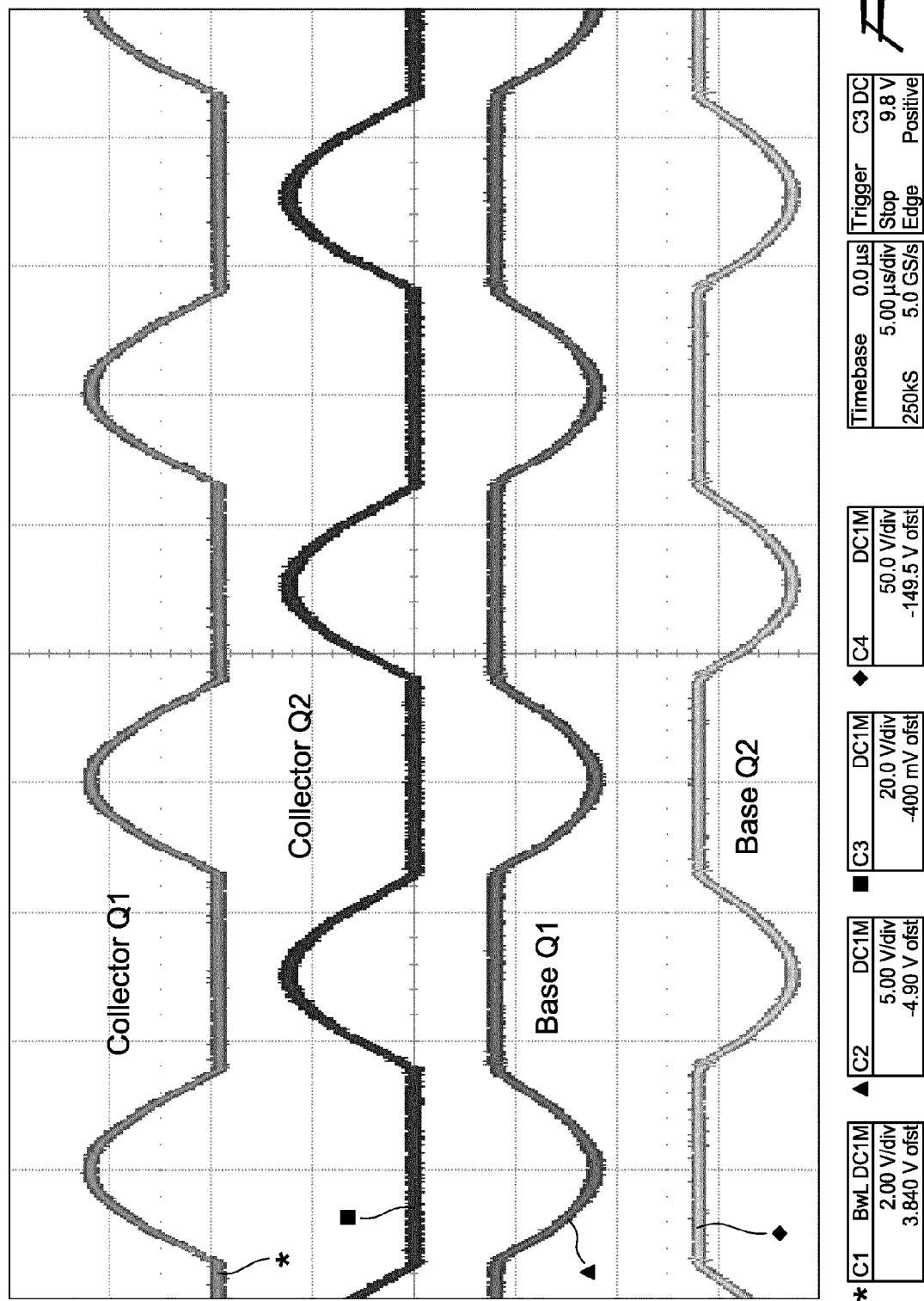

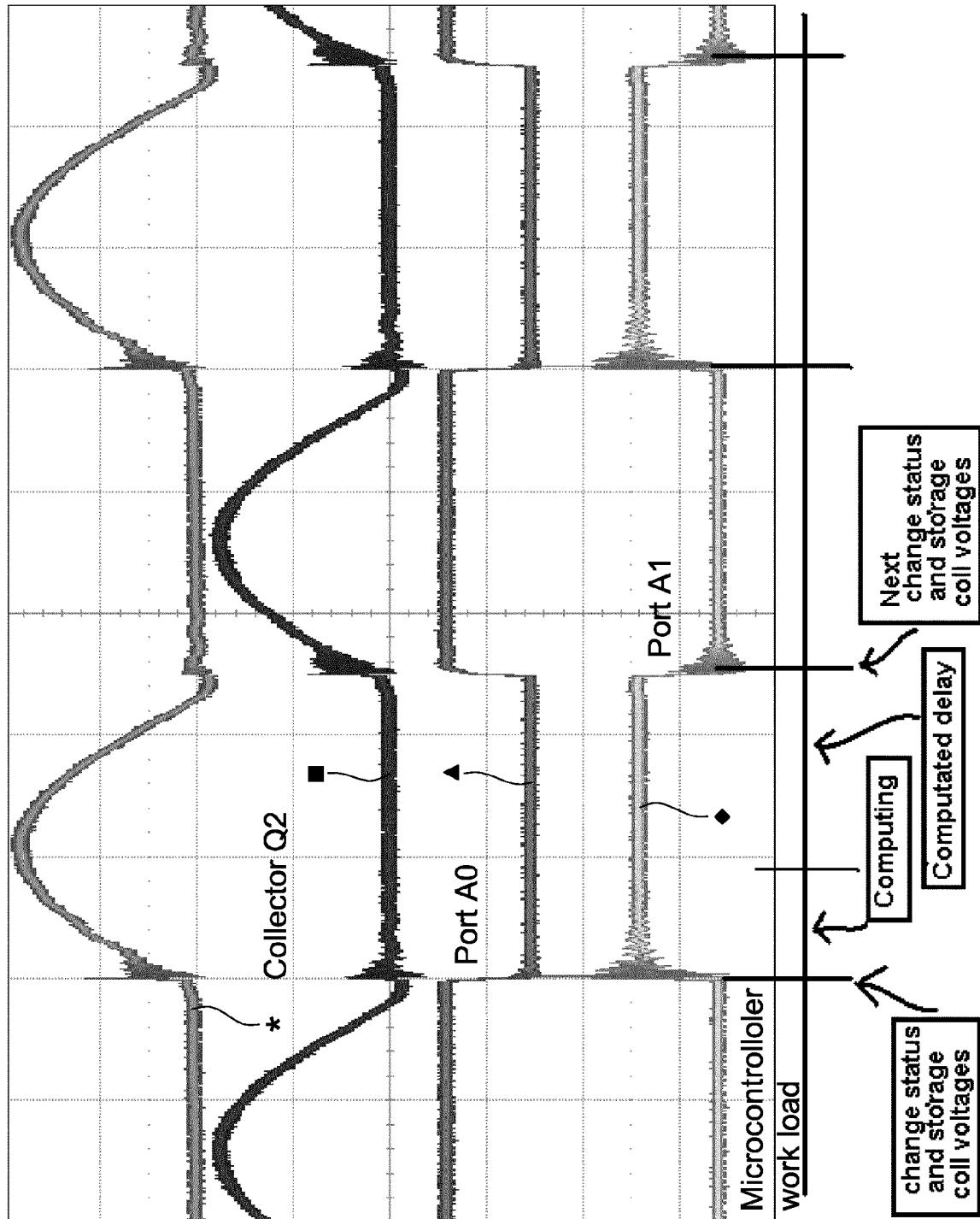

Figure 2 plots waves of the signals in the circuit of the known type of Figure 1;

15

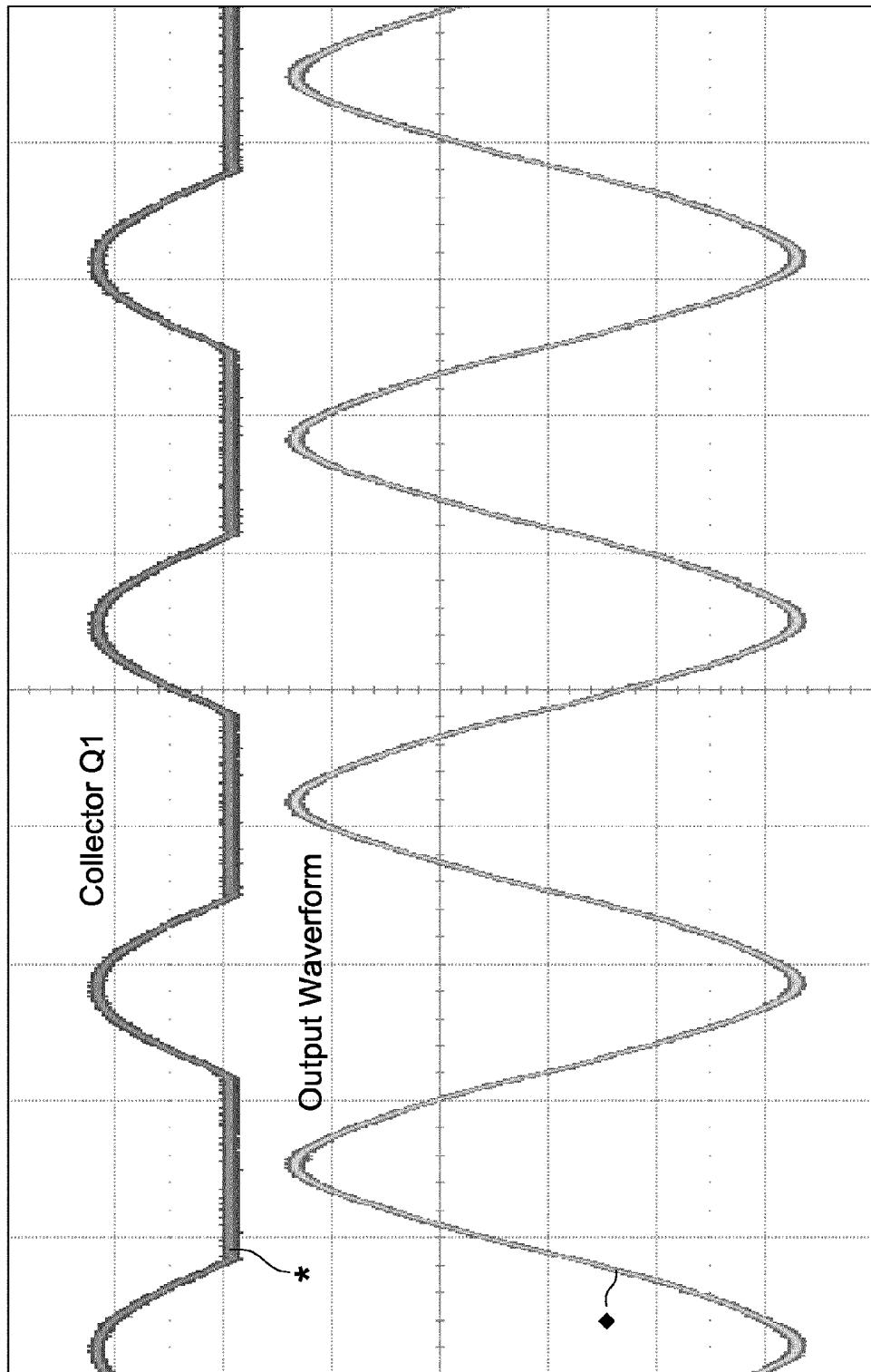

Figure 3 plots the wave of the output signal as a function of one of the waves of the internal signals in the circuit of the known type of Figure 1;

20

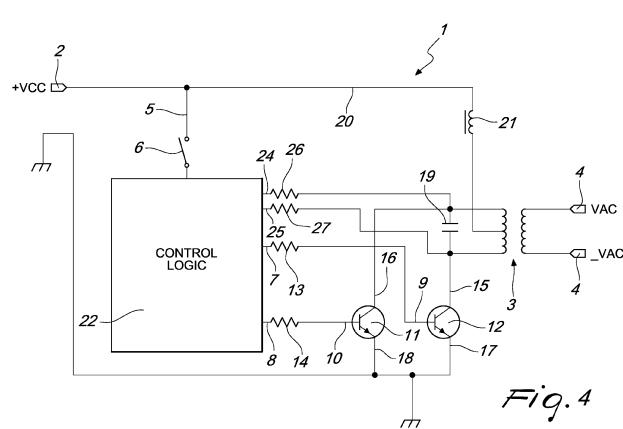

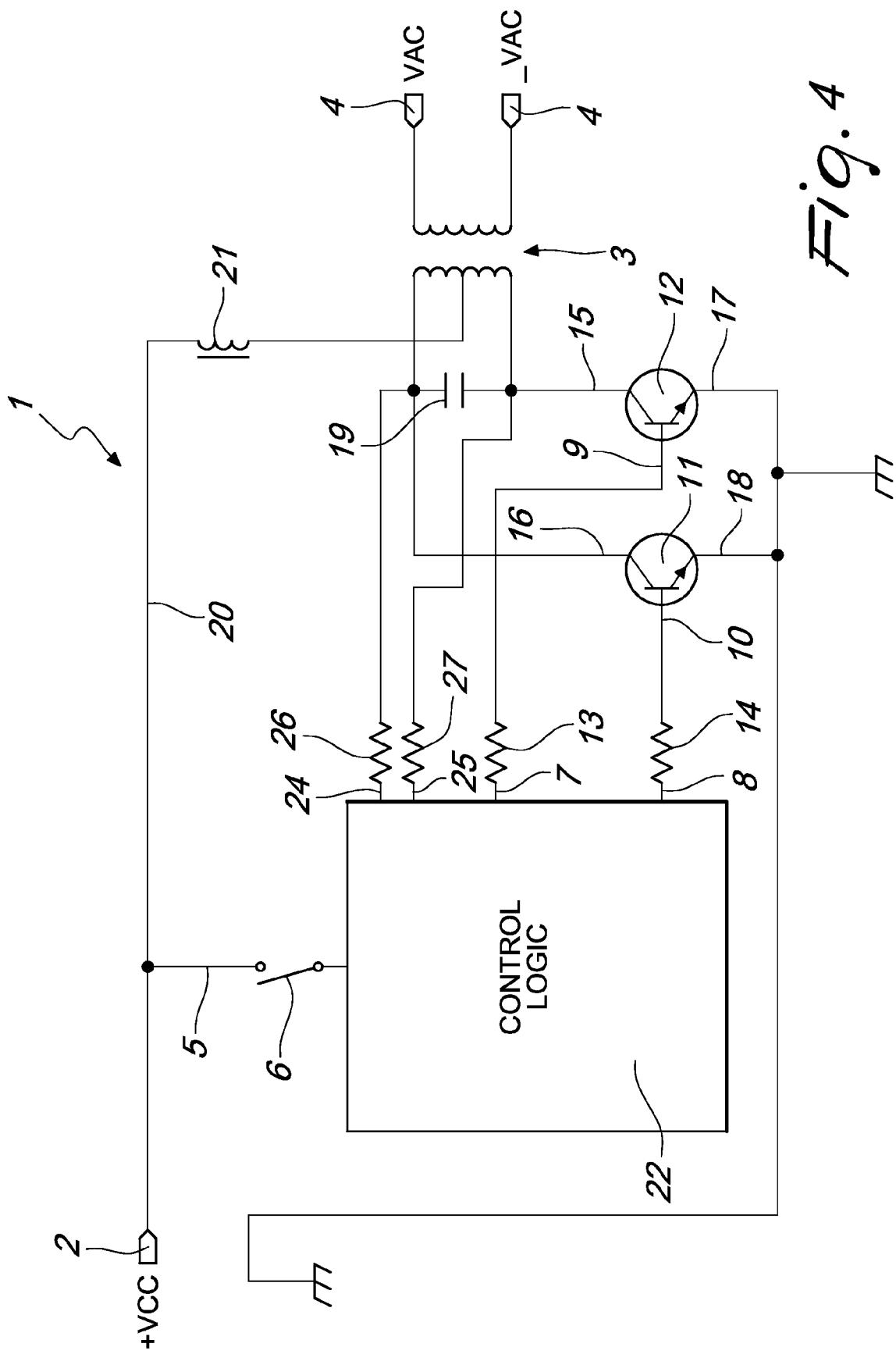

Figure 4 is a circuit diagram of a first constructive solution of the oscillator circuit according to the invention;

25

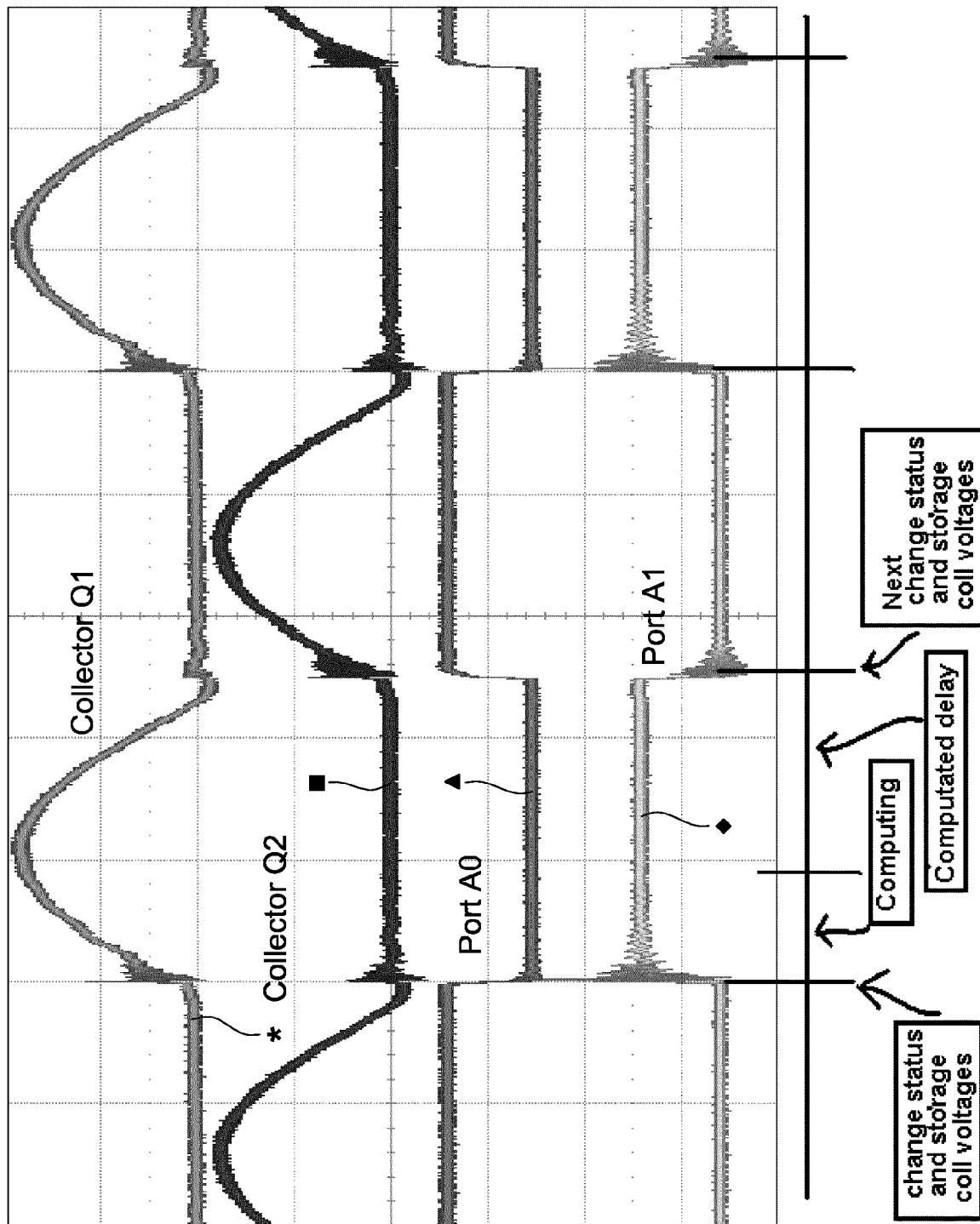

Figure 5 plots waves of the signals of the circuit of Figure 4;

30

Figure 6 plots waves of the signals of the circuit of Figure 4 upon the activation of said circuit;

35

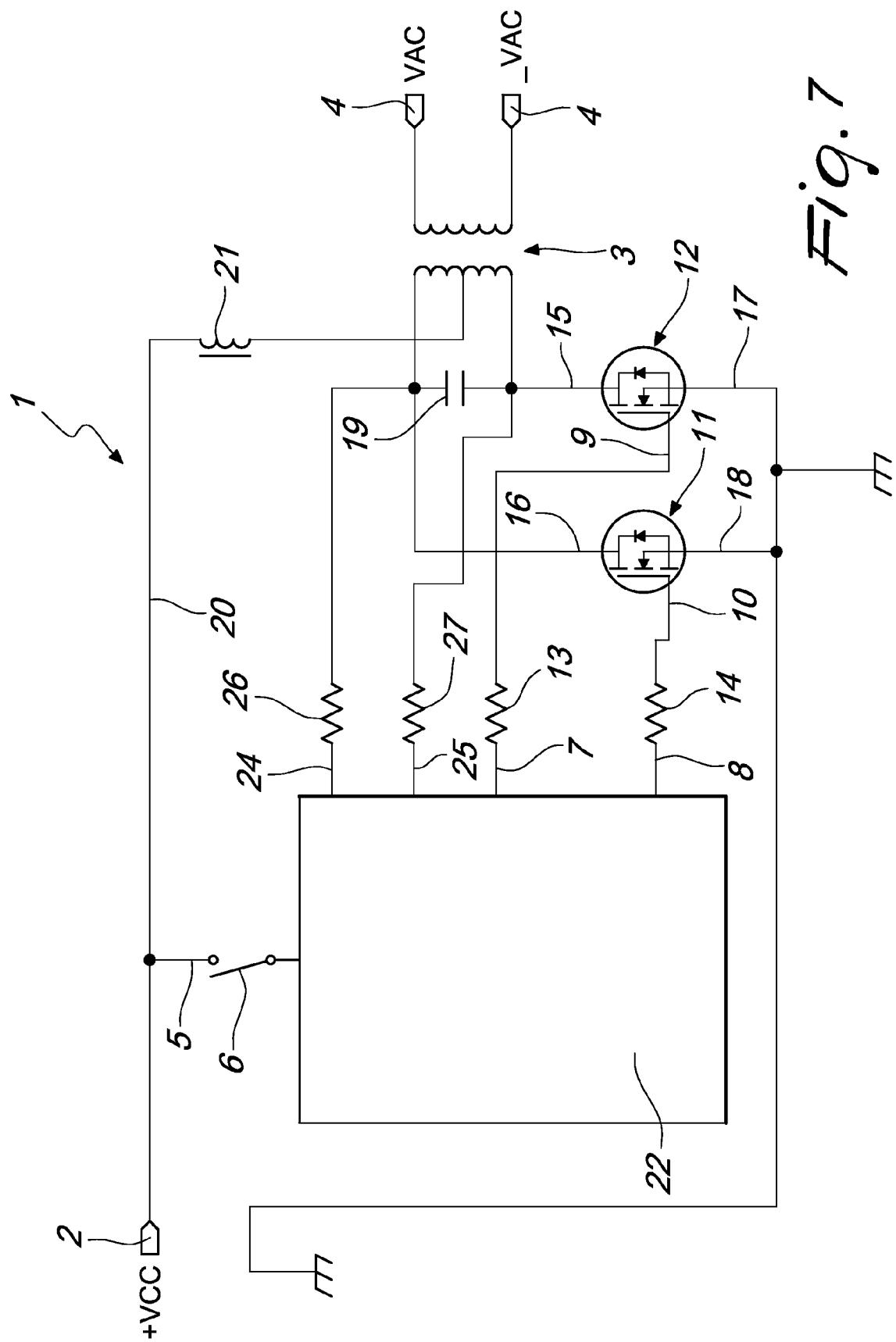

Figure 7 is a circuit diagram of a second constructive solution of the oscillator circuit according to the invention;

40

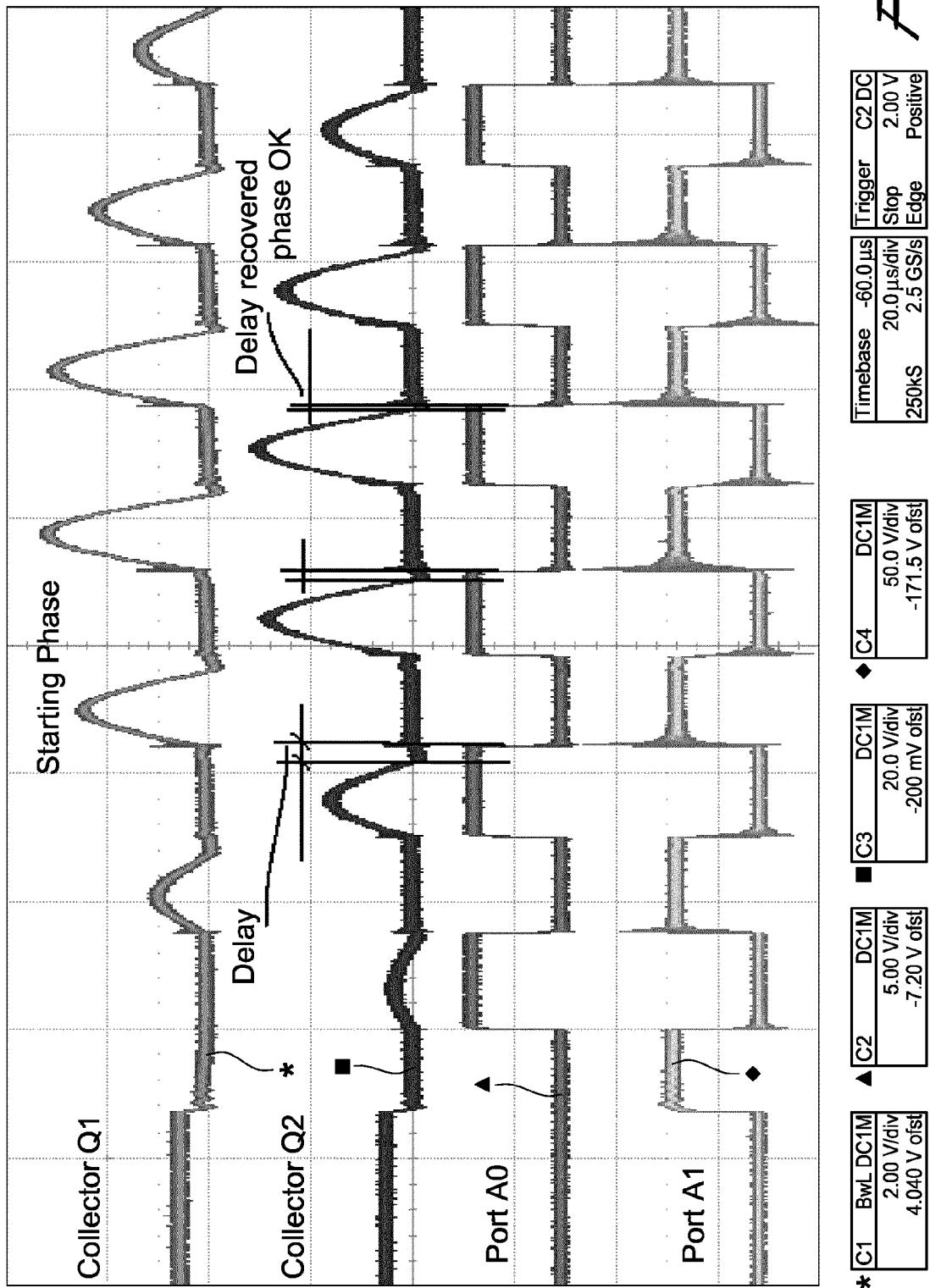

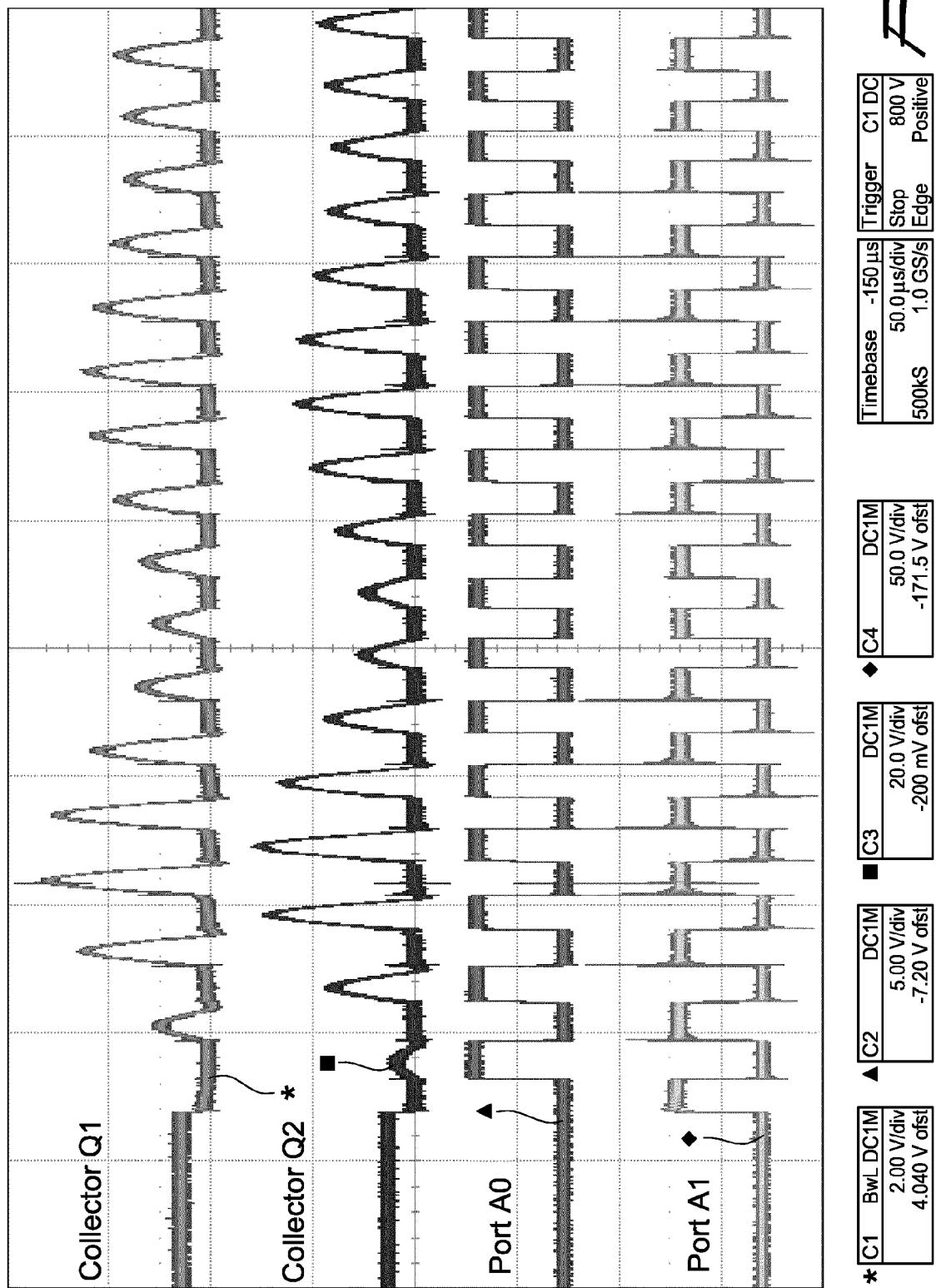

Figure 8 plots waves of the signals of the circuit of Figure 7;

45

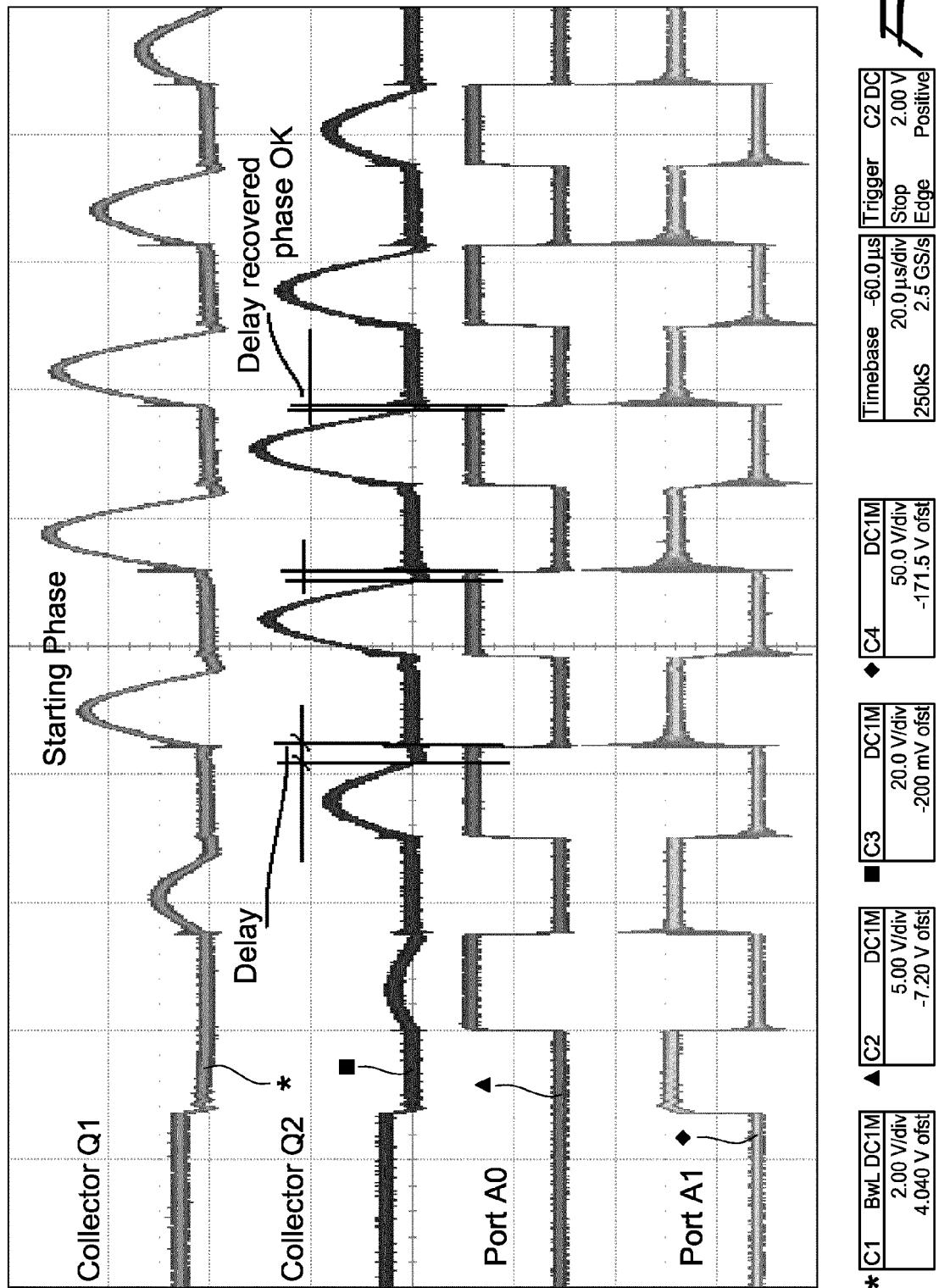

Figure 9 plots waves of the signals of the circuit of Figure 7 upon the activation of said circuit;

50

Figure 10 is an enlarged-scale view of Figure 9;

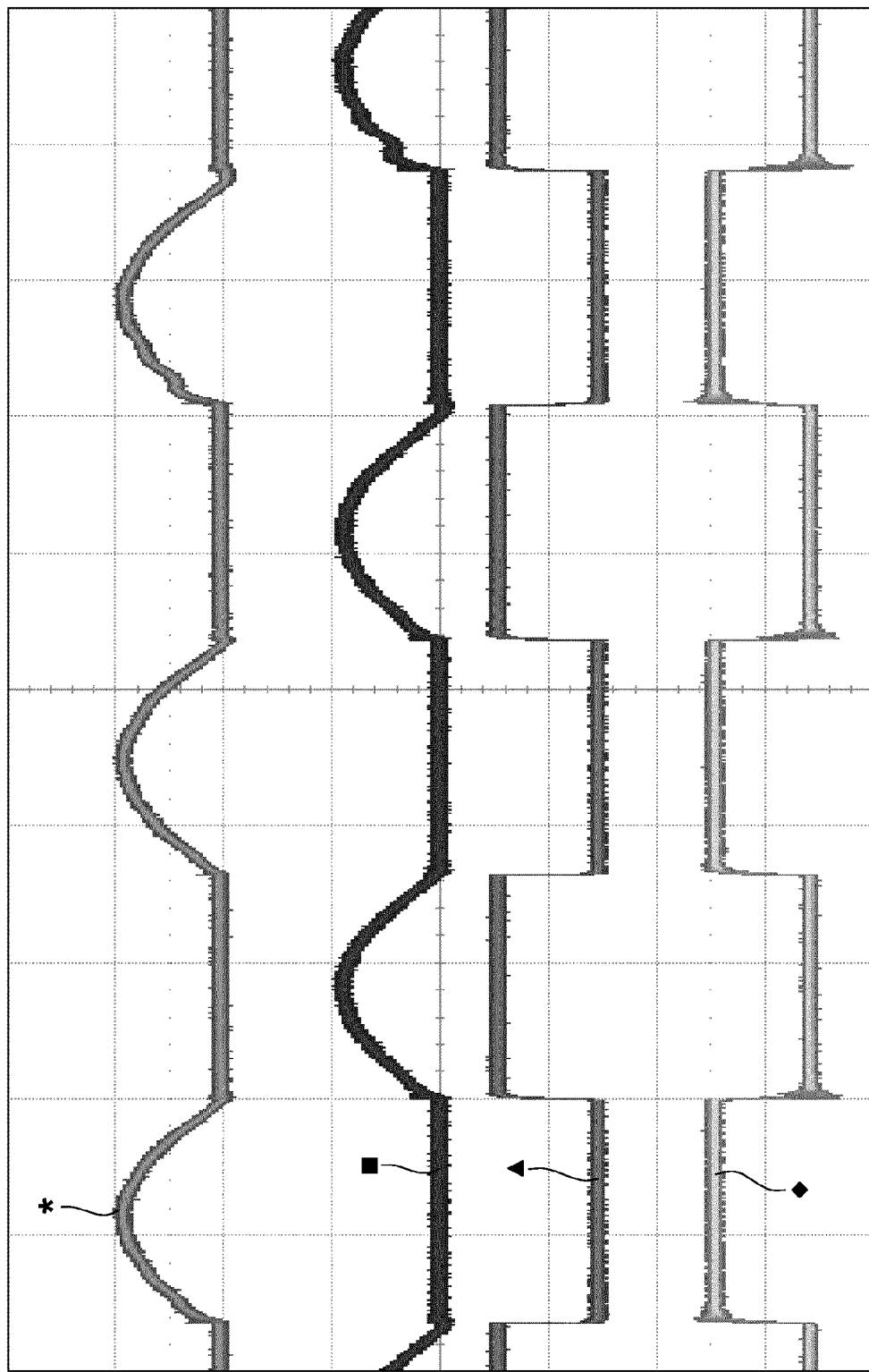

Figure 11 plots the typical behaviors of some waves of the signals of the oscillator circuit according to the invention.

30

**[0042]** With particular reference to the figures cited above, the reference numeral 1 designates a power supply oscillator circuit for light sources and other equivalent electrical user devices.

35

**[0043]** Oscillator circuits of the known type provide for the presence of a direct-current power supply source that has a predefined electrical potential +Vcc.

40

**[0044]** There is also a transformer T1, to the secondary winding terminals of which the electrical load is connected (supplied with alternating current by the secondary winding of said transformer).

45

**[0045]** A line that originates from the power supply source and is controlled upstream by a switch INT1 splits on two branches that lead to the control poles of respective transistors Q1 and Q2 (in the example related to the background art, shown in Figure 1, said transistors are BJT and the control pole of each of them is the respective base B).

50

**[0046]** A resistor (respectively R1 or R2) is arranged along the two predefined branches, upstream of the connection to the control pole of the respective transistor Q1 or Q2.

55

**[0047]** Downstream of the resistor R1 or R2 and upstream of the connection to the control pole of the respective transistor Q1 or Q2 there is an electric induction winding T1-B of the transformer to which the electric load is connected.

**[0048]** The poles at high potential of the transistors Q1 and Q2 are connected separately to a respective terminal

of the primary winding of the transformer T1 connected to the electric load.

**[0049]** In the specific case shown in Figure 1, for the exemplification of a constructive solution that is typical of the background art that provides for the adoption of BJTs as transistors Q1 and Q2, the poles at high potential are the collectors C.

**[0050]** The poles at low potential of the transistors Q1 and Q2 (in the case of Figure 1, said poles are the emitters E) are connected to the ground potential.

**[0051]** A capacitor C 1 is connected between the terminals of the transformer T1 and therefore also between the poles at high potential of the transistors Q1 and Q2.

**[0052]** A branch provided with an inductor L1 arranged in series connects the electric power supply source +Vcc to an intermediate point of the primary winding of the transformer T1.

**[0053]** Assuming that the value of the inductance of the transformer T1 is equal to a value L, upon closure of the switch INT1 a spontaneous oscillation of the energy flow in the circuit occurs at a frequency that is equal to:

$$f_0 = \frac{1}{2 * \pi * \sqrt{LC}}$$

**[0054]** The voltage available at the poles at high potential (according to the example of Figure 1, the collectors C) of Q1 and Q2 has the shape of a half sinusoid with a peak value equal to:

$$V_{\text{collectors}} = \pi V_{\text{cc}}$$

**[0055]** The voltage available across a secondary winding of T-1 is:

$$V_{\text{secondary}} = V_{\text{cc}} \pi \frac{M_{\text{ratio}}}{\sqrt{2}}$$

where  $M_{\text{ratio}}$  is the transformer ratio between the primary and secondary windings of the transformer T1.

**[0056]** Figures 2 and 3 plot the waveforms that can be detected in various points of the circuit with particular reference to the circuit of the known type shown in Figure 1.

**[0057]** The oscillator circuit 1 according to the invention also is a direct-current electric power source 2 that has a predefined electric potential +Vcc.

**[0058]** There is also a transformer 3, to the secondary winding terminals 4 of which the electric load (supplied with alternating current by the secondary winding of said transformer 3) is connected.

**[0059]** A line 5 that originates from the power supply

source and is controlled upstream by a switch 6 splits on two branches 7 and 8 that lead to the control poles 9 and 10 of respective transistors 11 and 12.

**[0060]** Respective resistors 13 and 14 are arranged along the two branches 7 and 8.

**[0061]** The poles at high potential 15 and 16 of the transistors 12 and 11 are connected separately to a respective terminal of the primary winding of the transformer 3 that is connected to the electric load.

**[0062]** The poles at low potentials 17 and 18 of the transistors 12 and 11 are connected to the ground potential.

**[0063]** A capacitor 19 is connected between the terminals of the transformer 3 and therefore also between the poles at high potential 16 and 17 of the transistors 12 and 11.

**[0064]** A branch 20 provided with an inductor 21 arranged in series connects the electric power supply source 2 at a potential +Vcc to an intermediate point of the primary winding of the transformer 3.

**[0065]** The circuit 1 according to the invention comprises a control and management unit 22 that is interposed between the switch 6 and the branches 7 and 8.

**[0066]** The unit 22 has at least one input terminal connected downstream to the line 5 controlled by the switch 6 and at least two output terminals associated with the branches 7 and 8.

**[0067]** The signal on the output terminals of the unit 22 is synchronized with the natural frequency of the circuit

30

$$f_0 = \frac{1}{2 \pi \sqrt{LC}}$$

35

where C is the value of the capacitance of the capacitor 19 and L is the value of the inductance of the transformer 3.

**[0068]** More specifically, it is convenient to point out that upon the closure of the switch 5 arranged upstream of the unit 22, the signal at the output terminals 7 and 8 of said unit 22 has a frequency that is substantially equal to the natural frequency  $f_0$ .

**[0069]** In this manner, upon the closure of the switch 6, the unit supplies to its own terminals 7 and 8 signals with a predefined frequency that is equal to the natural frequency of the circuit. This condition facilitates the reaching, with short transients, of a balance condition that corresponds to the onset of a fixed frequency (as close as possible to the natural frequency) even upon variations of the electric load placed at the output terminals 4 of the transformer 3.

**[0070]** With particular reference to constructive solutions of unquestionable interest in practice and in application, the circuit 1 can comprise positively a feedback control to detect the frequency of the resonance voltage that is present at the high-level output poles 15 and 16 of the transistors 12 and 11 and the variation, as a func-

tion of said detection, of the frequency of the signals emitted by the unit 22 to supply the control poles 9 and 10 of said transistors 12 and 11.

[0071] This adjustment of the signal in output from the unit 22 occurs up to synchronization with the natural oscillation  $f_0$ .

[0072] It should be noted that the signals at the output terminals of the unit 22 (on the branches 7 and 8) are substantially in mutual phase opposition.

[0073] This means that the maximum value of the signal at a first terminal is matched by the minimum value of the other terminal.

[0074] The transitions from the maximum value to the minimum value of the signal at one terminal and from the minimum value to the maximum value at the other terminal are substantially simultaneous.

[0075] It is noted furthermore that the signals at the output terminals of the unit 20 have a gradual amplitude increase ram at their initial steps.

[0076] According to the constructive solution shown by way of example in Figure 4, the transistors 11 and 12 are BJTs (i.e., bipolar junction transistors, which can be simplified as the joining of two diodes that are polarized oppositely and have a common anode or cathode).

[0077] In this case, the respective control pole 10 and 9 is the base, the respective high-level output pole 16 and 15 is the collector, and the respective low-level output pole 18 and 17 is the emitter.

[0078] According to an alternative constructive solution of unquestionable interest in practice and in application, the transistors 11 and 12 are MOSFETs (metal-oxide-semiconductor field effect transistors), the respective control pole 10 and 9 in this case is the GATE, the respective high-level output pole 16 and 15 is the DRAIN and the respective low-level output pole 18 and 17 is the corresponding SOURCE.

[0079] In any case, in order to allow frequency feedback control, it is convenient to specify that the control and management unit 22 comprises two auxiliary terminals 24 and 25, which are connected to the opposite terminals of the capacitor 19, to detect and store the voltage value that corresponds to the voltage of the high-level pole 16 and 15 of the transistor 11 and 12.

[0080] The unit 22 can thus proceed with the calculation of the frequency of the stored voltages for the feedback control of the value of the frequency of the signal transmitted to the control poles 10 and 9 in order to approximate a frequency that is substantially equal to the natural frequency  $f_0$ .

[0081] If the transistors 11 and 12 are MOSFETs, the control and management unit 22 is constituted by a microcontroller.

[0082] Respective resistors 26 and 27 for adapting the level of the signal are arranged and interposed between the auxiliary terminals 24 and 25 and the terminals of the capacitor 19 along the respective circuit branches.

[0083] In order to define precisely the operating sequence of the circuit 1 according to the invention it is

necessary to analyze in depth the method by means of which said circuit performs frequency control.

[0084] The frequency control and management method in the oscillator circuit 1, with particular reference to the case in which said circuit 1 is intended to supply power to light sources and other equivalent electrical user devices, consists of a series of consecutive steps.

[0085] First of all it is necessary to set, at the first closure of the switch 6, the frequency of the signal at the output terminals 7 and 8 from the control and management unit 22 with a value that is substantially equal to the natural frequency

$$f_0 = \frac{1}{2 \pi \sqrt{LC}}$$

[0086] Once this first step, which is necessary to set the initial operating conditions of the circuit 1, has been performed, and once signals have been generated at the initial step of operation at the output terminals of the unit 22 with a gradually increasing amplitude, it becomes necessary to detect the value of the frequency  $f$  of the voltage that is present at the two terminals of the capacitor 19.

[0087] This operation is performed by means of the auxiliary terminals 24 and 25 connected to the terminals of said capacitor 19.

[0088] It is thus possible to compare the value of the frequency  $f$  that corresponds to the detected signal with the value of the natural frequency  $f_0$ .

[0089] As a function of this comparison, the unit 22 increases/decreases the value of the frequency of the signal at its output terminals 7 and 8 in order to modify, i.e., increase/decrease, the frequency  $f$  of the voltage that is present at the two terminals of the capacitor 19 (detected by the auxiliary terminals 24 and 25) in order to make it substantially equal to the natural frequency  $f_0$ .

[0090] It is specified that in order to ensure an instant response of the circuit 1 to any changes in the electrical load placed downstream of the transformer 3, at each cycle of the oscillator circuit 1, the unit 22 detects the value of the frequency of the voltage at the terminals of the capacitor 19 to compare it with the natural frequency  $f_0$  and the variation of the frequency of the signal emitted by the terminals 7 and 8 on the two branches provided with the resistors 13 and 14.

[0091] It is therefore observed immediately that the circuit 1 according to the invention substantially eliminates all the defects of conventional circuits (described initially, within the definition of the background art) by generating a precise signal for control of the semiconductors Q1 and Q2 (in the specific case 11 and 12), synchronizing said signal with the characteristic frequency  $f_0$  of the circuit.

[0092] What makes the circuit 1 according to the invention particularly efficient is the fact that the control signal of Q1 and Q2 (in particular of the transistors 11 and 12) no longer originates from an auxiliary winding of

the transformer 3 (the one which, in the definition of the background art, had been identified by the reference T1-B), but from an adapted control and management unit 22, which provides a signal of adequate amplitude, synchronized with the characteristic oscillation frequency  $f_0$ . [0093] In this manner, the following advantages are achieved and solve the corresponding disadvantages of the conventional system:

- A) Since it is possible to set a maximum and minimum operating frequency, the oscillator circuit 1 cannot operate at higher harmonics or at subharmonics of the desired frequency, ensuring stable operation and a noise-free load power supply signal;

- B) At the initial instant, the applied signal is always alternated on the transistors 11 and 12 and is never simultaneous.

[0094] Furthermore, since the control logic is determined by the signal for the transistors 11 and 12 emitted by the unit 22, oscillation can be started by keeping the exact phase already from the start and with a gradually increasing amplitude, in order to ensure gradual starting and avoid excessive starting current values upon startup.

- C) The control signal of the transistors 11 and 12 (which originates from the terminals 7 and 8 of the unit 22) has an adjustable power level (controlled by the specific operating requirements), indeed thanks to the fact that it is generated by a logic component (the unit 22) and not by an auxiliary winding of the transformer 3.

- D) The variation of the parasitic parameters of the components (leakage inductance and parasitic capacitances) does not affect operation (as instead occurs in circuits of the known type), since said operation is forced (by the unit 22) on the main parameters (nominal inductance L and capacitance C).

[0095] Advantageously, therefore, the oscillator circuit 1 avoids the simultaneous presence of a signal on the two transistors 11 and 12 during startup.

[0096] Efficiently, the oscillator circuit 1 operates in operating conditions that eliminate or minimize the presence of higher harmonic frequencies (or subharmonics) of the desired frequency on the electric load that it supplies.

[0097] The oscillator circuit 1 furthermore ensures conveniently regular operation, regardless of the variation of the electrical values that are present therein.

[0098] Moreover, said regular operation is achieved independently of the parasitic parameters of said circuit.

[0099] It is evident that an emergency light source, which therefore receives electric power from a battery (its operation is in fact required only when the electrical mains does not supply power and therefore it is necessary to compensate for this failure by means of temporary lighting that is disconnected from said mains), despite

operating in alternating current, will gain an enormous benefit from the use of the oscillator circuit 1 according to the invention.

[0100] All the noise that might create malfunctions of said source are in fact eliminated, despite maintaining extreme circuit simplicity and therefore substantially low costs. The space occupation of the circuits 1 also is contained, to the benefit of the possibility to install it within the boxlike body that contains the emergency light source and the corresponding battery. The possibility to locate all the components within a single boxlike body furthermore eliminates the dispersion of energy along any external power supply lines, increasing considerably the overall efficiency of the emergency lighting device.

[0101] The invention thus conceived is susceptible of numerous modifications and variations, all of which are within the scope of the appended claims; all the details may further be replaced with other technically equivalent elements.

[0102] In the examples of embodiment shown, individual characteristics, given in relation to specific examples, may actually be interchanged with other different characteristics that exist in other examples of embodiment.

[0103] In practice, the materials used, as well as the dimensions, may be any according to requirements and to the state of the art.

[0104] The disclosures in Italian Patent Application no. BO2012A000672, from which this application claims priority, are incorporated herein by reference.

[0105] Where technical features mentioned in any claim are followed by reference signs, those reference signs have been included for the sole purpose of increasing the intelligibility of the claims and accordingly such reference signs do not have any limiting effect on the interpretation of each element identified by way of example by such reference signs.

## Claims

1. A power supply oscillator circuit for light sources and other equivalent electrical user devices of the type comprising at least one capacitor (19) interposed between a direct-current power supply source (2) and an output transformer (3), two transistors (11, 12) being interposed between said direct-current power supply source (2) and said capacitor (19) and having their corresponding control pole (10, 9) connected to a respective, and different, branch (8, 7) that originates from the high electrical potential terminal of the power supply source (2), the corresponding high-level output pole (16, 15) connected to a respective, and different, terminal of said capacitor (19) and the corresponding low-level output poles (18, 17) connected to the ground, along said branches (7, 8) there being at least one respective resistor (14, 13) that is connected upstream, with the interposition of a switch (6), to the high electrical potential terminal

of the power supply source (2), **characterized in that** it comprises a control and management unit (22), which is interposed between said switch (6) and said branches (8, 7) provided with at least one respective resistor (14, 13), said unit (22) having at least one input terminal connected downstream to the line (5) affected by said switch (6) and at least two output terminals associated with said branches (8, 7) provided with at least one resistor (14, 13), the signal on the output terminals of said unit (22) being synchronized with the natural frequency of the circuit

$$f_0 = \frac{1}{2 \pi \sqrt{LC}}$$

where C is the value of the capacitance of said capacitor and L is the value of the inductance of said transformer (3).

2. The oscillator circuit according to claim 1, **characterized in that** at the closure of the switch (6) arranged upstream of the unit (22) the signal at the output terminals of said unit (22) has a frequency that is substantially equal to the natural frequency  $f_0$ .

3. The oscillator circuit according to claim 2, **characterized in that** it comprises a feedback control for detecting the frequency of the resonance voltage that is present at the high-level output pole (16, 15) of said transistors (11, 12), and the variation, as a function of said detection, of the frequency of the signals emitted by said unit (22) for the power supply of the control poles (10, 9) of said transistors (11, 12), up to synchronization with the natural oscillation  $f_0$ .

4. The oscillator circuit according to claim 1, **characterized in that** the signals at the output terminals of said unit (22) are substantially in mutual phase opposition, the maximum value of the signal at a first terminal corresponding to the minimum value of the other terminal, the transitions from the maximum value to the minimum value of one terminal and from the minimum value to the maximum value of the other terminal being substantially simultaneous.

5. The oscillator circuit according to claim 1, **characterized in that** the signals at the output terminals of said unit (22) have a gradual amplitude increase ramp at their initial steps.

6. The oscillator circuit according to claim 1, **characterized in that** said transistors (11, 12) are BJT, the respective control pole (10, 9) being the base, the respective high-level output pole (16, 15) being the collector and the respective low-level output pole

(18, 17) being the emitter.

7. The oscillator circuit according to claim 1, **characterized in that** said transistors (11, 12) are MOS-FETs, the respective control pole (10, 9) being the GATE, the respective high-level output pole (16, 15) being the DRAIN and the respective low-level output pole (18, 17) being the SOURCE.

10 8. The oscillator circuit according to one of claims 6 or 7, **characterized in that** said control and management unit (22) comprises two auxiliary terminals (24, 25), which are connected to the opposite terminals of said capacitor (19), to detect and store the voltage value that corresponds to the voltage of the high-level pole (16, 15) of said transistor (11, 12), said unit (22) calculating the frequency of the stored voltages for feedback control of the value of the frequency of the signal transmitted to the control poles (10, 9) in order to approximate a frequency that is substantially equal to the natural frequency  $f_0$ .

9. A method for the control and management of the frequency in an oscillator circuit (1) for the power supply of light sources and other equivalent electrical user devices, of the type comprising at least one capacitor (19) that is interposed between a direct-current power supply source (2) and an output transformer (3), two transistors (11, 12) being interposed between said direct-current power supply source (2) and said capacitor (19), their corresponding control pole (10, 9) being connected to a respective, and different, branch (8, 7) that originates from the high electrical potential terminal of the power supply source (2), the corresponding high-level output pole (16, 15) connected to a respective, and different, terminal of said capacitor (19) and the corresponding low-level output poles (18, 17) connected to the ground, along said branches (8, 7) that originate from the high electrical potential terminal of the power supply source (2) there being at least one respective resistor (14, 13) that is connected upstream, with the interposition of a switch (6), to the high electrical potential terminal of the power supply source (2), which consists in

- setting, at the first closure of said switch (6), the frequency of the signal at the output terminals from a control and management unit (22), which is interposed between said switch (6) and said branches (8, 7) provided with respective resistors (14, 13), with a value that is substantially equal to the natural frequency

$$f_0 = \frac{1}{2 \pi \sqrt{LC}} ;$$

- generating, at the initial step of operation, sig-

nals at the output terminals of said unit (22) having a gradually increasing amplitude;

- detecting the value of the frequency  $f$  of the voltage that is present across the two terminals of said capacitor (19);

5

- comparing the value of the frequency  $f$  with the value of the natural frequency  $f_0$ ;

- increasing/decreasing the value of the frequency of the signal at the output terminals of said unit (22) in order to modify increase/decrease the frequency  $f$  of the voltage that is present across the two terminals in order to render it substantially equal to the natural frequency  $f_0$ .

10

10. The method according to claim 9, **characterized in** 15

**that** at each cycle of said oscillator circuit (1) the unit (22) detects the value of the frequency of the voltage across the terminals of the capacitor (19) in order to compare it with the natural frequency  $f_0$  and vary the frequency of the signal emitted on the two branches 20 (8, 7) provided with resistors (14, 13).

20

25

30

35

40

45

50

55

Fig. 2

Fig. 3

Fig. 5

Fig. 6

Fig. 8

Fig. 9

$\mathcal{T}/\mathcal{Q}.$  11

|          |                  |         |          |

|----------|------------------|---------|----------|

| Timebase | -30.0 $\mu$ s    | Trigger | C2 DC    |

|          | 10.0 $\mu$ s/div | Stop    | 2.00 V   |

|          | 500 $\mu$ s      | Edge    | Positive |

|    |                |   |    |                 |

|----|----------------|---|----|-----------------|

| C3 | DC1M           | ◆ | C4 | DC1M            |

|    | 20.0 V/div     |   |    | 5.00 V/div      |

|    | -200 mV offset |   |    | -17.25 V offset |

|    |                |   |    |                |

|----|----------------|---|----|----------------|

| C2 | DC1M           | ▲ | C1 | Bwl DC1M       |

|    | 5.00 V/div     |   |    | 20.0 V/div     |

|    | -7.20 V offset |   |    | 40.40 V offset |

|   |                |      |   |                |      |

|---|----------------|------|---|----------------|------|

| ◆ | C4             | DC1M | ◆ | C3             | DC1M |

|   | 5.00 V/div     |      |   | 20.0 V/div     |      |

|   | -200 mV offset |      |   | -200 mV offset |      |

|   |                |          |   |                |      |

|---|----------------|----------|---|----------------|------|

| * | C1             | Bwl DC1M | ▲ | C2             | DC1M |

|   | 20.0 V/div     |          |   | 5.00 V/div     |      |

|   | 40.40 V offset |          |   | -7.20 V offset |      |

\*

## EUROPEAN SEARCH REPORT

Application Number

EP 13 19 7196

| DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                   |                                                                                                     |                                                   | CLASSIFICATION OF THE APPLICATION (IPC) |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------|

| Category                                                                                                                                                                                                                                                                              | Citation of document with indication, where appropriate, of relevant passages                       | Relevant to claim                                 |                                         |

| X                                                                                                                                                                                                                                                                                     | US 5 652 479 A (LOCASCIO JAMES J [US] ET AL) 29 July 1997 (1997-07-29)<br>* columns 3-5; figure 1 * | 1-7                                               | INV.<br>H05B41/392<br>H05B41/282        |

| A                                                                                                                                                                                                                                                                                     | -----                                                                                               | 8-10                                              |                                         |

| A                                                                                                                                                                                                                                                                                     | US 6 064 160 A (NAKAMURA KYOTARO [JP]) 16 May 2000 (2000-05-16)<br>* abstract *                     | 1-10                                              |                                         |

| A                                                                                                                                                                                                                                                                                     | -----                                                                                               |                                                   |                                         |

| A                                                                                                                                                                                                                                                                                     | US 6 317 347 B1 (WENG DA FENG [US]) 13 November 2001 (2001-11-13)<br>* abstract *                   | 1-10                                              |                                         |

| A                                                                                                                                                                                                                                                                                     | -----                                                                                               |                                                   |                                         |

| A                                                                                                                                                                                                                                                                                     | EP 0 673 184 A2 (LINEAR TECHN INC [US]) 20 September 1995 (1995-09-20)<br>* figure 2 *              | 1-10                                              |                                         |

| A                                                                                                                                                                                                                                                                                     | -----                                                                                               |                                                   |                                         |

| A                                                                                                                                                                                                                                                                                     | US 5 055 993 A (MIYATA OSAMU [JP] ET AL) 8 October 1991 (1991-10-08)<br>* abstract *                | 1-10                                              |                                         |

|                                                                                                                                                                                                                                                                                       | -----                                                                                               |                                                   |                                         |

|                                                                                                                                                                                                                                                                                       |                                                                                                     |                                                   | TECHNICAL FIELDS<br>SEARCHED (IPC)      |

|                                                                                                                                                                                                                                                                                       |                                                                                                     |                                                   | H05B                                    |

| The present search report has been drawn up for all claims                                                                                                                                                                                                                            |                                                                                                     |                                                   |                                         |

| 3                                                                                                                                                                                                                                                                                     | Place of search<br>Munich                                                                           | Date of completion of the search<br>10 March 2014 | Examiner<br>Boudet, Joachim             |

| CATEGORY OF CITED DOCUMENTS                                                                                                                                                                                                                                                           |                                                                                                     |                                                   |                                         |

| X : particularly relevant if taken alone<br>Y : particularly relevant if combined with another document of the same category<br>A : technological background<br>O : non-written disclosure<br>P : intermediate document                                                               |                                                                                                     |                                                   |                                         |

| T : theory or principle underlying the invention<br>E : earlier patent document, but published on, or after the filing date<br>D : document cited in the application<br>L : document cited for other reasons<br>.....<br>& : member of the same patent family, corresponding document |                                                                                                     |                                                   |                                         |

**ANNEX TO THE EUROPEAN SEARCH REPORT

ON EUROPEAN PATENT APPLICATION NO.**

EP 13 19 7196

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on. The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

10-03-2014

| Patent document cited in search report |    | Publication date |    | Patent family member(s) |            | Publication date |

|----------------------------------------|----|------------------|----|-------------------------|------------|------------------|

| US 5652479                             | A  | 29-07-1997       |    | NONE                    |            |                  |

| US 6064160                             | A  | 16-05-2000       | JP | 3398734 B2              | 21-04-2003 |                  |

|                                        |    |                  | JP | H10284282 A             | 23-10-1998 |                  |

|                                        |    |                  | US | 6064160 A               | 16-05-2000 |                  |

| US 6317347                             | B1 | 13-11-2001       | CN | 1449642 A               | 15-10-2003 |                  |

|                                        |    |                  | EP | 1330944 A2              | 30-07-2003 |                  |

|                                        |    |                  | JP | 2004511195 A            | 08-04-2004 |                  |

|                                        |    |                  | US | 6317347 B1              | 13-11-2001 |                  |

|                                        |    |                  | WO | 0230161 A2              | 11-04-2002 |                  |

| EP 0673184                             | A2 | 20-09-1995       | DE | 69533681 D1             | 02-12-2004 |                  |

|                                        |    |                  | EP | 0673184 A2              | 20-09-1995 |                  |

|                                        |    |                  | JP | H0855691 A              | 27-02-1996 |                  |

| US 5055993                             | A  | 08-10-1991       | JP | 2707465 B2              | 28-01-1998 |                  |

|                                        |    |                  | JP | H0336963 A              | 18-02-1991 |                  |

|                                        |    |                  | US | 5055993 A               | 08-10-1991 |                  |

**REFERENCES CITED IN THE DESCRIPTION**

*This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.*

**Patent documents cited in the description**

- IT BO20120672 A [0104]