# (11) EP 2 759 900 A1

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

30.07.2014 Bulletin 2014/31

(51) Int Cl.:

G05F 1/575 (2006.01)

(21) Application number: 13392001.7

(22) Date of filing: 25.01.2013

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

Designated Extension States:

**BA ME**

(71) Applicant: Dialog Semiconductor GmbH

73230 Kirchheim (DE)

(72) Inventors:

Ambreesh Bhattad Swindon Wiltshire, SN57AH (GB)

Ludmil, Nikolov Chippenham Wiltshire SN153NB (GB)

(74) Representative: Schuffenecker, Thierry

120 Chemin de la Maure 06800 Cagnes sur Mer (FR)

## (54) Maintaining the resistor divider ratio during start-up

(57) Circuits and methods to maintain a resistive voltage divider ratio during start-up of an electronic circuit comprising a feed-forward capacitor across a feedback resistor using a dynamic start-up circuit are disclosed as e.g. a LDO or an amplifier. In a preferred embodiment of the disclosure is applied to an LDO. Modification of the

resistive voltage divider ratio caused by the feed-forward capacitor during start-up is prevented while the voltage level of a voltage access point of the voltage divider on the feed-forward capacitor is maintained. Embodiments of the disclosure presented comprise using a start-up buffer or a start-up capacitor during the start-up phase.

FIG. 1

EP 2 759 900 A1

30

35

45

50

55

## **Technical Field**

**[0001]** The present document relates to start-up processes of electronic circuits. In particular, the present document relates to a method and system for maintaining a resistor voltage divider ratio during start-up using a dynamic circuit.

1

#### **Background Art**

**[0002]** Prior art implementations of circuits as e.g. a low-dropout (LDO) voltage regulator using a feed-forward capacitor in parallel to a feedback resistor of a resistor voltage divider have the disadvantage that a voltage divider ratio is impacted by the feed-forward capacitor during start-up phase and clean start-up specification may not always being met.

**[0003]** It is a challenge for engineers to design startup processes of circuits as e.g. an LDO without the disadvantage cited above.

#### Summary of the invention

**[0004]** A principal object of the present disclosure is to achieve a correct determination of the output voltage of a circuit by a start-up comparator.

**[0005]** A further object of the disclosure is to avoid an output voltage drop (brown out) condition of the circuit as e.g. an LDO.

**[0006]** A further object of the disclosure is to avoid any violation of a start-up specification.

**[0007]** A further object of the disclosure is to achieve a clean start-up process.

**[0008]** A further object of the disclosure is to maintain a constant voltage divider ratio during start-up.

**[0009]** A further object of the disclosure is to use a dynamic circuit to manage the start-up process only during start-up.

[0010] In accordance with the objects of this disclosure a method to maintain a resistive voltage divider ratio during start-up of any electronic circuit comprising a feedforward capacitor across a feedback resistor of a resistive voltage divider using a dynamic start-up circuit has been disclosed. The method disclosed comprises the following steps: (1) providing an electronic circuit comprising a feed-forward capacitor across a first feedback resistor of a resistive voltage divider and a start-up circuit, (2) avoiding modification of resistive voltage divider ratio caused by feed-forward capacitor during start-up phase, (3) monitoring output voltage and finish start-up-phase when desired output voltage of the electronic circuit is reached, and (4) processing normal operation after start-up phase is finished wherein feed-forward capacitor is connected across the feedback resistor of the resistive voltage divider after end of start-up phase.

[0011] In accordance with the objects of this disclosure

a circuit to maintain a resistive voltage divider ratio during start-up of a LDO comprising a feed-forward capacitor across a feedback resistor using a dynamic start-up circuit has been achieved. The circuit disclosed comprises, the feed-forward capacitor, wherein a first plate of the feed-forward capacitor is connected to an output port of the LDO voltage, said resistive voltage divider, being connected between the output port of the LDO and ground, comprising the feedback resistor having a resistance R2 connected between the output port of the LDO and the voltage access point in-between the voltage divider having a fraction of the output voltage and further comprising a second resistor having a resistance R1, and a means to maintain a voltage level of the voltage access point across the feed-forward capacitor during start-up of the LDO.

[0012] In accordance with the objects of this disclosure a circuit to maintain a resistive voltage divider ratio during start-up of any electronic circuit comprising a feed-forward capacitor across a feedback resistor and a resistive voltage divider using a dynamic start-up circuit, has been disclosed. The circuit disclosed firstly comprises: the feed-forward capacitor, wherein a first plate of the feedforward capacitor is connected to an output port of the circuit and a second plate is connected to a voltage access point of the resistive voltage divider after the startup phase of the electronic circuit is finished and said resistive voltage divider, being connected between an output port of the circuit and ground, comprising the feedback resistor having a resistance R2 connected between the output port of the circuit and the voltage access point in-between the voltage divider having a fraction of the output voltage and further comprising a second resistor having a resistance R1. Furthermore the circuit comprises: a start-up comparator detecting if the start-up phase is finished by comparing a voltage representing the output voltage of the electronic circuit with a reference voltage and a means to maintain a voltage level of the voltage access point across the feed-forward capacitor during start-up of the circuit, wherein the means to maintain a voltage level of the voltage access point comprises switching means to connect or disconnect components of the circuit at beginning and end of the start-up process, wherein the switching means are activated by the startup comparator.

### Description of the drawings

**[0013]** In the accompanying drawings forming a material part of this description, there is shown:

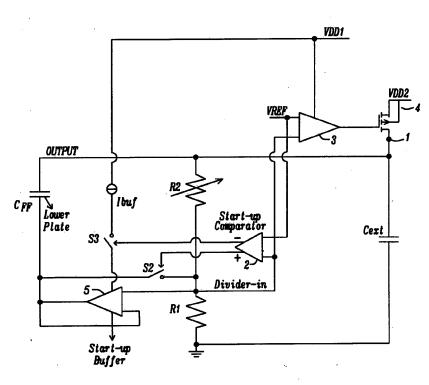

**Fig. 1** shows the basic elements of a second embodiment of a start-up circuit of the present disclosure applied to a LDO.

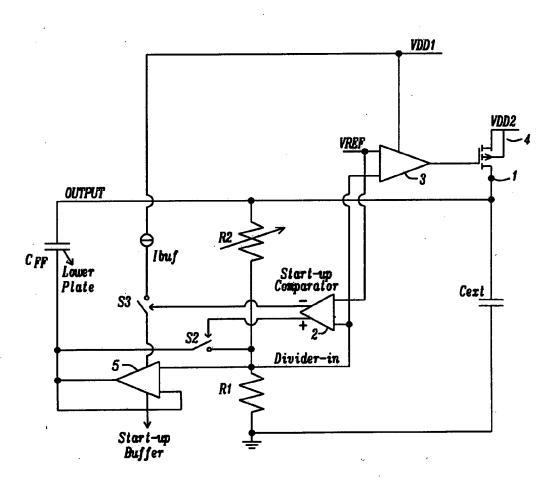

**Fig.** 2 illustrates a third embodiment of a start-up circuit of the present disclosure applied to a LDO.

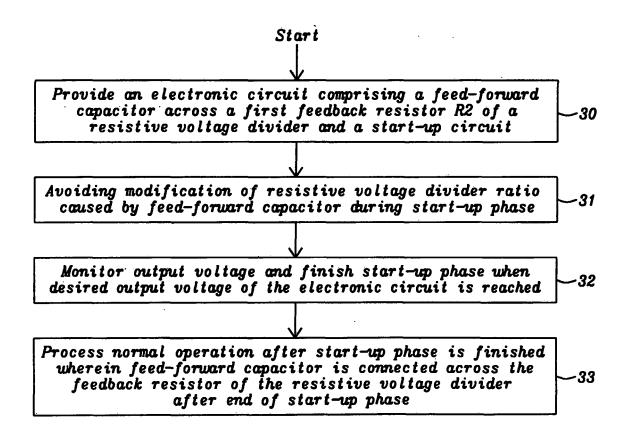

**Fig. 3** illustrates a flowchart of a method to maintain a resistive voltage divider ratio during start-up of an electronic circuit comprising a feed-forward capacitor across a feedback resistor using a dynamic start-up circuit.

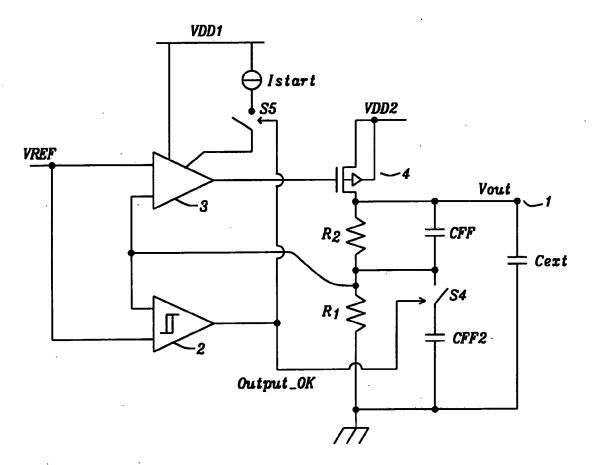

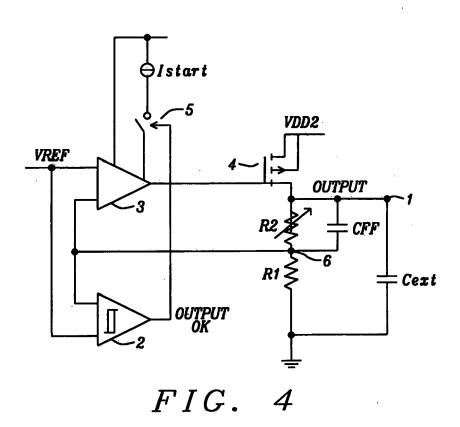

**Fig. 4** shows basic elements of an embodiment of a start-up circuit of the present disclosure applied for example to a LDO.

#### Description of the preferred embodiments

**[0014]** Methods and circuits to achieve fast and clean start-up process of an electronic circuit as e.g. a LDO or an amplifier using a feed-forward capacitor and a resistive voltage divider or another means to represent an output voltage of the electronic circuit are disclosed. It has to be noted that the methods and circuits disclosed can be applied to any other circuits using a feed-forward capacitor and a resistive voltage divider.

[0015] Fig. 4 shows basic elements of an embodiment of a start-up circuit of the present disclosure applied for example to a LDO. The circuit comprises a port for output voltage 1, a resistor voltage divider comprising a first resistor R1 and a second controllable resistor R2, a start-up comparator 2, a differential amplifier 3, having as inputs a reference input voltage V<sub>ref</sub> and the voltage of a voltage access point divider-in 6 of the voltage divider R1/R2, representing the output voltage V<sub>out</sub> of the circuit as input, and a pass transistor 4. During the start-up phase a current source I<sub>START</sub> provides an extra bias current to the differential amplifier 3. A switch 5 opens and hence deactivates the extra bias current I<sub>START</sub> when the start-up phase is finished.

[0016] The output of the start-up comparator 2 indicates that the circuit as e.g. a LDO is now ready for loading, i.e. the output of the comparator 2 triggers interrupting the extra bias current via switch 5.The feed-forward capacitor CFF modifies the resistor divider R1/R2 ratio [0017] The circuit of Fig. 4 may have the following disadvantages:

- 1. Longer startup time

- 2. Startup specifications may not being met

- 3.Incorrect decision by startup comparator about the output voltage which

- may impact system functionality if this output is used to load the output of the circuit

- 4. Drop in voltage of the LDO (brown out).

**[0018]** Fig. 1 shows a second embodiment of a start-up circuit of the present disclosure overcoming the disadvantages cited above. The start-up circuit of Fig. 1 can also be applied for example to a LDO or to other circuits as amplifiers, etc...

**[0019]** The circuit disclosed comprises a port for output voltage **1**, a resistor voltage divider comprising in a preferred embodiment a first resistor **R1** and a second con-

trollable resistor R2, a start-up comparator 2, a differential amplifier 3, having a reference input voltage  $V_{ref}$  and the voltage of a voltage access point divider-in 6 of the voltage divider R1/R2, representing the output voltage  $V_{out}$  of the circuit as input, a start-up buffer 5, and a pass transistor 4.

**[0020]** Each of the resistors **R1** and **R2** could be implemented by more than one resistor in series. Furthermore other resistive means than resistors could be implemented for the voltage divider as well, e.g. transistors (BJT or MOS) or diodes or FETS or MOS transistors connected as diodes.

[0021] The output of the start-up comparator 2, comparing voltage  $V_{ref}$  with the voltage of the voltage access point divider-in 6 of the voltage divider R1/R2, indicates that the circuit, as e.g. a LDO, that a start-up phase is completed and is now ready for loading. The comparator 2 controls the duration of a biasing current  $I_{buf}$  for the start-up buffer 5 via switch S3. Switch S3 opens after start-up is completed, i.e. comparator 2 detects that voltage  $V_{ref}$  is equal to divider-in 6 voltage, switch S3 opens, biasing current  $I_{buf}$  is interrupted and start-up time specification are met.

[0022] Furthermore the circuit comprises a capacitor  $C_{ext}$ , at the output which may be deployed externally or internally to the circuit, and a feed-forward capacitor  $C_{FF}$ , which is connected only after start-up phase is completed in parallel to the controllable resistor R2. Capacitor  $C_{FF}$  is connected in parallel to the controllable resistor R2 via switch S2, which is closed after the start-up phase is completed. The comparator 2 detects when the start-up phase is completed and activates the closing of switch S2.

[0023] Furthermore there may be an optional current source I<sub>start</sub> providing an optional bias current to the differential amplifier 3 during start-up, wherein the optional current source I<sub>start</sub> may be activated by a switch S1, which is used only if the optional extra bias current is to be provided during the startup. Switch S1 is also optional, it is not required if no extra bias current to the amplifier 3 is required during start-up of the circuit. Switch S2 connects, after it is closed when the start-up phase is finished, a voltage access point of the voltage divider R1/R2 to a lower plate of the feed-forward capacitor C<sub>FF</sub>.

[0024] Furthermore it should be noted that voltages VDD1 and VDD2 can be the same or different.

[0025] During startup the switch S3 is closed and switch S2 is open. The open switch S2 disconnects the feed-forward capacitor C<sub>FF</sub> from the resistor divider R1/R2 but the start-up buffer 5 maintains the lower plate of feed-forward capacitor C<sub>FF</sub> to a same potential as the voltage access point divider\_in 6 of the voltage divider R1/R2. Once the output voltage Vout reaches the desired voltage, switch S2 is closed and switch S3 is opened. The start-up buffer is then shut down.

[0026] The start-up buffer 5 is a means to maintain the voltage level of the voltage access point divider\_in 6 of the resistive voltage divider R1/R2 on the feed-forward

capacitor without impacting the voltage divider ratio. Other means could be used for this purpose as well. It has to be noted that the startup buffer 5 consumes power only during the start-up phase of the circuit. It does not add to the guiescent current consumption of the circuit. [0027] Fig. 2 illustrates a third embodiment of a startup circuit of the present disclosure applied to a LDO. Similarly to the circuit shown in Fig. 1 the circuit of Fig. 2 comprises also a differential amplifier 3, a start-up comparator 2, a pass transistor 4, and a voltage divider R1/R2 with a the voltage access point divider\_in 6. The differential amplifier 3 may have a fixed or variable reference voltage as first input and the voltage of the voltage access point divider in 6 as second input. As shown in Fig. 1 the start-up comparator 2 detects when the start-up phase is completed. The resistors R1/R2 may have a fixed resistance, or both a controllable resistance, or a combination thereof.

[0028] This implementation is characterized by having a start-up capacitor  $C_{FF2}$  connected during the start-up phase in series with the feed-forward capacitor  $C_{FF}$  and in parallel to resistor R1, i.e. the resistive voltage divider R1/R2 and the capacitor string  $C_{FF}/C_{FF2}$  are in parallel, while a mid-point of the capacitor string is connected to the voltage access point divider\_in 6 of the resistive divider R1/R2.

[0029] A key point of the circuit of Fig. 2 is that the start-up capacitor  $C_{FF2}$  is disconnected by switch S4 at the end of the start-up phase, which is triggered by the start-up comparator 2.

[0030] The start-up capacitor  $C_{EFF2}$  has a capacitance of  $C_{FF}xR2/R1$ , i.e. the capacitive string has capacitances according to the resistances of the resistive voltage divider R1/R2. Thus  $C_{FF2}$  prevents any modification of the resistive voltage divider ratio by the feed-forward capacitor  $C_{FF}$  during start-up.

[0031] Similarly to the circuit shown in Fig. 1 a start-up comparator 2 monitors if the output voltage has reached a desired level and if the start-up phase is finished and the desired output level has been reached the start-up comparator activates that switch  $\bf S4$  is opened and hence the additional capacitor  $\bf C_{EFF2}$  is disconnected.

[0032] Furthermore there may be an optional current source I<sub>start</sub> providing an optional extra bias current to the differential amplifier 3 during start-up, wherein the optional current source I<sub>start</sub> may be activated by a switch \$5, which is used only if the optional extra bias current is to be provided during the startup to the differential amplifier 3. Switch \$5 is also optional, it is not required if no extra bias current to the amplifier 3 is required during start-up of the circuit.

[0033] The embodiment of Fig. 2 does not require, compared to the circuit of Fig. 1, a start-up buffer amplifier 5 and switches S2 and S3 as shown in Fig. 1, but it requires switch S4 and the additional capacitor  $C_{\text{EFF2}}$ , which will be disconnected by switch S4 after start-up is completed.

[0034] Similarly to the circuit of Fig. 1 the circuit of Fig. 2 may comprise a capacitor  $\mathbf{C}_{\text{ext}}$ , at the output which may be deployed externally or internally to the circuit.

[0035] In alternative embodiments of the circuits of Figs. 1 or Fig. 2 the reference input voltage V<sub>ref</sub>, as shown in Fig. 1 and Fig. 2, may be replaced by a variable voltage Vin or both resistors R1 and R2 are controllable. Alternatively it would be possible to have a fixed resistance for R2 and a controllable resistance for R1.

[0036] Fig. 3 illustrates a flowchart of a method to maintain a resistive voltage divider ratio during start-up of an electronic circuit such as a LDO, amplifier, or buffer comprising a feed-forward capacitor across a feedback resistor using a dynamic start-up circuit. As already mentioned above, the circuit and the method disclosed are applicable to any circuit using a resistive voltage divider and a feed-forward capacitor. Step 30 of the method of Fig. 3 illustrates the provision of e.g. a LDO or any other suitable circuit as e.g. an amplifier comprising a feedforward capacitor across a first feedback resistor R2 of a resistive voltage divider and a start-up circuit. Step 31 depicts avoiding modification of resistive voltage divider ratio caused by feed-forward capacitor during start-up phase. Step 32 illustrates monitoring output voltage and finish start-up-phase when desired output voltage of the electronic circuit is reached. Step 33 shows processing normal operation after start-up phase is finished wherein feed-forward capacitor is connected across the feedback resistor of the resistive voltage after end of start-up phase.

**[0037]** While the disclosure has been particularly shown and described with reference to the preferred embodiments thereof, it will be understood by those skilled in the art that various changes in form and details may be made without departing from the spirit and scope of the disclosure.

#### Claims

30

40

- A method to maintain a resistive voltage divider ratio during start-up of any electronic circuit comprising a feed-forward capacitor across a feedback resistor of a resistive voltage divider using a dynamic start-up circuit, comprising the following steps:

- (1) providing an electronic circuit comprising a feed-forward capacitor across a first feedback resistor of a resistive voltage divider and a startup circuit;

- (2) avoiding modification of resistive voltage divider ratio caused by feed-forward capacitor during start-up phase;

- (3) monitoring output voltage and finish start-upphase when desired output voltage of the electronic circuit is reached; and

- (4) processing normal operation after start-up phase is finished wherein feed-forward capaci-

10

15

20

30

35

40

tor is connected across the feedback resistor of the resistive voltage divider after end of start-up phase.

- 2. The method of claim 1 wherein said electronic circuit is a LDO or an amplifier.

- The method of claim 1 wherein a start-up comparator detects if a desired output voltage is reached and hence the start-up phase is finished.

- 4. The method of claim 3 wherein the start-up comparator detects if the start-up phase is finished by comparing a voltage representing the output voltage of the electronic circuit with a reference voltage, e.g. a variable voltage.

- 5. The method of claim 1 wherein said modification of resistive voltage divider ratio is avoided by disconnecting the feed-forward capacitor from a voltage access point of the resistive voltage divider during start-up phase only, wherein the voltage of the voltage access point of the resistive voltage divider represents the output voltage of the electronic circuit.

- 6. The method of claim 1 wherein a voltage level of the voltage access point of the resistive voltage divider is maintained on the feed-forward capacitor by a start-up buffer during start-up phase, wherein the voltage of the voltage access point of the resistive voltage divider represents the output voltage of the electronic circuit and wherein a bias current of the buffer amplifier is disconnected at the end of the start-up phase, wherein an input of the start-up buffer is connected to the voltage access point of the voltage divider.

- 7. The method of claim 6 wherein a start-up comparator detects if a desired output voltage of the electronic circuit is reached and, in this case, initiates disconnecting the bias current of the start-up buffer and connecting the feed-forward capacitor directly to the voltage access point of the resistive voltage divider.

- 8. The method of claim 1 wherein said modification of resistive voltage divider ratio is prevented by connecting a start-up capacitor across a second resistor of the resistive voltage divider during the start-up phase only, wherein the start-up capacitor has a capacitance of C<sub>FF</sub> x R2/R1, wherein C<sub>FF</sub> is a capacitance of the feed-forward capacitor, R1 is a resistance of the part of the voltage divider between access point and ground and R2 is a resistance of the part of the voltage diver between output voltage and access point.

- 9. The method of claim 8 wherein a start-up comparator detects if a desired output voltage is reached and,

in this case, disconnects the start-up capacitor from the voltage access point of the voltage divider.

- 10. The method of claim 8 wherein the start-up capacitor has a capacitance of C<sub>FF</sub> x R2/R1, wherein C<sub>FF</sub> is a capacitance of the feed-forward capacitor, R1 is a resistance of a part of the voltage divider between a voltage access point of the resistive voltage divider and ground and R2 is a resistance of the part of the voltage divider between output voltage and access point.

- **11.** The method of claim 1 wherein said first feedback resistor is a part of the resistive voltage divider.

- 12. A circuit to maintain a resistive voltage divider ratio during start-up of any electronic circuit comprising a feed-forward capacitor across a feedback resistor and a resistive voltage divider using a dynamic startup circuit, comprising:

- the feed-forward capacitor, wherein a first plate of the feed-forward capacitor is connected to an output port of the circuit and a second plate is connected to a voltage access point of the resistive voltage divider after the start-up phase of the electronic circuit is finished;

- said resistive voltage divider, being connected between an output port of the circuit and ground, comprising the feedback resistor having a resistance R2 connected between the output port of the circuit and the voltage access point inbetween the voltage divider having a fraction of the output voltage and further comprising a second resistor having a resistance R1;

- a start-up comparator detecting if the start-up phase is finished by comparing a voltage representing the output voltage of the electronic circuit with a reference voltage;

- a means to maintain a voltage level of the voltage access point across the feed-forward capacitor during start-up of the circuit, wherein the means to maintain a voltage level of the voltage access point comprises switching means to connect or disconnect components of the circuit at beginning and end of the start-up process, wherein the switching means are activated by the start-up comparator.

- **13.** The circuit of claim 12 wherein said circuit is an LDO or an amplifier.

- **14.** The circuit of claim 12 wherein the end of the startup phase is reached when the voltage of the voltage access point equals a reference voltage, e.g. either a fixed voltage or a variable voltage.

- 15. The circuit of claim 12 wherein said means to main-

tain the voltage level further comprises a buffer amplifier wherein the start-up comparator initiates both connecting a second plate of the feed-forward capacitor to the voltage access point and disconnecting a bias current of the buffer amplifier at the end of the start-up phase using said switching means, wherein an input of the start-up buffer is connected to the voltage access point of the voltage divider.

16. The circuit of claim 15 wherein said switching means comprises a first switching means connecting the second plate of the feed-forward capacitor to the voltage access point at the end of the start-up phase and a second switching means disconnecting the bias current of the buffer amplifier.

17. The circuit of claim 16 wherein said switching means further comprises a third switching means providing an extra bias current to a differential amplifier of the circuit during start-up only.

18. The circuit of claim 12 wherein said means to maintain the voltage level comprises a second capacitor connected between the voltage access point and ground.

19. The circuit of claim 18 wherein the second capacitor has a capacitance  $C = C_{FF}xR2/R1$ , wherein  $C_{FF}$  is the capacitance of the feed-forward capacitor and wherein the start-up comparator initiates disconnecting the second capacitor from the voltage access point via a switching means at the end of the start-up phase.

10

15

20

25

35

40

45

50

FIG. 1

FIG. 2

FIG. 3

# **EUROPEAN SEARCH REPORT**

Application Number EP 13 39 2001

|                                                     | DOCUMENTS CONSID                                                                                                                                                                          | EKED IO BE I         | KELEVANI                                                                                                                                     |                                                                            |                                         |  |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------|--|

| Category                                            | Citation of document with in<br>of relevant pass                                                                                                                                          |                      | ropriate,                                                                                                                                    | Relevant<br>to claim                                                       | CLASSIFICATION OF THE APPLICATION (IPC) |  |

| Х                                                   | US 2011/291636 A1 (<br>1 December 2011 (20<br>* the whole documer                                                                                                                         | 11-12-01)            | [US])                                                                                                                                        | 1-7,<br>12-17                                                              | INV.<br>G05F1/575                       |  |

| Α                                                   | US 7 122 996 B1 (HU<br>17 October 2006 (20<br>* figure 1 *                                                                                                                                |                      | G [GB])                                                                                                                                      | 1-19                                                                       |                                         |  |

| А                                                   | WO 2011/090687 A2 (<br>[US]; IVANOV VADIM<br>TIMOTHY V [U) 28 Ju<br>* figure 2 *                                                                                                          | V [US]; KALT         | HOFF                                                                                                                                         | 8-11,18,<br>19                                                             |                                         |  |

| A                                                   | US 6 208 124 B1 (FU<br>AL) 27 March 2001 (<br>* figures 1,7 *                                                                                                                             |                      | [JP] ET                                                                                                                                      | 1-19                                                                       |                                         |  |

|                                                     |                                                                                                                                                                                           |                      |                                                                                                                                              |                                                                            | TECHNICAL FIELDS                        |  |

|                                                     |                                                                                                                                                                                           |                      |                                                                                                                                              | -                                                                          | SEARCHED (IPC)                          |  |

|                                                     |                                                                                                                                                                                           |                      |                                                                                                                                              |                                                                            |                                         |  |

|                                                     | The present search report has                                                                                                                                                             | oeen drawn up for al | claims                                                                                                                                       |                                                                            |                                         |  |

|                                                     | Place of search                                                                                                                                                                           | · ·                  | pletion of the search                                                                                                                        |                                                                            | Examiner                                |  |

| The Hague                                           |                                                                                                                                                                                           |                      | ne 2013                                                                                                                                      | Ari                                                                        | ias Pérez, Jagoba                       |  |

| X : part<br>Y : part<br>docu<br>A : tech<br>O : non | ATEGORY OF CITED DOCUMENTS ioularly relevant if taken alone ioularly relevant if combined with anot unent of the same category inological background written disclosure rmediate document |                      | T: theory or principle E: earlier patent door after the filing date D: document cited in L: document cited for &: member of the sar document | underlying the in<br>ument, but publis<br>the application<br>other reasons | vention<br>hed on, or                   |  |

#### ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 13 39 2001

5

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

27-06-2013

|--|

| 15 |  |

|----|--|

|    |  |

20

25

30

35

40

45

50

|              | Patent document<br>cited in search report |    | Publication<br>date | Patent family<br>member(s) |                                                                   |               | Publication<br>date                                                |

|--------------|-------------------------------------------|----|---------------------|----------------------------|-------------------------------------------------------------------|---------------|--------------------------------------------------------------------|

|              | US 2011291636                             | A1 | 01-12-2011          | CN<br>JP<br>KR<br>TW<br>US | 102262412<br>2011248869<br>20110131113<br>201217938<br>2011291636 | A<br>A<br>A   | 30-11-2011<br>08-12-2011<br>06-12-2011<br>01-05-2012<br>01-12-2011 |

|              | US 7122996                                | B1 | 17-10-2006          | NON                        | E                                                                 |               |                                                                    |

|              | WO 2011090687                             | A2 | 28-07-2011          | CN<br>JP<br>US<br>WO       | 102822760<br>2013518542<br>2011181258<br>2011090687               | A<br>A1<br>A2 | 12-12-2012<br>20-05-2013<br>28-07-2011<br>28-07-2011               |

|              | US 6208124                                | B1 | 27-03-2001          | NON                        | <br>E                                                             |               |                                                                    |

| D FORM P0459 |                                           |    |                     |                            |                                                                   |               |                                                                    |