## (11) EP 2 775 207 A1

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication: 10.09.2014 Bulletin 2014/37

(51) Int Cl.: F23N 5/24 (2006.01)

(21) Application number: 13158436.9

(22) Date of filing: 08.03.2013

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

Designated Extension States:

**BA ME**

(71) Applicant: Honeywell Technologies Sarl 1180 Rolle (CH)

- (72) Inventors:

- Galeazzi, Daniele 20871 Vimercate, Milan (IT)

- Vegter, Derk

7833 Nieuw-Amsterdam (NL)

- (74) Representative: Sturm, Christoph Quermann - Sturm - Weilnau Patentanwälte Partnerschaft mbB Unter den Eichen 5 65195 Wiesbaden (DE)

## (54) Control circuit for a gas valve

(57)Control circuit (10) for a gas valve, the control circuit (10) comprising in-put contacts (14, 21) by which the control circuit is connectable to a microprocessor, output contacts (31, 32) by which the control circuit is connectable to the gas valve to be operated, a drive circuit (11) and a fail-safe circuit (12), wherein the drive circuit (11) comprises a first transistor (19) and a second transistor (20) both being operated through the fail-safe circuit (12) on basis of a first signal provided by the microprocessor. The first signal is provided by the microprocessor at a first input contact (21) of the control circuit, namely at an input contact (21) of the fail-safe circuit (12). A first parallel connection of a resistor (33), a capacitor (34) and a first and a second diode (35, 36) being serially connected is connected between the gate and the source of the first transistor (19). A second parallel connection of a resistor (33), a capacitor (34) and a first and a second diode (35, 36) being serially connected is connected between the gate and the source of the second transistor (20). A first series connection (37) having a resistor (38) and a capacitor (39) is connected with a first contact point between the first diode (35) and the second diode (36) assigned to the first transistor (19) and with a second contact point to a first output contact (27) of the fail-safe circuit (12). A second series connection (40) having a resistor (38) and a capacitor (39) is connected with a first contact point between the first diode (35) and the second diode (36) assigned to the second transistor (20) and with a second contact point to the first output contact (27) of the fail-safe circuit (12). A series connection of the first transistor (19) and the second tran-sistor (20) is connected between a power supply contact (18) and a sec-ond output contact (28) of the fail-safe circuit (12).

30

#### Description

**[0001]** The present patent application relates to a control circuit for a gas valve.

**[0002]** Automatic control for a gas valve needs to be fail safe. If an automatic control is based on a microprocessor, an additional fail-safe watchdog makes the total control fail safe. In case of any failure the gas valve shall stop in a safe status, meaning that the gas valve shall not open and shall not be ignited.

[0003] EP 1 730 760 B1 discloses a control circuit for a gas valve. The control circuit according to EP 1 730 760 B1 comprises an input contact by which the control circuit is connectable to a microprocessor, output contacts by which the control circuit is connectable to the gas valve to be operated, a drive circuit and a fail-safe circuit. The microprocessor is connectable to an input contact of the control signal, namely to an input contact of the fail-safe circuit, whereby the fail-safe circuit can only open the gas valve when an input signal having at least two different frequency signals succeeding each other in time is provided at the input contact of the fail-safe circuit. The drive circuit of the control circuit known from EP 1 730 760 B1 comprises two Darlington transistor circuits.

**[0004]** Another control circuit for a gas valve comprises an input contact by which the control circuit is connectable to a microprocessor, output contacts by which the control circuit is connectable to the gas valve to be operated, a drive circuit and a fail-safe circuit is known from EP 1 730 432 A1. The fail-safe circuit of the control circuit of EP 1 730 432 A1 is almost identical to the fail-safe circuit of the control circuit of EP 1 730 760 B1. The drive circuit of the control circuit known from EP 1 730 432 A1 comprises a comparator and a transistor.

**[0005]** Against this background, a novel control circuit for a gas valve is provided. The control circuit is defined in the claim 1.

**[0006]** The drive circuit of the control circuit comprises at least two transistors.

**[0007]** A first parallel connection of a resistor, a capacitor and a first and a second diode being serially connected is connected between the gate and the source of a first transistor.

**[0008]** A second parallel connection of a resistor, a capacitor (and a first and a second diode being serially connected is connected between the gate and the source of a second transistor.

**[0009]** A first series connection having a resistor and a capacitor is connected with a first contact point between the first diode and the second diode assigned to the first transistor and with a second contact point to a first output contact of the fail-safe circuit.

**[0010]** A second series connection having a resistor and a capacitor is connected with a first contact point between the first diode and the second diode assigned to the second transistor and with a second contact point to the first output contact of the fail-safe circuit.

**[0011]** A series connection of the first transistor and the second transistor is connected between a power supply contact and a second output contact of the fail-safe circuit.

**[0012]** The control circuit of the present application is able to withstand failures and guarantees the safety of a gas valve to be operated. Any failure at the microprocessor will stop both transistors driven by the fail-safe circuit.

**[0013]** Preferably, the source of the first transistor is connected to a first output contact of the control circuit, the drain of the second transistor is connected to a second output contact of the control circuit, and the source of the first transistor and the drain of the second transistor are connected to each other through a third diode. The drain of the first transistor is connected directly or indirectly through a third transistor to the power supply contact. The source of the second transistor is connected directly or indirectly through a resistor to the second output contact of fail-safe circuit.

**[0014]** According to an improved development, the drive circuit of the control circuit comprises a third transistor being operated on basis of a second signal provided by the microprocessor, wherein the second signal is different from the first signal. The second signal is provided by the microprocessor at a second input contact of the control circuit, namely at an input contact of the drive circuit. A parallel connection of third and fourth series connections each having a resistor, a fourth diode and a fifth diode is connected between the third transistor and the first out-put contact of the fail-safe circuit. This provides a valve current control.

[0015] Preferably, the first series connection and the second series connection are both connected with the respective second contact point indirectly to the first output contact of the fail-safe circuit, namely in such a way that the second contact point of the first series connection is connected between the fourth diode and the fifth diode of the third series connection being connected between the third transistor and a first output contact of the fail-safe circuit, and that the second contact point of the second series is connected between the fourth diode and the fifth diode of the fourth series connection being connected between the third transistor and a first output contact of the fail-safe circuit.

**[0016]** Preferred developments of the invention are provided by the dependent claims and the description which follows. Exemplary embodiments are explained in more detail on the basis of the drawing, in which:

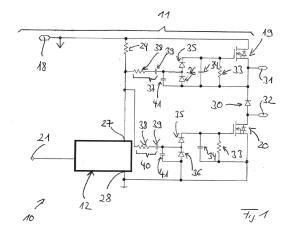

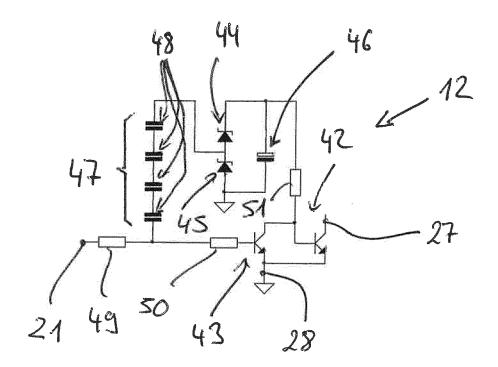

- Figure 1 shows a control circuit for operating a gas valve;

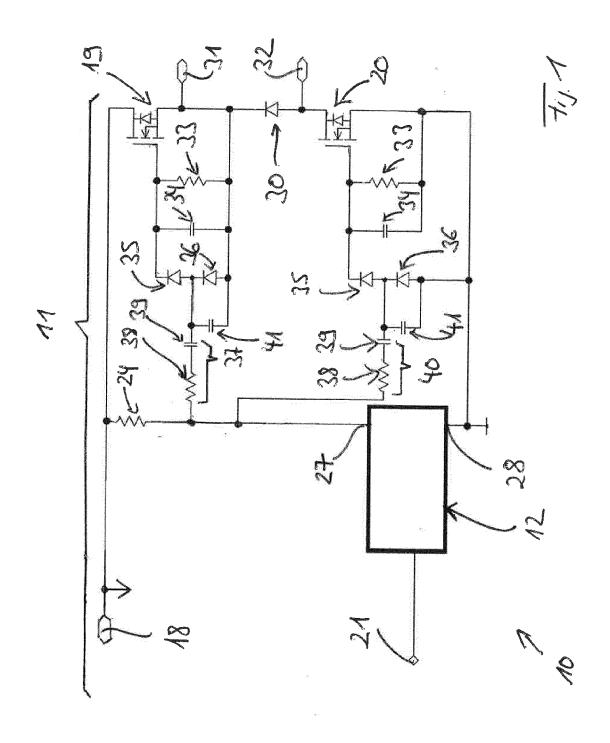

- Figure 2 shows another control circuit for operating a gas valve;

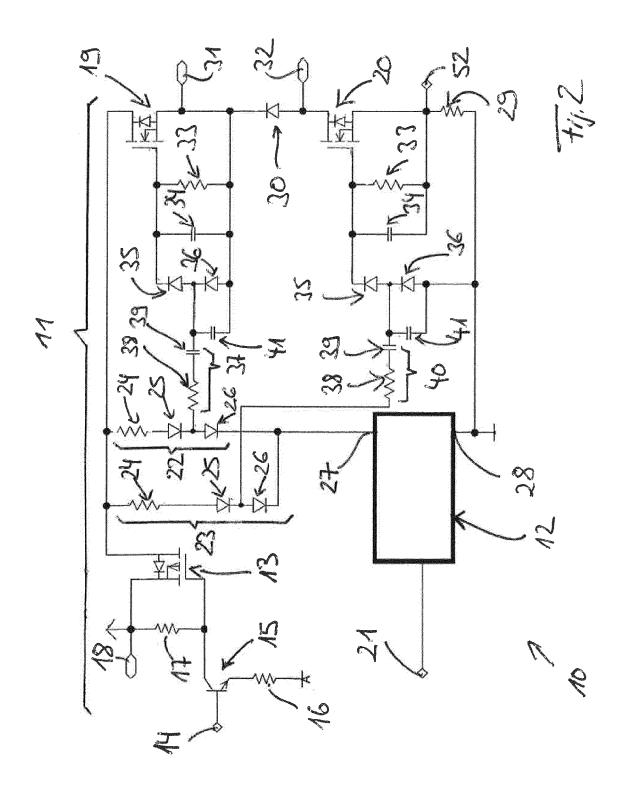

- Figure 3 shows another control circuit for operating a gas valve; and

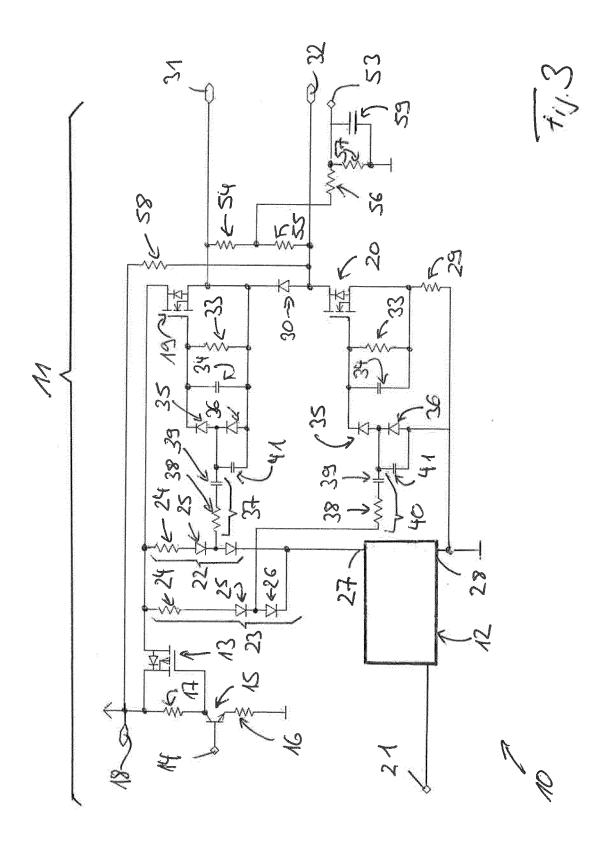

- Figure 4 shows details of a preferred fail-safe circuit for the control circuits of figures 1, 2 and 3.

[0017] The present patent application relates to control circuit 10 for a gas valve.

**[0018]** The control circuit 10 comprises input contacts by which the control circuit 10 is connectable to a microprocessor, output contacts by which the control circuit 10 is connectable to the gas valve to be operated, a drive circuit 11 and a fail-safe circuit 12. The fail-safe circuit is also often called watchdog circuit.

**[0019]** The drive circuit 11 of the control circuit 10 comprises a first transistor 19 and a second transistor 20. The first transistor 19 and the second transistor 20 are both operated through the fail-safe circuit 12 on basis of a first signal provided by the microprocessor.

**[0020]** The first signal contains two signal components, namely a high-frequency signal component having a first duty cycle and a low-frequency signal component having a second duty cycle. The first duty cycle and the second duty cycle are preferably the same.

[0021] The first signal is provided by the microprocessor at a first input contact 21 of the control circuit 10, namely at an input contact 21 of the fail-safe circuit 12. [0022] The first transistor 19 and a second transistor 20 are both provided by MOSFET transistors.

**[0023]** A first parallel connection having a resistor 33, a capacitor 34 and a first and a second diode 35, 36 being serially connected is connected between the gate and the source of the first transistor 19.

**[0024]** The first and the second diode 35, 36 of the first parallel connection are serially connected in such a way that the cathode of the first diode 35 is connected to gate of the first transistor 19, that the anode of the first diode 35 is connected to the cathode of the second diode 36, and that the anode of the second diode 36 is connected to the source of the first transistor 19.

**[0025]** A second parallel connection also having a resistor 33, a capacitor 34 and a first and a second diode 35, 36 being serially connected is connected between the gate and the source of the second transistor 20.

**[0026]** The first and the second diode 35, 36 of the second parallel connection are serially connected in such a way that the cathode of the first diode 35 is connected to gate of the second transistor 20, that the anode of the first diode 35 is connected to the cathode of the second diode 36, and that the anode of the second diode 36 is connected to the source of the second transistor 20.

[0027] A first series connection 37 having a resistor 38 and a capacitor 39 is connected with a first contact point between the first diode 35 and the second diode 36 assigned to the first transistor 19 and with a second contact point to a first out-put contact 27 of the fail-safe circuit 12. A further capacitor 41 is connected in parallel to one of the diodes of the first parallel connection, namely in parallel to the second diode 36.

[0028] A second series connection 40 also having a resistor 38 and a capacitor 39 is connected with a first contact point between the first diode 35 and the second diode 36 assigned to the second transistor 20 and with a second contact point to the first output contact 27 of

the fail-safe circuit 12. Another further capacitor 41 is connected in parallel to the fifth diode 36 of the second parallel connection.

**[0029]** The drain of the first transistor 19 is according to the embodiment of Figure 1 directly connected to a power supply contact 18.

**[0030]** The source of the of the second transistor 20 is according to the embodiment of Figure 1 directly connected to a second output contact 28 of the fail-safe circuit 12, wherein the second output contact 28 of the fail-safe circuit 12 is connected to ground.

**[0031]** The source of the first transistor 19 is connected to the drain of the second transistor 20 through a third diode 30, wherein the anode of the third diode 30 is connected to the drain of the of the second transistor 20 and wherein the cathode of the third diode 30 is connected to the source of the first transistor 19.

**[0032]** The source of the first transistor 19 is connected to a first output contact 31 of the control circuit and the drain of the second transistor 20 is connected to a second output contact 32. The gas valve to be operated is connectable to these output contacts 31 and 32.

[0033] According to the embodiment of Figure 1, a resistor 24 is connected between the first output contact 27 of the fail-safe circuit 12 and power supply contact 18. [0034] As mentioned above, the microprocessor provides the first signal at the input contact 21. The signal provided at the input contact 21 comprises the high-frequency (e.g. 1 MHz) signal component and the low-frequency (e.g. 4 kHz) signal component. The high-frequency signal component has the first duty cycle and the lowfrequency signal component having the second duty cycle. The first duty cycle and the second duty cycle of the two signal components of the first signal provided at the input contact 21 are non-variable. The first duty cycle and the second duty cycle of the two signal components of the first signal are preferably each 50%, meaning that the high-frequency signal component and the low-frequency signal component of the first signal are responsively present for a defined time period and responsively disappear for the same time period.

**[0035]** E.g. the first signal provided by the microprocessor at the input contact 21 comprises for a 11 msec the high-frequency signal component with a frequency of e.g. 1 MHz, thereafter the for 11 msec the low-frequency signal component with a frequency of e.g. 4 kHz, thereafter for 11 msec the high-frequency signal component with the frequency of e.g. 1 MHz, and so on. The high-frequency signal component and the low-frequency signal component succeed each other in time.

[0036] An improved further development of the drive circuit 11 of Figure 1 is shown in Figure 2. The drive circuit 11 of Figure 1 comprises a third transistor 13. According to the embodiment of Figure 2, the drain of the first transistor 19 is indirectly connected to the power supply contact 18 through said third transistor 13. The drive circuit 11 of Figure 2 comprises a series connection of three transistors, namely of the transistors 13, 19 and 20.

[0037] The third transistor 13 of the drive circuit 11 according to Figure 2 is operated on basis of a second signal provided by the microprocessor, wherein the second signal is provided by the microprocessor at a second input contact 14 of the control circuit 10, namely at an input contact 14 of the drive circuit 11.

**[0038]** The second signal provided by the microprocessor at the second input contact 14 is different from the first signal provided by the microprocessor at the first input contact 21. The second signal provided by the microprocessor at the second input contact 14 has a third frequency and a third duty cycle.

**[0039]** The third frequency (e.g. 32 kHz) of the second signal provided at the second input contact 14 is independent from the two frequencies of the two signal components of the first signal provided at the first input contact 21. Preferably, the third frequency of the second signal is between the two frequencies of the two signal components of the first signal. This ensures that the switching of transistor 13 is in an inaudible area.

[0040] However, it is also possible that the third frequency of the second signal is not between the two frequencies of the two signal components of the first signal.

[0041] The third duty cycle of the second signal provided at the second input contact 14 is variable. The second signal is shifted from the second input contact 14 to the third transistor 13 by a fourth transistor 15 of the drive circuit 11

**[0042]** As shown in Figure 2, the fourth transistor 15 is provided by a NPN transistor and the third transistor 13 is provided by a P-MOSFET transistor.

**[0043]** The second input contact 14 is connected to the basis of the fourth transistor 15. The collector of the fourth transistor 15 is connected to the gate of the third transistor 13. The emitter of the fourth transistor 15 is connected to ground through a resistor 16.

**[0044]** The collector of the fourth transistor 15 and the source of the third transistor 13 are both connected to the power supply contact 18, namely the source of the third transistor 13 directly and the collector of the fourth transistor 15 through a resistor 17. The drain of the third transistor 13 is connected to the drain of the first transistor 19.

**[0045]** A series connection of the first transistor 19 and the second transistor 20 is connected between the third transistor 13 and the second output contact 28 of the fail-safe circuit 12.

[0046] A parallel connection of third series connection 22 and fourth series connection 23 each having a resistor 24, a fourth diode 25 and a fifth diode 26 is connected between the third transistor 13 and a first output contact 27 of the fail-safe circuit 12.

[0047] Each resistor 24 of both series connections 22 and 23 is connected to the drain of the third transistor 13 being a P-MOSFET transistor. The diodes 25, 26 of each series connection 22, 23 are connected in such a way between the resistor 24 of the respective series connection 22, 23 and the first output contact 27 of the fail-safe

circuit 12, that the anode of a fourth diode 25 is connected to the resistor 24, that the cathode of the fourth diode 25 is connected to the anode of a fifth diode 26, and that the cathode of the fifth diode 26 is connected to the first output contact 27 of the fail-safe circuit 12.

**[0048]** The second contact point of the first series connection comprising the resistor 38 and the capacitor 39 is connected between the fourth diode 25 and the fifth diode 26 of the third series connection 22 being connected between the first transistor 13 and a first output contact 27 of the fail-safe circuit 12.

**[0049]** The second contact point of the second series comprising the resistor 38 and the capacitor 39 is connected between the fourth diode 25 and the fifth diode 26 of the fourth series connection 23 being connected between the first transistor 13 and a first output contact 27 of the fail-safe circuit 12.

**[0050]** According to Figure 2, a resistor 29 is preferably connected between ground and the source of the second transistor 20. Between the resistor 29 and the source of the second transistor 20 there is an output contact 52 by which the drive circuit 11 is connectable to the microprocessor which provides the signals at the input contacts 14 and 21. It is thereby possible to provide a feedback signal to the microprocessor.

**[0051]** The microprocessor being connectable to the input contacts 14, 21 generates two independent control signals.

**[0052]** The first control signal provided at the first input contact 21 drives the transistors 19 and 20 via the fail safe circuit 12. The second control signal provided at the second input contact 14 drives the third transistor 13.

**[0053]** A failure will drive one transistor of the transistors 13, 19 and 20 in conduction or short. The gas valve to be operated cannot be energized.

**[0054]** The third transistor 13 is driven like a switching device at a defined frequency and variable duty cycle. The duty cycle is defined to provide the output current needed to operate the gas valve. The fail-safe circuit 12 is provided with the first input signal.

[0055] The diode arrays provided by the diodes 35 and 36 force to charge and to discharge of the capacitors 39. The charge of the capacitors 39 is initiated by the third transistor 19. The discharge of the capacitors 39 is initiated by the fail-safe circuit 12. The capacitors 41, in combination with resistors 38, limit the bandwidth of the charging/discharging signal.

**[0056]** The capacitors 34, in combination with resistors 33, assure that the transistors 19, 20 are switched on for a defined time. The resistor 29 changes the current of the output into a voltage feedback.

**[0057]** The duty cycle of the signal provided by the microprocessor at the input contact 14 controls the electrical current at the output contacts 31 and 32. The resistor 29 provides a feedback signal at the output 52 for the microprocessor.

[0058] This feedback signal is used by the microprocessor to adapt the variable duty cycle of the signal pro-

40

vided at the first input contact 14 and thereby to adapt the electrical current at the output contacts 31 and 32. This feedback signal can also used to detect a failure in the circuit that drives the third transistor 13.

**[0059]** A further improved development of the drive circuit 11 of Figure 1 and 2 is shown in Figure 3. The additional details shown in Figure 3 allow a safety check of the transistors 13, 19 and 20.

**[0060]** As shown in Figure 3, the further improved drive circuit 11 comprises a further contact 53 for performing the safety check of the transistors 13, 19 and 20 in a standby mode in which no electrical current is provided to the gas valve being connected to the output contacts 31 and 32.

**[0061]** A series connection of two resistors 54 and 55 is connected between the two output contacts 31 and 32, whereby another resistor 56 is connected with a first contact point to the contact 53 and with a second contact point between the two resistors 54 and 55.

**[0062]** A parallel connection of another resister 57 and a capacitor 59 is connected between the contact 53 and ground, whereby the resistor 56 and the parallel connection of the resister 57 and the capacitor 59 is connected in series with reference to ground. The output contact 32 being connected to the drain of the second transistor 20 is connected to the power supply contact 18 through another resistor 58. The embodiment of Figure 3 comprises the additional resistors and an additional capacitor.

**[0063]** The safety check of the transistors 13, 19 and 20 can be done as follows:

**[0064]** First, in the standby mode the power supply provided at power supply contact 18 is measured at the contact 53 using the resistors 58, 54, 55, 56 and 59. The voltage at contact 53 must have a defined value. The second transistor 20 can then be checked because if the same is shorted the output voltage is zero. The power signal provided at power supply contact 18 can then also be checked.

[0065] Second, in the standby mode the third transistor 13 is periodically switched on by the second input signal provided at the second input contact 14. The first transistor 19 can then be checked because if it is shorted the voltage at contact 53 becomes almost 2 times the voltage being present at contact 53 the when second transistor is shorted.

[0066] Third, in the standby mode the transistor 42 of the fail-safe circuit 12 (see Figure 4) is periodically switched on by the first signal provided at the first input contact 21 with a duty of 0%. The first and second transistors 19 and 20 are decoupled by capacitor 39 and they are still not conducting. Due to partial conduction of first transistor 19, by the parallel diode in the bulk of transistor 19, drains the current to the collector of the transistor 42 of the fail-safe circuit 12, the voltage at the drain of the transistor 13 drops, and the voltage at contact 53 has have a defined value. Then, the third transistor 13 can be checked. A non-compliant safety check will lead to lock-out.

**[0067]** So, in the embodiment of Figure 3 the transistors 13, 19 and 20 can be checked by means of a single signal in a standby mode and by means of a current controlled mechanism in the operational mode. In a reverse conduction by a resistor, an intrinsic or external diode, power for the safety check is provided at the first transistor 19 being in the middle of the series connection of three transistors 13, 19 and 20.

**[0068]** Figure 4 shows an exemplary embodiment for the fail-safe circuit 12. The fail-safe circuit 12 shown in Figure 2 is known from EP 1 730 760 B1. The same comprises two transistors 42 and 43, two diodes 44 and 45, a capacitor 46 connected in parallel to the two diodes 44 and 45, a series connection 47 of further capacitors 48 and resistors 49, 50 and 51. The two resistors 49, 50 and connected between the input contact 21 of the fail-safe circuit 12 and the base of the input transistor 43. The collector of the input transistor 43 is connected to the base of the output transistor 42.

**[0069]** The emitter of the input transistor 43 and the emitter of the output transistor 42 are both connected to ground providing the second output 28 of the fail-safe circuit 12.

**[0070]** The collector of the output transistor 42 provides the first output 27 of the fail-safe circuit 12. Other fail-safe circuits 12 can be used in connection with the above described drive circuit 11 for providing the control circuit 10.

0 List of reference signs

10

#### [0071]

|      | 10 | control circuit                     |

|------|----|-------------------------------------|

| 35   | 11 | drive circuit                       |

|      | 12 | fail-safe circuit                   |

|      | 13 | transistor                          |

|      | 14 | input contact                       |

| 40   | 15 | transistor                          |

| 40   | 16 | resistor                            |

|      | 17 | resistor                            |

|      | 18 | power supply contact                |

|      | 19 | transistor                          |

| 45   | 20 | transistor                          |

|      | 21 | input contact                       |

|      | 22 | series connection                   |

|      | 23 | series connection                   |

| F.O. | 24 | resistor                            |

| 50   | 25 | diode                               |

|      | 26 | diode                               |

|      | 27 | output contact of fail-safe circuit |

|      | 28 | output contact of fail-safe circuit |

| 55   | 29 | resistor                            |

|      | 30 | diode                               |

|      | 31 | output contact                      |

|      |    |                                     |

control circuit

10

15

20

30

35

40

45

#### (continued)

- 32 output contact

- 33 resistor

- 34 capacitor

- 35 diode

- 36 diode

- 37 series connection

- 38 resistor

- 39 capacitor

- 40 series connection

- 41 capacitor

- 42 transistor

- 43 transistor

- 44 diode

- 45 diode

- 46 capacitor

- 47 series connection

- 48 capacitors

- 49 resistor

- 50 resistor

- 51 resistor

- 52 output contact

- 53 contact

- 54 resistor

- 55 resistor

- 56 resistor

- 57 resistor

- 58 resistor

- 59 capacitor

#### Claims

1. Control circuit (10) for a gas valve, the control circuit (10) comprising an input contact (14, 21) by which the control circuit is connectable to a microprocessor, an output contact (31, 32) by which the control circuit is connectable to the gas valve to be operated, a drive circuit (11) and a fail-safe circuit (12), wherein the drive circuit (11) comprises a first transistor (19) and a second transistor (20) both being operated through the fail-safe circuit (12) on basis of a first signal provided by the microprocessor, and wherein the first signal is provided by the microprocessor at a first input contact (21) of the control circuit, namely at an input contact (21) of the fail-safe circuit (12), characterized in that

a first parallel connection of a resistor (33), a capacitor (34) and a first and a second diode (35, 36) being serially connected is connected between the gate and the source of the first transistor (19),

a second parallel connection of a resistor (33), a capacitor (34) and a first and a second diode (35, 36) being serially connected is connected between the

gate and the source of the second transistor (20), a first series connection (37) having a resistor (38) and a capacitor (39) is connected with a first contact point between the first diode (35) and the second diode (36) assigned to the first transistor (19) and with a second contact point to a first output contact (27) of the fail-safe circuit (12),

a second series connection (40) having a resistor (38) and a capacitor (39) is connected with a first contact point between the first diode (35) and the second diode (36) assigned to the second transistor (20) and with a second contact point to the first output contact (27) of the fail-safe circuit (12),

a series connection of the first transistor (19) and the second transistor (20) is connected between a power supply contact (18) and a second output contact (28) of the fail-safe circuit (12).

- 2. Control circuit of claim 1 characterized in that the first signal provided by the microprocessor comprises a high-frequency signal component having a first duty cycle and a low-frequency signal component having a second duty cycle.

- 25 3. Control circuit of claim 1 or 2, characterized in that a capacitor (41) is connected in parallel to one of the diodes of the first parallel connection, and that another capacitor (41) is connected in parallel to one of the diodes of the second parallel connection.

- 4. Control circuit of one of claims 1 to 3, characterized in that

the source of the first transistor (19) is connected to a first output contact (31) of the control circuit, the drain of the second transistor (20) is connected to a second output contact (32) of the control circuit, the source of the first transistor (19) and the drain of the second transistor (20) are connected to each other through a third diode (30).

5. Control circuit of one of claims 1 to 4, **characterized** in that

the drain of the first transistor (19) is connected directly or indirectly through a third transistor (13) to the power supply contact (18),

the source of the second transistor (20) is connected directly or indirectly through a resistor (29) to the second output contact (28) of fail-safe circuit (12).

- 60 6. Control circuit of one of claims 1 to 5, characterized in that the first series connection (37) and the second series connection (40) are both connected with the respective second contact point directly to the first output contact (27) of the fail-safe circuit.

- 7. Control circuit of one of claims 1 to 5, **characterized by** a third transistor (13) of the drive circuit (11) being operated on basis of a second signal provided by

6

10

30

40

45

the microprocessor,

wherein the second signal is different from the first signal,

wherein the second signal is provided by the microprocessor at a second input contact (14) of the control circuit (10), namely at an input contact (14) of the drive circuit (11),

wherein a parallel connection of third and fourth series connections (22, 23) each having a resistor (24), a fourth diode (25) and a fifth diode (26) is connected between the third transistor (13) and the first output contact (27) of the fail-safe circuit (12).

8. Control circuit of claim 7, characterized in that the first series connection (37) and the second series connection (40) are both connected with the respective second contact point indirectly to the first output contact (27) of the fail-safe circuit, namely in such a way that

the second contact point of the first series connection is connected between the fourth diode (25) and the fifth diode (26) of the third series connection (22) being connected between the third transistor (13) and a first output contact (27) of the fail-safe circuit, the second contact point of the second series is connected between the fourth diode (25) and the fifth diode (26) of the fourth series connection (23) being connected between the third transistor (13) and a first output contact (27) of the fail-safe circuit.

- 9. Control circuit of claim 7 or 8, characterized in that the second signal has a third frequency and a third duty cycle, wherein the third frequency of the second signal is independent from the frequency of highfrequency signal component of the first signal and independent from the frequency of low-frequency signal component of the first signal.

- 10. Control circuit of one of claims 7 to 9, characterized in that third duty cycle is variable while the first duty cycle and the second duty cycle are both non-variable.

- 11. Control circuit of one of claims 7 to 10, **characterized** in that the second signal is shifted from the second input contact (14) to the third transistor (13) by a fourth transistor (15) of the drive circuit (11).

- **12.** Control circuit of one of claims 7 to 11, **characterized by** another contact (53) for performing a safety check of the first, second and third transistors (13, 19, 20).

- 13. Control circuit of claim 12, **characterized in that** a series connection of two resistors (54, 55) is connected between the output contacts (31, 32) whereby another resistor (56) is connected with a first contact point to the contact (53) and with a second contact point between the resistors (54, 55) being in se-

ries connection between the output contacts, wherein a parallel connection of another resister (57) and a capacitor (59) is connected between the contact (53) and ground, and whereby one of the output contacts (32) is connected to the power supply contact (18) through another resistor (58).

**14.** Control circuit of one of claims 1 to 13, **characterized in that** the output contacts (27, 28) of the fail-safe circuit (12) are provided by an output transistor (42) of the fail-safe circuit (12).

Fy. 4

## **EUROPEAN SEARCH REPORT**

Application Number EP 13 15 8436

| ı                                                     | DOCUMENTS CONSID                                                                                                                                                                                       | ]                                                                                            |                                                                                                                                                                                                                                                                   |                                         |  |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|

| Category                                              | Citation of document with in of relevant pass                                                                                                                                                          | ndication, where appropriate,<br>ages                                                        | Relevant<br>to claim                                                                                                                                                                                                                                              | CLASSIFICATION OF THE APPLICATION (IPC) |  |

| A                                                     | US 4 865 538 A (SCH<br>AL) 12 September 19<br>* the whole documer                                                                                                                                      |                                                                                              | 1-14                                                                                                                                                                                                                                                              | INV.<br>F23N5/24                        |  |

| A,D                                                   | EP 1 730 760 B1 (HC<br>SARL [CH]) 28 July<br>* figures *                                                                                                                                               | NEYWELL TECHNOLOGIES<br>2010 (2010-07-28)                                                    | 1-14                                                                                                                                                                                                                                                              |                                         |  |

| A,D                                                   | EP 1 730 432 A1 (HC SARL [CH]) 13 Decen * figures *                                                                                                                                                    | DNEYWELL TECHNOLOGIES aber 2006 (2006-12-13)                                                 | 1-14                                                                                                                                                                                                                                                              | TECHNICAL FIELDS SEARCHED (IPC) F23N    |  |

|                                                       |                                                                                                                                                                                                        |                                                                                              | -                                                                                                                                                                                                                                                                 |                                         |  |

|                                                       | The present search report has                                                                                                                                                                          |                                                                                              |                                                                                                                                                                                                                                                                   |                                         |  |

|                                                       | Place of search                                                                                                                                                                                        | Date of completion of the search                                                             |                                                                                                                                                                                                                                                                   | Examiner Mayor                          |  |

|                                                       | The Hague                                                                                                                                                                                              | 10 July 2013                                                                                 |                                                                                                                                                                                                                                                                   | egeman, Marc                            |  |

| X : parti<br>Y : parti<br>docu<br>A : tech<br>O : non | ATEGORY OF CITED DOCUMENTS<br>oularly relevant if taken alone<br>oularly relevant if combined with anot<br>ment of the same category<br>nological background<br>written disclosure<br>mediate document | E : earlier patent do<br>after the filing de<br>her D : document cited<br>L : document cited | T : theory or principle underlying the invention E : earlier patent document, but published on, or after the filing date D : document cited in the application L : document cited for other reasons  & : member of the same patent family, corresponding document |                                         |  |

EPO FORM 1503 03.82 (P04C01)

### ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 13 15 8436

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

10-07-2013

|            | Patent document cited in search report |        | Publication<br>date | Patent family<br>member(s)                                                                                | Publication<br>date                                                                            |

|------------|----------------------------------------|--------|---------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|            | US 4865538                             | Α      | 12-09-1989          | NONE                                                                                                      |                                                                                                |

|            | EP 1730760                             | B1     | 28-07-2010          | AT 475981 T<br>EP 1730760 A1<br>EP 2180493 A1<br>US 2007159761 A1<br>WO 2005098888 A1                     | 15-08-2010<br>13-12-2006<br>28-04-2010<br>12-07-2007<br>20-10-2005                             |

|            | EP 1730432                             | <br>A1 | 13-12-2006          | AT 373794 T DE 102004016764 B3 EP 1730432 A1 ES 2293544 T3 PT 1730432 E US 2008042085 A1 WO 2005098292 A1 | 15-10-2007<br>08-09-2005<br>13-12-2006<br>16-03-2008<br>30-11-2007<br>21-02-2008<br>20-10-2005 |

|            |                                        |        |                     |                                                                                                           |                                                                                                |

|            |                                        |        |                     |                                                                                                           |                                                                                                |

|            |                                        |        |                     |                                                                                                           |                                                                                                |

|            |                                        |        |                     |                                                                                                           |                                                                                                |

|            |                                        |        |                     |                                                                                                           |                                                                                                |

| FORM P0459 |                                        |        |                     |                                                                                                           |                                                                                                |

$\stackrel{ ext{O}}{\overset{ ext{D}}{\text{H}}}$  For more details about this annex : see Official Journal of the European Patent Office, No. 12/82

## EP 2 775 207 A1

#### REFERENCES CITED IN THE DESCRIPTION

This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.

## Patent documents cited in the description

• EP 1730760 B1 [0003] [0004] [0068]

• EP 1730432 A1 [0004]