### (11) **EP 2 833 333 A1**

(12)

### **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

04.02.2015 Bulletin 2015/06

(51) Int Cl.:

G08B 25/04 (2006.01) H04R 29/00 (2006.01) G08B 29/06 (2006.01)

(21) Application number: 13178845.7

(22) Date of filing: 31.07.2013

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

Designated Extension States:

**BA ME**

(71) Applicant: Honeywell Life Safety Austria GmbH 1230 Wien (AT)

(72) Inventors:

- Nejedly, Andreas 41469 Neuss (DE)

- Schreiner, Josef 41469 Neuss (DE)

- Reither, Robert 41469 Neuss (DE)

- Mueller, Thomas 41469 Neuss (DE)

- (74) Representative: Henkel, Breuer & Partner Patentanwälte

Maximiliansplatz 21

80333 München (DE)

### Remarks:

Amended claims in accordance with Rule 137(2) EPC.

### (54) Bus system and method for operating a bus system

(57) The present invention is directed to a method and a system for operating a bus system. The bus system comprises at least two bus lines formed as respective loops, a plurality of switching elements  $5_1$  to  $5_n$  connected in series so as to divide one of the bus lines in a plurality of sections, a central control unit 7 connected with the ends of the bus lines 1, 3, and a plurality of bus devices  $9_1$  to  $9_m$  connected in parallel between the two bus lines 1, 3 and distributed along the bus lines 1, 3 so that a bus device  $9_y$  is interposed between two consecutive switching elements  $5_x$ ,  $5_{x+1}$ . The method comprise applying a

supply voltage to both ends of the bus lines 1, 3 starting from terminals A, B of the central processing unit 7 and closing the switching elements  $5_1$ ,  $5_n$  upon reception of the supply voltage, so as to connect the subsequent respective sections of the bus from both ends, until all switching elements  $5_1$ ,  $5_2$ ,  $5_3$ ,  $5_4$ , ...  $5_n$  are closed or until a short circuit is detected. If a short circuit is detected, the last two switching elements closed before detecting the short circuit will be re-opened and the connection of the bus devices will continue only from one side, either terminal A side or terminal B side.

25

35

40

45

#### Description

**[0001]** The present invention is directed to a bus system and to a method for operating such a bus system.

1

**[0002]** Bus systems are used in fire detection and alarming installations in buildings, where a two-wired bus is used to supply power and communication to a plurality of bus devices connected in parallel to each other between two of the bus lines.

**[0003]** It is well-known to form these bus lines into a loop starting and ending at a central control unit. Such a bus system is known for example from DE 102010047220.

**[0004]** If a short circuit arises along a bus line or in a bus device, in case of forming the bus lines into a loop it is possible to isolate a short circuit and to operate the system now as two branch lines, each starting at the central control unit and ending immediately before the short circuit. In this way, it is possible to preserve the operability of the bus system to a large extent.

**[0005]** Usually, the bus is divided by a plurality of switching elements or interrupters, which might be associated with the bus devices, so as to interrupt or connect a respective bus line. For example, a bus device might have for two switching elements, one on an input side and the other on an output side.

**[0006]** In operation, when a short circuit occurs along a bus line, the supply voltage at the bus drops remarkably and in consequence all switching elements open.

[0007] Subsequently, the central control unit restarts the bus system by applying the supply voltage to the bus line. The first switching element, which is in an open state, will detect the supply voltage and close the switches so as to connect with the bus line. Subsequently, the second switching element will detect the supply voltage and will change in the closed state as well. This process goes on until reaching the short circuit. That is, when closing the switching element immediately before the short circuit, the drop of the voltage will be recognized, and the switching element will open again.

[0008] Subsequently, the central control unit will start to apply the supply voltage to the other branch line that is to other end of the former loop of bus lines and one switching element after the other will close until reaching the short circuit. When closing the switching element immediately before the short circuit, the associated bus device will detect the drop in the voltage and will open this switching element again. At the end, the system will be implemented as two separated branch lines, each extending from the central control unit to the switching element immediately before the short circuit.

**[0009]** One drawback of this configuration is that it might take a long time to restart this system after a short circuit.

**[0010]** In modern fire detector systems implementing this kind of bus configuration some of the bus devices have large capacities, and it might take a long time after closing one switching element before the supply voltage

applies to the next switching element with a necessary level to close the next switching element. The same holds true for voice-operated alarm devices.

[0011] The present invention intends to solve this problem.

**[0012]** According to the present invention there is provided a method for operating a bus system. The bus system comprises at least two bus lines formed as respective loops, a plurality of switching elements connected in series so as to divide one of the bus lines in a plurality of sections, a central control unit connected with the ends of the bus lines and a plurality of bus devices connected in parallel between the two bus lines and distributed along the bus lines, so that a bus device is interposed between two consecutive switching elements.

**[0013]** According to the invention the method comprises the steps of:

- (a) applying a supply voltage to both ends of the bus lines starting from the central processing unit;

- (b) closing the switching elements upon reception of the supply voltage, so as to connect the subsequent respective sections of the bus including the bus devices from both ends;

- (c) monitoring the bus lines 1, 3 in order to detect a first short circuit;

if no first short circuit is detected, repeating steps (a), (b) and (c) until all switching elements are closed or until a first short circuit is detected.

[0014] If a first short circuit is detected, the method comprises:

- (d) opening the two switching elements closed immediately before detecting the first short circuit;

- (e) closing again one of the switching elements opened in step (d);

- (f) monitoring the bus lines in order to detect a second short circuit.

[0015] If a second short circuit is detected:

- (g) opening the switching element closed immediately before detecting the second short circuit and keeping this switching element open and

- (h) closing again the other switching element opened in step (d).

**[0016]** The invention provides the benefit that the system is started from both ends of the bus lines simultaneously, so that the time for connecting all bus devices is reduced to a half.

**[0017]** However, since in this case, when two switching elements - one at each side - close within a short time period and one of them is adjacent to a short circuit, it is not easy to discriminate which of the switching elements closed in the last step is adjacent to the short circuit. The invention therefore proposes the above method, to open

25

35

40

again the last two switching elements closed immediately before detecting the short circuit, and then, with different time periods respectively time delays, closing these switching elements again, so as to surely recognize which of these switching elements is adjacent to the short circuit.

**[0018]** In this way, the reliable and fast recovery of the alarm system in case of a short circuit is possible.

**[0019]** According to a further advantageous aspect of the invention the method comprises an initialization step for setting the time periods for closing each switching element again after the detection of a first short circuit.

**[0020]** Basically, there are various different forms to set these time periods or delay times.

[0021] One advantageous form to set the time periods might be a dedicated time period writing command from the central control unit, which can be used to write a corresponding individual delay time into an internal memory of each switching element or an associated bus device. [0022] A further advantageous system might be to allow the central control unit to run a dedicated initialization sequence that can be used the first time the system is started. In this case, the central control unit would apply the supply voltage only from one end of the bus lines, so that all switching elements are closed one after the other in series. At that occasion the switching elements can recognize the direction from which the voltage is applied, and can store a first delay time for this event. Additionally, the switching elements can store a second delay time, which can be set at a different value, for the case that a supply voltage would be applied from the other direction. [0023] Accordingly, after opening the switching elements upon detection of a first short circuit in step (d), the closing of the switching elements in steps (e) and (h) will be done at a different timings so that it can be identified which one of these switching elements is adjacent to the short circuit.

**[0024]** As a further alternative it might be possible to construct the switching elements by hardware so that they have a dedicated direction of connection with the bus.

**[0025]** Finally it is possible to set individual delay times at random when manufacturing the switching elements. In this way the probability that the two switching elements will close again at the same time can be reduced.

[0026] As a further advantageous aspect of the invention - in a bus system offering an information exchange capability between the switches, bus devices and central control unit, it is possible to register the bus address of the last bus device before the switching elements which remain open. This information can be stored in a memory of the central processing unit and can be used to issue a notification message helping to locate the short circuit.

[0027] According to the invention, furthermore, there is provided a corresponding bus system which is configured to operate according to the above-described method.

[0028] According to another aspect of the invention a

bus device and one or two switching elements are grouped together at the bus unit, which is individually addressable by the central control unit.

**[0029]** A bus device of the invention can be any one of: an audio alarm device, an optical alarm device, a fire detector, a burglar detector and a building service management device.

**[0030]** Furthermore, according to the invention a central control unit is provided, which is specially configured to be used in a method as described above.

**[0031]** Furthermore, the invention is directed to a switching element for a bus system.

**[0032]** Finally, the invention is directed to a computer program that, when loaded in the internal memory of a processor of a central control unit of a bus system will cause the bus system to perform the above-described method.

**[0033]** In the following, preferred embodiments of the invention will be described based on the enclosed Figures, showing further advantageous modifications of the invention.

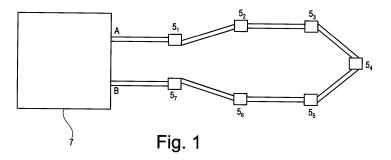

Fig. 1: the basic design of a bus system;

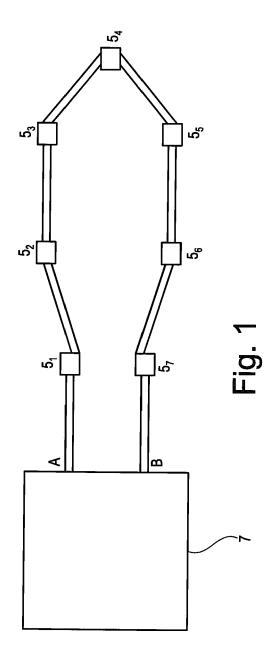

Fig. 2: a block diagram of a switching element used in the bus system of Fig. 1;

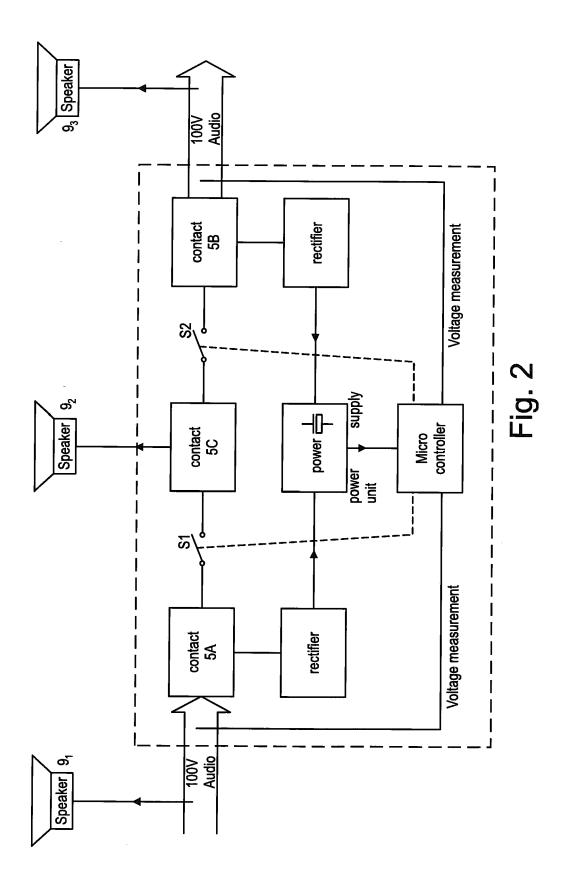

Fig. 3: a flowchart of the initialization step in a preferred embodiment, and

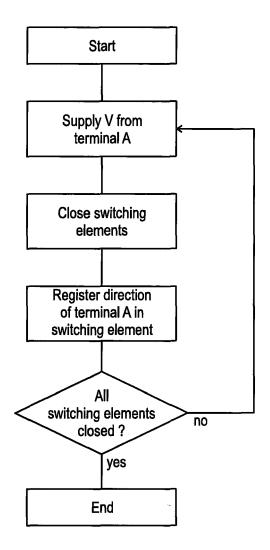

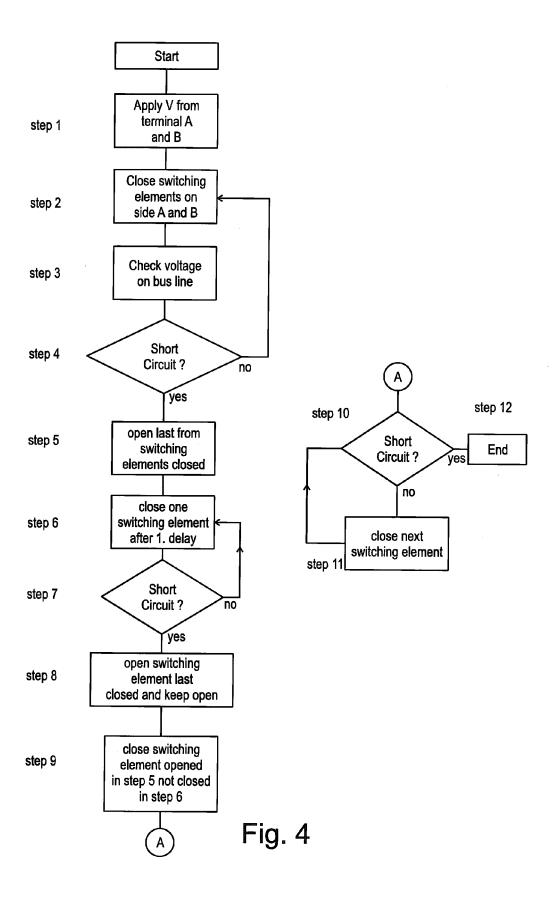

Fig. 4: a flowchart of the program execution in a microprocessor of a switching element according to Fig. 2;.

**[0034]** As Fig. 1 shows, a central control unit containing the inherently-known components, e.g. for public address systems, has a connection R for the start of a two-wired ring line and a connection B for the end of this ring line. The wires of the ring line are looped through switching elements  $5_1$ ,  $5_2$  ...  $5_n$ . In practice, the ring line may comprise 60 or more switching elements. Loudspeakers - not shown here - are connected to the wires of the ring line in the switching elements of the public address system. Loudspeakers is only one example of a bus device which might be used in connection with the bus system. Other bus devices might include audio alarm devices, optical alarm devices, fire detectors, burglar detectors or other kind of building service management devices.

**[0035]** Furthermore, although in the embodiment of Fig. 1 loudspeakers are shown to be connected with the switching element, it is possible to connect the bus devices, including loudspeakers to the line sections between the switching elements directly.

**[0036]** Usually, such systems involve the audio signals being supplied at up to 100 Vrms. In addition, the AC supply voltage supplied is a signal at 22 kHz and with an amplitude of 50 V, for example.

[0037] Between the central control unit 7 and switching elements 5<sub>1</sub> to 5<sub>n</sub> and between switching elements 5<sub>1</sub> to 5<sub>n</sub> themselves, there is no need to provide separate communication links, unlike in the case of some alarm sys-

35

40

tems, e.g. fire alarm systems, which are designed using ring bus technology and have, on the ring bus, switching elements which communicate digitally at least with a central control unit and are controlled by a dedicated bus communication protocol. However, communication between the bus devices, switching elements and central control unit is not excluded and can be advantageously used in many cases.

**[0038]** Fig. 2 shows a simplified block diagram of a switching element  $5_1$ , drawn with one pole. The contact terminal 5A has the incoming ring line 1 connected to it, and the contact terminal 5B has the outgoing ring line connected to it. Two switches S1 and S2 are connected in series in a wire of the ring line. The ring line is looped through contact terminal 5A to contact terminal 5B. Between S1 and S2 there is a contact terminal 5C for connecting a loudspeaker  $9_2$  as a bus device 9. Further loudspeakers  $9_1$  to  $9_n$  may be connected to the ring line outside the switching elements.

[0039] The switches S1 and S2 are in this case designed as relays which are not shown here in any more detail, both on account of the high audio voltages and on account of the high audio currents. The relays and hence the switches S1 and S2 are controlled by a microcontroller, specifically on the basis of whether there is an adequate voltage level on the input and/or the output, to be more precise, whether a prescribed supply voltage level is exceeded or undershot. The separate voltage checking circuits, respectively the short circuit detection means, which are required for this purpose are known and therefore not shown in more detail.

**[0040]** The microcontroller receives its operating voltage from a power supply unit. The power supply unit can be any of an external power supply unit or an internal power supply unit like a large capacitor or a secondary cell, which might be charged from the AC supply voltage via rectifiers during normal operation.

**[0041]** Fig. 3 shows an example of an initialization routine that can be used when setting up the bus system of the invention for the first time.

**[0042]** In the following, the routine of Fig. 3 is described as one example for initialization of the bus system.

**[0043]** In an initial state of the bus system, all switches of all switching elements  $5_1$  to  $5_n$  are in an open state, that is, so that the bus lines are interrupted at any switching element.

**[0044]** At the beginning, the central control unit 7 is advised to apply the supply voltage to the terminal A. The terminal B does not receive the supply voltage from the central control unit 7.

**[0045]** In reaction to applying the supply voltage to terminal A, the first switching element  $5_1$  of the series of switching elements  $5_1$  to  $5_n$  connected along the bus will close the switch S1 and, once the supply voltage reaches the second switch S2, the second switch will close as well.

**[0046]** The microcontroller of the switching element 5<sub>1</sub> will memorize the switching order of switches S1 and S2.

In this way, the switching element 5<sub>1</sub> knows in which direction of the bus line the terminal A and the terminal B respectively are located.

**[0047]** After closing the switches S1 and S2 of the first switching element  $5_1$ , the supply voltage applies to the switching element  $5_2$  and again, the first switching element S1 and S2 of this switching element  $5_2$  will close in the order described in connection with the first switching element  $5_1$ .

0 [0048] The initialization process will continue until closing the switches S1 and S2 of the last switching element 5...

**[0049]** After that, the bus system is in a condition to operate normally.

**[0050]** Based on the information memorized in the memory element of the individual switching elements  $5_1$  to  $5_n$  regarding the arrangement of the switches S1 and S2 with respect to the terminals A and B, the switching elements  $5_1$  to  $5_n$  are designed to allocate delay times to the switches S1 or S2 of each switching element  $5_1$  to  $5_n$ , depending on the orientation of the switches S1 and S2 with respect to the terminal A or terminal B.

**[0051]** For example, a delay time of 0.1 s can be assigned to the switches S1 and a delay time of 0,5 s can be assigned to the switch S2.

**[0052]** If during the operation of the bus system a short circuit occurs along the bus or at one of the bus devices, the supply voltage on the bus line will drop immediately. As a consequence, all switches S1 and S2 of all switching elements  $5_1$  to  $5_n$  will open immediately to protect the bus system..

**[0053]** Upon detection of this event, the central control unit 7 will start a short circuit recovery process, as shown in the flowchart of Fig. 4.

**[0054]** In order to accelerate the reestablishment of the operationability of the bus system of the invention, when restarting the bus system after a short circuit, the central control unit 7 is designed to apply the supply voltage at both terminals A and B, simultaneously.

[0055] As a consequence, the reconnection of the bus devices 9<sub>1</sub> to 9<sub>n</sub> which start from both sides of the loop and consequently, the time needed to reconnect the bus devices will be reduced, in best case only half of the time will be needed to reconnect all the bus devices.

45 [0056] However, when the connection process continues, as shown in Fig. 4, so as to reach a location of the short circuit, upon closing switches S1 or S2 of a switching element 5<sub>x</sub>, immediately adjacent to the location of the short circuit, the voltage on the supply line will drop again.

**[0057]** To cope with this event the switching elements  $5_1$  to  $5_n$  are specially configured. When closing the switches S1 and S2 the microcontroller of the respective switching element  $5_x$  runs a short circuit monitoring routine for a predetermined time and monitors the voltage at the bus. During this time a dedicated threshold value can be applied to discriminate between the normal operation and a short circuit. If, during this predetermined

30

45

50

time the voltage at the bus line drops below the above threshold, the switching element  $5_{\rm x}$  opens the switches again, since it assumes that a short circuit has occurred. **[0058]** The other switching elements  $5_{\rm 1}$  to  $5_{\rm x-1}$  and  $5_{\rm n}$  to  $5_{\rm n-x+1}$  will keep their switches closed, since they are not operating in the short circuit monitoring routine.

**[0059]** However, the switching element  $5_{n-x}$ , which is supplied with the supply voltage from the other terminal as the switching element  $5_x$  and which had turned in the closed state at about the same time as the switching element  $5_x$  will be in the short circuit monitoring routine as well and will open the associated switches S1 and S2.

**[0060]** In a subsequent step, the central control unit will continue to apply the supply voltage from both terminals A and B. The switches of the two switching elements 5x and  $5_{n-x}$ , would therefore close again. However, at time the delay time previously obtained in the initialization step will be applied, so that the switches of the switching elements  $5_x$  and that of the switches  $5_{n-x}$  will close at different timings so as to avoid that these switching elements run the short circuit monitoring routine at the same time again. That is, e.g. the switching element  $5_{n-x}$  will wait a time sufficiently large compared to the predetermined time during which the switching element  $5_x$  runs the short circuit monitoring routine, before closing the switches S1 and S2 again.

**[0061]** If the short circuit is located on the site of the switching element  $5_x$  the drop of the voltage will be detected again, and accordingly, the micro controller of the switching element  $5_x$  will know that the short circuit is immediately adjacent to the switching element  $5_x$ . In that case, the switches of the switching element  $5_x$  will remain open, and the setup of the loop will continue from the site of the terminal B by closing switches of the switching element  $5_{n-x}$

**[0062]** The closes will continue until reaching the switching element  $5_{x+1}$ . In case of a short circuit along the bus line, when closing the switches of the switching element  $5_{x+1}$ , the micro controller of this switching element  $5_{x+1}$  will detect the drop of the voltage at the bus line and open the switches S1 and S2 immediately. After waiting the corresponding predetermined time the switching element  $5_{x+1}$  will close the switches again and will detect the short circuit a new. In consequence, to the consecutive detection of two short circuit events the micro controller of this switching element  $5_{x+1}$  knows, that the short circuit is immediately adjacent and will therefore open the switches S1 and S2 and keep them open.

**[0063]** Therefore, the short circuit will remain isolated between the switching elements  $5_x$  and  $5_{x+1}$ , and the bus system can be operated in two branch lines.

**[0064]** On the other hand, if the short circuit is located adjacent to the switching element  $5_{n-x+1}$  and not immediately adjacent to the switching element  $5_x$ , in the above process, when closing the switches of the switching element  $5_x$ , no drop of the supply voltage on the bus line will occur, a short circuit recovery process will continue on the line starting from the terminal A by closing the

switches of the switching element  $5_{x+1}$  thereon.

**[0065]** In this case the short circuit has to be located adjacent to the switching element  $5_{n-x+1}$ . However, after the lapse of the delay time associated with this supply direction or with this switching element, the switching element  $5_{n-x+1}$  will close the respective switches again and will run the short circuit monitoring routine. The drop of the voltage at the bus line will be detected by the microcontroller of this switching element, and due to the two consecutive detections of a short circuit, the micro controller knows that the short circuit is located immediately adjacent to the switching element  $5_{n-x+1}$ . Therefore, it will control this switching element so as to keep the respective switch in an open state.

**[0066]** It might happen, that at the time the switching element  $5_{n-x+1}$  detects this short circuit, an other switching element, e.g.  $5_{x+y}$  receiving the supply voltage from the other terminal is running a short circuit monitoring routine as well. In this case this switching element will open the respective switches as well. However, since this was the first short circuit detection at that switching element  $5_{x+y}$  it will close the switches again after a certain delay and the reconnection of the bus can proceed.

**[0067]** In this way, a fast and safe reestablishment of the operationability of the system in large parts can be established after a short circuit.

[0068] In a preferred embodiment the micro controller of the switching elements are designed so as to send a message including a dedicated address to the central control unit upon closing the switches. From these messages the central control unit will know, which switching elements are immediately adjacent to the short circuit and might display a corresponding message. However, a skilled person will recognize that the above method can be run on a bus system without any bidirectional communication between the switching elements  $5_1$  to  $5_{\rm n/b}$ us devises  $9_1$  to  $9_{\rm m}$  and the central control unit 7.

**[0069]** According to the above-described process, the delay time is set during the initialization step depending on the connection direction of the switching elements. Although this is a preferred embodiment, alternative configurations might be possible. For example, it might be possible to set an individual and different delay time for each switching element  $5_1$  to  $5_n$  by a dedicated command of the central control unit, which will apply when closing the switching element again after detection of the first short circuit. In this way again, it can be avoided that repeatedly switching elements close simultaneously, which would obscure the discovery of the location of a short circuit.

**[0070]** As a further alternative it is possible to design the switching elements  $5_1$  to  $5_n$  so as to have different connection sites, which differ in the hardware construction, so that the delay is already built in the switching element. Although this conveys the drawback that, when installing the bus system, the workers connecting the switching elements  $5_1$  to  $5_n$  have to take care to connect the switching elements  $5_1$  to  $5_n$  in the correct orientation,

20

25

35

40

45

50

55

it has the advantage that no initial setup procedure is required, and therefore already at the first time of turning on the bus system the buildup of the system can start from both terminals A and B simultaneously.

**[0071]** The method can be implemented e.g. by programming the micro controllers in the switching elements  $5_1$  to  $5_n$  and the central control unit with a dedicated programming when installing an up-date on a corresponding bus system.

**[0072]** The invention has been described based on a voice operated alarm system. However the invention can advantageously be used in a bus system connection smoke detectors or visual and/or acoustical alarm devices.

[0073] Furthermore, the switching elements  $5_1$  to  $5_n$  have been described so as to comprise two switches. However, it is possible to build each or some switching devices so as to include only one switch. In this case in the initialization procedure of Fig. 3. The direction of the terminals A and B has to be discriminated in a different manner, e.g. based on the voltage measurement shown in Fig. 2. Depending on which site the voltage applies first, the micro controller will set different delay times.

[0074] While in the present invention the micro controller of the switching devices where used to control the respective steps, it is although possible to assign this task to a processor in the central control unit. This processor has to be arranged and implemented so as to monitor the voltage at the bus lines and so as to control the switching operations of the switches in the switching elements. Although this configuration requires a more complex communication on the bus it has the advantage that less power is needed in the individual switching devices. [0075] Although the present invention has been described by reference to preferred embodiments, it is clear that the invention is not limited to these particular embodiments. It is possible to adapt modifications and replacements. For example, it is possible to combine the switching element and the bus devices into a single device. In that case, the bus device will be connected between the switches S1 and S2 of a bus device, as shown in the example of Fig. 2 with the speaker 92. Alternatively, switching elements 5<sub>1</sub> to 5<sub>n</sub> can be provided independent

**[0076]** Furthermore, it is not necessary that the bus devices are loudspeakers. As mentioned above, other bus elements, such as fire detectors or smoke detectors or visual alarms can be used instead.

### **Claims**

of the bus devices as well.

Method for operating a bus system; the bus system comprising at least two bus lines (1, 3) formed as respective loops, a plurality of switching elements (5<sub>1</sub> to 5<sub>n</sub>) connected in series so as to divide one of the bus lines in a plurality of sections, a central control unit (7) connected with the ends of the bus lines (1, 3), and a plurality of bus devices ( $9_1$  to  $9_m$ ) connected in parallel between the two bus lines (1, 3) and distributed along the bus lines (1, 3) so that a bus device (9y) is interposed between two consecutive switching elements ( $5_x$ ,  $5_{x+1}$ ); the method comprising the steps:

- (a) applying a supply voltage to both ends of the bus lines (1, 3) starting from terminals (A, B) of the central processing unit (7);

- (b) closing the switching elements  $(5_1, 5_n)$  upon reception of the supply voltage, so as to connect the subsequent respective sections of the bus from both ends:

- (c) monitoring the bus lines (1, 3) in order to detect a first short circuit;

if no first short circuit is detected repeating the steps (a), (b) and (c) until all switching elements  $(5_1, 5_2, 5_3, 5_4, ...5_n)$  are closed or until a first short circuit is detected;

if a first short circuit is detected,

- (d) opening the two switching elements  $(5_1, 5_{(m-1)})$  closed immediately before detecting the first short circuit,

- (e) closing again one of the switching elements (5<sub>1</sub>) opened in step (d);

- (f) monitoring the bus lines (1, 3) in order to detect a second short circuit;

if a second short circuit is detected,

- (g) opening the switching element  $(5_1)$  closed immediately before detecting the second short circuit and keeping this switching element  $(5_1)$  open, and

- (h) closing again the other switching element  $(5_{(m-1)})$  opened in step (d).

- **2.** The method of claim 1 further comprising the step:

running a short circuit monitoring routine by a switching element ( $5_1$  to  $5_n$ ) for a predetermined time after closing the switching element, wherein during the short circuit monitoring routine comprises monitoring the bus line for a drop of a voltage below a second threshold value, which is higher than a threshold value used to monitor for a short circuit at other times.

- 3. The method of claim 2 wherein a difference in delay times between the closing again of the switching elements (5<sub>x</sub> and 5y) opened in step (d) is larger than the predetermined time of the short circuit monitoring routine.

- **4.** The method of claim 1, 2 or 3 further comprising the step:

upon opening a switching element ( $(5_1, 5(m-1))$ ) registering a bus addresses of a last bus devices

25

35

40

45

50

55

before said switching element  $(5_1, 5_{(m-1)}, 5_0)$  in a memory of the central control unit (7); issuing a notification message informing about the estimated location of the short circuit based on this bus addresses.

- 5. The method of claim 1, 2, 3 or 4 further comprising an initialisation process which is performed when setting up the bus system and which comprises the steps:

- applying a supply voltage to one of the bus lines (1, 3) starting from terminals (A) of the central processing unit (7);

closing the switching elements  $(5_1 \text{ to } 5_n)$  in series:

detecting the orientation of each switching element  $(5_1 \text{ to } 5_n)$  with regard to the terminal (A); setting different delay times for the switching element  $(5_1 \text{ to } 5_n)$  for the case of receiving the supply voltage via the site of said terminal (A) than for the case of receiving the supply voltage via the other site; wherein this delay times are used to control the closing of the switching elements in steps (e) and (h).

**6.** Bus system configure to be operated according to the method of claims 1 to 5, the bus system comprising:

at least two bus lines (1, 3) formed as respective loops,

a plurality of switching elements  $(5_1, 5_2, 5_3, 5_4, ...5_n)$  connected in series so as to divide one of the bus lines in a plurality of sections, a central control unit (7), and a plurality of bus devices  $(9_1, 9_2, 9_3, 9_4, ...9_m)$  connected in parallel between the two bus lines (1, 3) and distributed along the bus lines (1, 3) so that a bus device (9y) is interposed between two consecutive switching elements  $(5_x, 5_{x+1})$ ; wherein the central control unit (7) is configured to apply a supply voltage to both ends of the bus

- 7. Bus system according to claim 6, wherein a bus device (9<sub>1</sub>, 9<sub>2</sub>, 9<sub>3</sub>, 9<sub>4</sub>,...9<sub>m</sub>) and one or two switching elements (5<sub>1</sub>, 5<sub>2</sub>, 5<sub>3</sub>, 5<sub>4</sub>, ..5<sub>n</sub>) are grouped as a bus unit (11), which is individually addressable by the central control unit (7).

- The bus system according to any of claims 6 or 7, wherein

the bus devices ((9<sub>1</sub>, 9<sub>2</sub>, 9<sub>3</sub>, 9<sub>4</sub>,...9<sub>m</sub>) comprise at least one of:

an audio alarm device, an optical alarm device,

lines.

- a fire detector.

- a bugler detector, and

- a building service management device.

- 5 9. A central control unit configured for performing the method according to any of claims 1 to 5, wherein the central control unit comprises a processor arranged and implemented so as to monitor the voltage at the bus lines (1, 3) and so as to control the switching operations of the switching elements via the bus.

- **10.** The switching element configured for performing the method according to any of claims 1 to 5, wherein the switching element comprises:

at least one switch (S1, S2);

- a microcontroller configured to control the switching operations of the switch (S1, S2);

- a short circuit detection means for detecting a short circuit at the bus line.

- 11. A computer program that, when loaded in the internal memory of a processor of a central control unit and/or the switching elements of a bus system, will cause the bus system to perform the steps of the method of any of claims 1 to 5.

## Amended claims in accordance with Rule 137(2) 30 EPC.

1. Method for operating a bus system;

the bus system comprising at least two bus lines (1, 3) formed as respective loops, a plurality of switching elements ( $5_1$  to  $5_n$ ) connected in series so as to divide one of the bus lines in a plurality of sections, a central control unit (7) connected with the ends of the bus lines (1, 3), and a plurality of bus devices ( $9_1$  to  $9_m$ ) connected in parallel between the two bus lines (1, 3) and distributed along the bus lines (1, 3) so that a bus device ( $9_1$ ) is interposed between two consecutive switching elements ( $5_x$ ,  $5_{x+1}$ ); the method comprising the steps:

- (a) applying a supply voltage to both ends of the bus lines (1, 3) starting from terminals (A, B) of the central processing unit (7);

- (b) closing the switching elements  $(5_1, 5_n)$  upon reception of the supply voltage, so as to connect the subsequent respective sections of the bus from both ends;

- (c) monitoring the bus lines (1, 3) in order to detect a first short circuit;

if no first short circuit is detected repeating the steps (a), (b) and (c) until all switching elements  $(5_1, 5_2, 5_3, 5_4, ...5_n)$  are closed or until a first short circuit is detected;

if a first short circuit is detected,

10

15

20

25

30

35

40

45

50

55

(d) opening the two switching elements (51, 5<sub>(m-1)</sub>) closed immediately before detecting the first short circuit,

13

- (e) closing again one of the switching elements  $(5_1)$  opened in step (d);

- (f) monitoring the bus lines (1, 3) in order to detect a second short circuit;

- if a second short circuit is detected,

- (g) opening the switching element (5<sub>1</sub>) closed immediately before detecting the second short circuit and keeping this switching element (5<sub>1</sub>) open, and

- (h) closing again the other switching element  $(5_{(m-1)})$  opened in step (d).

- 2. The method of claim 1 further comprising the step:

running a short circuit monitoring routine by a switching element (5<sub>1</sub> to 5<sub>n</sub>) for a predetermined time after closing the switching element, wherein during the short circuit monitoring routine comprises monitoring the bus line for a drop of a voltage below a second threshold value, which is higher than a threshold value used to monitor for a short circuit at other times.

- 3. The method of claim 2 wherein a difference in delay times between the closing again of the switching elements (5, and 5y) opened in step (d) is larger than the predetermined time of the short circuit monitoring routine.

- 4. The method of claim 1, 2 or 3 further comprising the step:

upon opening a switching element ( $(5_1, 5_{(m-1)})$ registering a bus addresses of a last bus devices before said switching element (5<sub>I</sub>,  $5_{(m-I)}$ ,  $5_{o}$ ) in a memory of the central control unit (7); issuing a notification message informing about the estimated location of the short circuit based on this bus addresses.

5. The method of claim 1, 2, 3 or 4 further comprising an initialisation process which is performed when setting up the bus system and which comprises the

> applying a supply voltage to one of the bus lines (1, 3) starting from terminals (A) of the central processing unit (7);

> closing the switching elements (5<sub>1</sub> to 5<sub>n</sub>) in se-

detecting the orientation of each switching element  $(5_1 \text{ to } 5_n)$  with regard to the terminal (A); setting different delay times for the switching element (5<sub>1</sub> to 5<sub>n</sub>) for the case of receiving the supply voltage via the site of said terminal (A) than for the case of receiving the supply voltage via the other site; wherein this delay times are used to control the closing of the switching elements in steps (e) and (h).

6. Bus system configure to be operated according to the method of claims 1 to 5, the bus system comprising:

at least two bus lines (1, 3) formed as respective

a plurality of switching elements (5<sub>1</sub>, 5<sub>2</sub>, 5<sub>3</sub>,  $5_4, ...5_n$ ) connected in series so as to divide one of the bus lines in a plurality of sections,

a central control unit (7), and

a plurality of bus devices  $(9_1, 9_2, 9_3, 9_4, ...9_m)$ connected in parallel between the two bus lines (1, 3) and distributed along the bus lines (1, 3) so that a bus device (9y) is interposed between two consecutive switching elements  $(5_x, 5_{x+1})$ ; wherein the central control unit (7) is configured to apply a supply voltage to both ends of the bus lines (1, 3) starting from terminals (A, B) of the central processing unit (7);

the plurality of switching elements (5<sub>1</sub>, 5<sub>2</sub>, 5<sub>3</sub>,  $5_4, ...5_n$ ) is configured to close, upon reception of the supply voltage, so as to connect the subsequent respective sections of the bus from both ends, to monitor the bus lines (1, 3) in order to detect a first short circuit, to open the two switching elements (5<sub>I</sub>, 5<sub>(m-I)</sub>) closed immediately before detecting the first short circuit, to close again one of the switching elements (5<sub>1</sub>) just opened, to monitor the bus lines (1, 3) in order to detect a second short circuit, to open the switching element (5<sub>1</sub>) closed immediately before detecting the second short circuit and to keep this switching element (5<sub>1</sub>) open, and to close again the other switching element (5(m-l)) opened upon detection of the first short circuit.

- 7. Bus system according to claim 6, wherein a bus device (9<sub>1</sub>, 9<sub>2</sub>, 9<sub>3</sub>, 9<sub>4</sub>,...9<sub>m</sub>) and one or two switching elements (5<sub>1</sub>, 5<sub>2</sub>, 5<sub>3</sub>, 5<sub>4</sub>, ..5<sub>n</sub>) are grouped as a bus unit (11), which is individually addressable by the central control unit (7).

- 8. The bus system according to any of claims 6 or 7, wherein

the bus devices ( $(9_1, 9_2, 9_3, 9_4, ... 9_m)$  comprise at least one of:

an audio alarm device,

an optical alarm device,

a fire detector,

a bugler detector, and

a building service management device.

9. A central control unit configured for performing the method according to any of claims 1 to 5, wherein the central control unit comprises a processor arranged and implemented so as to monitor the voltage at the bus lines (1, 3) and so as to control the switching operations of the switching elements via the bus; the central control unit being configured to apply a supply voltage to both ends of the bus lines (1, 3) starting from terminals (A, B) of the central processing unit (7) upon detection of a short circuit.

**10.** The switching element configured for performing the method according to any of claims 1 to 5, wherein the switching element comprises:

at least one switch (S1, S2); a microcontroller configured to control the switching operations of the switch (S1, S2); a short circuit detection means for detecting a short circuit at the bus line; the switching element  $(5_1, 5_2, 5_3, 5_4, ...5_n)$  being configured to close, upon reception of the supply voltage, so as to connect the subsequent respective section of the bus, to monitor the bus lines (1, 3) in order to detect a first short circuit, to open again when detecting the first short circuit, to close again, to monitor the bus lines (1, 3) in order to detect a second short circuit, to open again upon detecting the second short circuit and to remain open.

11. A computer program that, when loaded in the internal memory of a processor of a central control unit and/or the switching elements of a bus system according to any of claims 86 to 8, will cause the bus system to perform the steps of the method of any of claims 1 to 5.

15

20

g n <sup>35</sup>

40

45

50

Fig. 3

### **EUROPEAN SEARCH REPORT**

Application Number EP 13 17 8845

|                                                                                                                                                        |                                                                                                    | ERED TO BE RELEVANT  Indication, where appropriate,                                                      | Relevant                              | OLAPPIEICATION OF THE                   |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------|--|

| ategory                                                                                                                                                | of relevant pass                                                                                   |                                                                                                          | to claim                              | CLASSIFICATION OF THE APPLICATION (IPC) |  |

| (                                                                                                                                                      | WO 2012/045436 A1 (MUELLER THOMAS [DE] REITHER RO) 12 Apri                                         | NOVAR GMBH [DE];<br>; NEJEDLY ANDREAS [DE];<br>1 2012 (2012-04-12)                                       | 6-10                                  | INV.<br>G08B25/04<br>G08B29/06          |  |

| ٩                                                                                                                                                      | * abstract *  * page 6, line 10 - figures 1-3 *                                                    |                                                                                                          | 1-5,11                                | H04R29/00                               |  |

| P                                                                                                                                                      | EP 0 532 787 A1 (SI<br>24 March 1993 (1993<br>* abstract *<br>* column 2, line 40<br>figures 1-3 * |                                                                                                          | 1-11                                  |                                         |  |

| A                                                                                                                                                      | EP 2 428 942 A1 (NC<br>14 March 2012 (2012<br>* abstract *                                         | 1-11                                                                                                     |                                       |                                         |  |

|                                                                                                                                                        | * paragraph [0019]                                                                                 | - paragraph [0030] *<br>                                                                                 |                                       |                                         |  |

|                                                                                                                                                        |                                                                                                    |                                                                                                          |                                       | TECHNICAL FIELDS<br>SEARCHED (IPC)      |  |

|                                                                                                                                                        |                                                                                                    |                                                                                                          |                                       | G08B<br>H04R                            |  |

|                                                                                                                                                        |                                                                                                    |                                                                                                          |                                       |                                         |  |

|                                                                                                                                                        | The present search report has                                                                      | been drawn up for all claims                                                                             |                                       |                                         |  |

| Place of search                                                                                                                                        |                                                                                                    | Date of completion of the search                                                                         | Examiner                              |                                         |  |

|                                                                                                                                                        | Munich                                                                                             | 10 December 2013                                                                                         | La Gioia, Cosimo                      |                                         |  |

| CATEGORY OF CITED DOCUMENTS  X : particularly relevant if taken alone Y : particularly relevant if combined with another document of the same category |                                                                                                    | E : earlier patent dool<br>after the filling date<br>her D : dooument cited in<br>L : dooument cited for | n the application<br>or other reasons |                                         |  |

| A : technological background O : non-written disclosure P : intermediate document                                                                      |                                                                                                    |                                                                                                          | same patent family, corresponding     |                                         |  |

### ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 13 17 8845

5

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

10-12-2013

|    |                                        |                  |                                                                                    | 10-12-2013                                                                       |

|----|----------------------------------------|------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 10 | Patent document cited in search report | Publication date | Patent family member(s)                                                            | Publication<br>date                                                              |

| 15 | WO 2012045436                          | A1 12-04-2012    | CN 103299352 A<br>DE 102010047220 A1<br>EP 2625678 A1<br>WO 2012045436 A1          | 11-09-2013<br>05-04-2012<br>14-08-2013<br>12-04-2012                             |

| 20 | EP 0532787                             | A1 24-03-1993    | AT 131648 T DE 59107087 D1 DK 0532787 T3 EP 0532787 A1 ES 2080208 T3 GR 3018512 T3 | 15-12-1995<br>25-01-1996<br>25-03-1996<br>24-03-1993<br>01-02-1996<br>31-03-1996 |

| 25 | EP 2428942                             | A1 14-03-2012    | DE 102010044892 A1<br>EP 2428942 A1                                                | 15-03-2012<br>14-03-2012                                                         |

| 20 |                                        |                  |                                                                                    |                                                                                  |

| 30 |                                        |                  |                                                                                    |                                                                                  |

| 35 |                                        |                  |                                                                                    |                                                                                  |

| 40 |                                        |                  |                                                                                    |                                                                                  |

| 45 |                                        |                  |                                                                                    |                                                                                  |

| 50 | ORM P0459                              |                  |                                                                                    |                                                                                  |

55

$\frac{\Omega}{m}$  For more details about this annex : see Official Journal of the European Patent Office, No. 12/82

### EP 2 833 333 A1

### REFERENCES CITED IN THE DESCRIPTION

This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.

### Patent documents cited in the description

• DE 102010047220 [0003]