## (12) CORRECTED EUROPEAN PATENT APPLICATION

(15) Correction information:

Corrected version no 1 (W1 A2) Corrections, see

Bibliography INID code(s) 71

(48) Corrigendum issued on:

24.02.2016 Bulletin 2016/08

(43) Date of publication:

24.06.2015 Bulletin 2015/26

(21) Application number: 14192381.3

(22) Date of filing: 07.11.2014

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

Designated Extension States:

**BA ME**

(30) Priority: 17.12.2013 US 201314109577

(71) Applicant: Intel Corporation Santa Clara, CA 95054 (US) (51) Int Cl.: **G06F** 9/38 (2006.01)

- (72) Inventors:

- Sodhi, Inder M.

Cupertino, CA 95014-1658 (US)

- Jahagirdar, Sanjeev S.

Folsom, CA California 95630 (US)

- (74) Representative: HGF Limited

Fountain Precinct Balm Green

Sheffield S1 2JA (GB)

## (54) Local closed loop efficiency control using IP metrics

(57) According to one embodiment, a processor includes an instruction decoder to decode instruction and a execution unit to execute instructions, the execution unit being associated with a capture logic to periodically capture operating heuristics of the execution unit, a detection logic coupled to the execution unit to evaluate the captured operating heuristics to determine whether there is a need to adjust an operating point of the execution unit, and a control logic coupled to the detection logic and the execution unit to adjust the operating point of the execution unit based on the evaluation of the operating heuristics.

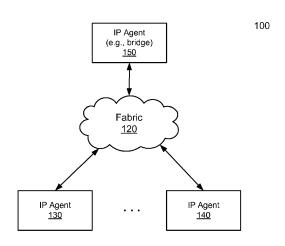

FIG. 1

EP 2 887 208 A8