## **CORRECTED EUROPEAN PATENT APPLICATION** (12)

(15) Correction information:

Corrected version no 1 (W1 A1)

Corrections, see

INID code(s) 71 **Bibliography**

(48) Corrigendum issued on:

17.02.2016 Bulletin 2016/07

(43) Date of publication:

01.07.2015 Bulletin 2015/27

(21) Application number: 14192164.3

(22) Date of filing: 06.11.2014

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

Designated Extension States:

**BA ME**

(30) Priority: 23.12.2013 US 201314138564

(71) Applicant: Intel Corporation Santa Clara, CA 95054 (US)

(72) Inventors:

· Kupermann, Eli 98577 Maale Adumim (IL) (51) Int Cl.: G06F 1/32 (2006.01)

- · Andiappan, Rajasekaran 33720 Tampere (FI)

- · Kareenahalli, Suryaprasad Folsom, CA 95630 (US)

- · Barcohen, Yuli 9091600 Nokdim (IL)

- (74) Representative: Jennings, Vincent Louis

**HGF Limited Fountain Precinct**

Balm Green

Sheffield S1 2JA (GB)

## (54)Method and apparatus to manage power usage in a processor

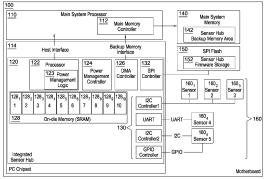

(57)In an embodiment, a processor includes first logic to determine first power to be provided to a first portion of a computational resource during a time period. The first portion may be reserved for execution by the processor of a first workload to be executed during the time period. The first power may be determined based at least in part on the first workload and independently of a second workload. The processor may include second logic to determine second power to be provided to a second portion of the computational resource during the time period. The second portion may be reserved for execution by the processor of the second workload during the time period. The second power may be determined based at least in part on the second workload and independently of the first workload.

Fig. 1