## (12) CORRECTED EUROPEAN PATENT APPLICATION

(15) Correction information:

Corrected version no 1 (W1 A2) Corrections, see

Bibliography INID code(s) 71

(48) Corrigendum issued on:

24.02.2016 Bulletin 2016/08

(43) Date of publication:

01.07.2015 Bulletin 2015/27

(21) Application number: 14193268.1

(22) Date of filing: 14.11.2014

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

Designated Extension States:

**BA ME**

(30) Priority: 27.12.2013 US 201314142734

(71) Applicant: Intel Corporation Santa Clara, CA 95054 (US) (51) Int Cl.: **G06F** 9/38 (2006.01)

- (72) Inventor: Lee, Victor W.

Santa Clara, CA California 95051 (US)

- (74) Representative: Jennings, Vincent Louis

HGF Limited

Fountain Precinct

Balm Green

Sheffield S1 2JA (GB)

## (54) Processor with architecturally-visible programmable on-die storage to store data that is accessible by instruction

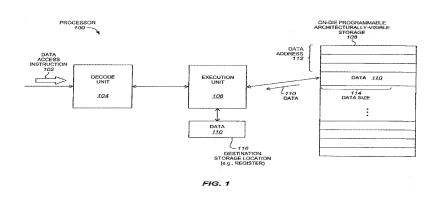

(57) A processor of an aspect includes an on-die programmable architecturally-visible storage. The processor also includes a decode unit to receive a data access instruction of an instruction set of the processor. The data access instruction to indicate a data address that is to be associated with data to be stored in the on-die programmable architecturally-visible storage, to indicate a data size associated with the data to be stored in the on-die programmable architecturally-visible storage, and to in-

dicate a destination storage location of the processor. An execution unit is coupled with the decode unit and the on-die programmable architecturally-visible storage. The execution unit is on-die with the on-die programmable storage. The execution unit is operable, in response to the data access instruction, to store the data, which is associated with the data address and the data size, in the destination storage location that is to be indicated by the instruction.

EP 2 889 759 A8