## (12) CORRECTED EUROPEAN PATENT APPLICATION

(15) Correction information:

Corrected version no 1 (W1 A1) Corrections, see

Bibliography INID code(s) 71

(48) Corrigendum issued on:

17.02.2016 Bulletin 2016/07

(43) Date of publication:

08.07.2015 Bulletin 2015/28

(21) Application number: 15153677.8

(22) Date of filing: 28.06.2011

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

- (30) Priority: 29.06.2010 US 825729

- (62) Document number(s) of the earlier application(s) in accordance with Art. 76 EPC: 11804112.8 / 2 589 077

- (71) Applicant: Intel Corporation Santa Clara, CA 95054 (US)

- (72) Inventors:

- Nalla, Ravi, K.

San Jose, CA 95117 (US)

(51) Int Cl.: H01L 23/538 (2006.01)

- Manusharow, Mathew, J. Phoenix, AZ 85048 (US)

- Delaney, Drew Chandler, AZ 95249 (US)

- (74) Representative: Rummler, Felix

RGC Jenkins & Co.

26 Caxton Street

London SW1H 0RJ (GB)

## Remarks:

This application was filed on 03-02-2015 as a divisional application to the application mentioned under INID code 62.

## (54) Microelectronic package and method of manufacturing same

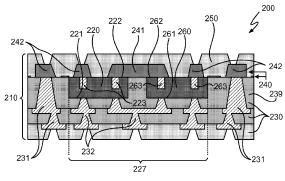

(57) A microelectronic package comprising: a substrate (210); a first die (220) and a second die (260), both of which are embedded in the substrate, both of which have a front side (221, 261) and an opposing back side (222, 262), and both of which have at least one through-silicon-via (223, 263) therein; a plurality of build-up layers (230) adjacent to and built up over the front sides of the first and second dies; and an electrically conductive structure (240) adjacent to and in physical contact with the back sides of the first and second dies.

FIG. 2B