## (11) EP 2 912 646 B1

(12)

## **FASCICULE DE BREVET EUROPEEN**

(45) Date de publication et mention de la délivrance du brevet: 05.10.2016 Bulletin 2016/40

(21) Numéro de dépôt: 13770668.5

(22) Date de dépôt: 24.09.2013

(51) Int Cl.: **G08B 29/12** (2006.01) **G05B 23/02** (2006.01)

(86) Numéro de dépôt international: PCT/EP2013/069853

(87) Numéro de publication internationale:

WO 2014/063889 (01.05.2014 Gazette 2014/18)

(54) **DÉTECTEUR SIL2 POLYVALENT DOTÉ DE DEUX SORTIES ET D'UNE ENTRÉE DE TEST**VIELSEITIGER SIL2-DETEKTOR MIT ZWEI AUSGÄNGEN UND EINEM TESTEINGANG

VERSATILE SIL2 DETECTOR HAVING TWO OUTPUTS AND ONE TEST INPUT

(84) Etats contractants désignés:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB

GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO

PL PT RO RS SE SI SK SM TR

(30) Priorité: 26.10.2012 FR 1260248

(43) Date de publication de la demande: **02.09.2015 Bulletin 2015/36**

(73) Titulaire: Schneider Electric Industries SAS 92500 Rueil-Malmaison (FR)

(72) Inventeur: BERNARD, Jacques F-16340 L'Isle d'Espagnac (FR)

(74) Mandataire: Dufresne, Thierry et al Schneider Electric Industries SAS Service Propriété Industrielle 35 rue Joseph Monier - CS 30323 92506 Rueil-Malmaison Cedex (FR)

(56) Documents cités:

WO-A2-2005/013098 US-A1- 2005 113 942

P 2 912 646 B1

Il est rappelé que: Dans un délai de neuf mois à compter de la publication de la mention de la délivrance du brevet européen au Bulletin européen des brevets, toute personne peut faire opposition à ce brevet auprès de l'Office européen des brevets, conformément au règlement d'exécution. L'opposition n'est réputée formée qu'après le paiement de la taxe d'opposition. (Art. 99(1) Convention sur le brevet européen).

30

45

#### Domaine technique de l'invention

**[0001]** La présente invention se rapporte à un détecteur de sécurité doté de deux sorties et d'une entrée de test. Ce détecteur présente un niveau de sécurité SIL au moins égal à 2.

1

#### Etat de la technique

[0002] Il est connu de proposer des systèmes de détection sécurisée permettant de sécuriser le fonctionnement d'une application. Par exemple, pour sécuriser l'accès à une machine située dans un local, il est connu de prévoir un système de détection sécurisée qui permet de ne pas autoriser le démarrage de la machine lorsque le moyen d'accès au local est ouvert. Un tel système de détection comporte un ou plusieurs détecteurs, une unité logique de traitement recevant l'état de chaque détecteur et un ou plusieurs actionneurs commandés par l'unité logique de traitement en tenant compte de l'état de chaque détecteur.

[0003] Lorsque le système de détection est sécurisé, il présente un certain niveau de sécurité, appelé SIL (pour "Safety Integrity Level"). Ces niveaux de sécurité sont définis par différentes normes (par exemple IEC 61508 ou IEC 62061 pour le niveau SIL2). Dans un système de détection à niveau SIL2 ou supérieur, l'une des problématiques principales est de savoir diagnostiquer les pannes sur les sorties du détecteur ainsi que sur le câble qui permet de raccorder le détecteur à l'unité logique de traitement. Un système de détection SIL2 est préférentiellement réalisé en employant un détecteur SIL2 ou plusieurs détecteurs de niveau inférieur à SIL2.

**[0004]** Dans l'état de la technique, il a été proposé différentes solutions pour attribuer un niveau SIL2 ou supérieur à un détecteur.

[0005] Une première solution consiste à proposer un détecteur doté de deux sorties de type NO (pour "Normally Opened", c'est-à-dire normalement ouverte) connectées à l'unité logique de traitement. Dans cette solution, le détecteur intègre un module de diagnostic lui permettant de diagnostiquer la panne de l'une des deux sorties NO et d'ouvrir l'autre sortie en cas de panne. Dans cette solution, une coupure du câble est détectée par l'unité logique de traitement et un court-circuit sur le câble est détecté par le module de diagnostic du détecteur.

[0006] Une deuxième solution consiste à proposer un détecteur doté d'une sortie NO et d'une sortie NC (pour "Normally Closed", c'est-à-dire normalement fermée). Dans cette solution, la panne de l'une des deux sorties est détectée par l'unité logique de traitement, par exemple en vérifiant la complémentarité des deux signaux de sortie. Une coupure du câble et un court-circuit sur le câble sont détectés par l'unité logique de traitement, immédiatement ou lors du changement d'état des sorties. [0007] Une troisième solution consiste à proposer un

détecteur doté d'une sortie NO et d'une entrée de test cyclique permettant à l'unité logique de traitement de vérifier la sortie du détecteur. Dans cette solution, les pannes sur la sortie du détecteur, sur le câble, ainsi que sur l'entrée de l'unité logique de traitement, sont détectées par l'unité logique de traitement lors du cycle de test.

[0008] Ces trois solutions permettent d'attribuer un niveau 2 de SIL au détecteur.

[0009] Cependant, elles présentent toutes certains ino convénients listés ci-dessous :

- Nécessité d'un module de diagnostic intégré au détecteur dans la première solution.

- Peu d'unité logique de traitement du commerce sont compatibles avec un détecteur du type de la deuxième solution, à deux sorties complémentaires.

- Nécessité de proposer deux variantes de détecteur du type de la première ou de la troisième solution pour pouvoir surveiller l'absence ou la présence de la cible.

**[0010]** US 2005/0112942 divulgue un système sécurisé destiné à surveiller un processus industriel conformément à un SIL souhaité.

**[0011]** Le but de l'invention est de proposer un détecteur polyvalent permettant de pallier les inconvénients listés ci-dessus tout en restant compatible avec une connectique à quatre points de connexion imposée par le connecteur de type M12.

#### Exposé de l'invention

[0012] Ce but est atteint par un détecteur conforme à la revendication 1.

**[0013]** Selon une particularité, le module de test comporte un module de comparaison agencé pour générer le signal de sortie selon l'état du signal d'entrée de test par rapport à une valeur seuil déterminée.

**[0014]** Selon une autre particularité, le détecteur comporte un module d'alimentation comprenant un condensateur agencé pour se charger en fonctionnement normal et à se décharger en maintenant une tension d'alimentation suffisante pour le bon fonctionnement du détecteur lors du test des sorties.

**[0015]** Selon une autre particularité, le détecteur comporte quatre bornes de connexion agencées pour recevoir un connecteur de type M12.

[0016] Selon une autre particularité, la première sortie est de type "normalement ouvert".

**[0017]** Selon une autre particularité, la deuxième sortie est de type normalement "normalement fermé".

**[0018]** L'invention concerne également un système de détection qui comporte :

une unité logique de traitement comprenant au moins une entrée et une sortie de test,

35

détecteur D1.

4

un détecteur tel que défini ci-dessus, dont la première borne de sortie est connectée à ladite entrée de l'unité logique de traitement et une borne d'alimentation est connectée à la sortie de test de l'unité logique de traitement, l'unité logique de traitement étant agencée pour générer un signal d'entrée de test appliqué sur ladite borne d'alimentation du détecteur afin de tester chaque sortie du détecteur connectée à l'unité logique de traitement.

**[0019]** L'invention concerne enfin un système de détection comprenant :

- une unité logique de traitement comprenant deux entrées et deux bornes d'alimentation,

- un détecteur tel que défini ci-dessus, dont les deux bornes d'alimentation sont connectées aux deux bornes d'alimentation de l'unité logique de traitement et les deux bornes de sortie sont connectées aux deux entrées de l'unité logique de traitement de manière à proposer une redondance entre les deux sorties du détecteur.

#### Brève description des figures

**[0020]** D'autres caractéristiques et avantages vont apparaître dans la description détaillée qui suit faite en regard des dessins annexés dans lesquels :

- La figure 1 représente un système de détection comprenant notamment un détecteur et une unité logique de traitement,

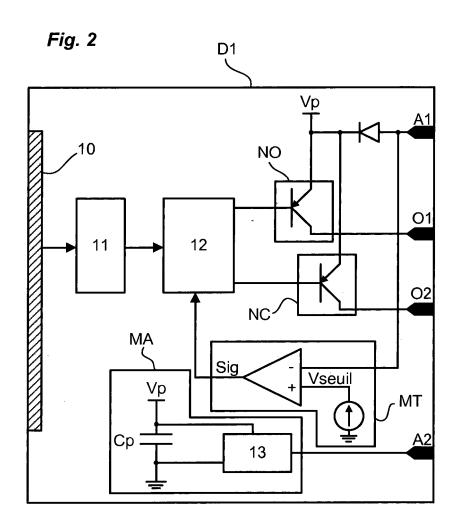

- la figure 2 représente de manière schématique un détecteur de l'invention,

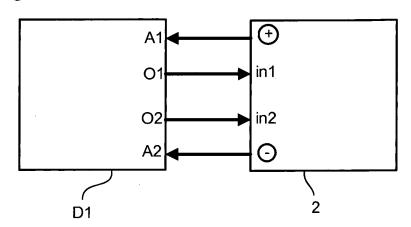

- la figure 3A représente un système de détection dans une première configuration de connexion du détecteur de l'invention à une unité logique de traitement, le détecteur étant dans un mode de fonctionnement à deux sorties redondantes,

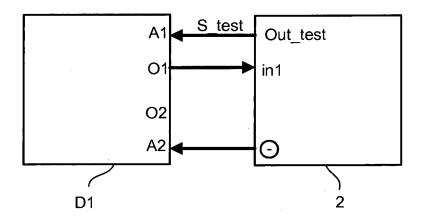

- la figure 3B représente un système de détection dans une deuxième configuration de connexion du détecteur de l'invention à une unité logique de traitement, le détecteur étant dans un mode de fonctionnement à au moins une sortie et une entrée de test.

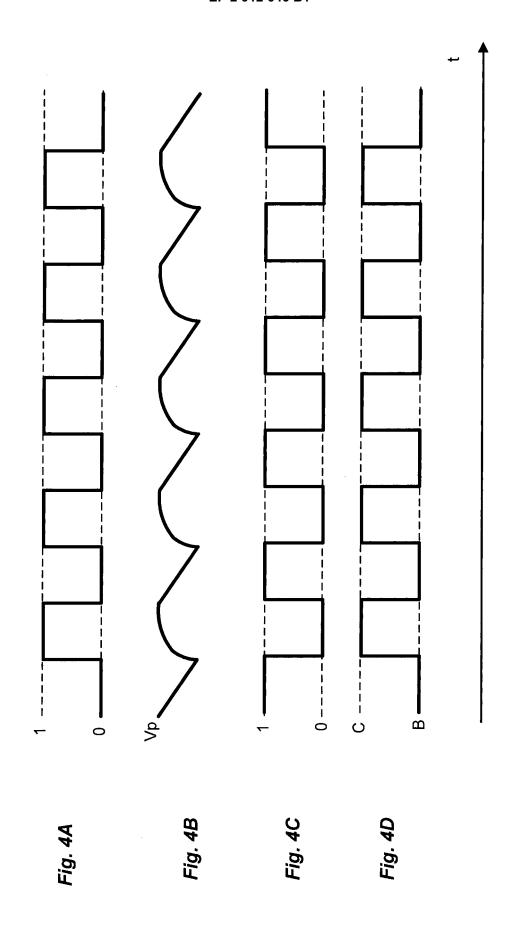

- les figures 4A à 4D illustrent le principe de fonctionnement du détecteur de l'invention dans la deuxième configuration de connexion.

# Description détaillée d'au moins un mode de réalisation

[0021] Le détecteur de l'invention est agencé pour présenter un niveau de sécurité SIL au moins égal à 2.

[0022] En référence à la figure 1, au moins un détecteur D1 est connecté par un câble de raccordement à une unité logique de traitement 2 afin de former un système de détection sécurisée. L'unité logique de traitement 2 fournit par exemple l'alimentation au détecteur via ledit câble qui est connecté à deux bornes d'alimentation (A1 et A2) présentes sur le détecteur D1. Les deux bornes d'alimentation sont désignées ci-après première borne d'alimentation A1 et deuxième borne d'alimentation A2. L'unité logique de traitement 2 est connectée à un ou plusieurs actionneurs 3 et permet de commander ces actionneurs 3 en fonction de l'état du signal de sortie du

[0023] Pour la suite de la description, on définit un état de détection sûr et un état de détection non sûr. Dans l'état de détection sûr, le détecteur D1 est agencé pour générer au moins un premier signal de sortie qui est interprété par l'unité logique de traitement 2 comme une autorisation de fonctionnement de l'application sécurisée. Dans l'état de détection non sûr, le détecteur D1 est agencé pour générer au moins un deuxième signal de sortie qui est interprété par l'unité logique de traitement 2 comme une mise en sécurité de l'application sécurisée. [0024] Selon la configuration de l'application à sécuriser, l'état de détection sûr peut correspondre à la détection de la cible devant le détecteur D1 ou à la non-détection de la cible devant le détecteur D1. De même, l'état de détection non sûr peut correspondre à la détection de la cible devant le détecteur D1 ou à la non-détection de la cible devant le détecteur D1.

**[0025]** Le détecteur D1 de l'invention peut être de tous types connus, à sortie tout ou rien, tels que par exemple inductif, capacitif, à ultrasons ou photoélectrique, voire des pressostats ou thermostats. Le détecteur comporte donc un organe capteur 10 adapté pour remplir sa fonction.

[0026] Le détecteur D1 comporte un étage de détection 11 connecté à l'organe capteur 10 et destiné à générer un signal de détection représentatif de l'état de détection sûr ou de l'état de détection non sûr. En sortie de l'étage de détection 11, le signal de détection est préférentiellement binaire.

**[0027]** Le détecteur D1 comporte un étage de traitement 12 connecté à l'étage de détection 11 et destiné à générer un ou plusieurs signaux de sortie.

**[0028]** Le détecteur de l'invention présente la particularité d'être polyvalent. Il peut s'adapter aux différentes configurations de traitement et de commande de l'unité logique de traitement 2 qui lui est connecté.

[0029] Pour cela, en référence à la figure 2, le détecteur de l'invention comporte :

- une première sortie, par exemple de type NO (pour "Normally Opened", c'est-à-dire normalement ouverte),

- une deuxième sortie, par exemple de type NC (pour "Normally Closed", c'est-à-dire normalement fer-

mée),

une entrée de test cyclique reliée à l'une de ses bornes d'alimentation.

[0030] Dans cette configuration, le détecteur D1 de l'invention pourra ainsi indifféremment se connecter sur une unité logique de traitement 2 qui est apte à gérer un détecteur à deux sorties NO et NC complémentaires ou apte à gérer un détecteur à sortie NO ou NC et une entrée de test cyclique.

**[0031]** Bien entendu, le détecteur D1 pourrait également comporter deux sorties de type NO ou deux sorties de type NC.

[0032] Par ailleurs, le détecteur D1 de l'invention est agencé pour disposer d'une connectique simple et standard à quatre points de connexion, telle que la connectique M12. En plus de ses deux bornes d'alimentation, le détecteur D1 de l'invention comporte donc deux bornes de sortie O1, O2, c'est-à-dire une première borne de sortie O1 connectée à la première sortie (de type NO sur les figures annexées) et une deuxième borne de sortie O2 connectée à la deuxième sortie (de type NC sur les figures annexées). Chaque sortie du détecteur comporte un transistor de type PNP ou NPN commandé par un dispositif de commande relié à l'étage de traitement.

[0033] Par ailleurs, le détecteur D1 de l'invention comporte un module de test MT connecté à la première borne d'alimentation A1 ou à la deuxième borne d'alimentation A2. Sur la figure 2, le module de test est connecté à la première borne d'alimentation.

[0034] Le module de test MT comporte un module de comparaison comprenant une première entrée recevant une valeur seuil Vseuil prédéterminée et une deuxième entrée connectée à la première borne d'alimentation A1 et recevant un signal d'entrée de test S\_test en provenance de l'unité logique de traitement 2. Le module de comparaison comporte une sortie sur laquelle est appliqué un signal de sortie Sig dont l'état dépend de la comparaison entre le signal d'entrée de test S\_test appliqué sur la deuxième entrée du module de comparaison et la valeur seuil Vseuil appliquée sur la première entrée. Le module de test MT permet de tester que la première sortie (NO) et/ou la deuxième sortie (NC) du détecteur D1 sont en parfait état de fonctionnement lorsque le détecteur est connecté à une unité logique de traitement 2 disposant d'une sortie de test Out\_test (figure 3B par exemple). Lors du test des sorties, le signal de sortie Sig est envoyé à l'étage de traitement 12 qui commande alors le blocage simultané des 2 sorties.

[0035] Par ailleurs, le détecteur D1 comporte également un module d'alimentation MA lui permettant de rester alimenté lorsque le test des sorties est en cours. Ce module d'alimentation MA comporte un condensateur Cp chargé périodiquement par la tension d'alimentation appliquée par l'unité logique de traitement 2 entre les deux bornes d'alimentation A1, A2 du détecteur et un régulateur de tension 13 destiné à réguler la tension d'alimen-

tation aux bornes du condensateur. Le module d'alimentation MA est connecté à la deuxième borne d'alimentation du détecteur.

**[0036]** En référence aux figures 3A et 3B, par sa polyvalence, le détecteur D1 de l'invention est ainsi capable de s'adapter aux deux configurations classiques de connexion à une unité logique de traitement 2.

[0037] La figure 3A illustre une première configuration dans laquelle le détecteur D1 de l'invention est doté de deux sorties redondantes (identiques ou complémentaires) connectées à deux entrées in1, in2 de l'unité logique de traitement 2. Dans cette configuration, le module de test MT du détecteur n'est pas employé. Les deux bornes d'alimentation A1, A2 du détecteur sont connectées à deux bornes d'alimentation +, - de l'unité logique de traitement 2.

[0038] La figure 3B illustre une deuxième configuration dans laquelle le détecteur D1 de l'invention est employé dans un mode de fonctionnement à une sortie (NO ou NC) connectée à une entrée in1 de l'unité logique de traitement. Le détecteur D1 est alimenté par la sortie de test de l'unité logique de traitement 2 et sa première borne d'alimentation A1 reçoit le signal d'entrée de test S test.

[0039] Le principe de fonctionnement du détecteur D1 de l'invention dans cette deuxième configuration est illustré par les figures 4A à 4D.

[0040] La figure 4A représente l'état du signal d'entrée de test S\_test envoyé par la sortie de test Out\_test de l'unité logique de traitement 2 sur la première borne d'alimentation A1 du détecteur. Afin de tester la sortie du détecteur D1 de manière cyclique, le signal d'entrée de test S\_test alterne périodiquement entre deux valeurs (0 ou 1 en binaire). Lorsque le signal d'entrée de test S\_test est à 1, le détecteur D1 fonctionne normalement et est alimenté par l'unité logique de traitement 2. Lorsque le signal d'entrée de test S\_test est à 0, l'unité logique de traitement 2 teste chaque sortie du détecteur et le détecteur D1 n'est donc plus alimenté par l'unité logique de traitement 2.

[0041] La figure 4B représente l'état de charge et décharge du condensateur Cp. Le condensateur Cp se charge lorsque le signal d'entrée de test appliqué sur la première borne d'alimentation A1 est à 1, c'est-à-dire lorsque le détecteur D1 est alimenté par l'unité logique de traitement. Lorsque le signal d'entrée de test est à la valeur 0, le détecteur D1 n'est plus alimenté par l'unité logique de traitement 2 et s'alimente alors sur l'énergie emmagasinée dans le condensateur Cp, qui se décharge.

[0042] La figure 4C représente l'état du signal de sortie Sig du module de comparaison. La valeur 1 du signal de sortie Sig correspond à la commande d'inhibition de chaque sortie du détecteur D1. Le signal de sortie Sig est à la valeur 1 lorsque le signal d'entrée de test S\_test est à la valeur 0.

[0043] La figure 4D représente l'état des deux sorties NO et NC du détecteur D1 (même si une seule sortie est

40

45

10

15

20

35

40

50

connectée à l'unité logique de traitement 2, les deux sorties basculent simultanément). Par exemple, les deux sorties NO, NC prennent alternativement un état complémentaire (C) lorsque le détecteur D1 fonctionne normalement et un état commun de blocage (B) lorsque l'unité logique de traitement 2 passe le signal d'entrée de test S\_test à la valeur 0 pour tester les deux sorties NO et NC. [0044] Le module de test MT décrit ci-dessus pourrait présenter un fonctionnement différent de celui décrit ci-dessus. En effet, l'idée principale consiste à inhiber périodiquement les sorties de manière à les tester, sur sollicitation de l'unité logique de traitement. La comparaison effectuée par le module de comparaison pour la génération du signal de sortie Sig pourrait donc être différente de celle décrite ci-dessus.

#### Revendications

- 1. Détecteur (D1) comprenant :

- un organe capteur (10),

- un étage de détection (11) connecté à l'organe capteur (10) et destiné à générer un signal de détection représentatif, selon la position d'une cible par rapport au détecteur, d'un état de détection sûr ou d'un état de détection non sûr,

- une première borne d'alimentation (A1) et une deuxième borne d'alimentation (A2) entre lesquelles peut être appliquée une tension d'alimentation nécessaire à l'alimentation du dispositif

- une première borne de sortie (O1) connectée à une première sortie.

- une deuxième borne de sortie (02) connectée à une deuxième sortie,

- un étage de traitement (12) destiné à traiter le signal de détection et à commander la première sortie et la deuxième sortie en fonction du signal de détection reçu,

- caractérisé en ce qu'il comporte un module de test (MT) connecté à la première borne d'alimentation (A1) ou à la deuxième borne d'alimentation et agencé pour recevoir un signal d'entrée de test cyclique (S\_test) en provenance d'une unité logique de traitement (2) externe sur ladite première borne d'alimentation ou deuxième borne d'alimentation, ledit module de test étant agencé pour générer un signal de sortie (Sig) envoyé à l'étage de traitement (12) pour placer chaque sortie dans un état déterminé interprétable par ladite unité logique de traitement (2) externe.

- Détecteur selon la revendication 1, caractérisé en ce que le module de test (MT) comporte un module de comparaison agencé pour générer le signal de sortie (Sig) selon l'état du signal d'entrée de test

(S\_test) par rapport à une valeur seuil (Vseuil) déterminée.

- 3. Détecteur selon la revendication 1 ou 2, caractérisé en ce qu'il comporte un module d'alimentation (MA) comprenant un condensateur (Cp) agencé pour se charger en fonctionnement normal et à se décharger en maintenant une tension d'alimentation suffisante pour le bon fonctionnement du détecteur lors du test des sorties.

- 4. Détecteur selon l'une des revendications 1 à 3, caractérisé en ce qu'il comporte quatre bornes de connexion agencées pour recevoir un connecteur de type M12.

- Détecteur selon l'une des revendications 1 à 4, caractérisé en ce que La première sortie est de type "normalement ouvert" (NO).

- 6. Détecteur selon la revendication 5, caractérisé en ce que la deuxième sortie est de type normalement "normalement fermé" (NC).

- 25 7. Système de détection, caractérisé en ce qu'il comporte :

- une unité logique de traitement comprenant au moins une entrée (in1) et une sortie de test (Out\_test),

- un détecteur (D1) tel que défini dans l'une des revendications précédentes, dont la première borne de sortie (01) est connectée à ladite entrée (in1) de l'unité logique de traitement (2) et une borne d'alimentation (A1, A2) est connectée à la sortie de test de l'unité logique de traitement (2), l'unité logique de traitement (2), l'unité logique de traitement (2) étant agencée pour générer un signal d'entrée de test (S\_test) appliqué sur ladite borne d'alimentation du détecteur (D1) afin de tester chaque sortie (NO, NC) du détecteur (D1) connectée à l'unité logique de traitement (2).

- 8. Système de détection, caractérisé en ce qu'il comporte :

- une unité logique de traitement comprenant deux entrées (in1, in2) et deux bornes d'alimentation (+, -),

- un détecteur (D1) tel que défini dans l'une des revendications précédentes, dont les deux bornes d'alimentation (A1, A2) sont connectées aux deux bornes d'alimentation (+, -) de l'unité logique de traitement (2) et les deux bornes de sortie (O1, O2) sont connectées aux deux entrées (in1, in2) de l'unité logique de traitement (2) de manière à proposer une redondance entre les deux sorties du détecteur.

15

#### Patentansprüche

- 1. Detektor (D1), umfassend:

- ein Sensororgan (10),

- eine Detektionsstufe (11), die an das Sensororgan (10) angeschlossen ist und dazu bestimmt ist, ein repräsentatives Detektionssignal nach der Position eines Ziels relativ zu dem Detektor eines sicheren Detektionszustands oder eines nicht sicheren Detektionszustands zu erzeugen,

- eine erste Einspeiseklemme (A1) und eine zweite Einspeiseklemme (A2) zwischen denen eine Versorgungsspannung angelegt werden kann, die für die Stromversorgung der Vorrichtung notwendig ist,

- eine erste Ausgangsklemme (O1), die an einen ersten Ausgang angeschlossen ist,

- eine zweite Ausgangsklemme (O2), die an einen zweiten Ausgang angeschlossen ist,

- eine Verarbeitungsstufe (12), die dazu bestimmt ist, das Detektionssignal zu verarbeiten und den ersten Ausgang und den zweiten Ausgang in Abhängigkeit von dem empfangenen Detektionssignal zu steuern,

- dadurch gekennzeichnet, dass er ein Testmodul (MT) aufweist, das an die erste Einspeiseklemme (A1) oder an die zweite Einspeiseklemme angeschlossen ist und angeordnet ist, um ein zyklisches Eingangstestsignal (S\_test), das von einer externen logischen Verarbeitungseinheit (2) stammt, auf der ersten Einspeiseklemme oder der zweiten Einspeisklemme zu empfangen, wobei das Testmodul angeordnet ist, um ein Ausgangssignal (Sig) zu erzeugen, das an die Verarbeitungsstufe (12) gesendet wird, um jeden Ausgang in einen bestimmten Zustand zu versetzen, der von der externen logischen Verarbeitungseinheit (2) lesbar ist.

- Detektor nach Anspruch 1, dadurch gekennzeichnet, dass das Testmodul (MT) ein Vergleichsmodul aufweist, das angeordnet ist, um das Ausgangssignal (Sig) nach dem Zustand des Eingangstestsignals (S\_test) in Bezug auf einen vorbestimmten Schwellenwert (Vseuil) zu erzeugen.

- 3. Detektor nach Anspruch 1 oder 2, dadurch gekennzeichnet, dass er ein Einspeisemodul (MA) aufweist, das einen Kondensator (Cp) aufweist, der angeordnet ist, um sich im normalen Betrieb aufzuladen und sich zu entladen, indem eine Versorgungsspannung aufrechterhalten wird, die für das ordnungsgemäße Funktionieren des Detektors während des Tests der Ausgänge ausreichend ist.

- 4. Detektor nach einem der Ansprüche 1 bis 3, dadurch gekennzeichnet, dass er vier Anschlussklemmen aufweist, die angeordnet sind, um einen M12-Steckverbinder aufzunehmen.

- Detektor nach einem der Ansprüche 1 bis 4, dadurch gekennzeichnet, dass der erste Ausgang vom "normalerweise offenen" Typ (NO) ist.

- 6. Detektor nach Anspruch 5, dadurch gekennzeichnet, dass der zweite Ausgang vom "normalerweise geschlossenen" Typ (NC) ist.

- Detektionssystem, dadurch gekennzeichnet, dass es Folgendes aufweist:

- eine logische Verarbeitungseinheit, umfassend mindestens einen Eingang (in1) und einen Testausgang (Out\_test),

- einen Detektor (D1), wie in einem der vorhergehenden Ansprüche definiert, dessen erste Ausgangsklemme (O1) an den ersten Eingang (in1) der logischen Verarbeitungseinheit (2) angeschlossen ist, und eine Einspeiseklemme (A1, A2) an den Testausgang der logischen Verarbeitungseinheit (2) angeschlossen ist, wobei die logische Verarbeitungseinheit (2) angeordnet ist, um ein Testeingangssignal (S\_test) zu erzeugen, das auf die Einspeiseklemme des Detektors (D1) angelegt ist, um jeden Ausgang (NO, NC) des Detektors (D1) zu testen, der an die logische Verarbeitungseinheit (2) angeschlossen ist.

- 8. Detektionssystem, dadurch gekennzeichnet, dass es Folgendes aufweist:

- eine logische Verarbeitungseinheit, umfassend zwei Eingänge (in1, in2) und zwei Einspeiseklemmen (+, -),

- einen Detektor (D1), wie in einem der vorhergehenden Ansprüche definiert, dessen zwei Einspeiseklemmen (A1, A2) an die zwei Einspeiseklemmen (+, -) der logischen Verarbeitungseinheit (2) angeschlossen sind und dessen zwei Ausgangsklemmen (O1, O2) an die zwei Eingänge (in1, in2) der logischen Verarbeitungseinheit (2) derart angeschlossen sind, dass eine Redundanz angeboten wird.

#### Claims

- 1. A detector (D1) comprising:

- a sensor member (10),

- a detection stage (11) connected to the sensor member (10) and intended to generate a detec-

6

55

20

25

40

50

tion signal representative, depending on the position of a target relative to the detector, of a safe detection state or of an unsafe detection state,

- a first power supply terminal (A1) and a second power supply terminal (A2) between which can be applied a power supply voltage required to power the device,

- a first output terminal (O1) connected to a first output,

- a second output terminal (O2) connected to a second output,

- a processing stage (12) intended to process the detection signal and to control the first output and the second output as a function of the detection signal received,

- characterized in that it comprises a test module (MT) connected to the first power supply terminal (A1) or to the second power supply terminal and arranged to receive a cyclical test input signal (S\_test) arriving from an external processing logic unit (2) on said first power supply terminal or second power supply terminal, said test module being arranged to generate an output signal (Sig) sent to the processing stage (12) in order to place each output in a determined state that can be interpreted by said external processing logic unit (2).

- 2. The detector as claimed in claim 1, characterized in that the test module (MT) comprises a comparison module arranged to generate the output signal (Sig) according to the state of the test input signal (S\_test) relative to a determined threshold value (Vseuil).

- 3. The detector as claimed in claim 1 or 2, characterized in that it comprises a power supply module (MA) comprising a capacitor (Cp) arranged to charge in normal operation and to discharge while maintaining a sufficient power supply voltage for the correct operation of the detector when the outputs are being tested.

- 4. The detector as claimed in one of claims 1 to 3, characterized in that it comprises four connection terminals arranged to receive a connector of M12 type.

- 5. The detector as claimed in one of claims 1 to 4, characterized in that the first output is of "normally open" (NO) type.

- **6.** The detector as claimed in claim 5, **characterized in that** the second output is of "normally closed" (NC) type.

- **7.** A detection system, **characterized in that** it comprises:

- a processing logic unit comprising at least one

input (in1) and one test output (Out\_test),

- a detector (D1) as defined in one of the preceding claims, the first output terminal (01) of which is connected to said input (in1) of the processing logic unit (2) and a power supply terminal (A1, A2) of which is connected to the test output of the processing logic unit (2), the processing logic unit (2) being arranged to generate a test input signal (S\_test) applied to said power supply terminal of the detector (D1) in order to test each output (NO, NC) of the detector (D1) connected to the processing logic unit (2).

- 8. A detection system, characterized in that it comprises:

- a processing logic unit comprising two inputs (in1, in2) and two power supply terminals (+, -), a detector (D1) as defined in one of the preceding claims, the two power supply terminals (A1, A2) of which are connected to the two power supply terminals (+, -) of the processing logic unit (2) and the two output terminals (O1, O2) of which are connected to the two inputs (in1, in2) of the processing logic unit (2) so as to offer redundancy between the two outputs of the detector.

Fig. 1

Fig. 3A

Fig. 3B

## EP 2 912 646 B1

## RÉFÉRENCES CITÉES DANS LA DESCRIPTION

Cette liste de références citées par le demandeur vise uniquement à aider le lecteur et ne fait pas partie du document de brevet européen. Même si le plus grand soin a été accordé à sa conception, des erreurs ou des omissions ne peuvent être exclues et l'OEB décline toute responsabilité à cet égard.

## Documents brevets cités dans la description

• US 20050112942 A [0010]