### (11) EP 3 007 279 A1

(12) EUROPÄISCHE PATENTANMELDUNG

(43) Veröffentlichungstag: 13.04.2016 Patentblatt 2016/15

(51) Int Cl.: H01R 12/73<sup>(2011.01)</sup>

H01R 12/71 (2011.01)

(21) Anmeldenummer: 14188309.0

(22) Anmeldetag: 09.10.2014

(84) Benannte Vertragsstaaten:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

Benannte Erstreckungsstaaten:

**BA ME**

(71) Anmelder: Siemens Aktiengesellschaft 80333 München (DE)

(72) Erfinder:

• Blei, Hendrik 90491 Nürnberg (DE)

Fürholzer, Roland

92224 Amberg (DE)

### (54) Leiterplattenanordnung

(57) Die Erfindung betrifft eine Leiterplattenanordnung (1) umfassend,

- eine erste Leiterplatte (11) mit einer Oberseite (11a) und einer Unterseite (11b),

- eine zweite Leiterplatte (12) mit einer Oberseite (12a) und einer Unterseite (12b),

- eine Stiftleiste (13),

- eine Buchsenleiste (14),

wobei die Stiftleiste (13) auf der ersten Leiterplatte (11) und die Buchsenleiste (14) auf der zweiten Leiterplatte (12) angeordnet ist, die Stiftleiste (13) und die Buchsenleiste (14) sind derart ausgestaltet, dass sie mehrere Stifte (31,32) bzw. Buchsen (71,72) aufweisen, welche beim

Zusammenstecken von Stiftleiste (13) und Buchsenleiste (14) elektrisch miteinander kontaktieren, um elektrische Verbindungswege von der ersten Leiterplatte (11) zu der zweiten Leiterplatte (12) herzustellen,

wobei die Stiftleiste (13) auf der Oberseite (11a) der ersten Leiterplatte (11) angeordnet ist, wobei die Stifte (31,32) der Stiftleiste (13) durch die erste Leiterplatte (11) hindurchgeführt angeordnet sind,

die Buchsenleiste (14) auf der zweiten Leiterplatte (12) derart angeordnet ist, dass in den Buchsen (71,72) der Buchsenleiste (14) die Stifte (31,32) der Stiftleiste (13) angeordnet sind, wobei sich die Unterseite (11b) der ersten Leiterplatte (11) und die Unterseite (12b) der zweiten Leiterplatte (12) gegenüberstehen.

FIG 4

EP 3 007 279 A1

1

#### Beschreibung

[0001] Die Erfindung betrifft eine Leiterplattenanordnung mit einer ersten Leiterplatte mit einer Oberseite und einer Unterseite, einer zweiten Leiterplatte mit einer Oberseite und einer Unterseite, eine Stiftleiste, eine Buchsenleiste, wobei die Stiftleiste auf der ersten Leiterplatte und die Buchsenleiste auf der zweiten Leiterplatte angeordnet ist, dabei sind die Stiftleiste und die Buchsenleiste derart ausgestaltet, dass mehrere Stifte bzw. mehrere Buchsen vorhanden sind, welche beim Zusammenstecken von Stiftleiste und Buchsenleiste elektrisch miteinander kontaktieren, um Verbindungswege von der ersten Leiterplatte zu der zweiten Leiterplatte herzustellen

[0002] Bei der Entwicklung elektronischer Baugruppen tritt das Problem eines begrenzten Bauraums für die erforderlichen Komponenten der elektronischen Baugruppe auf. Ein wichtiger Gesichtspunkt ist hier ein Abstand zweier Leiterplatten zueinander, die miteinander, insbesondere über sogenannte Boardto-Board-Verbinder verbunden sind. Oftmals ist eine Bauhöhe eines Steckverbinders, welcher eine Stiftleiste und eine Buchsenleiste umfasst, die bestimmende Größe des Mindestabstandes A zwischen den zu verbindenden Leiterplatten.

[0003] Bisher wurde durch die Auswahl möglichst kleiner Steckverbinder versucht, den Abstand der zu verbindenden Leiterplatten möglichst gering zu halten. Dabei wurden die beiden Seiten des Steckverbinderpärchens (Stiftleiste und Buchsenleiste) auf die sich jeweils gegenüberliegenden einander zugewandten Seiten der Leiterplatten bestückt.

**[0004]** Der vorliegenden Erfindung liegt die Aufgabe zugrunde, eine Leiterplattenanordnung zu schaffen, bei welcher bei einer Verbindung der beiden Leiterplatten mit einer Stiftleiste und einer Buchsenleiste ein Abstand der beiden Leiterplatten zueinander minimiert wird.

[0005] Bei der eingangs genannten Leiterplattenanordnung mit der ersten Leiterplatte und der zweiten Leiterplatte wird die Aufgabe dadurch gelöst, dass die Stiftleiste auf der Oberseite der ersten Leiterplatte angeordnet ist, wobei die Stifte der Stiftleiste durch die erste Leiterplatte hindurchgeführt angeordnet sind, die Buchsenleiste ist dabei auf der zweiten Leiterplatte derart angeordnet, das in den Buchsen der Buchsenleiste die Stifte der Stiftleiste angeordnet sind, wobei sich die Unterseite der ersten Leiterplatte und die Unterseite der zweiten Leiterplatte gegenüberstehen. Um auf vorteilhafter Weise den Abstand zwischen der ersten Leiterplatte und der zweiten Leiterplatte zu minimieren, wird die Stiftleiste auf der Oberseite der ersten Leiterplatte bestückt. Dabei werden die Stifte der Stiftleiste durch die Leiterplatte geschoben, so dass ein Isolierkörper der Stiftleiste sich nun nicht mehr auf den Abstand zwischen der ersten Leiterplatte und der zweiten Leiterplatte zueinander auswirkt. So kann der Abstand der Leiterplatten um die Höhe des Isolierkörpers der Stiftleiste verringert werden.

[0006] In einer weiteren Optimierung der Leiterplattenanordnung ist es von Vorteil, wenn die Buchsenleiste einen Buchsenleistenisolierkörper aufweist und die erste

Leiterplatte eine Ausnehmung aufweist, in welche der

Buchsenleistenisolierkörper zumindest teilweise eindringen kann. Durch diese Anordnung verringert sich der Abstand der beiden Leiterplatten zueinander nochmals um

die Höhe des Buchsenleistenisolierkörpers.

[0007] Ein Minimum an einem Abstand A der beiden Leiterplatten zueinander kann erreicht werden, wenn die Buchsenleiste auf der Oberseite der zweiten Leiterplatte angeordnet ist, wobei die Stifte der Stiftleiste durch die zweite Leiterplatte hindurchgeführt und in den Buchsen der Buchsenleiste angeordnet sind. Der Bauraum des Isolierkörpers der Stiftleiste und des Buchsenleistenisolierkörpers hat nun keine Auswirkungen mehr auf dem Abstand der Leiterplatten zueinander. Dadurch kann ein erforderlicher Bauraum einer elektronischen Baugruppe erheblich verkleinert werden. Ein weiterer Vorteil dieser Anordnung ist, dass eine beidseitige Bestückung einer Leiterplatte vermieden werden kann. Dadurch können beim Bestückund Lötprozess Arbeitsschritte und damit Kosten gespart werden.

[0008] Insbesondere von Vorteil ist es, wenn die Stiftleiste und/oder die Buchsenleiste derart ausgestaltet sind, dass als Montageart ein THT-Lötverfahren oder ein SMD-Lötverfahren Anwendung findet.

[0009] Gemäß der Zeichnung werden Ausführungsbeispiele der Erfindung gezeigt und näher erläutert. Es zeigen

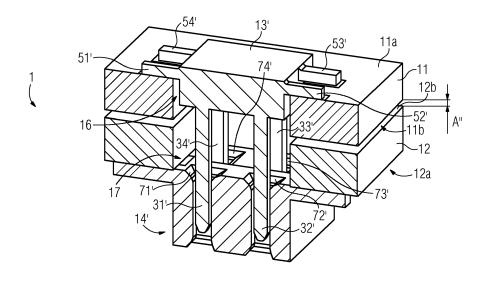

- FIG 1 eine Leiterplattenanordnung gemäß einer ersten Ausgestaltungsvariante,

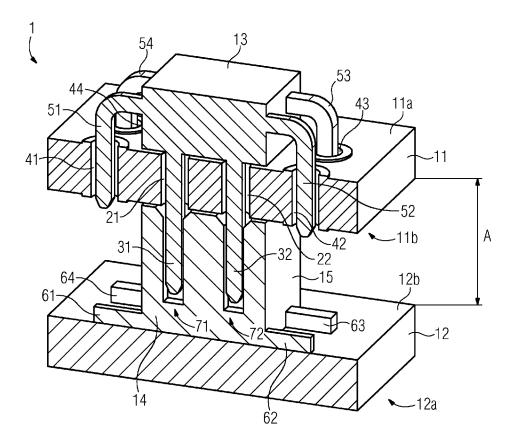

- FIG 2 eine Leiterplattenanordnung gemäß einer zweiten Ausgestaltungsvariante,

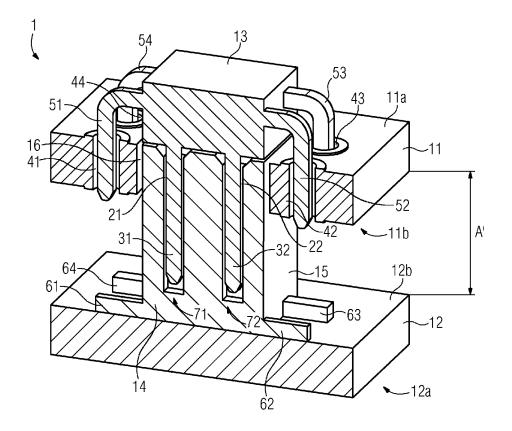

- FIG 3 eine Leiterplattenanordnung gemäß einer dritten Ausgestaltungsvariante und die

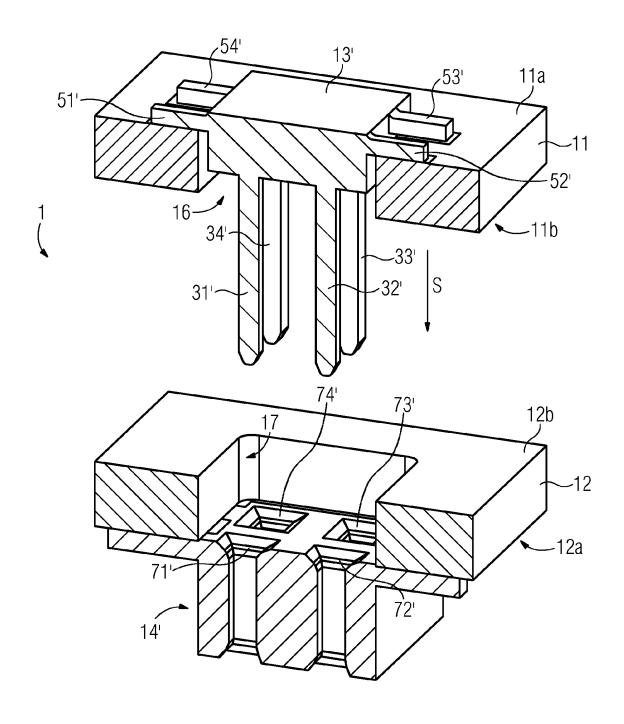

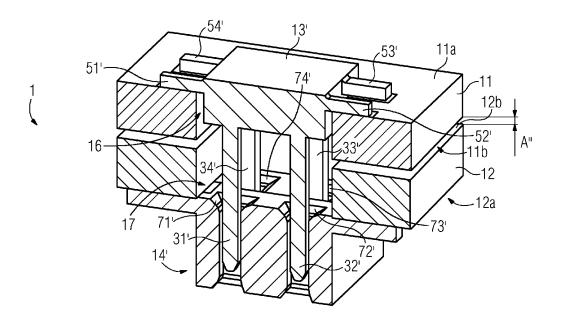

- FIG 4 die Leiterplattenanordnung gemäß FIG 3 in einer zusammengesteckten Darstellung.

[0010] Gemäß FIG 1 ist eine Leiterplattenanordnung 1 umfassend, eine erste Leiterplatte 11 mit einer Oberseite 11a und einer Unterseite 11b, eine zweite Leiterplatte 12 mit einer Oberseite 12a und einer Unterseite 12b, einer Stiftleiste 13, und eine Buchsenleiste 14 gezeigt. Die Stiftleiste 13 und die Buchsenleiste 14 agieren als ein Steckverbinderpärchen.

[0011] Die Stiftleiste 13 ist auf der ersten Leiterplatte 11 und die Buchsenleiste 14 ist auf der zweiten Leiterplatte 12 angeordnet. Die Stiftleiste 13 ist mit einem ersten Stift 31, einem zweiten Stift 32, einem dritten Stift 33 und einem vierten Stift 34 versehen, wobei in dieser Darstellung der dritte und der vierte Stift nicht sichtbar sind. Die Buchsenleiste 14 weist eine erste Buchse 71, eine zweite Buchse 72, eine dritte Buchse und eine vierte

40

45

40

Buchse auf, wobei auch hier wiederum die dritte und die vierte Buchse nicht sichtbar sind.

**[0012]** Die Stifte 31,32 bzw. die Buchsen 71,72 kontaktieren beim Zusammenstecken von Stiftleiste 13 und Buchsenleiste 14 elektrisch miteinander, um elektrische Verbindungswege von der ersten Leiterplatte 11 zu der zweiten Leiterplatte 12 herzustellen.

[0013] Um einen Abstand A der Leiterplatten 11,12 zueinander zu minimieren, ist die Stiftleiste 13 auf der Oberseite 11a der ersten Leiterplatte 11 angeordnet, wobei die Stifte 31,32 der Stiftleiste 13 durch die erste Leiterplatte 11 hindurchgeführt angeordnet sind, dabei ist die Buchsenleiste 14 derart auf der zweiten Leiterplatte 12 angeordnet, dass in den Buchsen 71,72 der Buchsenleiste 14 die Stifte 31,32 der Stiftleiste 13 angeordnet sind, wobei sich die Unterseite 11b der ersten Leiterplatte 11 und die Unterseite 12b der zweiten Leiterplatte 12 gegenüberstehen.

[0014] Wird eine Seite des Steckverbinderpärchens, nämlich die Stiftleiste 13, auf die Oberseite 11a der ersten Leiterplatte 11 bestückt, und werden dabei die Stifte durch die erste Leiterplatte 11 geschoben, so wirkt sich ein Isolierkörper der Stiftleiste 13 nun nicht mehr auf den Abstand A der beiden Leiterplatten 11,12 zueinander aus. Der Abstand A der beiden Leiterplatten zueinander kann um die Höhe des Isolierkörpers der Stiftleiste 13 verringert werden.

[0015] Um die Stiftleiste 13 auf der Oberseite 11a der ersten Leiterplatte 11 zu bestücken, weist die erste Leiterplatte 11 eine erste Bauteilbohrung 41, eine zweite Bauteilbohrung 42, eine dritte Bauteilbohrung 43 und eine vierte Bauteilbohrung 44 auf. In den Bauteilbohrungen 41,42,43,44 wird jeweils ein erstes Anschlussbein 51, ein zweites Anschlussbein 52, ein drittes Anschlussbein 53 und ein viertes Anschlussbein 54 angeordnet. Die Anschlussbeine 51,52,53,54 der Stiftleiste 13 können in einem THT-Lötverfahren verlötet werden.

[0016] Die Anschlussbeine 51,52,53,54 stellen jeweils die Verbindung zu den Stiften der Stiftleiste 13 her. Die Buchsenleiste 14 weist einen Buchsenleistenisolierkörper 14 auf. In diesem Buchsenleistenisolierkörper 14 sind die erste Buchse 71, die zweite Buchse 72, eine dritte Buchse und eine vierte Buchse angeordnet, wobei wiederum die Stifte 31,32 der Stiftleiste 13 in den Buchsen 71,72 der Buchsenleiste 14 angeordnet sind.

[0017] Die Buchsenleiste 14 ist über eine erste Lötfläche 61, eine zweite Lötfläche 62, eine dritte Lötfläche 63 und eine vierte Lötfläche 64 auf die zweite Leiterplatte 12 angelötet. Durch die Ausmaße des Buchsenleistenisolierkörpers 15 ergibt sich der Abstand A der ersten Leiterplatte 11 zu der zweiten Leiterplatte 12. Bei dieser Ausgestaltungsvariante ist der Abstand A bereits um eine Bauhöhe eines Isolierkörpers der Stiftleiste 13 reduziert worden.

[0018] Gemäß FIG 2 wird eine zweite Ausgestaltungsvariante der Erfindung gezeigt. Durch das Einbringen einer Ausnehmung 16 in die erste Leiterplatte 11 kann der Abstand A aus FIG 1 der Leiterplatten 11,12 zueinander

auf einen Abstand A' gemäß der FIG 2 reduziert werden. Die Ausnehmung 16 in der ersten Leiterplatte 11 ermöglicht es, dass der Buchsenleistenisolierkörper 15 der Buchsenleiste 14 in die Ausnehmung 16 teilweise eindringen kann und somit den Abstand A der beiden Leiterplatten 11,12 zueinander auf einen reduzierten Abstand A' verkleinert wird.

**[0019]** Mit der FIG 3 wird eine dritte Variante der Leiterplattenanordnung 1 aufgezeigt. Mit dieser Variante kann der Abstand A der beiden Leiterplatten 11,12 theoretisch bis auf null Millimeter reduziert werden.

[0020] Die FIG 3 zeigt die erste Leiterplatte 11 und die zweite Leiterplatte 12 quasi in einer Explosionsdarstellung. Das bedeutet, wird die erste Leiterplatte 11 in einer Steckrichtung S zu der zweiten Leiterplatte 12 bewegt, so können die Stifte der Stiftleiste in die Buchsen der Buchsenleiste eindringen. Da es sich im Gegensatz zu der Darstellung gemäß FIG 1 und FIG 2 bei der Stiftleiste gemäß FIG 3 um eine andere Bauform von Stiftleiste handelt, nämlich um eine SMD-Bauform, werden gemäß der FIG 3 die Bezugszeichen für diese weitere Bauform von Stiftleiste und deren Stifte mit einem Strich indiziert. Auf der ersten Leiterplatte 11 ist damit eine Stiftleiste 13' mit einem ersten Stift 31', einem zweiten Stift 32', einem dritten Stift 33' und einem vierten Stift 34' angeordnet. Um die Stiftleiste 13' auf der ersten Leiterplatte 11 zu bestücken, weist die Stiftleiste 13' ein ersten Anschlussbein 51', ein zweites Anschlussbein 52', ein drittes Anschlussbein 53' und ein viertes Anschlussbein 54' auf. Die Anschlussbeine 51', 52', 53', 54' sind in der SMD-Technologie ausgeführt. Wie bereits mit der Ausgestaltungsvariante gemäß FIG 2 gezeigt, weist die erste Leiterplatte 11 die Ausnehmung 16 auf. Um nun den Abstand A der ersten Leiterplatte 11 zu der zweiten Leiterplatte 12 weiter zu reduzieren, weist auf vorteilhafte Weise die zweite Leiterplatte 12 eine weitere Ausnehmung 17 auf. Auch hier ist wieder die Stiftleiste 13' auf der Oberseite 11a der ersten Leiterplatte 11 angeordnet, da die Buchsenleiste 14' (ebenfalls in SMD-Technik aufgebaut) nun auch auf der Oberseite 12a der zweiten Leiterplatte 12 angeordnet ist und die Stifte 31', 32', 33', 34' der Stiftleiste 13' durch die zweite Leiterplatte 12 hindurchführbar sind und in den Buchsen 71', 72', 73', 74' der Buchsenleiste 14' angeordnet werden können, kann der Abstand A der beiden Leiterplatten nahezu auf null Millimeter reduziert werden.

[0021] Mit der FIG 4 wird die Abstandsreduzierung auf einen Abstand A'' verdeutlicht. Bei dieser Leiterplattenanordnung gemäß den Figuren 3 und 4 sollte die Buchsenleiste 14' als eine beidseitig kontaktierbare Buchsenleiste 14 ausgestaltet werden, dadurch kann der Abstand

A'' der beiden Leiterplatten 11,12 zueinander frei gewählt

werden. Bei einem minimalen Abstand von beispielsweise null Millimeter der beiden Leiterplatten zueinander

können die Stifte der Stiftleiste 13' komplett durch die

Buchsen der Buchsenleiste 14' hindurchdringen und sogar etwas überstehen. Bei einem anders gewählten Abstand z.B. 3 Millimeter der Leiterplatten 11,12 zueinander

15

5

würden die Stifte der Stiftleiste 13 in den Buchsen der Buchsenleiste 14' entsprechend etwas höher angeordnet sein.

Patentansprüche

1. Leiterplattenanordnung (1) umfassend,

- eine erste Leiterplatte (11) mit einer Oberseite (11a) und einer Unterseite (11b),

- eine zweite Leiterplatte (12) mit einer Oberseite (12a) und einer Unterseite (12b),

- eine Stiftleiste (13),

- eine Buchsenleiste (14),

wobei die Stiftleiste (13) auf der ersten Leiterplatte (11) und die Buchsenleiste (14) auf der zweiten Leiterplatte (12) angeordnet ist, die Stiftleiste (13) und die Buchsenleiste (14) sind derart ausgestaltet, dass sie mehrere Stifte (31,32) bzw. Buchsen (71,72) aufweisen, welche beim Zusammenstecken von Stiftleiste (13) und Buchsenleiste (14) elektrisch miteinander kontaktieren, um elektrische Verbindungswege von der ersten Leiterplatte (11) zu der zweiten Leiterplatte (12) herzustellen,

dadurch gekennzeichnet, dass die Stiftleiste (13) auf der Oberseite (11a) der ersten Leiterplatte (11) angeordnet ist, wobei die Stifte (31,32) der Stiftleiste (13) durch die erste Leiterplatte (11) hindurchgeführt angeordnet sind,

die Buchsenleiste (14) auf der zweiten Leiterplatte (12) derart angeordnet ist, dass in den Buchsen (71,72) der Buchsenleiste (14) die Stifte (31,32) der Stiftleiste (13) angeordnet sind, wobei sich die Unterseite (11b) der ersten Leiterplatte (11) und die Unterseite (12b) der zweiten Leiterplatte (12) gegenüberstehen.

- Leiterplattenanordnung (1) nach Anspruch 1, wobei die Buchsenleiste (14) einen Buchsenleistenisolierkörper (15) aufweist und die erste Leiterplatte (11) eine Ausnehmung (16) aufweist, in welche der Buchsenleistenisolierkörper (15) zumindest teilweise eindringen kann.

- 3. Leiterplattenanordnung (1) nach Anspruch 1, wobei die Buchsenleiste (14) auf der Oberseite (12a) der zweiten Leiterplatte (12) angeordnet ist, wobei die Stifte der Stiftleiste (13) durch die zweite Leiterplatte (12) hindurchgeführt und in den Buchsen der Buchsenleiste (14) angeordnet sind.

- **4.** Leiterplattenanordnung (1) nach Anspruch 3, wobei die Buchsenleiste (14) als eine beidseitig kontaktierbare Buchsenleiste ausgestaltet ist.

- 5. Leiterplattenanordnung (1) nach einem der Ansprü-

che 1 bis 4, wobei die Stiftleiste (13) und/oder die Buchsenleiste (14) derart ausgestaltet sind, dass als Montageart ein THT-Lötverfahren oder ein SMD-Lötverfahren Anwendung findet.

45

## FIG 1

### FIG 2

FIG 3

FIG 4

Kategorie

#### **EUROPÄISCHER RECHERCHENBERICHT**

**EINSCHLÄGIGE DOKUMENTE**

Kennzeichnung des Dokuments mit Angabe, soweit erforderlich, der maßgeblichen Teile

Nummer der Anmeldung EP 14 18 8309

KLASSIFIKATION DER ANMELDUNG (IPC)

Betrifft

Anspruch

5

10

15

20

25

30

35

40

45

50

55

| X                          | WO 94/02975 A1 (BEF<br>3. Februar 1994 (19<br>* Seite 5, Zeilen 1                                                                              | 94-02-03)                                               | BV)                                                                                                                                                                                                                                                                 | 1,2,5                          | INV.<br>H01R12/7 | 3 |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------|---|--|

|                            | * Seite 7, Zeile 18<br>* Abbildungen 1-14                                                                                                      | 3 - Seite 9, Zeile                                      | 35 *                                                                                                                                                                                                                                                                |                                | ADD.<br>H01R12/7 | 1 |  |

| X                          | JP 2012 138320 A (3<br>19. Juli 2012 (2012<br>* Zusammenfassung;                                                                               | :-07-19)                                                |                                                                                                                                                                                                                                                                     | 1,2,5                          |                  |   |  |

| X                          | WO 2007/056291 A1 (<br>[US]; BREKOSKY LAWF<br>KEITH) 18. Mai 2007<br>* Zusammenfassung;                                                        | RENCE JOHN [US]; M<br>' (2007-05-18)                    | ILLER                                                                                                                                                                                                                                                               | 1,3,4                          |                  |   |  |

| A                          | WO 93/16504 A1 (ELC<br>19. August 1993 (19<br>* Seite 3, Zeile 18<br>Abbildung 1 *                                                             | 93-08-19)                                               | 3;                                                                                                                                                                                                                                                                  | 1-5                            |                  |   |  |

| A                          | WO 2004/086831 A2 (<br>KRUEGER MARIO [DE];<br>WACKER FRANZ) 7. OF<br>* Zusammenfassung;                                                        | PAUL REINHOLD [D<br>-tober 2004 (2004                   | 1-5                                                                                                                                                                                                                                                                 | RECHERCHI<br>SACHGEBIE<br>H01R |                  |   |  |

|                            |                                                                                                                                                |                                                         |                                                                                                                                                                                                                                                                     |                                |                  |   |  |

|                            |                                                                                                                                                |                                                         |                                                                                                                                                                                                                                                                     |                                |                  |   |  |

|                            |                                                                                                                                                |                                                         |                                                                                                                                                                                                                                                                     |                                |                  |   |  |

|                            |                                                                                                                                                |                                                         |                                                                                                                                                                                                                                                                     |                                |                  |   |  |

| Der vo                     | orliegende Recherchenbericht wu                                                                                                                | rde für alle Patentansprüche e                          | erstellt                                                                                                                                                                                                                                                            |                                |                  |   |  |

|                            | Recherchenort                                                                                                                                  | Abschlußdatum der Recherche  16. März 2015              |                                                                                                                                                                                                                                                                     | Georgiadis, Ioannis            |                  |   |  |

| . v.                       | Den Haag  ATEGORIE DER GENANNTEN DOK                                                                                                           |                                                         |                                                                                                                                                                                                                                                                     |                                |                  |   |  |

| X : von<br>Y : von<br>ande | besonderer Bedeutung allein betrach<br>besonderer Bedeutung in Verbindung<br>eren Veröffentlichung derselben Kateg<br>nnologischer Hintergrund | E : ältere tet nach mit einer D : in de torie L : aus a | T : der Erfindung zugrunde liegende Theorien oder Grundsätze<br>E : älteres Patentdokument, das jedoch erst am oder<br>nach dem Anmeldedatum veröffentlicht worden ist<br>D : in der Anmeldung angeführtes Dokument<br>L : aus anderen Gründen angeführtes Dokument |                                |                  |   |  |

| O : nich<br>P : Zwir       | ntschriftliche Offenbarung<br>schenliteratur                                                                                                   |                                                         | en Patentfamilie, übereinstimmendes                                                                                                                                                                                                                                 |                                |                  |   |  |

#### EP 3 007 279 A1

### ANHANG ZUM EUROPÄISCHEN RECHERCHENBERICHT ÜBER DIE EUROPÄISCHE PATENTANMELDUNG NR.

EP 14 18 8309

In diesem Anhang sind die Mitglieder der Patentfamilien der im obengenannten europäischen Recherchenbericht angeführten Patentdokumente angegeben.

Patentdokumente angegeben.

Die Angaben über die Familienmitglieder entsprechen dem Stand der Datei des Europäischen Patentamts am Diese Angaben dienen nur zur Unterrichtung und erfolgen ohne Gewähr.

16-03-2015

| WO 946 | 02975    | A1 | 03-02-1994 | D.E.                                         |                                                                                                 | I                              | Veröffentlichung                                                                                             |

|--------|----------|----|------------|----------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------|

|        |          |    |            | DE<br>DE<br>EP<br>JP<br>SG<br>TW<br>US<br>WO | 650643<br>69326613<br>69326613<br>0650643<br>H07509342<br>49161<br>234212<br>5919051<br>9402975 | D1<br>T2<br>A1<br>A<br>A1<br>B | 18-01-1996<br>04-11-1999<br>26-08-2004<br>03-05-1999<br>12-10-1999<br>18-05-1999<br>06-07-1999<br>03-02-1994 |

| JP 201 | 12138320 | A  | 19-07-2012 | CN<br>JP<br>KR<br>TW                         | 102570080<br>2012138320<br>20120075341<br>201244267                                             | A<br>A                         | 11-07-2012<br>19-07-2012<br>06-07-2012<br>01-11-2012                                                         |

| WO 200 | 07056291 | A1 | 18-05-2007 | CA<br>CN<br>EP<br>US<br>WO                   | 2626854<br>101305500<br>1949504<br>2007105409<br>2007056291                                     | A<br>A1<br>A1                  | 18-05-2007<br>12-11-2008<br>30-07-2008<br>10-05-2007<br>18-05-2007                                           |

| WO 931 | 16504    | A1 | 19-08-1993 | KEIN                                         | NE                                                                                              |                                |                                                                                                              |

| WO 200 | 04086831 | A2 | 07-10-2004 | CN<br>DE<br>EP<br>WO                         | 1765160<br>10313622<br>1606982<br>2004086831                                                    | B3<br>A2                       | 26-04-2000<br>13-01-2000<br>21-12-2000<br>07-10-2004                                                         |

Für nähere Einzelheiten zu diesem Anhang : siehe Amtsblatt des Europäischen Patentamts, Nr.12/82