# (11) EP 3 176 669 A1

# (12)

# **DEMANDE DE BREVET EUROPEEN**

(43) Date de publication:

07.06.2017 Bulletin 2017/23

(51) Int Cl.: **G05F** 3/24 (2006.01)

(21) Numéro de dépôt: 16200987.2

(22) Date de dépôt: 28.11.2016

(84) Etats contractants désignés:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

Etats d'extension désignés:

**BA ME**

Etats de validation désignés:

MA MD

(30) Priorité: 30.11.2015 FR 1561551

- (71) Demandeur: COMMISSARIAT À L'ÉNERGIE ATOMIQUE ET AUX ÉNERGIES ALTERNATIVES 75015 Paris (FR)

- (72) Inventeur: QUELEN, Anthony 38180 SEYSSINS (FR)

- (74) Mandataire: Thibon, Laurent et al Cabinet Beaumont

1, rue Champollion

38000 Grenoble (FR)

# (54) CIRCUIT DE GÉNÉRATION D'UNE TENSION DE RÉFÉRENCE

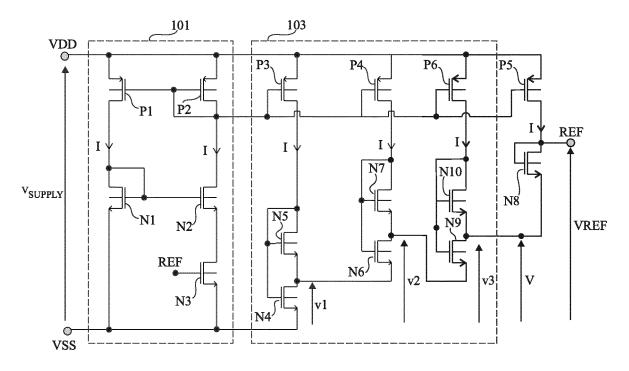

(57) L'invention concerne un circuit FDSOI de génération d'une tension de référence (V<sub>REF</sub>), comportant : un circuit (101) de génération d'un courant CTAT (I) ; un circuit (103) de génération d'une tension PTAT (V), comportant une première branche comportant des premier (N4) et deuxième (N5) transistors en série, les grilles de face avant des premier (N4) et deuxième (N5) transistors étant connectées au noeud de conduction du deuxième (N5) transistor opposé au premier transistor (N4) ;

un troisième transistor (N8) monté en diode dont un noeud de conduction est connecté à un noeud de sortie du circuit de génération de la tension PTAT et dont l'autre noeud de conduction constitue un noeud de fourniture de la tension de référence (V<sub>REF</sub>); et

un miroir de courant (P2, P3, P5),

dans lequel les premier (N4) et deuxième (N5) transistors sont de type LVT, et le troisième transistor (N8) est de type RVT.

Fig 1

# Description

#### Domaine

[0001] La présente demande concerne le domaine des systèmes électroniques de façon générale, et vise plus particulièrement un circuit de génération d'une tension de référence.

### Exposé de l'art antérieur

[0002] Dans de nombreux systèmes électroniques, on utilise un circuit de génération d'une tension de référence pour produire, à partir d'une tension d'alimentation continue du système, une tension de référence continue indépendante des fluctuations de la tension d'alimentation et indépendante des variations de température. Un tel circuit est généralement intégré dans une puce semiconductrice qui peut être une puce autonome ou qui peut comporter d'autres circuits destinés à mettre en oeuvre d'autres fonctions du système.

[0003] On a déjà proposé des circuits de génération d'une tension de référence réalisés à base de transistors bipolaires. Un inconvénient de ces circuits est que, pour obtenir une bonne stabilité en température, la tension de référence doit être relativement élevée, typiquement de l'ordre de 1,2 V.

[0004] Dans certains systèmes électroniques, notamment dans des systèmes à faible tension d'alimentation (par exemple des systèmes destinés à être alimentés sous une tension comprise entre 1,2 V et 4 V), on souhaite pouvoir disposer d'une tension de référence moins élevée, typiquement inférieure à 1 V, par exemple une tension de l'ordre de 0,9 V. Des circuits de génération d'une tension de référence inférieure à 1 V réalisés à base de transistors MOS ont été proposés. Des exemples de tels circuits sont notamment décrits dans les publications suivantes : [1] "A 300 nW, 15 ppm/ C, 20 ppm/V CMOS Voltage Reference Circuit Consisting of Subthreshold MOSFETs", Ken Ueno, IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 44, NO. 7, JULY 2009 ; [2] "173nA-7.5ppm/C-771mV-0.03mm2 CMOS Resistorless Voltage Reference", A. Samir, 2011 Faible Tension Faible Consommation (FTFC) ; [3] "A 280NA , 87PPM/oC, HIGH PSRR FULL CMOS VOLTAGE REFERENCE AND ITS APPLICATION", Song QIN, 978-1-4673-1717-7112/\$31.00 ©2012 IEEE ; [4] "A Sub-1-V, 10 ppm/ C, Nanopower Voltage Reference generator", Giuseppe De Vita, IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 42, NO. 7, JULY 2007 ; [5] "A Sub-1V 32nA Process, Voltage and Temperature Invariant Voltage Reference Circuit", Anvesha A, 2013 26th International Conference on VLSI Design ; et [6] "1.2-V Supply, 100-nW, 1.09-V Bandgap and 0.7-V Supply, 52.5-nW, 0.55-V Subbandgap Reference Circuits for Nanowatt CMOS LSIs", Yuji Osaki, IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 48, NO. 6, JUNE 2013.

[0005] Ces circuits présentent toutefois divers inconvénients. En particulier, ces circuits sont relativement sensibles aux variations de procédé de fabrication, et ont en conséquence une précision intrinsèque relativement faible. En d'autres termes, deux circuits distincts réalisés selon le même procédé peuvent, du fait des dispersions de procédé, générer des tensions de référence distinctes. Dans le circuit décrit dans l'article [1] susmentionné, la variabilité de la tension de référence en fonction des variations de procédé de fabrication est d'ailleurs recherchée et exploitée pour caractériser et compenser les dispersions de procédé.

**[0006]** On s'intéresse ici plus particulièrement à la réalisation d'un circuit de génération d'une tension de référence à base de transistors MOS, ce circuit présentant une meilleure précision intrinsèque que les circuits connus, c'est-à-dire fournissant une tension de référence moins dépendante des dispersions de procédé que les circuits connus.

[0007] On notera que pour garantir que des puces distinctes fournissent bien la même tension de référence, des étapes d'ajustement post fabrication peuvent être prévues. Toutefois, ces étapes, ainsi que la prévision éventuelle de composants d'ajustement sur les puces, engendrent un surcoût d'autant plus élevé que la précision intrinsèque du circuit est faible.

[0008] Il serait souhaitable de pouvoir disposer d'un circuit de génération d'une tension de référence palliant tout ou partie des inconvénients des circuits connus, et présentant en particulier une meilleure précision intrinsèque que les circuits connus.

# Résumé

50

55

20

30

35

40

[0009] Ainsi, un mode de réalisation prévoit un circuit de génération d'une tension de référence réalisé en technologie FDSOI, comportant : un premier circuit de génération d'un courant de polarisation de type CTAT ; un deuxième circuit de génération d'une tension de type PTAT comportant une première branche comportant des premier et deuxième transistors en série, les grilles de face avant des premier et deuxième transistors étant connectées au noeud de conduction du deuxième transistor opposé au premier transistor ; un troisième transistor monté en diode dont un noeud de conduction est connecté à un noeud de fourniture de la tension de sortie du deuxième circuit et dont l'autre noeud de conduction constitue un noeud de fourniture de la tension de référence ; et un miroir de courant imposant, dans le troisième transistor d'une part et dans la première branche d'autre part, des courants proportionnels au courant de polarisation, dans lequel

les premier et deuxième transistors sont de type LVT, et le troisième transistor est de type RVT.

[0010] Selon un mode de réalisation, le premier transistor présente une première épaisseur d'oxyde de grille de face avant, et les deuxième et troisième transistors présentent une deuxième épaisseur d'oxyde de grille de face avant supérieure à la première épaisseur.

**[0011]** Selon un mode de réalisation, les premier, deuxième et troisième transistors sont des transistors NMOS, le drain du premier transistor étant connecté à la source du deuxième transistor, le drain du deuxième transistor étant connecté aux grilles des premier et deuxième transistors, et la source du troisième transistor étant connectée à un noeud de fourniture de la tension de sortie du deuxième circuit.

[0012] Selon un mode de réalisation, le deuxième circuit comprend en outre une deuxième branche comportant des quatrième et cinquième transistors en série, les grilles de face avant des quatrième et cinquième transistors étant connectées au noeud de conduction du cinquième transistor opposé au quatrième transistor, et le noeud de conduction du quatrième transistor opposé au cinquième transistor étant connecté au point milieu de l'association en série des premier et deuxième transistors.

[0013] Selon un mode de réalisation, le miroir de courant impose dans la deuxième branche un courant proportionnel au courant de polarisation.

[0014] Selon un mode de réalisation, le point milieu de l'association en série des quatrième et cinquième transistors constitue un noeud de fourniture de la tension de sortie du deuxième circuit.

**[0015]** Selon un mode de réalisation, les quatrième et cinquième transistors sont des transistors NMOS, le drain du quatrième transistor étant connecté à la source du cinquième transistor, et le drain du cinquième transistor étant connecté aux grilles des quatrième et cinquième transistors.

[0016] Selon un mode de réalisation, les quatrième et cinquième transistors sont tous deux de type RVT ou tous deux de type LVT.

**[0017]** Selon un mode de réalisation, le premier circuit comprend des sixième et septième transistors montés en miroir de courant, et un huitième transistor connecté en série avec le septième transistor, les sixième et septième transistors étant de même type LVT ou RVT et présentant la même épaisseur d'oxyde de grille de face avant, et le sixième transistor ayant un rapport largeur de canal sur longueur de canal supérieur à celui du septième transistor.

[0018] Selon un mode de réalisation, le huitième transistor est de type LVT.

[0019] Selon un mode de réalisation, les sixième, septième et huitième transistors sont de type NMOS.

[0020] Selon un mode de réalisation, le huitième transistor a sa grille de face avant reliée au noeud de fourniture de la tension de référence.

### Brève description des dessins

10

20

30

35

40

45

50

55

**[0021]** Ces caractéristiques et avantages, ainsi que d'autres, seront exposés en détail dans la description suivante de modes de réalisation particuliers faite à titre non limitatif en relation avec les figures jointes parmi lesquelles :

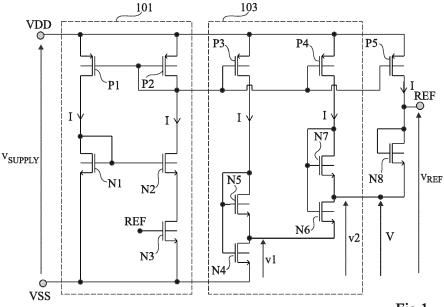

la figure 1 est un schéma électrique d'un exemple d'un mode de réalisation d'un circuit de génération d'une tension de référence :

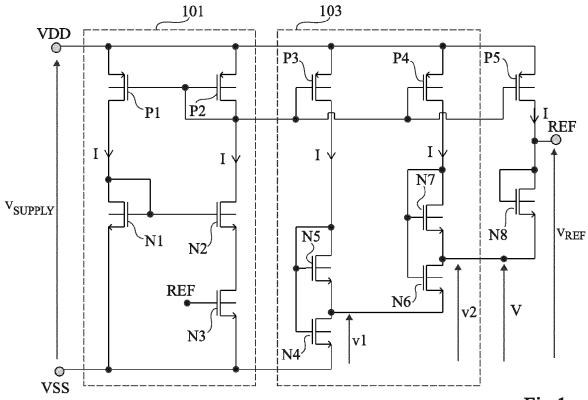

la figure 2 est un diagramme illustrant le fonctionnement du circuit de la figure 1;

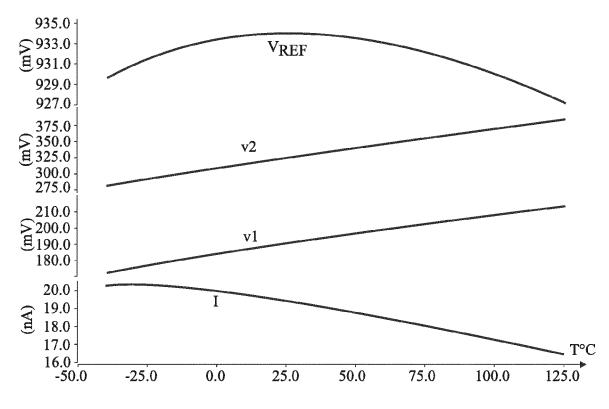

la figure 3 est un diagramme représentant la sensibilité du circuit de la figure 1 aux variations de procédé de fabrication ; et

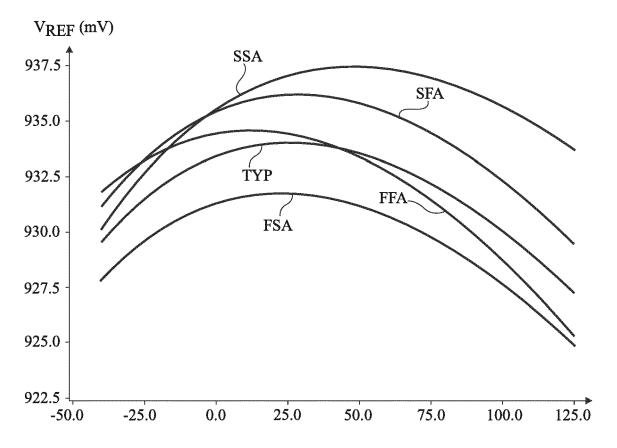

la figure 4 est un schéma électrique d'une variante de réalisation du circuit de la figure 1.

# Description détaillée

[0022] De mêmes éléments ont été désignés par de mêmes références aux différentes figures. Par souci de clarté, seuls les éléments qui sont utiles à la compréhension des modes de réalisation décrits ont été représentés et sont détaillés. En particulier, les utilisations qui peuvent être faites des circuits de génération de tension de référence décrits ne sont pas détaillées, les modes de réalisation décrits étant compatibles avec les applications usuelles d'un circuit de génération d'une tension de référence. Sauf précision contraire, les expressions "approximativement", "environ", "sensiblement", et "de l'ordre de" signifient à 10 % près, de préférence à 5 % près. Dans la présente description, on utilise le terme "connecté" pour désigner une liaison électrique directe, sans composant électronique intermédiaire, par exemple au moyen d'une ou plusieurs pistes conductrices, et le terme "couplé" ou le terme "relié", pour désigner soit une liaison électrique directe (signifiant alors "connecté") soit une liaison via un ou plusieurs composants intermédiaires (résistance, diode, condensateur, etc.).

[0023] La figure 1 est un schéma électrique d'un exemple d'un mode de réalisation d'un circuit de génération d'une tension de référence.

[0024] Le circuit de la figure 1 est réalisé à base de transistors MOS en technologie FDSOI (de l'anglais "Fully Depleted

Semiconductor On Insulator" - semiconducteur entièrement déplétable sur isolant). Plus particulièrement, les transistors MOS du circuit de la figure 1 sont réalisés dans et sur une structure de type semiconducteur sur isolant comportant un empilement d'un substrat semiconducteur revêtu d'une couche d'un matériau diélectrique, cette couche étant elle-même revêtue d'une couche semiconductrice. Chaque transistor comprend une grille conductrice isolée, appelée grille de face avant, revêtant la face de la couche semiconductrice opposée à la couche diélectrique. La région de formation de canal du transistor est située sous la grille de face avant, dans la couche semiconductrice. Les régions de source et de drain du transistor sont par exemple des régions implantées formées dans la couche semiconductrice, de part et d'autre de la région de formation de canal. Les régions de source et de drain sont respectivement dopées de type P pour un transistor à canal P (PMOS) et dopées de type N pour un transistor à canal N (NMOS). La région de substrat située sous la couche diélectrique, en regard de la région de formation de canal du transistor, est appelée grille de face arrière, et peut être polarisée pour contrôler la tension de seuil du transistor.

10

30

35

50

[0025] On considère ici une filière de fabrication en technologie FDSOI dans laquelle on dispose, pour chaque type de conductivité (NMOS et PMOS), de deux types de transistors, appelés respectivement RVT (de l'anglais "Regular Voltage Threshold") et LVT (de l'anglais "Low Voltage Threshold"), présentant, pour des dimensions des grilles de face avant identiques et pour des tensions de polarisation des grilles de face arrière identiques, des tensions de seuil différentes. Plus particulièrement, à dimensions de grille de face avant identiques et à tensions de polarisation de grille de face arrière identiques, les transistors RVT ont une tension de seuil plus élevée que les transistors LVT. Dans cet exemple, pour obtenir des transistors présentant des tensions de seuils différentes, on joue sur le dopage de la région substrat située au contact de la couche diélectrique, en regard de la région de formation de canal du transistor (correspondant à la grille de face arrière du transistor). Plus particulièrement, les transistors LVT comprennent un caisson de même type de conductivité que les régions de source et de drain du transistor, s'étendant dans le substrat, sous la couche diélectrique, en regard de la région de formation de canal du transistor, et les transistors RVT comprennent un caisson de type de conductivité opposé à celui des régions de source et de drain, s'étendant dans le substrat, sous la couche diélectrique, en regard de la région de formation de canal du transistor. A titre de variante, le comportement LVT ou RVT des transistors peut être obtenu en jouant sur un paramètre autre que le dopage de la région de substrat située sous la région de formation de canal du transistor, par exemple en jouant sur le dopage de la grille de face avant du transistor.

[0026] Par ailleurs, dans cet exemple, on considère une filière de fabrication en technologie FDSOI dans laquelle chacun des quatre types de transistors susmentionnés, à savoir le type NMOS LVT, le type NMOS RVT, le type PMOS LVT et le type PMOS RVT, peut être décliné en deux sous-types, appelés respectivement SO et DO, correspondant à des épaisseurs d'oxyde ou d'isolant de grille de face avant différentes. Plus particulièrement, les transistors de type SO (pour simple oxyde) présentent une première épaisseur d'oxyde de grille de face avant, et les transistors de type DO (pour double oxyde) présentent une deuxième épaisseur d'oxyde de grille de face avant supérieure à la première épaisseur, par exemple deux fois supérieure à la première épaisseur.

[0027] Le circuit de la figure 1 comprend des bornes ou des noeuds VDD et VSS d'application d'une tension d'alimentation V<sub>SUPPLY</sub>, et une borne ou un noeud REF de fourniture d'une tension de référence V<sub>REF</sub>. Dans cet exemple, le noeud VDD est destiné à recevoir le potentiel haut de la tension d'alimentation V<sub>SUPPLY</sub>, et le noeud VSS est destiné à recevoir le potentiel bas de la tension d'alimentation V<sub>SUPPLY</sub>. La tension de référence V<sub>REF</sub> fournie sur le noeud REF est référencée par rapport au noeud VSS, qui correspond par exemple à la masse du circuit.

[0028] Le circuit de la figure 1 comprend un circuit 101 de génération d'un courant de polarisation I de type CTAT (de l'anglais "Complementary To Absolute Temperature"), c'est-à-dire dont l'intensité diminue lorsque la température augmente. Dans l'exemple représenté, le courant I est généré à partir d'une différence de tensions grille-source entre deux transistors N1 et N2 de même type mais présentant des dimensions différentes. Cette différence de tensions grillesource est appliquée aux bornes d'un transistor N3 fonctionnant en régime linéaire pour générer le courant I. Dans cet exemple, les transistors N1, N2 et N3 sont des transistors NMOS. Les transistors N1 et N2 sont par exemple tous deux des transistors LVT. A titre de variante, les transistors N1 et N2 sont tous deux des transistors RVT. Les transistors N1 et N2 sont par exemple tous deux à oxyde épais (DO). Le transistor N3 est par exemple un transistor NMOS LVT à oxyde épais (DO). Le rapport K<sub>N1</sub> entre la largeur de canal W<sub>N1</sub> et la longueur de canal L<sub>N1</sub> du transistor N1 est différent du rapport  $K_{N2}$  entre la largeur de canal  $W_{N2}$  et la longueur de canal  $L_{N2}$  du transistor N2. A titre d'exemple, le rapport  $K_{N1}$  est inférieur au rapport  $K_{N2}$  de façon que, en fonctionnement, la tension grille-source du transistor N1 soit supérieure à la tension grille-source du transistor N2. Les transistors N1 et N2 sont montés en miroir de courant. Plus particulièrement, le transistor N1 a sa grille de face avant connectée à son drain et a sa source reliée au noeud VSS. La grille de face avant du transistor N2 est connectée à la grille de face avant du transistor N1. La source du transistor N2 est reliée au noeud VSS par l'intermédiaire du transistor N3. Plus particulièrement, le drain du transistor N3 est connecté à la source du transistor N2, et la source du transistor N3 est reliée au noeud VSS. Dans cet exemple, la grille de face avant du transistor N3 est connectée au noeud REF de sortie du circuit.

[0029] Outre les transistors N1, N2 et N3, le circuit 101 de génération du courant de polarisation I comprend un transistor PMOS P1 reliant le drain du transistor N1 au noeud VDD, et un transistor PMOS P2 reliant le drain du transistor

N2 au noeud VDD. Le transistor P1 a son drain connecté au drain du transistor N1, et le transistor P2 a son drain connecté au drain du transistor N2. Le transistor P1 a sa source reliée au noeud VDD, et le transistor P2 a sa source reliée au noeud VDD. Les transistors P1 et P2 sont montés en miroir de courant. Plus particulièrement, le transistor P1 a sa grille de face avant connectée à la grille de face avant du transistor P2, et le transistor P2 a sa grille de face avant connectée à son drain. Les transistors P1 et P2 sont par exemple tous deux des transistors RVT. A titre de variante, les transistors P1 et P2 sont tous deux des transistors P1 et P2 sont par exemple tous deux à oxyde épais (DO).

[0030] Le circuit de la figure 1 comprend en outre un circuit 103 de génération d'une tension V de type PTAT (de l'anglais "Proportional To Absolute Temperature"), c'est-à-dire dont la valeur augmente lorsque la température augmente.

[0031] Dans cet exemple, le circuit 103 comprend une première branche comportant un transistor N4 en série avec un transistor N5, et une deuxième branche comportant un transistor N6 en série avec un transistor N7. Dans cet exemple, les transistors N4, N5, N6 et N7 sont de type NMOS.

[0032] Les transistors N4 et N5 sont par exemple respectivement de type LVT à oxyde mince (SO) et de type LVT à oxyde épais (DO). A titre de variante, les transistors N4 et N5 de la première branche sont respectivement de type LVT à oxyde mince (SO) et de type RVT à oxyde épais (DO). A titre de variante, les transistors N4 et N5 de la première branche sont respectivement de type RVT à oxyde mince (SO) et de type LVT à oxyde épais (DO). Plus généralement, la première branche est une branche dite à épaisseur d'oxyde mixte (c'est-à-dire que son transistor situé côté noeud VSS, à savoir son transistor N4, est un transistor à oxyde mince, et que son transistor opposé au noeud VSS, à savoir son transistor N5, est un transistor à oxyde épais), dont au moins un des deux transistors N4 et N5 est de type LVT.

[0033] Les transistors N6 et N7 sont par exemple tous deux des transistors RVT. A titre de variante, les transistors N6 et N7 sont tous deux des transistors LVT. Les transistors N5 et N6 sont des transistors à oxyde épais (DO). Ainsi, dans cet exemple, la deuxième branche est une branche dite à oxyde épais (c'est-à-dire que ses deux transistors N6 et N7 sont des transistors à oxyde épais), dont les deux transistors N6 et N7 sont de même type, soit LVT, soit RVT.

20

30

35

45

50

[0034] Le transistor N4 a sa source reliée au noeud VSS et son drain connecté à la source du transistor N5. Le transistor N5 a son drain connecté à sa grille de face avant. La grille de face avant du transistor N5 est en outre connectée à la grille de face avant du transistor N4. Le transistor N6 a sa source connectée au point milieu de l'association en série des transistors N4 et N5, c'est-à-dire à la source du transistor N5 et au drain du transistor N4. Le transistor N6 a son drain connecté à la source du transistor N7. Le transistor N7 a son drain connecté à sa grille de face avant. La grille de face avant du transistor N7 est en outre connectée à la grille de face avant du transistor N6. Le point milieu de l'association en série des transistors N6 et N7, c'est-à-dire le noeud de source du transistor N7 ou noeud de drain du transistor N6, constitue le noeud de fourniture de la tension V de sortie du circuit 103 (référencée par rapport au noeud VSS).

[0035] Dans cet exemple, le circuit 103 comprend en outre un transistor PMOS P3 reliant le drain du transistor N5 au noeud VDD, et un transistor PMOS P4 reliant le drain du transistor N7 au noeud VDD. Le transistor P3 a son drain connecté au drain du transistor N5, et le transistor P4 a son drain connecté au drain du transistor N7. Les transistors P3 et P4 ont chacun leur source reliée au noeud VDD. Chacun des transistors P3 et P4 est monté de façon à former un miroir de courant avec le transistor P2. Plus particulièrement, le transistor P3 a sa grille de face avant connectée à la grille de face avant du transistor P2, et le transistor P4 a sa grille de face avant connectée à la grille de face avant du transistors P3 et P4 sont par exemple tous deux des transistors RVT. A titre de variante, les transistors P3 et P4 sont tous deux des transistors P3 et P4 sont par exemple tous deux à oxyde épais (DO).

[0036] Le circuit de la figure 1 comprend en outre un transistor N8 monté en diode, dans lequel est appliqué le courant de polarisation I de type CTAT, et dont un noeud de conduction reçoit la tension de sortie V de type PTAT du circuit 103. Dans cet exemple, le transistor N8 est un transistor NMOS. Le transistor N8 est par exemple un transistor RVT, par exemple à oxyde épais (DO). La source du transistor N8 est connectée au noeud de fourniture de la tension de sortie V du circuit 103, c'est-à-dire au noeud de source du transistor N7 et au noeud de drain du transistor N6 dans cet exemple. Le drain du transistor N8 est connecté à sa grille de face avant, et au noeud de sortie REF du circuit de la figure 1. Dans cet exemple, le circuit de la figure 1 comprend en outre un transistor PMOS P5 reliant le drain du transistor N8 au noeud VDD. Le transistor P5 a son drain connecté au drain du transistor N8, et sa source reliée au noeud VDD. Le transistor P5 est monté de façon à former un miroir de courant avec le transistor P2. Plus particulièrement, le transistor P5 a sa grille de face avant du transistor P2. Le transistor P5 peut être de type RVT ou de type LVT. A titre d'exemple, le transistor P5 est à oxyde épais (DO). Les transistors P1, P2, P3, P4 et P5 sont par exemple identiques, c'est-à-dire de même type (RVT ou LVT, de même épaisseur d'oxyde DO ou SO) et sensiblement de mêmes dimensions.

[0037] En fonctionnement, un même courant de polarisation I circule dans la branche comportant les transistors P1 et N1, et dans la branche comportant les transistors P2, N2 et N3. Le transistor N3, fonctionnant en régime linéaire, voit à ses bornes une tension de type PTAT égale à la différence entre la tension grille-source du transistor N1 et la tension grille-source du transistor N2, ce qui fixe la valeur du courant I. La résistance interne du transistor N3 augmente avec la température plus rapidement que la tension PTAT vue par le transistor N3, de sorte que le courant I (qui est le ratio

de la tension aux bornes du transistor N3 par la résistance interne du transistor N3) diminue avec la température.

[0038] Le courant de polarisation I généré par le circuit 101 est recopié dans la branche comportant les transistors P3, N5 et N4, et dans la branche comportant les transistors P4, N7 et N6. Sous l'effet de ce courant, une tension v1 de type PTAT est fournie sur le point milieu de l'association en série des transistors N4 et N5, et une tension v2, également de type PTAT mais de niveau supérieur à v1, est fournie sur le point milieu de l'association en série des transistors N6 et N7. Les tensions v1 et v2 sont référencées par rapport au noeud VSS. Dans cet exemple, la tension V de sortie du circuit 103 est la tension v2.

[0039] Le courant de polarisation I généré par le circuit 101 est en outre recopié dans la branche comportant les transistors P5 et N8. La tension de sortie V<sub>REF</sub> du circuit de la figure 1 est égale à la somme de la tension grille-source du transistor N8 et de la tension V de sortie du circuit 103. Lorsque la température augmente, le courant I tend à diminuer, et la tension de seuil du transistor N8 tend à diminuer, ce qui tendrait à faire baisser la tension V<sub>REF</sub>. Toutefois, la tension V de sortie du circuit 103 augmente avec la température, ce qui permet de maintenir la tension V<sub>REF</sub> relativement stable en température.

[0040] La tension d'alimentation V<sub>SUPPLY</sub> et les dimensions des transistors du circuit de la figure 1 sont de préférence choisis de façon que, en fonctionnement, les transistors P1, P2, P3, P4, P5, N4, N5 et N8 soient en régime de saturation, les transistors N1, N2, N6 et N7 soient en régime de conduction sous le seuil, et le transistor N3 soit en régime linéaire. [0041] A titre d'exemple, la tension d'alimentation V<sub>SUPPLY</sub> est de l'ordre de 1,2 V, et les dimensions des transistors N1, N2, N3, N4, N5, N6, N7 et N8 sont sensiblement comme suit :

$$K_{N1} = W_{N1}/L_{N1} = 2 \ \mu \text{m} \ / \ 15 \ \mu \text{m} \ ;$$

$$K_{N2} = W_{N2}/L_{N2} = 6 \ \mu \text{m} \ / \ 15 \ \mu \text{m} \ ;$$

$$K_{N3} = W_{N3}/L_{N3} = 0,17 \ \mu \text{m} \ / \ (2*30 \ \mu \text{m}) \ ;$$

$$K_{N4} = W_{N4}/L_{N4} = 0,34 \ \mu \text{m} \ / \ 30 \ \mu \text{m} \ ;$$

$$K_{N5} = W_{N5}/L_{N5} = 0,68 \ \mu \text{m} \ / \ 30 \ \mu \text{m} \ ;$$

$$K_{N6} = W_{N6}/L_{N6} = 0,34 \ \mu \text{m} \ / \ 4 \ \mu \text{m} \ ;$$

$$K_{N7} = W_{N7}/L_{N7} = 12,24 \ \mu \text{m} \ / \ 4 \ \mu \text{m} \ ;$$

et

10

50

55

où W<sub>Ni</sub>, L<sub>Ni</sub> et K<sub>Ni</sub> désignent respectivement la largeur de canal du transistor Ni, la longueur de canal du transistor Ni, et le rapport largeur de canal sur longueur de canal du transistor Ni, avec i entier allant de 1 à 8. A titre d'exemple, les transistors de type SO (à oxyde mince) sont adaptés à supporter sans dégradation une tension maximale de l'ordre de 1V, et les transistors de type DO sont adaptés à supporter sans dégradation une tension maximale de l'ordre de 1,8 V. [0042] A titre d'exemple, tous les transistors NMOS du circuit de la figure 1 ont leurs grilles de face arrière reliées à la masse, c'est-à-dire au noeud VSS, et tous les transistors PMOS du circuit ont leurs grilles de face arrière reliées au noeud VDD d'application du potentiel d'alimentation haut du circuit. Les modes de réalisation décrits ne se limitent toutefois pas à ce cas particulier. A titre de variante, tous les transistors du circuit de la figure 1 peuvent avoir, en fonctionnement, leurs grilles de face arrière polarisées à un même potentiel de référence distinct du potentiel du noeud VSS ou VDD. A titre de variante des transistors distincts du circuit de la figure 1 peuvent avoir, en fonctionnement, leurs grilles de face arrière polarisées à des potentiels distincts.

[0043] La figure 2 est un diagramme illustrant le comportement du circuit de la figure 1. Plus particulièrement, la figure

2 représente l'évolution en fonction de la température, dans une plage de température allant de -40°C à +125°C, du courant de polarisation I, en nanoampères, des tensions v1 et v2, en mV, et de la tension de sortie  $V_{REF}$ , en mV du circuit de la figure 1. Comme cela apparaît sur la figure 2, le courant I décroit de façon sensiblement linéaire en fonction de la température depuis une valeur haute de l'ordre de 20,2 nA pour une température de -40°C jusqu'à une valeur basse de l'ordre de 16,5 nA pour une température de 125°C, la tension v1 augmente de façon sensiblement linéaire en fonction de la température depuis une valeur basse de l'ordre de 172 mV pour une température de -40°C jusqu'à une valeur haute de l'ordre 215 mV pour une température de 125°C, et la tension v2 augmente de façon sensiblement linéaire en fonction de la température depuis une valeur basse de l'ordre de 280 mV pour une température de -40°C jusqu'à une valeur haute de l'ordre de 385 mV pour une température de 125°C. La tension de référence  $V_{REF}$  évolue selon une forme en cloche entre environ 928 mV et 934 mV dans la plage de température de -40°C à +125°C.

[0044] Les essais réalisés ont montré que le circuit de la figure 1 présente une très bonne précision intrinsèque par rapport aux circuits existants (c'est-à-dire une quasi-indépendance de la tension de sortie aux variations de procédé), comme cela est illustré notamment par la figure 3.

[0045] La figure 3 représente l'évolution de la tension de sortie V<sub>REF</sub> du circuit de la figure 1 en fonction de la température, dans la plage de température allant de -40°C à +125°C, aux différentes limites des variations de paramètres du procédé de fabrication, dans la technologie de fabrication FDSOI considérée (ici la technologie FDSOI 28 nm). Plus particulièrement, la figure 3 comprend une courbe FSA correspondant au cas où les transistors NMOS sont plus rapides que la normale et les transistors PMOS sont plus lents que la normale, une courbe FFA correspondant au cas où les transistors NMOS et PMOS sont plus rapides que la normale, une courbe SFA correspondant au cas où les transistors NMOS sont plus lents que la normale et les transistors PMOS sont plus rapides que la normale, une courbe SSA correspondant au cas où les transistors NMOS et PMOS sont plus lents que la normale, et une courbe TYP correspondant au cas où les transistors NMOS et PMOS ont une vitesse moyenne.

**[0046]** Comme cela apparaît sur la figure 3, l'imprécision du circuit de la figure 1 liée aux dispersions de fabrication est de l'ordre de 5,5 mV à 25°C pour une tension de référence typique de l'ordre de 934 mV, ce qui correspond à une imprécision de 0,5 % crête à crête. Les mesures effectuées montrent qu'à une température donnée, le rapport de l'écart type de la distribution des tensions de référence fournies par les circuits d'un lot représentatif des variations de procédé de fabrication, sur la tension de référence moyenne de la distribution, est de l'ordre de +/- 0,1%.

[0047] Les inventeurs ont déterminé que la bonne précision intrinsèque du circuit de la figure 1, c'est-à-dire le fait que la tension de référence délivrée par le circuit soit relativement peu dépendante des variations de procédé, résulte principalement de la combinaison d'un circuit 103 de génération d'une tension V de type PTAT dont une première branche (transistors N4 et N5) est à épaisseur d'oxyde mixte et comprend au moins un transistor (N4 ou N5) de type LVT, et d'un transistor N8 de type RVT à oxyde épais pour réaliser l'étage de sortie du circuit de génération de la tension de référence V<sub>REF</sub>. Le choix d'un transistor N3 de type LVT dans la deuxième branche du circuit 101 de génération du courant de polarisation I contribue aussi à augmenter la précision intrinsèque du circuit.

30

35

40

50

[0048] Outre sa bonne précision intrinsèque, un avantage du circuit de la figure 1 est que le niveau de la tension de référence fournie peut aisément être ajusté à la conception en jouant sur le courant de polarisation I et sur le rapport largeur de canal sur longueur de canal des différents transistors. En particulier, la tension de référence fournie par le circuit de la figure 1 peut, si besoin, être fixée à un niveau proche de la tension d'alimentation V<sub>SUPPLY</sub>. En effet, l'écart minimal entre la tension d'alimentation V<sub>SUPPLY</sub> et la tension de sortie V<sub>REF</sub> correspond à la tension drain-source minimale nécessaire pour obtenir une bonne recopie du courant de polarisation I par le transistor P5, qui peut être de l'ordre de 200 mV.

[0049] De plus, le circuit de la figure 1 comportant uniquement des transistors MOS, il ne nécessite qu'une faible surface de silicium pour sa réalisation, et présente une consommation électrique relativement faible. En ce qui concerne la surface occupée, un compromis pourra être choisi entre la précision intrinsèque et la surface de silicium en fonction des besoins de l'application. En effet, plus les surfaces W\*L des transistors MOS du circuit seront élevées, meilleure sera la précision intrinsèque du circuit. En ce qui concerne la consommation, un avantage du circuit de la figure 1 est que, du fait que le courant de polarisation I est de type CTAT, la consommation du circuit n'augmente pas lorsque la température augmente.

[0050] Des modes de réalisation particuliers ont été décrits. Diverses variantes et modifications apparaîtront à l'homme de l'art. En particulier, les modes de réalisation décrits ne se limitent pas à l'exemple de circuit 101 de génération d'un courant de polarisation I décrit en relation avec la figure 1. Plus généralement, le circuit 101 peut être remplacé par tout autre circuit adapté à générer un courant de polarisation I de type CTAT.

**[0051]** A titre de variante, le circuit 101 peut être remplacé par un circuit adapté à générer un courant de polarisation I de type PTAT. Dans ce cas, le dimensionnement des transistors, et en particulier le dimensionnement du transistor N8, pourra être ajusté pour préserver une bonne stabilité en température de la tension de sortie. On notera toutefois que l'utilisation d'un circuit 101 adapté à générer un courant de polarisation I de type CTAT est préférable dans la mesure où elle permet de limiter la consommation électrique globale du circuit.

[0052] De plus, les modes de réalisation décrits ne se limitent pas à l'exemple de circuit 103 de génération d'une

tension V de type PTAT décrit en relation avec la figure 1.

[0053] A titre de variante, on peut notamment prévoir de supprimer la branche comportant les transistors P4, N7 et N6, et de relier la source du transistor N8 directement au point milieu de l'association en série des transistors N4 et N5. Dans ce cas, la tension V appliquée sur la source du transistor N8 est la tension v1.

[0054] Dans une autre variante, on peut prévoir de remplacer la deuxième branche (transistors N6 et N7) par une branche à épaisseur d'oxyde mixte comportant au moins un transistor LVT. Autrement dit, le transistor N6 situé côté noeud VSS peut être remplacé par un transistor à oxyde mince, le transistor N7 restant un transistor à oxyde épais, et au moins un des deux transistors N6 et N7 étant un transistor de type LVT, l'autre transistor pouvant être de type LVT ou RVT.

[0055] Dans une autre variante illustrée par la figure 4, chacune des première (transistors N4 et N5) et deuxième (transistors N6 et N7) branches du circuit 103 est une branche à épaisseur d'oxyde mixte comportant au moins un transistor de type LVT (tel que décrit dans le paragraphe précédent), et le circuit 103 comporte en outre une troisième branche comportant un transistor N9 en série avec un transistor N10. Dans cet exemple, les transistors N9 et N10 sont de type NMOS. La troisième branche est une branche à oxyde épais, c'est-à-dire que ses deux transistors N9 et N10 sont des transistors à oxyde épais (DO). Les transistors N9 et N10 sont par exemple tous deux des transistors RVT ou tous deux des transistors LVT.

[0056] Le transistor N9 a sa source connectée au point milieu de l'association en série des transistors N6 et N7, c'est-à-dire à la source du transistor N7 et au drain du transistor N6. Le transistor N9 a son drain connecté à la source du transistor N10. Le transistor N10 a son drain connecté à sa grille de face avant. La grille de face avant du transistor N10 est en outre connectée à la grille de face avant du transistor N9. Le point milieu de l'association en série des transistors N9 et N10, c'est-à-dire le noeud de source du transistor N10 et de drain du transistor N9, constitue le noeud de fourniture de la tension V de sortie du circuit 103 (référencée par rapport au noeud VSS).

[0057] Dans cet exemple, le circuit 103 comprend en outre un transistor PMOS P6 reliant le drain du transistor N10 au noeud VDD. Le transistor P6 a son drain connecté au drain du transistor N10 et sa source reliée au noeud VDD. Le transistor P6 est monté de façon à former un miroir de courant avec le transistor P2. Plus particulièrement, le transistor P6 a sa grille de face avant connectée à la grille de face avant du transistor P2. Le transistor P6 est par exemple de type RVT. A titre de variante, le transistor P6 est de type LVT. Le transistor P6 est par exemple à oxyde épais (DO). Le transistor P6 est par exemple identique aux transistors P1, P2, P3, P4 et P5.

[0058] Dans la variante de la figure 4, le transistor N8 monté en diode a sa source connectée non plus au point milieu de la deuxième branche, c'est-à-dire au noeud de source du transistor N7 et de drain du transistor N6, mais au point milieu de la troisième branche, c'est-à-dire au noeud de source du transistor N10 et de drain du transistor N9.

[0059] En fonctionnement, le courant de polarisation I généré par le circuit 101 est recopié dans la branche comportant les transistors P3, N5 et N4, dans la branche comportant les transistors P4, N7 et N6, et dans la branche comportant les transistors P6, N10 et N9. Sous l'effet de ce courant, une tension v1 de type PTAT est fournie sur le point milieu de l'association en série des transistors N4 et N5, une tension v2, également de type PTAT mais de niveau supérieur à v1, est fournie sur le point milieu de l'association en série des transistors N6 et N7, et une tension v3 également de type PTAT mais de niveau supérieur à v2 est fournie sur le point milieu de l'association en série des transistors N9 et N10. Dans cet exemple, la tension V de sortie du circuit 103 est la tension v3.

**[0060]** Ainsi, le fonctionnement du circuit de la figure 4 est similaire à celui du circuit de la figure 1 à ceci près que la tension de sortie V du circuit 103 est plus élevée que dans l'exemple de la figure 1.

[0061] Un avantage du circuit de la figure 4 est qu'il présente une précision intrinsèque encore meilleure que celle du circuit de la figure 1, c'est-à-dire une dépendance de sa tension de sortie V<sub>REF</sub> aux variations de procédé plus faible que dans l'exemple de la figure 1, du fait notamment de l'augmentation de la valeur de la tension de sortie V du circuit 103. [0062] Les modes de réalisation décrits ne se limitent pas aux exemples susmentionnés dans lesquels les transistors N1, N2, N3, N4, N5, N6, N7, N8, et, le cas échéant (figure 4), N9 et N10 sont des transistors MOS à canal N. A titre de variante, un circuit similaire (complémentaire) peut être obtenu en inversant les types de conductivité de tous les transistors.

# Revendications

10

25

30

35

40

45

50

55

1. Circuit de génération d'une tension de référence (V<sub>REF</sub>) réalisé en technologie FDSOI, comportant :

un premier circuit (101) de génération d'un courant de polarisation (I); un deuxième circuit (103) de génération d'une tension (V) de type PTAT comportant une première branche comportant des premier (N4) et deuxième (N5) transistors en série, les grilles de face avant des premier (N4) et deuxième (N5) transistors étant connectées au noeud de conduction du deuxième (N5) transistor opposé au premier transistor (N4);

un troisième transistor (N8) monté en diode dont un noeud de conduction est connecté à un noeud de fourniture de la tension de sortie (V) du deuxième circuit et dont l'autre noeud de conduction constitue un noeud de fourniture de la tension de référence (V<sub>REF</sub>) ; et

un miroir de courant (P2, P3, P5) imposant, dans le troisième transistor (N8) d'une part et dans la première branche (N4, N5) d'autre part, des courants proportionnels au courant de polarisation (I),

dans lequel au moins l'un des premier (N4) et deuxième (N5) transistors est de type LVT, et le troisième transistor (N8) est de type RVT,

et dans lequel le premier transistor (N4) présente une première épaisseur d'isolant de grille de face avant (SO), le deuxième transistor (N5) et le troisième transistor (N8) présentant une deuxième épaisseur d'isolant de grille de face avant (DO) supérieure à la première épaisseur.

- 2. Circuit selon la revendication 1, dans lequel le drain du premier transistor (N4) est connecté à la source du deuxième transistor (N5), le drain du deuxième transistor (N5) étant connecté aux grilles des premier (N4) et deuxième (N5) transistors.

- 3. Circuit selon la revendication 1 ou 2, dans lequel la source du troisième transistor (N8) est connectée à un noeud de fourniture de la tension de sortie (V) du deuxième circuit (103).

- 4. Circuit selon l'une quelconque des revendications 1 à 3, dans lequel :

5

10

15

20

25

35

40

55

le deuxième circuit (103) comprend en outre une deuxième branche comportant des quatrième (N6) et cinquième (N7) transistors en série, les grilles de face avant des quatrième (N6) et cinquième transistors (N7) étant connectées au noeud de conduction du cinquième transistor (N7) opposé au quatrième transistor (N6), et le noeud de conduction du quatrième transistor (N6) opposé au cinquième transistor (N7) étant connecté au point milieu de l'association en série des premier (N4) et deuxième (N5) transistors ; et le miroir de courant (P2, P3, P4, P5) impose dans la deuxième branche (N6, N7) un courant proportionnel au courant de polarisation (I).

- 5. Circuit selon la revendication 4, dans lequel le drain du quatrième transistor (N6) est connecté à la source du cinquième transistor (N7), et le drain du cinquième transistor (N7) est connecté aux grilles des quatrième (N6) et cinquième (N7) transistors.

- 6. Circuit selon la revendication 4 ou 5, dans lequel les quatrième (N6) et cinquième (N7) transistors ont tous deux une épaisseur d'isolant de grille égale à la deuxième épaisseur, et sont tous deux de type RVT ou tous deux de type LVT.

- 7. Circuit selon la revendication 4 ou 5, dans lequel le quatrième transistor (N6) présente une épaisseur d'isolant de grille égale à la première épaisseur, le cinquième transistor (N7) présentant une épaisseur d'isolant de grille égale à la deuxième épaisseur, et dans lequel au moins l'un des quatrième (N6) et cinquième (N7) transistors est de type LVT.

- **8.** Circuit selon la revendication 7, dans lequel :

- le deuxième circuit (103) comprend en outre une troisième branche comportant des sixième (N9) et septième (N10) transistors en série, les grilles de face avant des sixième (N9) et septième transistors (N10) étant connectées au noeud de conduction du septième transistor (N10) opposé au sixième transistor (N9), et le noeud de conduction du sixième transistor (N9) opposé au septième transistor (N10) étant connecté au point milieu de l'association en série des quatrième (N6) et cinquième (N7) transistors ; et le miroir de courant (P2, P3, P4, P5, P6) impose dans la troisième branche (N9, N10) un courant proportionnel au courant de polarisation (I).

- 9. Circuit selon la revendication 8, dans lequel le drain du sixième transistor (N9) est connecté à la source du septième transistor (N10), et le drain du septième transistor (N10) est connecté aux grilles des sixième (N9) et septième (N10) transistors.

- **10.** Circuit selon la revendication 8 ou 9, dans lequel les sixième (N9) et septième (N10) transistors ont tous deux une épaisseur d'isolant de grille égale à la deuxième épaisseur, et sont tous deux de type RVT ou tous deux de type LVT.

- 11. Circuit selon l'une quelconque des revendications 1 à 10, dans lequel le premier circuit (101) comprend des huitième (N1) et neuvième (N2) transistors montés en miroir de courant, et un dixième transistor (N3) connecté en série avec le neuvième transistor (N2), les huitième (N1) et neuvième (N2) transistors étant de même type LVT ou RVT et présentant la même épaisseur d'oxyde de grille de face avant, et le huitième transistor (N1) ayant un rapport largeur de canal sur longueur de canal supérieur à celui du neuvième transistor (N2).

- 12. Circuit selon la revendication 11, dans lequel le dixième transistor (N3) est de type LVT.

- **13.** Circuit selon la revendication 11 ou 12, dans lequel les huitième (N1), neuvième (N2) et dixième (N3) transistors sont de type NMOS.

- **14.** Circuit selon l'une quelconque des revendications 11 à 13, dans lequel le dixième transistor (N3) a sa grille de face avant reliée au noeud de fourniture de la tension de référence (V<sub>RFF</sub>).

- 15. Circuit selon l'une quelconque des revendications 1 à 14, dans lequel le premier circuit (101) est adapté à générer un courant de polarisation (I) de type CTAT.

Fig 2

Fig 3

Fig 4

# RAPPORT DE RECHERCHE EUROPEENNE

Numéro de la demande EP 16 20 0987

| 0 |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

| DOCUMENTS CONSIDERES COMME PERTINENTS                    |                                                                                                                                                                                                 |                                                                                                                     |                                                             |                                         |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------|

| Catégorie                                                | Citation du document avec<br>des parties pertin                                                                                                                                                 | indication, en cas de besoin,<br>entes                                                                              | Revendication concernée                                     | CLASSEMENT DE LA<br>DEMANDE (IPC)       |

| A,D                                                      | ppm/V CMOS Voltage<br>Consisting of Subth                                                                                                                                                       | reshold MOSFETs",<br>ID-STATE CIRCUITS, IEEE<br>CATAWAY, NJ, USA,<br>19-07-01), pages<br>260,<br>II:<br>021922      | 1-15                                                        | INV.<br>G05F3/24                        |

| A                                                        | US 2012/323508 A1 (<br>[BR] ET AL) 20 déce<br>* alinéa [0028]; fi                                                                                                                               | VILAS BOAS ANDRE LUIS mbre 2012 (2012-12-20) gure 1 *                                                               | 1-15                                                        |                                         |

| A                                                        | US 2012/242398 A1 (<br>AL) 27 septembre 20<br>* abrégé; figure 1                                                                                                                                |                                                                                                                     | 1-15                                                        |                                         |

| <b>A</b>                                                 | US 2011/121809 A1 (<br>MAURICIO [BR] ET AL<br>26 mai 2011 (2011-0<br>* abrégé; figure 2                                                                                                         | 5-26)                                                                                                               | 1-15                                                        | DOMAINES TECHNIQUES<br>RECHERCHES (IPC) |

| A                                                        | From MOSFETs to SRA<br>IEEE TRANSACTIONS O<br>IEEE SERVICE CENTER                                                                                                                               | ar FDSOI Technology: M Cells", N ELECTRON DEVICES, PISACATAWAY, NJ, US, oût 2011 (2011-08-01), 011336343, II: 57162 | 1-15                                                        |                                         |

| Le pre                                                   | ésent rapport a été établi pour tοι                                                                                                                                                             | ıtes les revendications                                                                                             |                                                             |                                         |

| Lieu de la recherche Date d'achèvement de la recherche   |                                                                                                                                                                                                 | 1                                                                                                                   | Examinateur                                                 |                                         |

|                                                          | La Haye                                                                                                                                                                                         | 25 avril 2017                                                                                                       | Ari                                                         | as Pérez, Jagoba                        |

| X : parti<br>Y : parti<br>autre<br>A : arriè<br>O : divu | ATEGORIE DES DOCUMENTS CITE: culièrement pertinent à lui seul culièrement pertinent en combinaison c document de la même catégorie re-plan technologique ligation non-écrite ument intercalaire | E : document de bre<br>date de dépôt ou<br>avec un D : cité dans la dem<br>L : cité pour d'autres                   | evet antérieur, ma<br>après cette date<br>ande<br>s raisons |                                         |

page 1 de 2

# RAPPORT DE RECHERCHE EUROPEENNE

Numéro de la demande EP 16 20 0987

5

| -                                  |                                                       |                                                                                                                                                                                                                      |                                                                                               |                                                           | •                                       |

|------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------|

|                                    | DOCUMENTS CONSIDERES COMME PERTINENTS                 |                                                                                                                                                                                                                      |                                                                                               |                                                           |                                         |

|                                    | Catégorie                                             | Citation du document avec<br>des parties pertir                                                                                                                                                                      | indication, en cas de besoin,<br>nentes                                                       | Revendication concernée                                   | CLASSEMENT DE LA<br>DEMANDE (IPC)       |

| 10                                 | А                                                     | CMOS at 28 nm node<br>ultra-low power des<br>CIRCUITS AND SYSTEM<br>INTERNATIONAL SYMPO                                                                                                                              | MS (ISCAS), 2013 IEEE<br>DSIUM ON, IEEE,<br>DS-19), pages 554-557,<br>2013.6571903<br>760-9   | 1-15                                                      |                                         |

| 20                                 | А                                                     | analog mixed-signal<br>technology",<br>2015 IEEE SOI-3D-SU<br>MICROELECTRONICS TE<br>CONFERENCE (S3S), I                                                                                                             | UBTHRESHOLD<br>ECHNOLOGY UNIFIED<br>EEE,                                                      | 1-15                                                      |                                         |

| 25                                 |                                                       | 5 octobre 2015 (201<br>XP032815123,<br>DOI: 10.1109/S3S.20<br>* page 1 - page 2 *                                                                                                                                    |                                                                                               |                                                           | DOMAINES TECHNIQUES<br>RECHERCHES (IPC) |

| 30                                 |                                                       |                                                                                                                                                                                                                      |                                                                                               |                                                           |                                         |

| 35                                 |                                                       |                                                                                                                                                                                                                      |                                                                                               |                                                           |                                         |

| 40                                 |                                                       |                                                                                                                                                                                                                      |                                                                                               |                                                           |                                         |

| 45                                 |                                                       |                                                                                                                                                                                                                      |                                                                                               |                                                           |                                         |

| 1                                  | ·                                                     | ésent rapport a été établi pour to                                                                                                                                                                                   |                                                                                               |                                                           |                                         |

| 02)                                |                                                       | Lieu de la recherche                                                                                                                                                                                                 | Date d'achèvement de la recherche                                                             | A 10.2                                                    | Examinateur                             |

| P04C(                              |                                                       | La Haye                                                                                                                                                                                                              | 25 avril 2017                                                                                 |                                                           | as Pérez, Jagoba                        |

| 05<br>PPO FORM 1503 03.82 (P04C02) | X : parl<br>Y : parl<br>autr<br>A : arrid<br>O : divi | ATEGORIE DES DOCUMENTS CITE<br>iculièrement pertinent à lui seul<br>iculièrement pertinent en combinaisor<br>e decoument de la même catégorie<br>ère-plan technologique<br>algation non-écrite<br>ument intercalaire | E : document de brev<br>date de dépôt ou à<br>D : cité dans la dema<br>L : cité pour d'autres | vet antérieur, mai<br>après cette date<br>unde<br>raisons | s publié à la                           |

55

page 2 de 2

# ANNEXE AU RAPPORT DE RECHERCHE EUROPEENNE RELATIF A LA DEMANDE DE BREVET EUROPEEN NO.

5

EP 16 20 0987

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités dans le rapport de recherche européenne visé ci-dessus. Lesdits members sont contenus au fichier informatique de l'Office européen des brevets à la date du Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets.

25-04-2017

| 10             | Document brevet cité<br>au rapport de recherche |    | Date de<br>publication | Membre(s) de la<br>famille de brevet(s) | Date de<br>publication |

|----------------|-------------------------------------------------|----|------------------------|-----------------------------------------|------------------------|

|                | US 2012323508                                   | A1 | 20-12-2012             | AUCUN                                   |                        |

| 15             | US 2012242398                                   | A1 | 27-09-2012             | AUCUN                                   |                        |

|                | US 2011121809                                   | A1 | 26-05-2011             | AUCUN                                   |                        |

|                |                                                 |    |                        |                                         |                        |

| 20             |                                                 |    |                        |                                         |                        |

|                |                                                 |    |                        |                                         |                        |

|                |                                                 |    |                        |                                         |                        |

| 25             |                                                 |    |                        |                                         |                        |

|                |                                                 |    |                        |                                         |                        |

| 30             |                                                 |    |                        |                                         |                        |

|                |                                                 |    |                        |                                         |                        |

|                |                                                 |    |                        |                                         |                        |

| 35             |                                                 |    |                        |                                         |                        |

|                |                                                 |    |                        |                                         |                        |

| 40             |                                                 |    |                        |                                         |                        |

|                |                                                 |    |                        |                                         |                        |

|                |                                                 |    |                        |                                         |                        |

| 45             |                                                 |    |                        |                                         |                        |

|                |                                                 |    |                        |                                         |                        |

| 50             |                                                 |    |                        |                                         |                        |

| P0460          |                                                 |    |                        |                                         |                        |

| EPO FORM P0460 |                                                 |    |                        |                                         |                        |

| <u>հ</u><br>55 |                                                 |    |                        |                                         |                        |

Pour tout renseignement concernant cette annexe : voir Journal Officiel de l'Office européen des brevets, No.12/82

#### RÉFÉRENCES CITÉES DANS LA DESCRIPTION

Cette liste de références citées par le demandeur vise uniquement à aider le lecteur et ne fait pas partie du document de brevet européen. Même si le plus grand soin a été accordé à sa conception, des erreurs ou des omissions ne peuvent être exclues et l'OEB décline toute responsabilité à cet égard.

# Littérature non-brevet citée dans la description

- KEN UENO. A 300 nW, 15 ppm/ C, 20 ppm/V CMOS Voltage Reference Circuit Consisting of Subthreshold MOSFETs. IEEE JOURNAL OF SOLID-STATE CIRCUITS, Juillet 2009, vol. 44 (7 [0004]

- A. SAMIR. 173nA-7.5ppm/C-771mV-0.03mm2 CMOS Resistorless Voltage Reference. Faible Tension Faible Consommation (FTFC), 2011 [0004]

- GIUSEPPE DE VITA. A Sub-1-V, 10 ppm/ C, Nanopower Voltage Reference generator. IEEE JOUR-NAL OF SOLID-STATE CIRCUITS, Juillet 2007, vol. 42 (7 [0004]

- ANVESHA A. A Sub-1V 32nA Process, Voltage and Temperature Invariant Voltage Reference Circuit. 26th International Conference on VLSI Design, 2013 [0004]

- YUJI OSAKI. 1.2-V Supply, 100-nW, 1.09-V Bandgap and 0.7-V Supply, 52.5-nW, 0.55-V Subbandgap Reference Circuits for Nanowatt CMOS LSIs. *IEEE JOURNAL OF SOLID-STATE CIRCUITS*, Juin 2013, vol. 48 (6 [0004]