# (11) EP 3 223 145 A1

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

27.09.2017 Bulletin 2017/39

(51) Int CI.:

G06F 5/06 (2006.01)

H04L 7/00 (2006.01)

(21) Application number: 17161840.8

(22) Date of filing: 20.03.2017

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

Designated Extension States:

**BA ME**

**Designated Validation States:**

MA MD

(30) Priority: 21.03.2016 CN 201610160841

- (71) Applicant: **HUAWEI TECHNOLOGIES CO., LTD. Shenzhen Guangdong 518129 (CN)**

- (72) Inventor: XIN, Hengchao Shenzhen, Guangdong 518129 (CN)

- (74) Representative: Pfenning, Meinig & Partner mbB

Patent- und Rechtsanwälte

Theresienhöhe 11a

80339 München (DE)

## (54) DATA READING CIRCUIT

(57) Embodiments of the present invention disclose a data reading circuit, where the circuit is applied to a second clock domain. A first clock domain simultaneously sends data and an echo clock signal to the second clock domain. The data reading circuit includes a phase difference determining module, a time delay detection module, and a reading control module, and the phase difference determining module is connected to the echo clock signal and a clock signal of the second clock domain. The phase difference determining module is configured to determine a phase difference between the

echo clock signal and the clock signal of the second clock domain; the time delay detection module is configured to detect a time delay value in transmission of data from a buffer to a flip-flop; and the reading control module is configured to determine, according to the phase difference and the time delay value, a triggering edge, at which the flip-flop can read data output by the buffer, of the clock signal of the second clock domain. By means of the present invention, a phase difference between an echo clock signal and a clock signal of a local domain can be determined, thereby implementing data reading.

#### First clock domain

#### Second clock domain

FIG. 1

EP 3 223 145 A1

20

25

35

40

45

#### Description

#### **TECHNICAL FIELD**

**[0001]** The present invention relates to the field of electronic technologies, and in particular, to a data reading circuit.

#### **BACKGROUND**

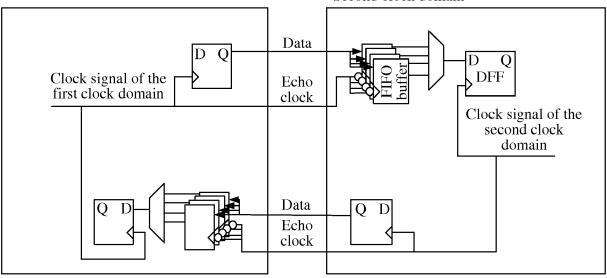

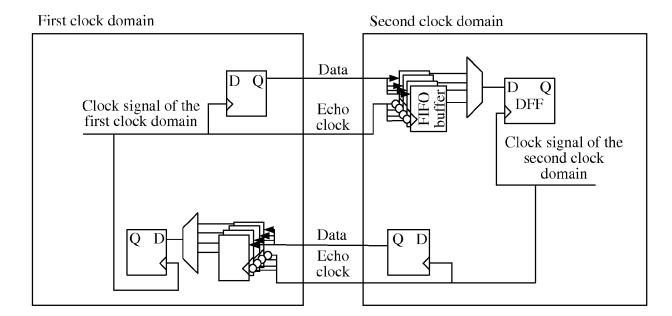

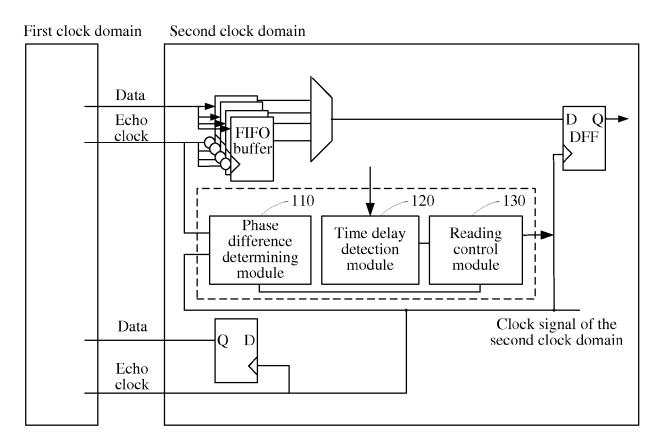

[0002] A source synchronization technology is a cross clock domain synchronization technology with a low delay, and is mainly applied to a process of data exchange between clock domains having a same source and a same frequency but different phases. A major technical principle of the technology is that: a first clock domain simultaneously sends data and an echo clock signal (that is, a clock signal of the first clock domain) to a second clock domain; and the second clock domain writes the data according to the echo clock signal, and reads the written data according to a clock signal of the local domain (that is, a clock signal of the second clock domain). A specific implementation process may be shown in FIG. 1. The first clock domain simultaneously sends data and an echo clock signal to the second clock domain; a FIFO (First In First Out) buffer in the second clock domain regularly writes data at each beat; and then a DFF (D-type flip-flop, D trigger) in the second clock domain regularly reads data at each beat according to a clock signal of the local domain. The echo clock signal has the same frequency as the clock signal of the second clock domain, and therefore the foregoing data reading method is feasible as long as a phase difference between the echo clock signal and the second clock domain is determined. [0003] Currently, the phase difference may be determined by using an associated data synchronization (Data Sync) signal. Referring to FIG. 2, the first clock domain generates a Data Sync signal for an echo clock signal, and the second clock domain may calculate, according to the Data Sync signal, a phase difference between a clock signal of the local clock domain and the echo clock signal. However, when a Data Sync signal is used, an I/O (Input/Output, input/output) interface that is used to transmit the Data Sync signal needs to be added, which increases hardware overheads. In addition, a phase relationship between a Data Sync signal and data needs to be strictly maintained during a signal transmission process, which increases difficulty of implementation.

# SUMMARY

[0004] Embodiments of the present invention provide a data reading circuit, so that a phase difference between an echo clock signal and a clock signal of a local domain can be determined, thereby implementing data reading. [0005] An embodiment of the present invention provides a data reading circuit. The circuit is applied to a second clock domain, the second clock domain includes

a buffer configured to write data sent by a first clock domain and a flip-flop configured to read data output by the buffer, the first clock domain simultaneously sends the data and an echo clock signal, and the echo clock signal is a clock signal of the first clock domain. The data reading circuit includes a phase difference determining module, a time delay detection module, and a reading control module, the phase difference determining module is connected to the echo clock signal and a clock signal of the second clock domain, the phase difference determining module is connected to the reading control module, and the time delay detection module is connected to the reading control module. The phase difference determining module is configured to determine a phase difference between the echo clock signal and the clock signal of the second clock domain, and send the phase difference to the reading control module. The time delay detection module is configured to detect a time delay value in transmission of the data from the buffer to the flip-flop, and send the time delay value to the reading control module. The reading control module is configured to determine, according to the phase difference and the time delay value, a triggering edge, at which the flip-flop can read the data output by the buffer, of the clock signal of the second clock domain.

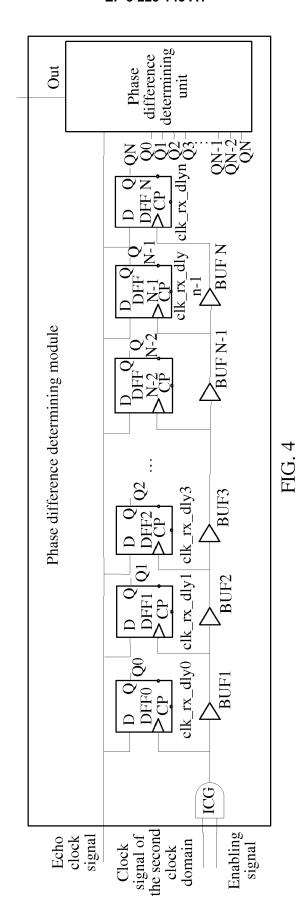

[0006] In a first possible implementation manner, the phase difference determining module includes N identical time delayers, N+1 identical D flip-flops, and a phase difference determining unit, where N is an integer greater than 1; the N time delayers are successively connected in series; an input port of the first time delayer is connected to the clock signal of the second clock domain; a time delay generated by the N time delayers is greater than a clock cycle of the clock signal of the second clock domain; input ports of the N+1 D flip-flops are connected to the echo clock signal; a clock port of the first D flip-flop is connected to the input port of the first time delayer; clock ports of the remaining N D flip-flops are successively connected to output ports of the N time delayers; output ports of the N+1 D flip-flops are connected to the phase difference determining unit; the phase difference determining unit is connected to the echo clock signal; and the phase difference determining unit is configured to determine, according to output results of the N+1 D flip-flops, the phase difference between the echo clock signal and the clock signal of the second clock domain, and send the phase difference to the reading control module.

**[0007]** With reference to the first possible implementation manner, in a second possible implementation manner, the phase difference determining unit is specifically configured to: first, at a time point corresponding to a level falling edge of the echo clock signal, obtain levels of output signals of the second flip-flop to the (N+1)<sup>th</sup> D flip-flop, where in the levels of the output signals, the first a levels are high levels, the middle b levels are low levels, the last clevels are high levels, and a, b, and c are positive

30

35

40

45

50

55

integers; then calculate, according to a formula

$\lambda = \frac{b-a}{2 \cdot b} \cdot 360^{\circ}$  , phase difference between the echo

clock signal and the clock signal of the second clock domain, where  $\lambda$  denotes the phase difference.

[0008] In a third possible implementation manner, the reading control module is specifically configured to: if the triggering edge at which the flip-flop reads the data output by the buffer is a rising edge, when the phase difference is greater than or equal to the time delay value, use a next rising edge, from a time point at which the buffer writes the data, of the clock signal of the second clock domain as a time point at which the flip-flop reads the data; or when the phase difference is less than the time delay value, according to a formula  $j = (\Delta t_{\text{max}} - \lambda)/T + 2$ , use the jth rising edge, from a time point at which the buffer writes the data, of the clock signal of the second clock domain as a time point at which the flip-flop reads the data, where  $\Delta \textit{t}_{\text{max}}$  denotes the time delay value,  $\lambda$ denotes the phase difference, / denotes an exact-division symbol, and T denotes a cycle of the clock signal of the second clock domain. If the triggering edge at which the flip-flop reads the data output by the buffer is a rising edge, when the phase difference is greater than or equal to the time delay value, use a next rising edge, from a time point at which the buffer writes the data, of the clock signal of the second clock domain as a time point at which the flip-flop reads the data; or when the phase difference is less than the time delay value, according to a formula  $j = (\Delta t_{\text{max}} - T / 2 - \lambda) / T + 2$ , use the  $j^{\text{th}}$  rising edge, from a time point at which the buffer writes the data, of the clock signal of the second clock domain as a time point at which the flip-flop reads the data, where  $\Delta t_{\rm max}$  denotes the time delay value,  $\lambda$  denotes the phase difference, / denotes an exact-division symbol, and T denotes a cycle of the clock signal of the second clock domain.

**[0009]** With reference to the first possible implementation manner, in a fourth possible implementation manner, the phase difference determining module further includes a switch component, where the input port of the first time delayer is connected to the clock signal of the second clock domain by using the switch component, and the switch component is configured to control connection and disconnection between the input port of the first time delayer and the clock signal of the second clock domain.

**[0010]** With reference to the fourth possible implementation manner, in a fifth possible implementation manner, the switch component is an inside clock generator ICG switch. The input port of the first time delayer is connected to an output port of the ICG switch, an input port of the ICG switch is connected to the clock signal of the second clock domain, and an enabling port of the ICG switch is connected to an enabling signal. The switch component is specifically configured to control connection and disconnection between the input port of the first time delayer and the clock signal of the second clock domain.

**[0011]** With reference to the first possible implementation manner, in a sixth possible implementation manner, the time delayer is a gate circuit or multiple gate circuits that are connected in series.

**[0012]** With reference to the second possible implementation manner, in a seventh possible implementation manner, the D flip-flop is a D flip-flop that resists a metastable state.

[0013] It can be seen from the foregoing that, the data reading circuit in this embodiment of the present invention includes a phase difference determining module, a time delay detection module, and a reading control module, where the phase difference determining module may determine a phase difference between an echo clock signal and a clock signal of a local clock domain, the time delay detection module may detect a time delay value in internal transmission of data, and the reading control module may determine a time point for data reading according to the phase difference and the time delay value, thereby implementing data reading. In addition, in the embodiments of the present invention, except for I/O interfaces used to transmit the data and echo clock signal, the phase difference between the echo clock signal and the clock signal of the local clock domain can be determined without the need to add an extra I/O interface between two clock domains, thereby reducing hardware overheads and difficulty in implementation.

#### **BRIEF DESCRIPTION OF DRAWINGS**

**[0014]** To describe the technical solutions in the embodiments of the present invention or in the prior art more clearly, the following briefly describes the accompanying drawings required for describing the embodiments or the prior art. Apparently, the accompanying drawings in the following description show merely some embodiments of the present invention, and a person of ordinary skill in the art may still derive other drawings from these accompanying drawings without creative efforts.

FIG. 1 is a schematic diagram of a cross clock domain synchronization technology in the prior art;

FIG. 2 is a schematic diagram of another cross clock domain synchronization technology in the prior art; FIG. 3 is a schematic structural diagram of a data reading circuit according to an embodiment of the present invention;

FIG. 4 is a schematic structural diagram of a time delay detection module according to an embodiment of the present invention;

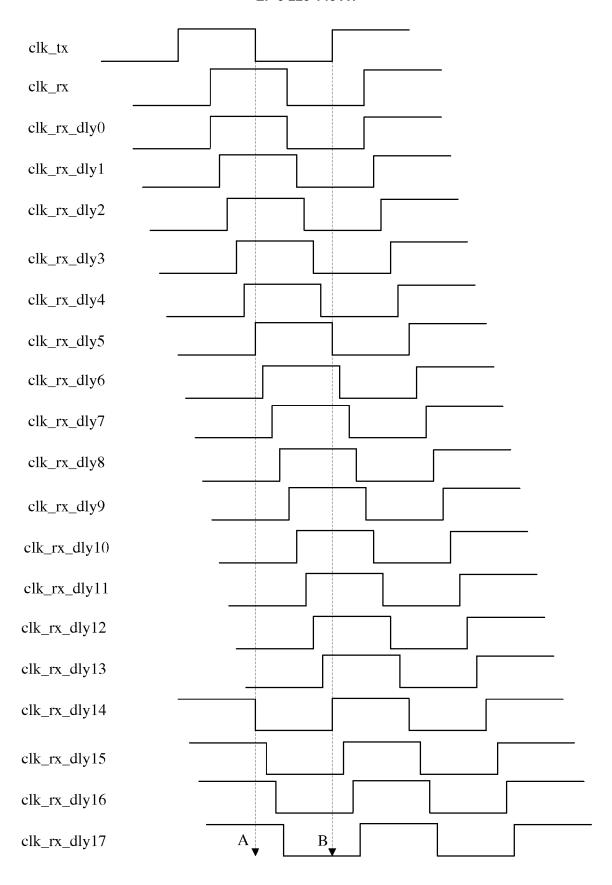

FIG. 5 is a schematic diagram of a time sequence of a signal according to an embodiment of the present invention;

FIG. 6 is a schematic diagram of data reading according to an embodiment of the present invention; FIG. 7 is a schematic diagram of another type of data reading according to an embodiment of the present invention; and

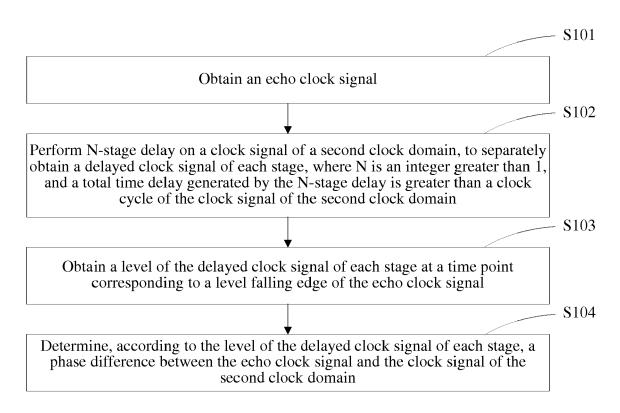

FIG. 8 is a schematic flowchart of a method for determining a phase difference according to an embodiment of the present invention.

#### **DESCRIPTION OF EMBODIMENTS**

**[0015]** The following clearly and completely describes the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Apparently, the described embodiments are merely some but not all of the embodiments of the present invention. All other embodiments obtained by a person of ordinary skill in the art based on the embodiments of the present invention without creative efforts shall fall within the protection scope of the present invention.

[0016] Embodiments of the present invention are applied to a cross clock domain interaction scenario, and the interaction scenario includes at least two clock domains that have a same source and frequency but different phases. Each clock domain may be used as a sending end and a receiving end. When being used as a sending end, a clock domain sends data to another clock domain; and when being used as a receiving end, the clock domain receives data sent by another clock domain. To make the following text easy to understand, it is specified that a clock domain used as a sending end is a first clock domain, and a clock domain used as a receiving end is a second clock domain. It should be understood that, a clock domain may be used as either a sending end or a receiving end, and therefore the first clock domain and the second clock domain do not refer to two clock domains in space, but two logical clock domains.

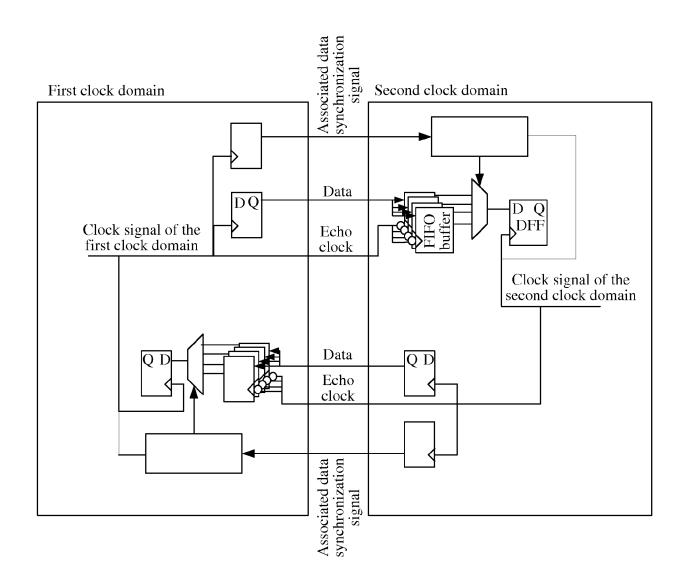

**[0017]** FIG. 3 is a schematic structural diagram of a data reading circuit according to an embodiment of the present invention.

[0018] As shown in FIG. 3, a first clock domain in this embodiment simultaneously sends data and an echo clock signal to a second clock domain, and the echo clock signal is a clock signal of the first clock domain. It should be noted that, it takes time to transmit the echo clock signal from the first clock domain to the second clock domain, and therefore there is a time delay between the echo clock signal received by the second clock domain and a current actual clock signal of the first clock domain. [0019] As shown in FIG. 3, the second clock domain in this embodiment includes a buffer configured to write data sent by the first clock domain and a flip-flop DFF configured to read the data output by the buffer. It should be noted that, during transmission of the data and the echo clock signal from the first clock domain to the second clock domain, a phase difference may be strictly kept unchanged (for example, the phase difference is kept unchanged by designing transmission lines to have a same length or neighboring line locations), and therefore it is feasible to write the data according to the echo clock signal. During a specific implementation process, a buffer in the second clock domain may be a FIFO buffer shown

in FIG. 3, and the FIFO buffer regularly writes data at each beat according to the echo clock signal.

**[0020]** As shown in FIG. 3, the data reading circuit in this embodiment includes a phase difference determining module 110, a time delay detection module 120, and a reading control module 130. The phase difference determining module 110 is connected to the echo clock signal and a clock signal of the second clock domain, the phase difference determining module 110 is connected to a reading control module 130, and the time delay detection module 120 is connected to the reading control module 130.

**[0021]** The phase difference determining module 110 is configured to determine a phase difference between the echo clock signal and the clock signal of the second clock domain, and send the phase difference to the reading control module 130. Specifically, the phase difference determining module 110 may further include, as shown in FIG. 4, N identical time delayers (BUF 1, BUF 2, BUF 3,..., BUF N-1, and BUF N), N+1 identical D flip-flops (DFF 0, DFF 1, DFF 2,..., DFF N-1, and DFF N), and a phase difference determining unit, where N is an integer greater than 1.

[0022] During a specific implementation process, an input port of BUF 1 is connected to a clock signal clk\_rx of the second clock domain; BUF 1, BUF 2, BUF 3, ..., BUF N-1, and BUF N are successively connected in series; input ports D of DFF 0, DFF 1, DFF 2,..., DFF N-1, and DFF N are connected to an echo clock signal clk\_tx; a clock port CP of DFF 0 is connected to the input port of BUF 1; clock ports CP of DFF 1, DFF 2, ..., DFF N-1, and DFF N are successively connected to output ports of BUF 1, BUF 2, BUF 3, ..., BUF N-1, and BUF N; output ports Q of DFF 0, DFF 1, DFF 2, ..., DFF N-1, and DFF N are connected to the phase difference determining unit; the phase difference determining unit is connected to the echo clock signal; and an output port Out of the phase difference determining unit is connected to the reading control module 130.

[0023] The time delayer is configured to shift a phase of a signal. BUF 1, BUF 2, BUF 3, ..., BUF N-1, and BUF N perform phase shifting on clk\_rx stage by stage, and separately output delayed clock signals clk\_rx\_dly\_1, clk\_rx\_dly\_2, clk\_rx\_dly\_3, ..., clk\_rx\_dly\_n-1, and clk\_rx\_dly\_n. It is required that a total time delay generated by the N time delayers is greater than a clock cycle of clk\_rx (that is, a phase difference between clk\_rx\_dly\_n and clk\_rx\_dly\_0 is greater than 360°). It should be understood that, when a D flip-flop detects a level rising edge at the clock port CP, an output port Q of the D flip-flop outputs a signal received by the input port D. Because clk\_rx and clk\_tx are signals that differ only in phase, signals that are actually output by output ports Q 0, Q 1, ..., Q N-1, and Q N of the N+1 D flip-flops may be considered as clk\_rx\_dly\_0, clk\_rx\_dly\_1, clk\_rx\_dly\_2, ..., clk\_rx\_dly\_n-1, and clk\_rx\_dly\_n.

[0024] Further, the phase difference determining unit determines, according to output results of the N+1 D flip-

55

40

35

40

flops (that is, signals output by Q 0, Q 1, ..., Q N-1, and Q N), the phase difference between the echo clock signal and the clock signal of the second clock domain. A specific manner is as follows:

At a time point corresponding to a level falling edge of the echo clock signal, levels of the output signals of Q 1, ..., Q N-1, and Q N are obtained; and in the levels, if the first a levels are high levels, the middle b levels are low levels, and the last c levels are high levels, and a, b, and c are positive integers, the phase difference between the echo clock signal and the clock signal of the second clock domain is calculated

according to a formula

$$\lambda = \frac{b-a}{2 \cdot h} \cdot 360^{\circ}$$

, where  $\lambda$

denotes the phase difference. For example, assuming that phases of the echo clock signal clk\_tx, the clock signal clk\_rx of the second clock domain, and clk\_rx\_dly\_0 to clk\_rx\_dly\_n are as shown in FIG. 5, at a level falling edge of clk\_tx (shown by A in FIG. 5), a sampling result of clk\_rx\_dly\_1 to clk\_rx\_dly\_n is 0x111110000000011111 (where "1" denotes a high level, and "0" denotes a low level), and therefore, it is obtained that a = 5, b = 9, and c = 4. It can be known, according to " b=9", that clk\_tx has nine unit delays from a level falling edge to a level rising edge, and therefore the phase of clk\_tx has 2x9 unit delays in one cycle; and it can be known, according to "a = 5 and b = 9", that there are five unit delays from a level rising edge of clk\_rx to a level falling edge of clk\_tx, and therefore there are (9-5) unit delays from a rising edge of clk\_rx to a previous rising edge of clk\_tx. Therefore, a phase difference by clk\_rx behind which lags clk tx is ((9-5)/2x9)x360°=80°. It should be noted that, the phase difference between the echo clock signal and the clock signal of the second clock domain may also be calculated when it is detected that an output of Q 0 is a level rising edge (shown by B in FIG. 5). A specific derivation method is substantially the same, and details are not described herein again. However, a disadvantage of this implementation manner is that: levels of output signals of Q 1 to Q N can only be obtained at a second level rising edge of the echo clock signal, lowering a calculation speed.

**[0025]** Optionally, a process of calculating, by the phase difference determining unit, the phase difference between the echo clock signal and the clock signal of the second clock domain may be implemented by using software or a hardware circuit, and this is not specifically limited herein.

**[0026]** Further optionally, the phase difference determining module 110 may further include a switch component as shown in FIG. 4. The input port of BUF 1 is connected to the clock signal clk\_rx of the second clock domain by using the switch component, and the switch com-

ponent is configured to control connection and disconnection between the input port of BUF 1 and clk\_rx. Further, the switch component is an ICG (Inside Clock Generator, inside clock generator) switch. The input port of BUF 1 is connected to an output port of the ICG switch, an input port of the ICG switch is connected to clk\_rx, an enabling port of the ICG switch is connected to an enabling signal, and the ICG switch is configured to control, according to the enable signal, connection and disconnection between the input port of BUF 1 and clk\_rx. An advantage lies in that, the switch component may turn off a circuit without determining a phase difference, thereby lowering power consumption.

**[0027]** Further optionally, the time delayer (BUF 1, BUF 2, BUF 3, ..., BUF N-1, or BUF N) is a gate circuit or multiple gate circuits that are connected in series.

**[0028]** Further optionally, the D flip-flop is a D flip-flop that resists a metastable state, and the metastable state refers to that the flip-flop cannot reach a stable state in a prescribed period of time. An advantage lies that, the D flip-flop that resists a metastable state can improve stability of a circuit.

**[0029]** The time delay detection module 120 is configured to detect a time delay value in transmission of data from the buffer to the flip-flop, and send the time delay value to the reading control module 130.

**[0030]** Specifically, referring to FIG. 3, the time delay detection module 120 detects a time delay value in transmission of data from an output port of the FIFO buffer to an input port D of the flip-flop. Optionally, a process of detecting a time delay value by the reading control module 130 may be implemented by using software or a hardware circuit, and this is not specifically limited herein.

**[0031]** The reading control module 130 is configured to determine, according to the phase difference and the time delay value, a triggering edge, at which the flip-flop can read the data output by the buffer, of the clock signal of the second clock domain.

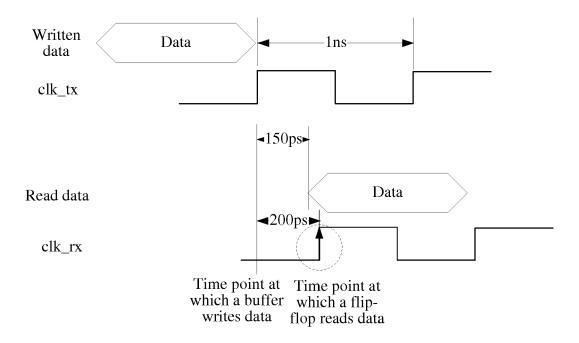

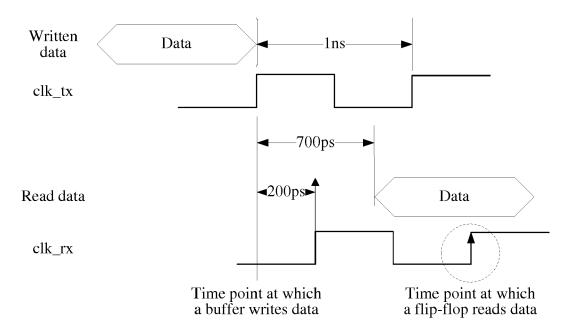

[0032] It should be noted that, a triggering edge of a flip-flop may include, according to a type thereof, a rising edge and a falling edge. For example, a triggering edge of a rising-edge flip-flop is a rising edge, and when a level rising edge is detected at a clock port CP of the risingedge flip-flop, and an output port Q of the rising-edge flipflop outputs a signal received by an input port D thereof. [0033] On one hand, if the triggering edge of the flipflop is a rising edge, when it is determined that a time value corresponding to the phase difference is greater than or equal to the time delay value, a next rising edge of the clock signal of the second clock domain from a time point at which the FIFO buffer writes data is used as a time point at which the flip-flop reads data. For example, referring to FIG. 6, assuming that a clock cycle of the clock signal clk\_rx of the second clock domain is 1 ns, a phase difference between clk\_rx and the echo clock signal clk\_tx is 72°, and a time delay value of data transmission is 150 ps, then the time value corresponding to the phase difference can be obtained through calcu-

20

40

45

50

lation: 200 ps (=1000 ps \*  $72^{\circ}$ /  $360^{\circ}$ ). Because 200 ps is greater than 150 ps, a next rising edge of clk\_rx (shown by a circle in FIG. 6) is used as a time point for reading data, thereby implementing data reading. When it is determined that the time value corresponding to the phase difference is less than the time delay value, according to a formula  $j = (\Delta t_{\text{max}} - \lambda)/T + 2$ , the  $j^{\text{th}}$  rising edge of the clock signal of the second clock domain from a time point at which the FIFO buffer writes data is used as a time point at which the flip-flop reads data, where  $\Delta t_{\rm max}$  denotes the time delay value,  $\lambda$  denotes the phase difference, / denotes an exact-division symbol, and T denotes the clock cycle of the clock signal of the second clock domain. For example, referring to FIG. 7, assuming that the clock cycle of the clock signal clk\_rx of the second clock domain is 1 ns, the phase difference between clk\_rx and the echo clock signal clk\_tx is 72°, and the time delay value of data transmission is 700 ps, then the time value corresponding to the phase difference can be obtained through calculation: 200 ps (=1000ps \* 72°/360°). Because 200 ps is less than 700 ps, it is obtained through calculation that j = (700-200)/1000 + 2 = 2, and therefore, the second rising edge of clk\_rx (shown by a circle in FIG. 7) is used as a time point for reading data, thereby implementing data reading.

9

[0034] On the other hand, if the triggering edge of the flip-flop is a falling edge, when it is determined that the time value corresponding to the phase difference is greater than or equal to the time delay value, a next rising edge of the clock signal of the second clock domain from a time point at which the FIFO buffer writes data is used as a time point at which the flip-flop reads data. When it is determined that the time value corresponding to the phase difference is less than the time delay value, according to a formula  $j = (\Delta t_{\text{max}} - T/2 - \lambda)/T + 2$ , the  $j^{\text{th}}$  falling edge of the clock signal of the second clock domain from a time point at which the buffer writes data is used as a time point at which the FIFO flip-flop reads data, where  $\Delta t_{\mathsf{max}}$  denotes the time delay value,  $\lambda$  denotes the phase difference, / denotes an exact-division symbol, and T denotes the cycle of the clock signal of the second clock domain.

[0035] It can be seen from the foregoing that, the data reading circuit in this embodiment of the present invention includes the phase difference determining module 110, the time delay detection module 120, and the reading control module 130, where the phase difference determining module 110 can determine a phase difference between an echo clock signal and a clock signal of a local domain, the time delay detection module 120 can detect a time delay value in internal transmission of data, and the reading control module 130 can determine, according to the phase difference and the time delay value, a time point for reading data, thereby implementing data reading. In addition, in this embodiment of the present invention, except for I/O interfaces used to transmit the data and the echo clock signal, the phase difference between the echo clock signal and the clock signal of the local

domain can be determined without the need to add an extra I/O interface between two clock domains, thereby reducing hardware overheads and difficulty in implementation.

**[0036]** FIG. 8 is a schematic flowchart of a method for determining a phase difference according to an embodiment of the present invention, and the method may be applied to the time delay detection module 110 in the method described in FIG. 3 and/or FIG. 4. As shown in the figure, a process of the method for determining a phase difference in this embodiment may include:

S101: Obtain an echo clock signal.

S102: Perform N-stage delay on a clock signal of a second clock domain, to obtain a delayed clock signal of each level, where N is an integer greater than 1, and a total time delay generated by the N-stage delay is greater than a clock cycle of the clock signal of the second clock domain.

[0037] For example, multi-stage delay is performed on the clock signal clk\_rx of the second clock domain, to separately obtain delayed clock signals clk\_rx\_dly\_1, clk\_rx\_dly\_2, clk\_rx\_dly\_3, ..., clk\_rx\_dly\_n-1, and clk\_rx\_dly\_n of respective stages, where a phase difference between clk\_rx\_dly\_n and clk\_rx\_dly\_0 exceeds 360°, as shown in FIG. 5.

[0038] It should be noted that step S101 and step S102 are performed at the same time rather than successively. [0039] S103: Obtain a level of the delayed clock signal of each stage at a time point corresponding to a level falling edge of the echo clock signal.

**[0040]** It should be noted that, in multiple levels that are obtained, the first a levels are high levels, the middle b levels are low levels, the last c levels are high levels, and a, b, and c are positive integers.

**[0041]** For example, assuming that phases of the echo clock signal clk\_tx, the clock signal clk\_rx of the second clock domain, and clk\_rx\_dly\_1 to clk\_rx\_dly\_n are as shown in FIG. 5, then when a level falling edge (shown by A in FIG. 5) of clk\_tx is detected, obtained levels of clk\_rx\_dly\_1 to clk\_rx\_dly\_n are 0x111110000000001111 (where "1" denotes a high level, and "0" denotes a low level), and it is obtained that a = 5, b = 9, and c = 4.

**[0042]** S104: Determine, according to the level of the delayed clock signal of each stage, a phase difference between the echo clock signal and the clock signal of the second clock domain.

**[0043]** Optionally, the phase difference between the echo clock signal and the clock signal of the second clock domain is calculated according to a formula

$$\lambda {=} \frac{b - a}{2 \cdot b} {\cdot} 360^{\circ} \,, \,\, \text{where} \,\, \lambda \,\, \text{denotes the phase differ-}$$

ence.

**[0044]** For example, assuming that a = 5, b = 9, and c = 4, it can be known, according to "b = 9", that clk\_tx

20

25

30

40

45

50

55

has nine unit delays from a level falling edge to a level rising edge of a level, and therefore the phase of clk\_tx has 2x9 unit delays in one cycle; and it can be known, according to "a = 5 and b = 9", that there are five unit delays from a level rising edge of clk\_rx to a level falling edge of clk\_tx; therefore, there are (9-5) unit delays from a rising edge of clk rx to a previous rising edge of clk\_tx, and it is obtained that a phase difference by which clk\_rx lags behind clk\_tx is  $((9-5)/2x9)x360^\circ=80^\circ$ .

**[0045]** It can be seen from the foregoing that, in this embodiment of the present invention, N-stage delay is performed on the clock signal of the second clock domain, to obtain a delayed clock signal of each stage; and then a phase difference between the echo clock signal and the clock signal of the second clock domain may be obtained according to a level of the delayed clock signal of each stage at a voltage falling edge of the echo clock signal.

[0046] The data reading circuit in this embodiment of the present invention includes a phase difference determining module, a time delay detection module, and a reading control module, where the phase difference determining module can determine a phase difference between an echo clock signal and a clock signal of a local domain, the time delay detection module can detect a time delay value in internal transmission of data, and the reading control module can determine, according to the phase difference and the time delay value, a time point for reading data, thereby implementing data reading. In addition, in this embodiment of the present invention, except for I/O interfaces used to transmit the data and the echo clock signal, the phase difference between the echo clock signal and the clock signal of the local domain can be determined without the need to add an extra I/O interface between two clock domains, thereby reducing hardware overheads and difficulty in implementation.

**[0047]** A person of ordinary skill in the art may understand that all or some of the processes of the methods in the embodiments may be implemented by a computer program instructing relevant hardware. The program may be stored in a computer readable storage medium. When the program runs, the processes of the methods in the embodiments are performed. The foregoing storage medium may include: a magnetic disk, an optical disc, a read-only memory (Read-Only Memory, ROM), or a random access memory (Random Access Memory, RAM).

**[0048]** What is disclosed above is merely exemplary embodiments of the present invention, and certainly is not intended to limit the protection scope of the present invention. Therefore, equivalent variations made in accordance with the claims of the present invention shall fall within the scope of the present invention.

#### Claims

1. A data reading circuit, wherein the circuit is applied

to a second clock domain; the second clock domain comprises a buffer configured to write data sent by a first clock domain, and a flip-flop configured to read data output by the buffer; the first clock domain simultaneously sends the data and an echo clock signal; the echo clock signal is a clock signal of the first clock domain; the circuit comprises a phase difference determining module, a time delay detection module, and a reading control module; the phase difference determining module is connected to the echo clock signal and a clock signal of the second clock domain; the phase difference determining module is connected to the reading control module; and the time delay detection module is connected to the reading control module; and

the phase difference determining module is configured to determine a phase difference between the echo clock signal and the clock signal of the second clock domain, and send the phase difference to the reading control module;

the time delay detection module is configured to detect a time delay value in transmission of the data from the buffer to the flip-flop, and send the time delay value to the reading control module; and

the reading control module is configured to determine, according to the phase difference and the time delay value, a triggering edge, at which the flip-flop can read the data output by the buffer, of the clock signal of the second clock domain.

- 2. The circuit according to claim 1, wherein the phase difference determining module comprises N identical time delayers, N+1 identical D flip-flops, and a phase difference determining unit, wherein N is an integer greater than 1; the N time delayers are successively connected in series; an input port of the first time delayer is connected to the clock signal of the second clock domain; a time delay generated by the N time delayers is greater than a clock cycle of the clock signal of the second clock domain; input ports of the N+1 D flip-flops are connected to the echo clock signal; a clock port of the first D flip-flop is connected to the input port of the first time delayer; clock ports of the remaining N D flip-flops are successively connected to output ports of the N time delayers; output ports of the N+1 D flip-flops are connected to the phase difference determining unit; the phase difference determining unit is connected to the echo clock signal; and the phase difference determining unit is configured to determine, according to output results of the N+1 D flip-flops, the phase difference between the echo clock signal and the clock signal of the second clock domain, and send the phase difference to the reading control module.

- 3. The circuit according to claim 2, wherein the phase difference determining unit is specifically configured to:

15

20

25

at a time point corresponding to a level falling edge of the echo clock signal, obtain levels of output signals of the second D flip-flop to the  $(N+1)^{th}$  D flip-flop, wherein in the levels of the output signals, the first a levels are high levels, the middle b levels are low levels, the last c levels are high levels, and a, b, and c are positive integers; and

calculate, according to a formula

$$\lambda = \frac{b-a}{2 \cdot b} \cdot 360^{\circ}$$

, the phase difference be-

tween the echo clock signal and the clock signal of the second clock domain, wherein  $\lambda$  denotes the phase difference.

**4.** The circuit according to claim 1, wherein the reading control module is specifically configured to:

if the triggering edge at which the flip-flop reads the data output by the buffer is a rising edge, when a time value corresponding to the phase difference is greater than or equal to the time delay value, use a next rising edge, from a time point at which the buffer writes the data, of the clock signal of the second clock domain as a time point at which the flip-flop reads the data; or when a time value corresponding to the phase difference is less than the time delay value, according to a formula  $j = (\Delta t_{\text{max}} - \lambda)/T + 2$ , use the Jth rising edge, from a time point at which the buffer writes the data, of the clock signal of the second clock domain as a time point at which the flip-flop reads the data, wherein  $\Delta t_{\rm max}$  denotes the time delay value,  $\lambda$  denotes the phase difference, I denotes an exact-division symbol, T denotes a cycle of the clock signal of the first clock domain and a cycle of the clock signal of the second clock domain; or

if the triggering edge at which the flip-flop reads the data output by the buffer is a falling edge, when a time value corresponding to the phase difference is greater than or equal to the time delay value, use a next falling edge, from a time point at which the buffer writes the data, of the clock signal of the second clock domain as a time point at which the flip-flop reads the data; or when the time value corresponding to the phase difference is less than the time delay value, according to a formula  $j = (\Delta t_{\text{max}} - T / 2 \lambda$ ) /T + 2, use the  $j^{th}$  falling edge, from a time point at which the buffer writes the data, of the clock signal of the second clock domain as a time point at which the flip-flop reads the data, wherein  $\Delta t_{\rm max}$  denotes the time delay value,  $\lambda$ denotes the phase difference, I denotes an exact-division symbol, T denotes a cycle of the clock signal of the second clock domain.

- 5. The circuit according to claim 2, wherein the phase difference determining module further comprises a switch component, the input port of the first time delayer is connected to the clock signal of the second clock domain by using the switch component, and the switch component is configured to control connection and disconnection between the input port of the first time delayer and the clock signal of the second clock domain.

- 6. The circuit according to claim 5, wherein the switch component is an inside clock generator ICG switch, the input port of the first time delayer is connected to an output port of the ICG switch, an input port of the ICG switch is connected to the clock signal of the second clock domain, an enabling port of the ICG switch is connected to an enabling signal, and the switch component is specifically configured to control connection and disconnection between the input port of the first time delayer and the clock signal of the second clock domain.

- 7. The circuit according to claim 2, wherein the time delayer is a gate circuit or multiple gate circuits that are connected in series.

- **8.** The circuit according to claim 3, wherein the D flip-flop is a D flip-flop that resists a metastable state.

FIG. 1

FIG. 2

FIG. 3

12

FIG. 5

FIG. 6

FIG. 7

FIG. 8

## **EUROPEAN SEARCH REPORT**

Application Number EP 17 16 1840

| DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                        |                                                                                                                                                                      |                                                                                                     |                                                                                                                                                                                                     |                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Category                                                                                                                                                                                                   | Citation of document with ind<br>of relevant passag                                                                                                                  |                                                                                                     | Relevant<br>to claim                                                                                                                                                                                | CLASSIFICATION OF THE APPLICATION (IPC)            |

| A                                                                                                                                                                                                          | CLIFFORD E CUMMINGS:<br>Crossing (CDC) Desig<br>Techniques Using Sys<br>SYNOPSYS USERS GROUP<br>30 November 2008 (20<br>XP055306405,<br>* section 3.6;<br>figure 7 * | n & Verification<br>temVerilog",                                                                    | 1-8                                                                                                                                                                                                 | INV.<br>G06F5/06<br>H04L7/00                       |

| A                                                                                                                                                                                                          | US 2013/170591 A1 (S<br>4 July 2013 (2013-07<br>* paragraphs [0024]                                                                                                  |                                                                                                     | 1-8                                                                                                                                                                                                 |                                                    |

| A                                                                                                                                                                                                          | 11 August 1998 (1998                                                                                                                                                 | IO SATOSHI [JP] ET AL) -08-11) - column 10, line 19;                                                | 1-8                                                                                                                                                                                                 | TECHNICAL FIELDS<br>SEARCHED (IPC)<br>G06F<br>H04L |

|                                                                                                                                                                                                            | The present search report has be                                                                                                                                     | en drawn up for all claims                                                                          | -                                                                                                                                                                                                   |                                                    |

| Place of search Date of co                                                                                                                                                                                 |                                                                                                                                                                      | Date of completion of the search                                                                    |                                                                                                                                                                                                     | Examiner                                           |

| Munich                                                                                                                                                                                                     |                                                                                                                                                                      | 17 July 2017                                                                                        | Pri                                                                                                                                                                                                 | ns, Leendert                                       |

| CATEGORY OF CITED DOCUMENTS  X: particularly relevant if taken alone Y: particularly relevant if combined with another document of the same category A: technological background O: non-written disclosure |                                                                                                                                                                      | E : earlier patent doc<br>after the filing dat<br>or D : document cited in<br>L : document cited fo | T : theory or principle underlying the invention E : earlier patent document, but published on, or after the filing date D : document cited in the application L : document cited for other reasons |                                                    |

# EP 3 223 145 A1

# ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 17 16 1840

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

17-07-2017

| )         | Patent document cited in search report | Publication<br>date | Patent family<br>member(s)                                        | Publication<br>date                                  |

|-----------|----------------------------------------|---------------------|-------------------------------------------------------------------|------------------------------------------------------|

|           | US 2013170591 A1                       | 04-07-2013          | NONE                                                              |                                                      |

| i         | US 5793823 A                           | 11-08-1998          | DE 19537342 A1<br>FR 2725572 A1<br>JP H08111675 A<br>US 5793823 A | 18-04-1996<br>12-04-1996<br>30-04-1996<br>11-08-1998 |

|           |                                        |                     |                                                                   |                                                      |

| )         |                                        |                     |                                                                   |                                                      |

|           |                                        |                     |                                                                   |                                                      |

| į         |                                        |                     |                                                                   |                                                      |

|           |                                        |                     |                                                                   |                                                      |

|           |                                        |                     |                                                                   |                                                      |

| '         |                                        |                     |                                                                   |                                                      |

|           |                                        |                     |                                                                   |                                                      |

| i         |                                        |                     |                                                                   |                                                      |

|           |                                        |                     |                                                                   |                                                      |

| )         |                                        |                     |                                                                   |                                                      |

|           |                                        |                     |                                                                   |                                                      |

|           |                                        |                     |                                                                   |                                                      |

| i         |                                        |                     |                                                                   |                                                      |

|           |                                        |                     |                                                                   |                                                      |

| )         |                                        |                     |                                                                   |                                                      |

| ගු        |                                        |                     |                                                                   |                                                      |

| ORM P0459 |                                        |                     |                                                                   |                                                      |

For more details about this annex : see Official Journal of the European Patent Office, No. 12/82