### (11) EP 3 421 965 A1

(12)

## **EUROPEAN PATENT APPLICATION** published in accordance with Art. 153(4) EPC

(43) Date of publication: **02.01.2019 Bulletin 2019/01**

(21) Application number: 16891414.1

(22) Date of filing: 23.02.2016

(51) Int Cl.: **G01N** 3/00 (2006.01)

(86) International application number: PCT/JP2016/055194

(87) International publication number:WO 2017/145255 (31.08.2017 Gazette 2017/35)

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

**Designated Extension States:**

**BA ME**

**Designated Validation States:**

MA MD

(71) Applicant: Shimadzu Corporation Kyoto-shi, Kyoto 604-8511 (JP) (72) Inventor: TSUJI Hiroshi Kyoto-shi

Kyoto 604-8511 (JP)

(74) Representative: Webster, Jeremy Mark et al Mewburn Ellis LLP City Tower

40 Basinghall Street London EC2V 5DE (GB)

#### (54) SYNCHRONIZATION CIRCUIT FOR MATERIAL TESTER AND MATERIAL TESTER

(57) A synchronous controller 49 is connected to each of boards 51, 52, and 53 by one communication wire, and one communication path is formed between the synchronous controller 49 and each of the boards 51, 52, and 53. A multiple synchronization signal S in which a plurality of synchronization signals are multiplexed is transmitted from the synchronous controller 49 to each of the boards 51, 52, and 53. Signal extraction

units 61a, 61b, and 61c as extraction means for recognizing synchronization signals included in the multiple synchronization signal S and extracting the individual synchronization signals are provided in the boards 51, 52, and 53, respectively. The individual synchronization signals are extracted from the multiple synchronization signal S input to the boards 51, 52, and 53 by the signal extraction units 61a, 61b, and 61c, respectively.

[FIG. 1]

EP 3 421 965 A1

25

35

45

zation signals having different frequencies. In the syn-

#### Description

#### Technical Field

**[0001]** The present invention relates to a synchronous circuit for a material testing machine synchronously operating a plurality of functional units and a material testing machine provided with the synchronous circuit.

#### **Background Art**

[0002] Arranged in a material testing machine performing material testing are a load mechanism giving a test load to a test piece and a plurality of measuring devices such as a load detector detecting a test force given to the test piece by the load mechanism and a displacement meter detecting displacement generated in the test piece. Configured in the material testing machine as described above are a plurality of circuits such as a detection circuit converting a physical quantity detected by the measuring devices from an analog signal to a digital signal and inputting the digital signal to a control unit and an operating circuit operating the testing machine by converting a command value for controlling an operation of a motor as a load mechanism driving source from the control unit from a digital signal to an analog signal (see

[0003] Patent Document 1 and Patent Document 2).

Citation List

Patent Document

#### [0004]

Patent Document 1: JP-A-2007-218809 Patent Document 2: Japanese Patent No. 5435135

Summary of the Invention

#### **Technical Problem**

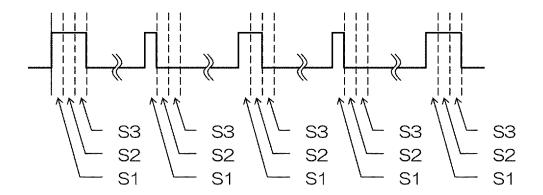

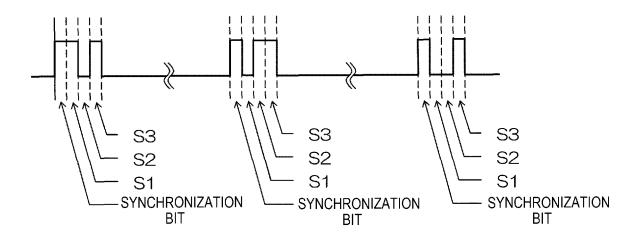

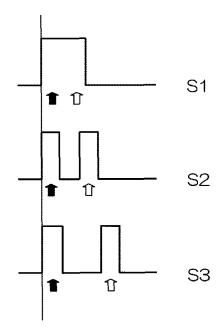

[0005] Fig. 9 is a block diagram illustrating the outline of a synchronous circuit according to the related art. Fig. 10 is an explanatory diagram of a synchronization signal according to the related art. A physical quantity detection circuit and a load mechanism operating circuit in a material testing machine are configured as units in which function-executing parts are placed on separate boards. A synchronous circuit in which a synchronous controller 149 and each of boards 151, 152, and 153 are connected to each other by communication wiring is organized so that a synchronized operation is performed by an analog-to-digital (AD) converter and a digital-to-analog (DA) converter mounted on the separate boards.

**[0006]** In the related art, communication paths are provided between the synchronous controller 149 and each of the boards 151, 152, and 153 and the number of communication paths depends on the number of synchroni-

chronous circuit that is illustrated in Fig. 9, communication paths are provided to respond to each of three synchronization signals S1, S2, and S3 having different pulse repetition cycles in the pulse train that is illustrated in Fig. 10. The synchronization signals S1, S2, and S3 are respectively transmitted from the synchronous controller 149 to the boards 151, 152, and 153 through the communication paths assigned to the respective signals. Each of the synchronization signals S1, S2, and S3 indicates the timing of an operation to be synchronized in each circuit. For example, when data output from the AD converter and the DA converter of the circuits are synchronized at a timing specified in the synchronization signal S1, the synchronization signal S1 is transmitted from the synchronous controller to each board via the communication path through which the synchronization signal S1 is transmitted.

**[0007]** The synchronous circuit according to the related art is problematic in that the number of communication paths and the number of synchronization signals should be equal to each other, the number of communication wiring increases as the number of synchronization signals increases, and handling of wiring is complicated as described above. In addition, as the number of communication paths is determined during circuit design, an increase or decrease in the number of synchronization signals after circuit design requires a time-taking change in circuit design, which is another problem.

**[0008]** The invention has been made to solve the above problems, and an object thereof is to provide a synchronous circuit for a material testing machine and a material testing machine in which a plurality of synchronization signals are multiplexed in one communication path.

Solution to Problem

**[0009]** According to the invention described in claim 1, a synchronous circuit is provided with a synchronous controller synchronizing operations of a plurality of functional units constituting a material testing machine, communication paths are provided to be connected to the synchronous controller and the respective functional units, the synchronous controller transmits a multiple synchronization signal in which a plurality of synchronization signals are multiplexed to the plurality of functional units via one communication path, and each of the plurality of functional units is provided with extraction means and the extraction means recognize and extract the respective synchronization signals from the multiple synchronization signal.

**[0010]** According to the invention described in claim 2, in the synchronous circuit for a material testing machine according to the invention described in claim 1, the multiple synchronization signal is a signal in which each of the plurality of synchronization signals included in the multiple synchronization signal is a multiplexed signal

25

35

40

45

50

55

with a frequency as 1/integer of a closest higher frequency and a pulse width in a pulse train varies with the number of the plurality of synchronization signals included in the multiple synchronization signal.

[0011] According to the invention described in claim 3, in the synchronous circuit for a material testing machine according to the invention described in claim 2, an analog circuit or a digital circuit constitutes the extraction means. [0012] According to the invention described in claim 4, in the synchronous circuit for a material testing machine according to the invention described in claim 1, the multiple synchronization signal is a signal in which a signal with a frequency as 1/integer of the synchronization signal with a highest frequency among the plurality of synchronization signals included in the multiple synchronization signal is multiplexed and has a pulse train in which a pulse train of the highest-frequency synchronization signal is used as a reference and pulses of the other synchronization signals are placed at predetermined positions behind a position of a pulse of the highest-frequency synchronization signal in the pulse train.

[0013] According to the invention described in claim 5, in the synchronous circuit for a material testing machine according to the invention described in claim 1, the multiple synchronization signal includes a synchronization bit as a common multiple of frequencies of the plurality of synchronization signals included in the multiple synchronization signal and has a pulse train in which respective pulses of the plurality of synchronization signals are placed at predetermined different positions with respect to a position of the synchronization bit in the pulse train.

[0014] According to the invention described in claim 6, in the synchronous circuit for a material testing machine according to the invention described in claim 4, a digital circuit constitutes the extraction means.

**[0015]** According to the invention described in claim 7, in the synchronous circuit for a material testing machine according to the invention described in claim 5, a digital circuit constitutes the extraction means.

[0016] According to the invention described in claim 8, a material testing machine includes a load mechanism giving a test load to a test piece, a measuring device detecting a change in physical quantity in the test piece, and a control device including a calculation control unit calculating a controlled variable of the load mechanism and calculating a physical quantity based on a value detected by the measuring device and a display section displaying a result of the calculation by the calculation control unit, in which the control device includes a load mechanism control unit converting the controlled variable calculated by the calculation control unit into an operation signal of a power source of the load mechanism and outputting the operation signal, a physical quantity detection unit receiving input from the measuring device, and a display unit for displaying the physical quantity calculated by the calculation control unit in the display section, and the control device includes the synchronous circuit for a material testing machine according to the invention described in any one of claims 1 to 7.

Advantageous Effects of the Invention

[0017] According to the inventions described in claims 1 to 8, the synchronous controller transmits the multiple synchronization signal in which the plurality of synchronization signals are multiplexed to one of the plurality of functional units via one communication path and the reception sides are provided with the extraction means for recognizing and extracting the individual synchronization signals from the multiple synchronization signal. Accordingly, one path is sufficient for wiring between the synchronous controller and the boards and units as the functional units and wiring during synchronous circuit organization can be simplified. In addition, an easy response is possible and no change in circuit design is required, unlike in the related art, even in a case where the number of synchronization signals is to be increased.

**[0018]** According to the invention described in claim 2, the multiple synchronization signal is a signal in which each of the plurality of synchronization signals included in the multiple synchronization signal is the multiplexed signal with the frequency as 1/integer of the closest higher frequency and the pulse width in the pulse train varies with the number of the plurality of synchronization signals included in the multiple synchronization signal. Accordingly, the configuration of the circuit receiving the multiple synchronization signal and extracting the individual synchronization signals can be simplified.

**[0019]** According to the invention described in claim 4, the multiple synchronization signal is a signal in which the signal with the frequency as 1/integer of the synchronization signal with the highest frequency among the plurality of synchronization signals included in the multiple synchronization signal is multiplexed and has the pulse train in which the pulses of the other frequencies are placed based on the pulse train of the highest-frequency synchronization signal. The frequency of the synchronization signal can be selected without considering the relationship between the other synchronization signals insofar as the condition is satisfied that the frequency of the synchronization signal is 1/integer of the frequency of the highest-frequency synchronization signal.

**[0020]** According to the invention described in claim 5, the multiple synchronization signal includes the synchronization bit as a common multiple of the frequencies of the plurality of synchronization signals included in the multiple synchronization signal and has the pulse train in which the respective pulses of the plurality of synchronization signals are placed based on the position of the synchronization bit in the pulse train. Accordingly, placement of the pulses of the plurality of synchronization signals in the pulse train can be performed more freely.

Brief Description of the Drawings

[0021]

40

45

50

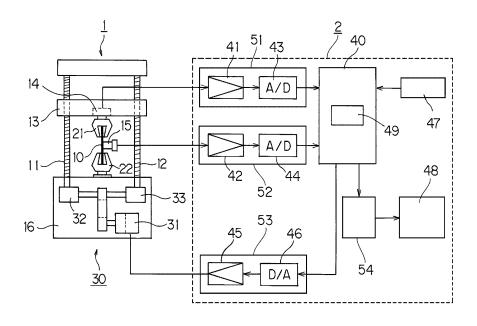

Fig. 1 is a schematic diagram of a material testing machine according to the invention.

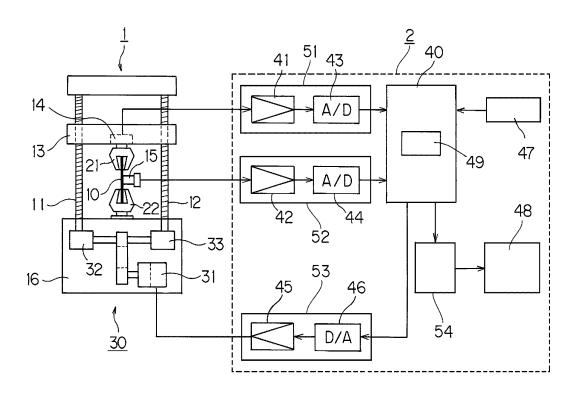

Fig. 2 is a block diagram illustrating the outline of a synchronous circuit according to the invention.

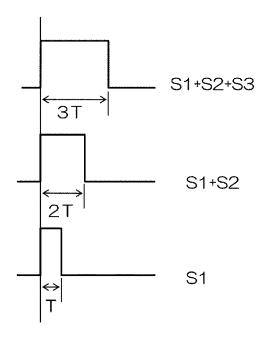

Fig. 3 is an explanatory diagram illustrating an example of a multiple synchronization signal.

Fig. 4 is a schematic diagram describing separation of the multiple synchronization signal into individual synchronization signals.

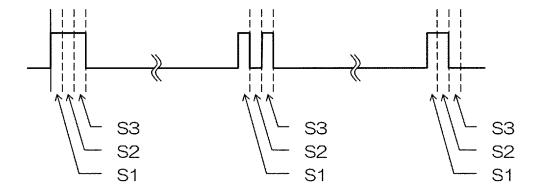

Fig. 5 is an explanatory diagram illustrating another example of the multiple synchronization signal.

Fig. 6 is a schematic diagram describing separation of the multiple synchronization signal into individual synchronization signals.

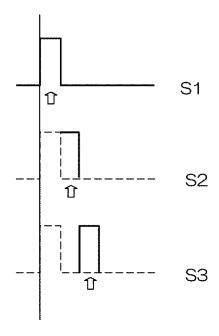

Fig. 7 is an explanatory diagram illustrating another example of the multiple synchronization signal.

Fig. 8 is a schematic diagram describing separation of the multiple synchronization signal into individual synchronization signals.

Fig. 9 is a block diagram illustrating the outline of a synchronous circuit according to the related art.

Fig. 10 is an explanatory diagram of a synchronization signal according to the related art.

#### Mode for Carrying Out the Invention

**[0022]** Hereinafter, an embodiment of the invention will be described with reference to accompanying drawings. Fig. 1 is a schematic diagram of a material testing machine according to the invention.

**[0023]** A testing machine main body 1 and a control device 2 constitute this material testing machine. The testing machine main body 1 is provided with a table 16, a pair of screw rods 11 and 12 rotatably standing on the table 16 while facing a vertical direction, a crosshead 13 movable along the screw rods 11 and 12, a load mechanism 30 for giving a load to a test piece 10 by moving the crosshead 13, and a load cell 14 and a displacement meter 15 as measuring devices measuring a change in physical quantity in the test piece 10.

[0024] The crosshead 13 is connected to the pair of screw rods 11 and 12 via nuts (ball nuts, not illustrated). Worm reducers 32 and 33 of the load mechanism 30 are connected to the lower end portions of the screw rods 11 and 12, respectively. The worm reducers 32 and 33 are connected to a servomotor 31, which is a driving source for the load mechanism 30, and are configured such that rotation of the servomotor 31 is transmitted to the pair of screw rods 11 and 12 via the worm reducers 32 and 33. As a result of rotation of the servomotor 31, the pair of screw rods 11 and 12 synchronously rotate, and then the crosshead 13 moves upward or downward along the screw rods 11 and 12.

**[0025]** An upper gripper 21 for gripping the upper end portion of the test piece 10 is attached to the crosshead 13. A lower gripper 22 for gripping the lower end portion of the test piece 10 is attached to the table 16. In a case where a tensile test is performed, the test piece 10 is

loaded with a test force (tensile load) by the crosshead 13 being raised in a state where both end portions of the test piece 10 are gripped by the upper gripper 21 and the lower gripper 22.

[0026] A computer, a sequencer, and peripheral equipment thereof constitute the control device 2, and the control device 2 is provided with a control unit 40 that has a CPU executing a logical operation, a ROM storing an operation program required for apparatus control, a RAM temporarily storing data and so on during control, and the like and controls the entire apparatus, a test force detection board 51 on which a load amplifier 41 and an AD converter 43 are mounted, a displacement detection board 52 on which a strain amplifier 42 and an AD converter 44 are mounted, and a motor control board 53 on which a servo amplifier 45 and a DA converter 46 are mounted. The board 51 and the board 52 correspond to the physical quantity detection units according to the invention, and the board 53 corresponds to the load mechanism control unit according to the invention.

[0027] When the load mechanism 30 is operated, the test force that acts on the test piece 10 with both ends gripped by the upper gripper 21 and the lower gripper 22 is detected by the load cell 14, amplified by the load amplifier 41, and then digitalized by the AD converter 43 and input to the control unit 40. In addition, the displacement amount that is generated in the test piece 10 is measured by the displacement meter 15, amplified by the strain amplifier 42, and then digitalized by the AD converter 44 and input to the control unit 40.

[0028] In the control unit 40, data processing is executed with test force data and displacement amount data from the load cell 14 and the displacement meter 15 captured and feedback control of rotational drive of the servomotor 31 is executed by means of fluctuations in the test force and the displacement amount input as digital data. The servomotor 31 is driven to rotate by a current supplied from the servo amplifier 45. The servo amplifier 45 supplies the servomotor 31 with the current in accordance with the magnitude according to a rotational angular velocity command supplied from the control unit 40 via the DA converter 46.

[0029] An input unit 47 is connected to the control unit 40 to receive various types of input from an operator. In addition, a display section 48 is connected to the control unit 40 via a graphic board 54 on which a graphics processing unit (GPU) is mounted, and the display section 48 displays the displacement amount and the test force calculated in the control unit 40. The graphic board 54 corresponds to the display unit according to the invention. Furthermore, the control unit 40 is provided with a synchronous controller 49 for synchronizing operations of the AD converter 43, the AD converter 44, and the DA converter 46.

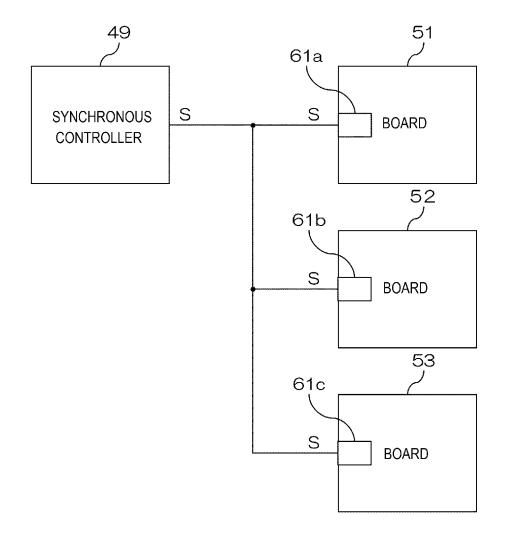

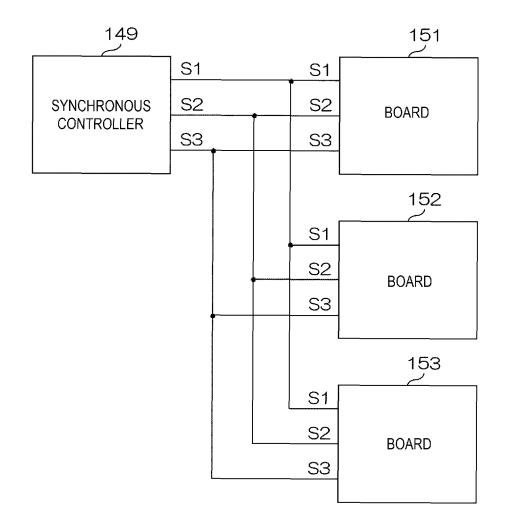

**[0030]** Fig. 2 is a block diagram illustrating the outline of a synchronous circuit according to the invention. In Fig. 2, wiring between the synchronous controller 49 and the boards 51, 52, and 53 are schematically illustrated.

25

30

40

45

[0031] The synchronous controller 49 is connected to each of the boards 51, 52, and 53 by one communication wire, and one communication path is formed between the synchronous controller 49 and each of the boards 51, 52, and 53. A multiple synchronization signal S in which a plurality of synchronization signals are multiplexed is transmitted from the synchronous controller 49 to each of the boards 51, 52, and 53. Signal extraction units 61a, 61b, and 61c as extraction means for recognizing synchronization signals S1, S2, and S3 included in the multiple synchronization signal S and extracting the individual synchronization signals S1, S2, and S3 are provided in the boards 51, 52, and 53, respectively. The individual synchronization signals S1, S2, and S3 are extracted from the multiple synchronization signal S input to the boards 51, 52, and 53 by the signal extraction units 61a, 61b, and 61c, respectively. Then, for example, the AD converter 43 of the board 51, the AD converter 44 of the board 52, and the DA converter 46 of the board 53 synchronously output data by the timing of the synchronization signal S1 separated from the multiple synchronization signal S.

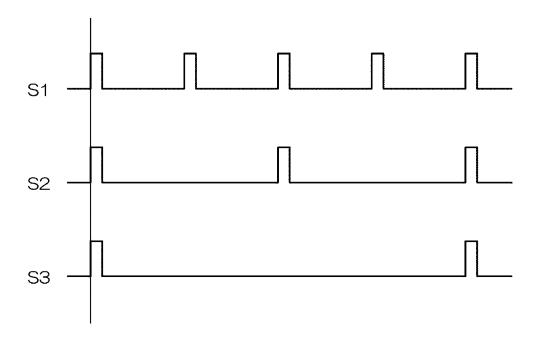

**[0032]** Fig. 3 is an explanatory diagram illustrating an example of the multiple synchronization signal S. Fig. 4 is a schematic diagram describing separation of the multiple synchronization signal S into the individual synchronization signals S1, S2, and S3.

[0033] The three synchronization signals S1, S2, and S3 that have different frequencies are multiplexed in the multiple synchronization signal S illustrated in Fig. 3. The pulse train of the multiple synchronization signal S is a pulse train in which the synchronization signal S1, which has the highest frequency among the synchronization signals included in the multiple synchronization signal S, is at the head with the synchronization signal S2 that has the second-highest frequency following the synchronization signal S1 and the synchronization signal S3 that has the third-highest frequency following the synchronization signal S2. In this multiple synchronization signal S, the frequency of the synchronization signal S2 is 1/integer of the frequency of the synchronization signal S1 and the frequency of the synchronization signal S3 is 1/integer of the frequency of the synchronization signal S2. In other words, in the relationship thereof, the synchronization signals S1, S2, and S3 included in the multiple synchronization signal S have a frequency as 1/integer of the closest higher frequency. The pulse width of each pulse in the pulse train of the multiple synchronization signal S is an integral multiple of a predetermined time T, which is the pulse width of the highest-frequency synchronization signal S1.

[0034] In the case of the multiple synchronization signal S illustrated in Fig. 3, the signal extraction units 61a, 61b, and 61c confirm the ratio of the pulse width of a signal to the predetermined time T in the boards 51, 52, and 53 receiving the multiple synchronization signal S transmitted from the synchronous controller 49. In other words, the signal extraction units 61a, 61b, and 61c rec-

ognize that only the synchronization signal S1 is included in the pulse when the pulse width is 100% of the predetermined time T as shown in the lower part of Fig. 4. The signal extraction units 61a, 61b, and 61c recognize that the synchronization signal S1 and the synchronization signal S2 are included in the pulse when the pulse width is 200% of the predetermined time T as shown in the middle part of Fig. 4. The signal extraction units 61a, 61b, and 61c recognize that the synchronization signal S1, the synchronization signal S2, and the synchronization signal S3 are included in the pulse when the pulse width is 300% of the predetermined time T as shown in the upper part of Fig. 4. Then, the pulses of the synchronization signal S1, the synchronization signal S2, and the synchronization signal S3 of different timings are separated and extracted from the pulse train of the multiple synchronization signal S.

[0035] In the multiple synchronization signal S illustrated in Fig. 3, the synchronization signals S1, S2, and S3 have a frequency as 1/integer of the closest higher frequency, and thus the individual synchronization signals S1, S2, and S3 can be easily sorted out from the multiple synchronization signal S with an analog circuit using a CR filter based on capacity (C) and resistance (R). Accordingly, in the case of the multiple synchronization signal S illustrated in Fig. 3, the circuit configuration of the respective signal extraction units 61a, 61b, and 61c of the boards 51, 52, and 53 can be simplified. Although the three synchronization signals S1, S2, and S3 with different frequencies are multiplexed in Figs. 3 and 4, the number of multiplexed synchronization signals is not limited thereto. In addition, the extraction of the synchronization signals can be performed with a pulse width-determining sequential logic circuit (digital circuit) as well as the above-described analog circuit.

**[0036]** Another example of the multiple synchronization signal will be described below. Fig. 5 is an explanatory diagram illustrating another example of the multiple synchronization signal S. Fig. 6 is a schematic diagram describing separation of the multiple synchronization signal S into the individual synchronization signals S1, S2, and S3.

[0037] The three synchronization signals S1, S2, and S3 that have different frequencies are multiplexed in the multiple synchronization signal S illustrated in Fig. 5 as is the case with the multiple synchronization signal S illustrated in Fig. 3. In the example of Fig. 5, however, the frequency of the synchronization signal S3 does not have to be 1/integer of the frequency of the synchronization signal S2, unlike in the example illustrated in Fig. 3, insofar as the frequencies of the synchronization signals S2 and S3 are 1/integer of the frequency of the highestfrequency synchronization signal S1 in the relationship of the synchronization signals S1, S2, and S3. Accordingly, the pulse train of the multiple synchronization signal S illustrated in Fig. 5 is a pulse train in which the synchronization signal S1, which has the highest frequency among the synchronization signals included in the mul-

25

40

45

tiple synchronization signal S, is at the head with the other synchronization signals S2 and S3 following the synchronization signal S1 in any order. In other words, the multiple synchronization signal S has a pulse train in which the pulse train of the highest-frequency synchronization signal is used as a reference and the pulses of the synchronization signals S2 and S3 with different frequencies are placed at predetermined positions behind the position of the pulse of the highest-frequency synchronization signal in the pulse train.

[0038] In the case of the multiple synchronization signal S illustrated in Fig. 5, the signal extraction units 61a, 61b, and 61c extract the pulses of the synchronization signals S2 and S3 (indicated by white arrows in the middle and lower parts of Fig. 6) following the synchronization signal S1, based on the time of the highest-frequency synchronization signal S1 (indicated by a solid line in the upper part of Fig. 6) at the head of the pulse train, in the boards 51, 52, and 53 receiving the multiple synchronization signal S transmitted from the synchronous controller 49. In the case of the multiple synchronization signal S illustrated in Fig. 5, a digital circuit constitutes the respective signal extraction units 61a, 61b, and 61c of the boards 51, 52, and 53. A sequential logic circuit appropriately set for extraction of the synchronization signals S2 and S3 is used as an example of the digital circuit. Although the three synchronization signals S1, S2, and S3 with different frequencies are multiplexed in Figs. 5 and 6, the number of multiplexed synchronization signals is not limited thereto. In addition, a combinational logic circuit may be used as the digital circuit for the extraction of the synchronization signals S1, S2, and S3 in the signal extraction units 61a, 61b, and 61c.

**[0039]** Fig. 7 is an explanatory diagram illustrating another example of the multiple synchronization signal S. Fig. 8 is a schematic diagram describing separation of the multiple synchronization signal S into individual synchronization signals.

[0040] The three synchronization signals S1, S2, and S3 that have different frequencies and a synchronization bit are multiplexed in the multiple synchronization signal S illustrated in Fig. 7. The synchronization bit is selected from the frequencies that are common multiples of the frequencies of the synchronization signals S1, S2, and S3. The pulse train of the multiple synchronization signal S illustrated in Fig. 7 is a pulse train in which the synchronization bit as a common multiple of the frequencies of the synchronization signals S1, S2, and S3 included in the multiple synchronization signal S is at the head with the synchronization signals S1, S2, and S3 placed behind in any order. In other words, the multiple synchronization signal S has a pulse train in which each of the respective pulses of the synchronization signals S1, S2, and S3 is placed at a predetermined position with respect to the positions of the pulses of the synchronization bits, which are at predetermined intervals in the pulse train. The synchronization bit is not limited to the least common multiple of the frequencies of the synchronization signals

S1, S2, and S3 insofar as the synchronization bit is a common multiple of the frequencies of the synchronization signals S1, S2, and S3.

[0041] In the case of the multiple synchronization signal S illustrated in Fig. 7, the signal extraction units 61a, 61b, and 61c extract the synchronization signals S1, S2, and S3 (indicated by white arrows in Fig. 8) following the synchronization bit, based on the time of the synchronization bit (indicated by black arrows in Fig. 8) in the pulse train, in the boards 51, 52, and 53 receiving the multiple synchronization signal S transmitted from the synchronous controller 49. In the case of the multiple synchronization signal S illustrated in Fig. 7, a digital circuit constitutes the respective signal extraction units 61a, 61b, and 61c of the boards 51, 52, and 53. A sequential logic circuit appropriately set for extraction of the synchronization signals S1, S2, and S3 is used as an example of the digital circuit. Although the three synchronization signals S1, S2, and S3 with different frequencies are multiplexed in Figs. 7 and 8, the number of multiplexed synchronization signals is not limited thereto.

[0042] The synchronous circuit synchronizing a plurality of functional units of the material testing machine by transmitting and receiving the multiple synchronization signal S described above is used for data input or data output from a measuring device to the control unit 40 and control timing of the load mechanism 30 feedback-controlled by the control unit 40. In addition, the material testing machine according to this embodiment is provided with the graphic board 54, and display update timing at a time when the display section 48 displays results of the calculation of the test force and displacement in the test piece 10 that is executed by the control unit 40 can also be synchronized by the same synchronous circuit. [0043] As described above, in the synchronous circuit according to the invention, no individual communication path reflecting the types of synchronization signals has to be provided between the synchronous controller 49 and each of the boards 51, 52, and 53, and thus wiring of the control device 2 can be simplified. Furthermore, the plurality of synchronization signals can be transmitted through one communication path by multiplexing, and thus an increase and decrease in synchronization signal

can be easily performed without a physical change in

Reference Signs List

circuit design.

#### [0044]

| ) |    |                           |

|---|----|---------------------------|

|   | 1  | Testing machine main body |

|   | 2  | Control device            |

|   | 10 | Test piece                |

|   | 11 | Screw rod                 |

| 5 | 12 | Screw rod                 |

|   | 13 | Crosshead                 |

|   | 14 | Load cell                 |

|   | 15 | Displacement meter        |

10

15

20

25

30

35

40

Table

| 16            | Table                  |

|---------------|------------------------|

| 21            | Upper gripper          |

| 22            | Lower gripper          |

| 30            | Load mechanism         |

| 31            | Servomotor             |

| 32            | Worm reducer           |

| 33            | Worm reducer           |

| 40            | Control unit           |

| 41            | Load amplifier         |

| 42            | Strain amplifier       |

| 43            | AD converter           |

| 44            | AD converter           |

| 45            | Servo amplifier        |

| 46            | DA converter           |

| 47            | Input unit             |

| 48            | Display section        |

| 49            | Synchronous controller |

| 51            | Board                  |

| 52            | Board                  |

| 53            | Board                  |

| 54            | Graphic board          |

| 61a, 61b, 61c | Signal extraction unit |

|               |                        |

Claims

10

1. A synchronous circuit for a material testing machine, the synchronous circuit being provided with a synchronous controller synchronizing operations of a plurality of functional units constituting the material testing machine,

wherein communication paths are provided to be connected to the synchronous controller and the respective functional units,

wherein the synchronous controller transmits a multiple synchronization signal in which a plurality of synchronization signals are multiplexed to the plurality of functional units via one communication path, and

wherein each of the plurality of functional units is provided with extraction means and the extraction means recognize and extract the respective synchronization signals from the multiple synchronization signal.

- 2. The synchronous circuit for a material testing machine according to claim 1,

- wherein the multiple synchronization signal is a signal in which each of the plurality of synchronization signals included in the multiple synchronization signal is a multiplexed signal with a frequency as 1/integer of a closest higher frequency and a pulse width in a pulse train varies with the number of the plurality of synchronization signals included in the multiple synchronization signal.

- 3. The synchronous circuit for a material testing machine according to claim 2,

wherein an analog circuit or a digital circuit constitutes the extraction means.

The synchronous circuit for a material testing machine according to claim 1,

wherein the multiple synchronization signal is a signal in which a signal with a frequency as 1/integer of the synchronization signal with a highest frequency among the plurality of synchronization signals included in the multiple synchronization signal is multiplexed and has a pulse train in which a pulse train of the highest-frequency synchronization signal is used as a reference and pulses of the other synchronization signals are placed at predetermined positions behind a position of a pulse of the highest-frequency synchronization signal in the pulse train.

- 5. The synchronous circuit for a material testing machine according to claim 1, wherein the multiple synchronization signal includes

- a synchronization bit as a common multiple of frequencies of the plurality of synchronization signals included in the multiple synchronization signal and has a pulse train in which respective pulses of the plurality of synchronization signals are placed at predetermined different positions with respect to a position of the synchronization bit in the pulse train.

- The synchronous circuit for a material testing machine according to claim 4, wherein a digital circuit constitutes the extraction means.

- 7. The synchronous circuit for a material testing machine according to claim 5, wherein a digital circuit constitutes the extraction means.

- 8. A material testing machine comprising:

a load mechanism giving a test load to a test

a measuring device detecting a change in physical quantity in the test piece; and

a control device including a calculation control unit calculating a controlled variable of the load mechanism and calculating a physical quantity based on a value detected by the measuring device and a display section displaying a result of the calculation by the calculation control unit, wherein the control device includes

a load mechanism control unit converting the controlled variable calculated by the calculation control unit into an operation signal of a power source of the load mechanism and outputting the operation signal,

a physical quantity detection unit receiving input from the measuring device, and

7

45

50

a display unit for displaying the physical quantity calculated by the calculation control unit in the display section, and wherein the control device includes the synchronous circuit for a material testing machine according to any one of claims 1 to 7.

[FIG. 1]

[FIG. 2]

[FIG. 3]

[FIG. 4]

[FIG. 5]

[FIG. 6]

[FIG. 7]

[FIG. 8]

[FIG. 9]

[FIG. 10]

#### EP 3 421 965 A1

#### International application No. INTERNATIONAL SEARCH REPORT PCT/JP2016/055194 A. CLASSIFICATION OF SUBJECT MATTER G01N3/00(2006.01)i 5 According to International Patent Classification (IPC) or to both national classification and IPC Minimum documentation searched (classification system followed by classification symbols) 10 G01N3/00 Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Jitsuyo Shinan Koho 1922-1996 Jitsuyo Shinan Toroku Koho 1996-2016 15 Kokai Jitsuyo Shinan Koho 1971-2016 Toroku Jitsuyo Shinan Koho Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) 20 C. DOCUMENTS CONSIDERED TO BE RELEVANT Category\* Citation of document, with indication, where appropriate, of the relevant passages Relevant to claim No. JP 51-24284 A (Shimadzu Corp.), 1,5,7-8 27 February 1976 (27.02.1976), Α 2-4,6entire text; all drawings 25 (Family: none) JP 55-5759 B2 (Toyo Kogyo Co., Ltd.), 1,5,7-8Υ Α 08 February 1980 (08.02.1980), 2-4,6 page 1, right column, line 16 to page 3, left column, line 43; fig. 1, 2, 10 to 13 30 & JP 50-33385 A & US 3968477 A column 1, line 15 to column 2, line 52; fig. 1, 35 × Further documents are listed in the continuation of Box C. See patent family annex. 40 Special categories of cited documents: later document published after the international filing date or priority date and not in conflict with the application but cited to understand "A" document defining the general state of the art which is not considered to the principle or theory underlying the invention "E' earlier application or patent but published on or after the international filing document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) document of particular relevance; the claimed invention cannot be 45 considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art "O' document referring to an oral disclosure, use, exhibition or other means document published prior to the international filing date but later than the priority date claimed "P' document member of the same patent family Date of the actual completion of the international search Date of mailing of the international search report 09 May 2016 (09.05.16) 17 May 2016 (17.05.16) 50 Name and mailing address of the ISA/ Authorized officer Japan Patent Office 3-4-3, Kasumigaseki, Chiyoda-ku, Tokyo 100-8915, Japan Telephone No. 55 Form PCT/ISA/210 (second sheet) (January 2015)

#### EP 3 421 965 A1

# International application No. INTERNATIONAL SEARCH REPORT PCT/JP2016/055194 C (Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT 5 Category\* Citation of document, with indication, where appropriate, of the relevant passages Relevant to claim No. Microfilm of the specification and drawings annexed to the request of Japanese Utility Model Application No. 19205/1990 (Laid-open No. 110353/1991) 10 (Shimadzu Corp.), 12 November 1991 (12.11.1991), entire text; all drawings (Family: none) 15 20 25 30 35 40 45 50

Form PCT/ISA/210 (continuation of second sheet) (January 2015)

#### EP 3 421 965 A1

#### REFERENCES CITED IN THE DESCRIPTION

This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.

#### Patent documents cited in the description

• JP 2007218809 A **[0004]**

• JP 5435135 B [0004]