(11)

EP 3 503 132 A1

(12)

## EUROPEAN PATENT APPLICATION

(43) Date of publication:

26.06.2019 Bulletin 2019/26

(51) Int Cl.:

H01F 21/12 <sup>(2006.01)</sup>

(21) Application number: 18187744.0

(22) Date of filing: 07.08.2018

(84) Designated Contracting States:

**AL AT BE BG CH CY CZ DE DK EE ES FI FR GB

GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO

PL PT RO RS SE SI SK SM TR**

Designated Extension States:

**BA ME**

Designated Validation States:

**KH MA MD TN**

(30) Priority: 20.12.2017 US 201715847960

(71) Applicant: **National Chung Shan Institute of

Science and

Technology

Taoyuan City 325 (TW)**

(72) Inventors:

• **LIANG, Chia-Jen**

**Kaohsiung City 807 (TW)**

• **KUAN, Yen-Cheng**

**Kaohsiung City 802 (TW)**

• **CHIANG, Ching-Wen**

**Chiayi City 600 (TW)**

• **YU, Chien-Te**

**Taoyuan City 320 (TW)**

(74) Representative: **Perani & Partners S.p.A.**

**Piazza Armando Diaz, 7**

**20123 Milano (IT)**

## (54) VARIABLE INDUCTOR AND INTEGRATED CIRCUIT USING THE VARIABLE INDUCTOR

(57) A variable inductor comprises a primary conductor, a first secondary conductor and one or more switch. The primary conductor has a first node and a second node, wherein the first node is used to connect a first external component and the second node is used to connect a second external component. The first secondary conductor magnetically couples to the primary con-

ductor. The one or more switch has two sides connected to the first secondary conductor, respectively. The first secondary conductor is formed a single-loop structure with two or more changeable current paths which are operated by the states of the one or more switch. An integrated circuit using the variable inductor is also introduced.

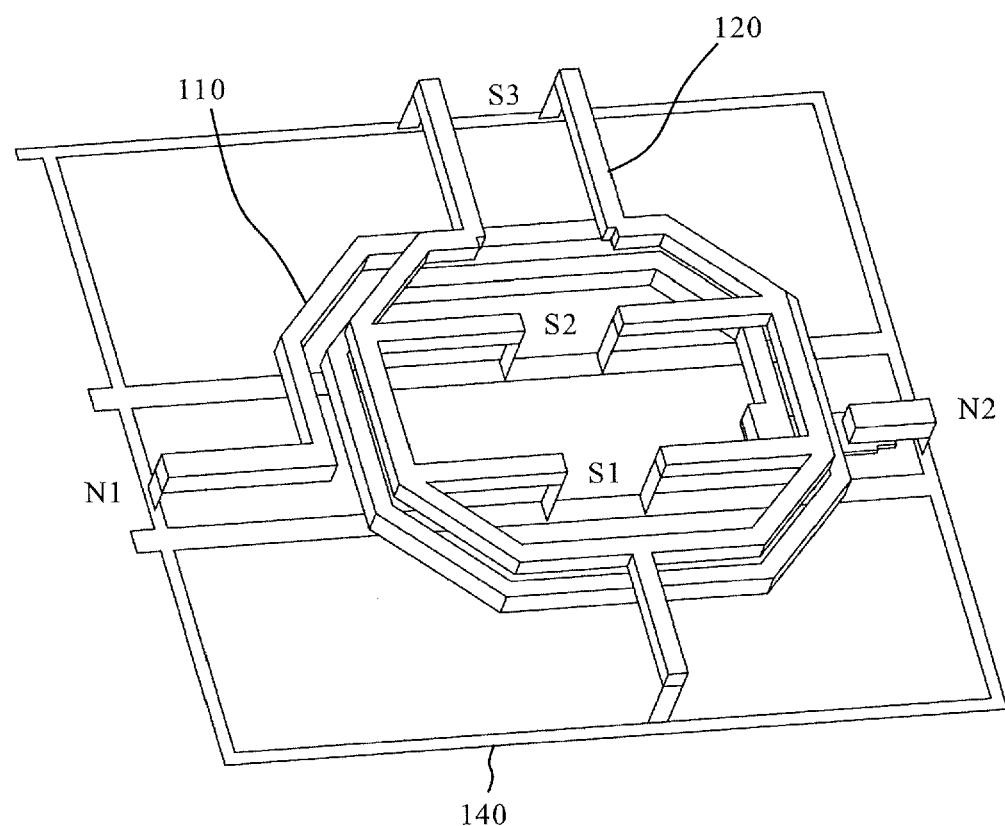

FIG. 3

**Description****FIELD OF THE INVENTION**

**[0001]** The present disclosure relates to a variable inductor and, more particularly, to a variable inductor which can be formed on an integrated circuit.

**BACKGROUND OF THE INVENTION**

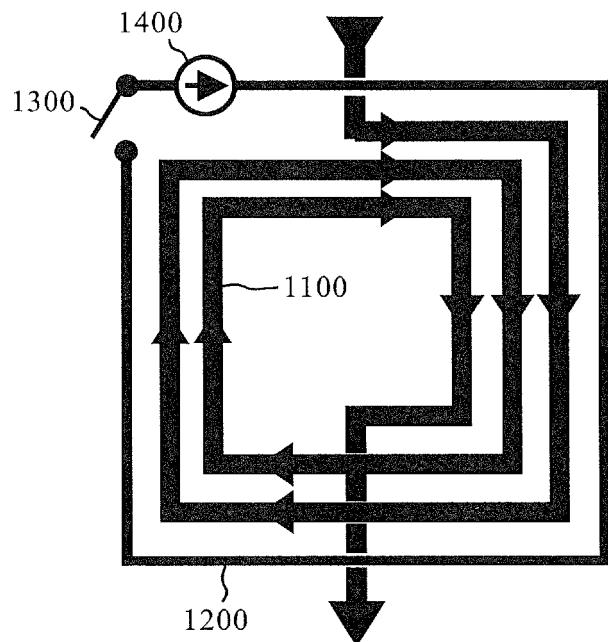

**[0002]** Referring to FIG. 1A and FIG. 1B, FIG. 1A and FIG. 1B shows a conventional variable inductor. The conventional variable inductor 1000 has a primary conductor 1100 and a secondary conductor 1200, a switch 1300 and a current source 1400. The secondary conductor 1200 forms a loop on the outside of the primary conductor 1100. The switch 1300 couples in series with the secondary conductor 1200 and is turned on or off to make the loop close or open. The inductance of the conventional variable inductor 1000 is varied by closing and opening the loop with the switch 1300. The current source 1400 is also coupled in series with the secondary conductor 1200 and used to control the current flow in the secondary conductor 1200 to either increase or decrease the inductance.

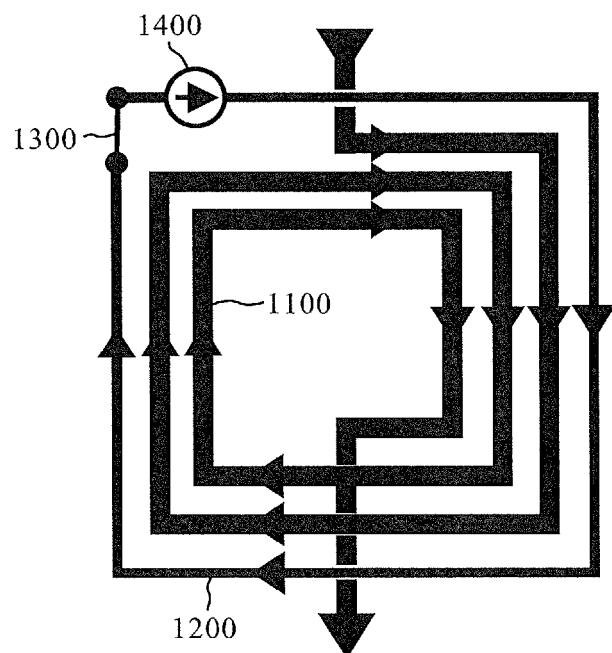

**[0003]** Referring to FIG. 2, FIG. 2 shows another one conventional variable inductor. The conventional variable inductor 2000 has a first conductor 2100, a second conductor 2200, a first switch 2300, a second switch 2400 and a third switch 2500. The first switch 2300, the second switch 2400 and the third switch 2500 are disposed on three current paths connected between the first conductor 2100 and the second conductor 2200, respectively. The inductance of the conventional variable inductor 2000 is varied by closing and opening the first switch 2300, the second switch 2400 and the third switch 2500.

**[0004]** The conventional variable inductor 1000 may have a limitedly adjustable inductance range and an insufficient inductance resolution. The conventional variable inductor 2000 may have a lower Q value, durability issues and bias concern.

**[0005]** Accordingly, it is imperative to provide a variable inductor and an integrated circuit using the variable inductor which can overcome the aforesaid drawbacks of the conventional variable inductors.

**SUMMARY OF THE INVENTION**

**[0006]** In view of the aforesaid drawbacks of the prior art, it is an objective of the present disclosure to provide a variable inductor and an integrated circuit using the variable inductor which can have a wider adjustable inductance range, a better inductance resolution, a higher Q value, fewer durability issues and no bias concern.

**[0007]** In order to achieve the above and other objectives, the present disclosure provides a variable inductor which comprises a primary conductor, a first secondary conductor and a first switch. The primary conductor has

a first node and a second node, wherein the first node being used to connect a first external component and the second node being used to connect a second external component. The first secondary conductor magnetically couples to the primary conductor. The first switch has two sides connected to the first secondary conductor, respectively. The first secondary conductor is formed a single-loop structure with two changeable current paths which are operated by the states of the first switch.

**[0008]** Regarding the variable inductor, the variable inductor further comprises a second switch having two sides connected to the first secondary conductor, respectively, and the first secondary conductor is formed a single-loop structure with four changeable current paths which are operated by the states of the first and second switches.

**[0009]** Regarding the variable inductor, the variable inductor further comprises a third switch having two sides connected to the first secondary conductor, respectively, and the first secondary conductor is formed a single-loop structure with eight changeable current paths which are operated by the states of the first, second and third switches.

**[0010]** Regarding the variable inductor, the variable inductor further comprises a second secondary conductor magnetically coupling to the primary conductor and a fourth switch having two sides connected to the second secondary conductor, respectively. The second secondary conductor is formed a single-loop structure with two changeable current paths which are operated by the states of the fourth switch.

**[0011]** Regarding the variable inductor, the variable inductor further comprises a fifth switch having two sides connected to the second secondary conductor, respectively, and the second secondary conductor is formed a single-loop structure with four changeable current paths which are operated by the states of the fourth and fifth switches.

**[0012]** Regarding the variable inductor, the variable inductor further comprises a sixth switch having two sides connected to the second secondary conductor, respectively, and the second secondary conductor is formed a single-loop structure with eight changeable current paths which are operated by the states of the fourth, fifth and sixth switches.

**[0013]** Regarding the variable inductor, the first secondary conductor is disposed on one side of the primary conductor and the second secondary conductor is disposed on another side of the primary conductor.

**[0014]** Regarding the variable inductor, the first node is on one end of the primary conductor and the second node is on another end of the primary conductor.

**[0015]** Regarding the variable inductor, the variable inductor is integrated in a radio frequency integrated circuit.

**[0016]** Regarding the variable inductor, the first switch is implemented by a CMOS (complementary metal oxide semiconductor) or PCB (printed circuit board) lump component.

**[0017]** In order to achieve the above and other objectives, the present disclosure provides an integrated circuit. The integrated circuit comprises a first component, a second component and a variable inductor. The variable inductor comprises a primary conductor, a first secondary conductor and a first switch. The primary conductor has a first node and a second node. The first node is used to connect a first external component and the second node is used to connect a second external component. The first secondary conductor magnetically couples to the primary conductor. The first switch has two sides connected to the first secondary conductor, respectively. The first secondary conductor is formed a single-loop structure with two changeable current paths which are operated by the states of the first switch.

**[0018]** Regarding the integrated circuit, the variable inductor further comprises a second switch having two sides connected to the first secondary conductor, respectively, and the first secondary conductor is formed a single-loop structure with four changeable current paths which are operated by the states of the first and second switches.

**[0019]** Regarding the integrated circuit, the variable inductor further comprises a third switch having two sides connected to the first secondary conductor, respectively, and the first secondary conductor is formed a single-loop structure with eight changeable current paths which are operated by the states of the first, second and third switches.

**[0020]** Regarding the integrated circuit, the variable inductor further comprises a second secondary conductor magnetically coupling to the primary conductor and a fourth switch having two sides connected to the second secondary conductor, respectively. The second secondary conductor is formed a single-loop structure with two changeable current paths which are operated by the states of the fourth switch.

**[0021]** Regarding the integrated circuit, the variable inductor further comprises a fifth switch having two sides connected to the second secondary conductor, respectively, and the second secondary conductor is formed a single-loop structure with four changeable current paths which are operated by the states of the fourth and fifth switches.

**[0022]** Regarding the integrated circuit, the variable inductor further comprises a sixth switch having two sides connected to the second secondary conductor, respectively, and the second secondary conductor is formed a single-loop structure with eight changeable current paths which are operated by the states of the fourth, fifth and sixth switches.

**[0023]** Regarding the integrated circuit, the first secondary conductor is disposed on one side of the primary conductor and the second secondary conductor is disposed on another side of the primary conductor.

**[0024]** Regarding the integrated circuit, the first node is on one end of the primary conductor and the second node is on another end of the primary conductor.

**[0025]** Regarding the integrated circuit, the integrated circuit is used for radio frequency.

**[0026]** Regarding the integrated circuit, the first switch is implemented by a CMOS (complementary metal oxide semiconductor).

**[0027]** In conclusion, give the aforesaid variable inductor and integrated circuit, the present disclosure feature a wider adjustable inductance range, a better inductance resolution, a higher Q value ,fewer durability issues and no bias concern.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0028]** Objectives, features, and advantages of the present disclosure are hereunder illustrated with specific embodiments in conjunction with the accompanying drawings.

FIG. 1A shows a schematic diagram of a conventional variable inductor;

FIG. 1B shows a schematic diagram of a conventional variable inductor;

FIG. 2 shows a schematic diagram of another one conventional variable inductor;

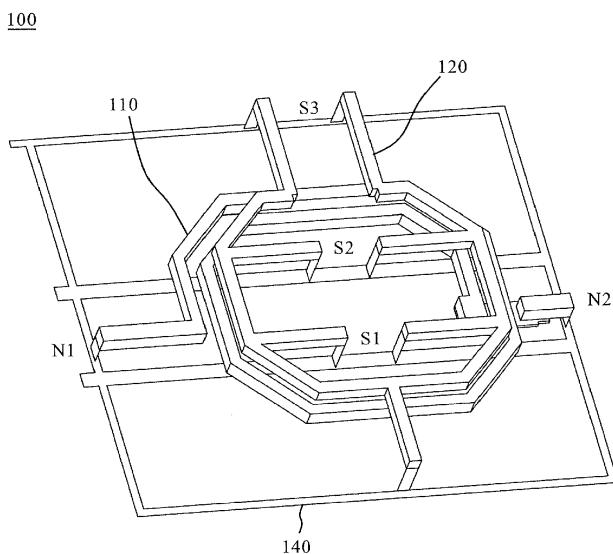

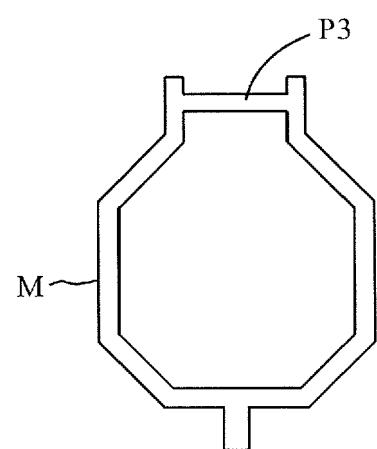

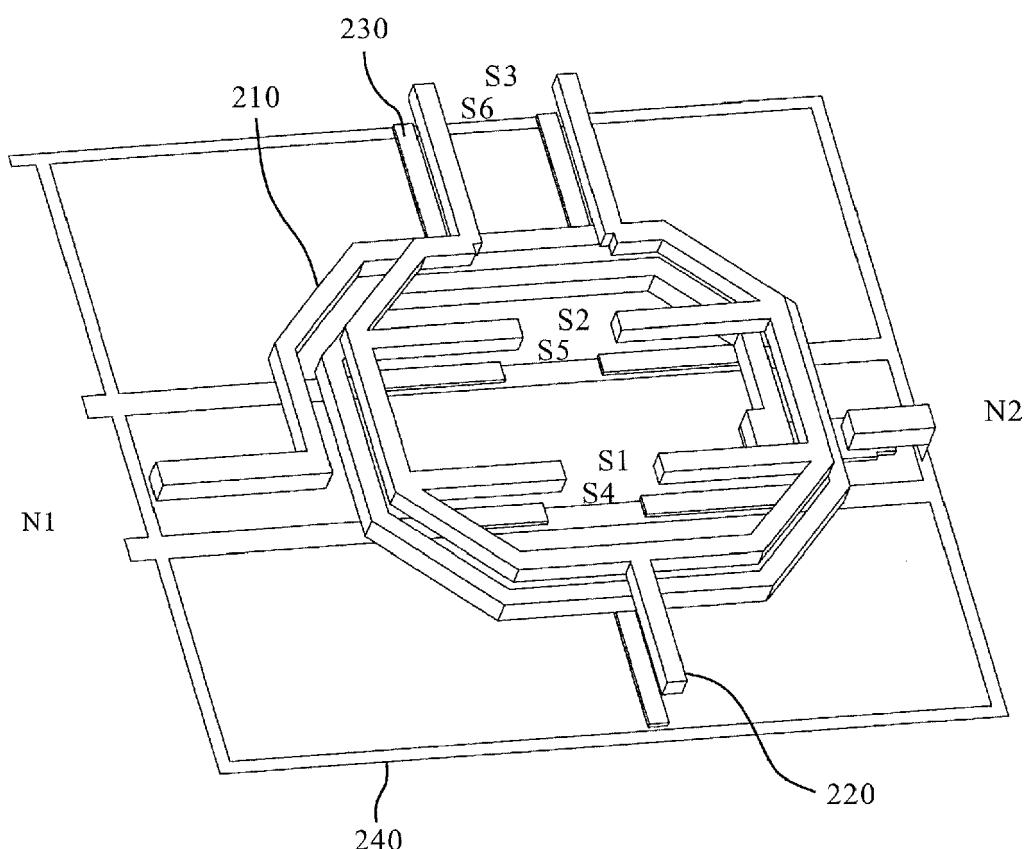

FIG. 3 is schematic diagrams of a variable inductor according to an embodiment of the present disclosure;

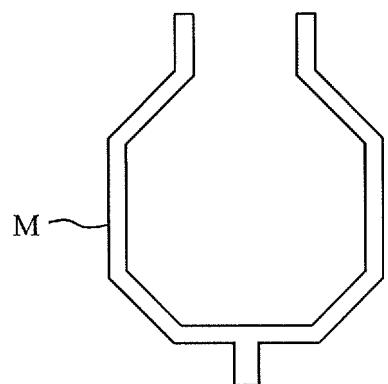

FIG. 4A is a plan view of different current paths of a first secondary conductor of the variable inductor according to an embodiment of the present disclosure;

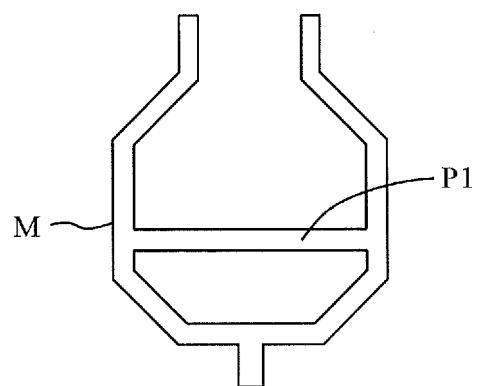

FIG. 4B is a plan view of different current paths of a first secondary conductor of the variable inductor according to an embodiment of the present disclosure;

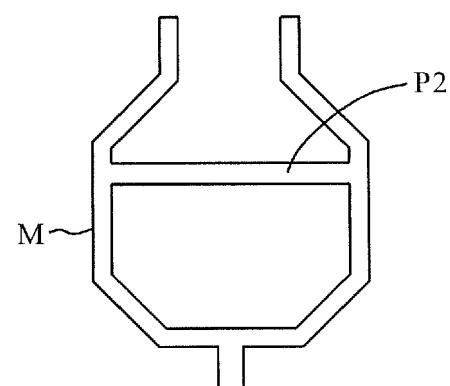

FIG. 4C is a plan view of different current paths of a first secondary conductor of the variable inductor according to an embodiment of the present disclosure;

FIG. 4D is a plan view of different current paths of a first secondary conductor of the variable inductor according to an embodiment of the present disclosure;

FIG. 4E is a plan view of different current paths of a first secondary conductor of the variable inductor according to an embodiment of the present disclosure;

FIG. 4F is a plan view of different current paths of a first secondary conductor of the variable inductor according to an embodiment of the present disclosure;

FIG. 4G is a plan view of different current paths of a first secondary conductor of the variable inductor according to an embodiment of the present disclosure;

FIG. 4H is a plan view of different current paths of a first secondary conductor of the variable inductor according to an embodiment of the present disclosure;

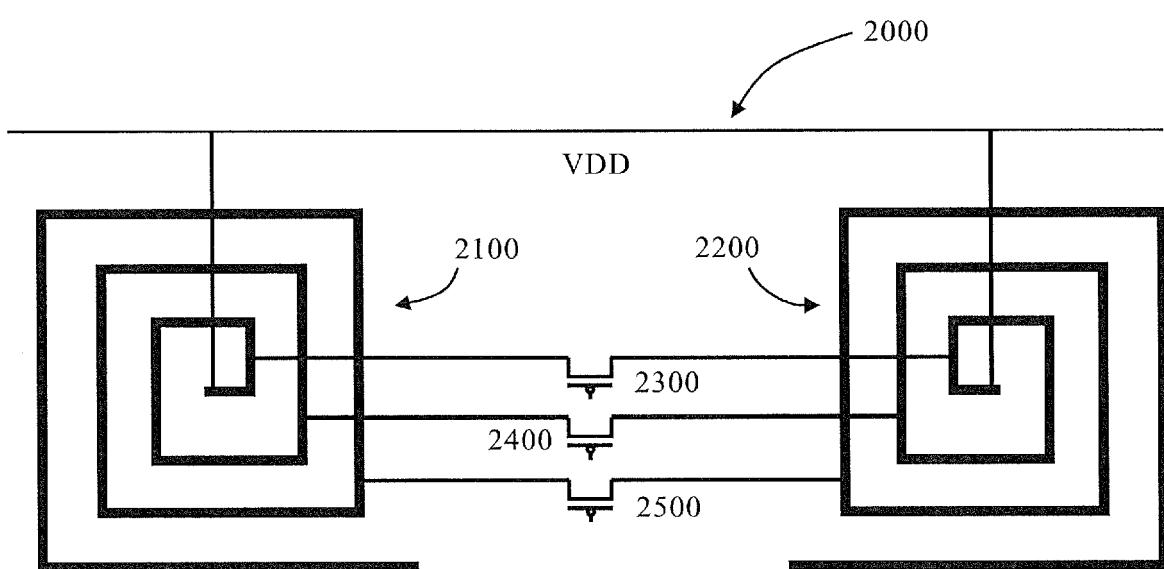

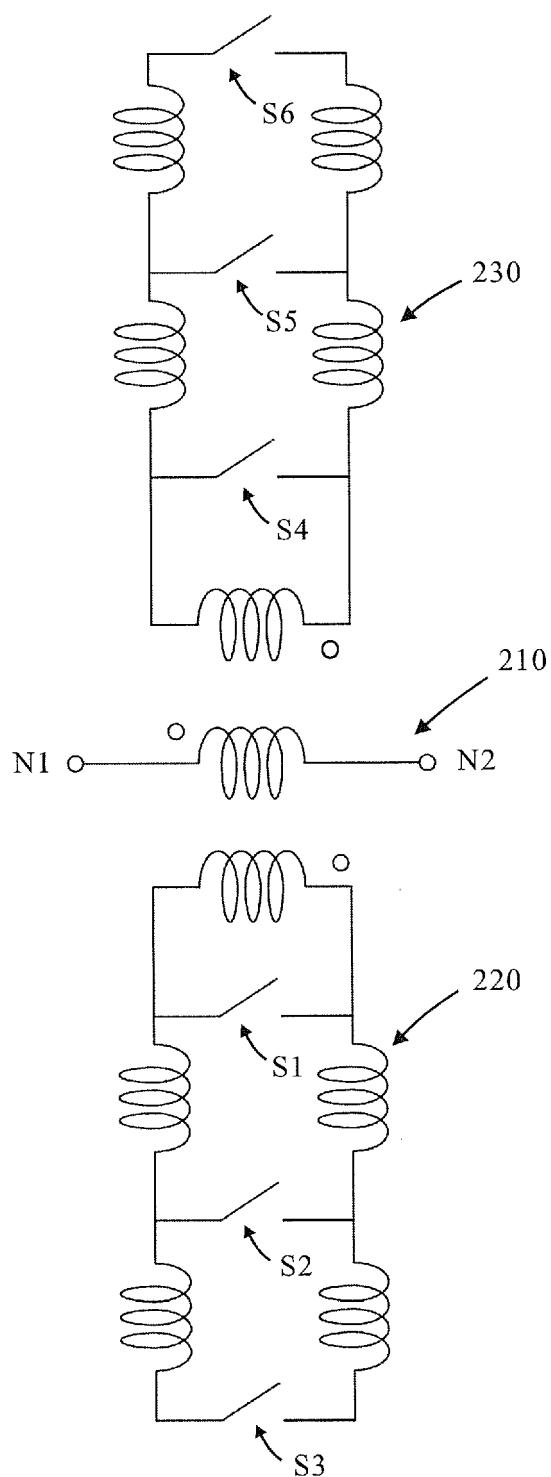

FIG. 5 shows an illustratively equivalent circuit of the variable inductor of FIG. 3;

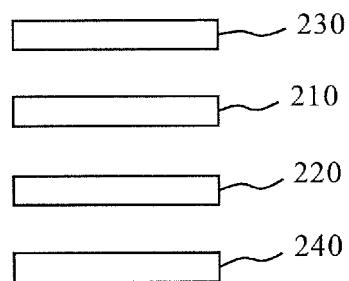

FIG. 6A shows two different arrangements of a variable inductor according to another two embodiments of the present disclosure;

FIG. 6B shows two different arrangements of a variable inductor according to another two embodi-

ments of the present disclosure;

FIG. 7 is schematic diagrams of a variable inductor according to another one embodiment of the present disclosure;

FIG. 8 shows an illustratively equivalent circuit of the variable inductor of FIG. 7;

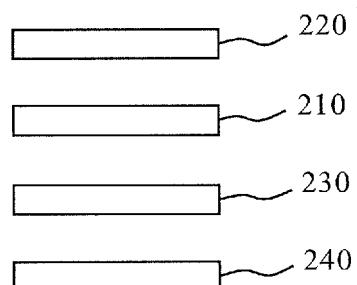

FIG. 9A shows two different arrangements of a variable inductor according to two embodiments of the present disclosure;

FIG. 9B shows two different arrangements of a variable inductor according to two embodiments of the present disclosure; and

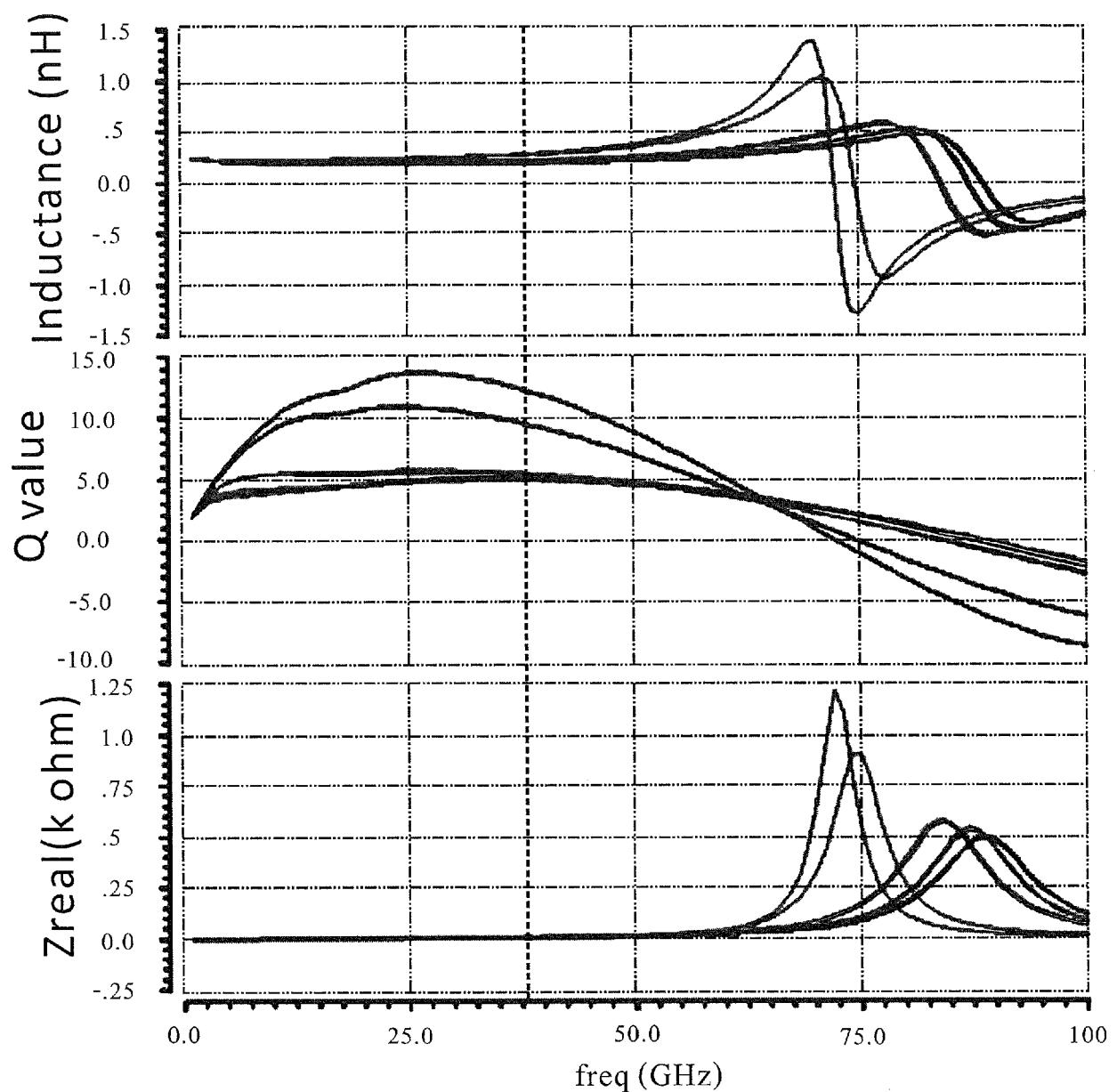

FIG. 10 shows a simulation result of FIG. 3.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

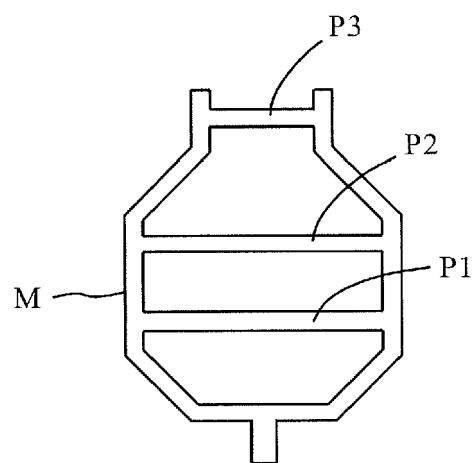

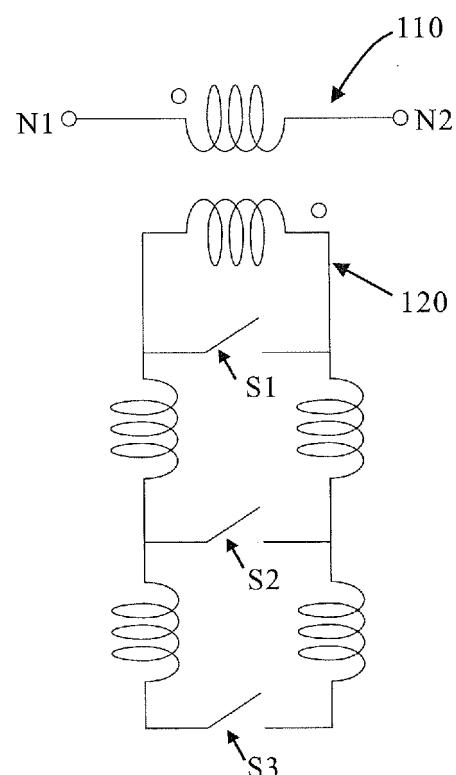

**[0029]** Referring to FIG. 3, FIG. 3 is schematic diagrams of a variable inductor according to an embodiment of the present disclosure. The variable inductor 100 has a primary conductor 110, a first secondary conductor 120, a first switch S1, a second switch S2 and a third switch S3, wherein the primary conductor 110 and the first secondary conductor 120 magnetically couple to each other to form a transformer structure. By controlling the first through third switches S1 through S3, the equivalent inductance of the first secondary conductor 120 and coupling factor are changed due to magnetic coupling theory of the transformer structure. The inductance value of the primary conductor 110 is changed as the equivalent inductance of the first secondary conductor 120 and coupling factor are changed. Therefore, the primary conductor 110, the first secondary conductor 120 and the first through third switches S1 through S3 can achieve the object of variable inductance.

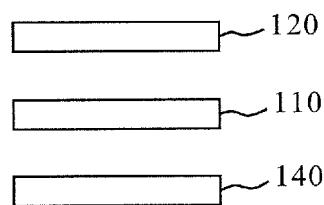

**[0030]** In FIG. 3, the first secondary conductor 120 is disposed on the top of the primary conductor 110. The first switch S1, the second switch S2 and the third switch S3 can be implemented on a substrate or printed circuit board 140. The substrate or printed circuit board 140 can be disposed under the bottom of the primary conductor 110.

**[0031]** The first switch S1 has two sides connected to the first secondary conductor 120, respectively. The second switch S2 has two sides connected to the first secondary conductor 120, respectively. The third switch S3 has two sides connected to the first secondary conductor 120, respectively. The first switch S1, the second switch S2 and the third switch S3 are formed on current paths P1-P3, respectively.

**[0032]** The first secondary conductor 120 is formed a single-loop structure. The current paths P1-P3 are formed as three different bypasses of the single-loop structure. Therefore, if the state of anyone of the first switch S1, the second switch S2 and the third switch S3 are changed, then the current paths of the first secondary conductor 120 is changed.

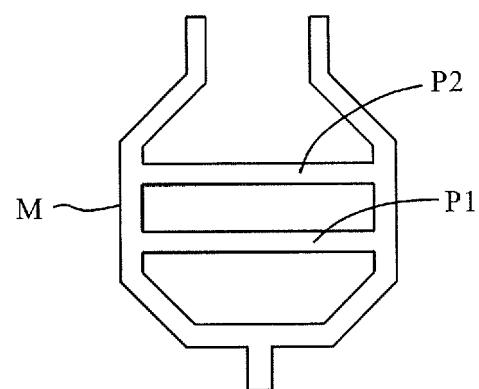

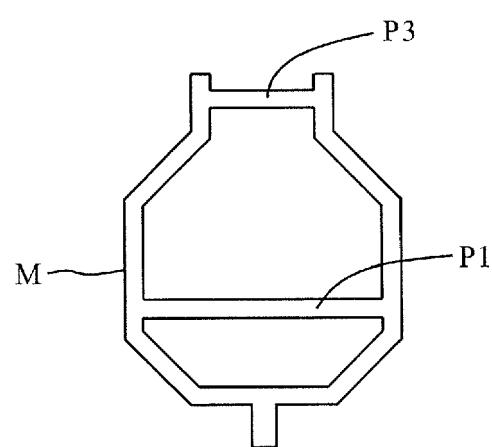

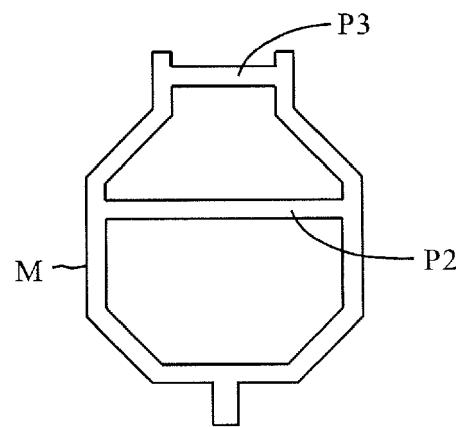

**[0033]** FIGS. 4A through 4H show eight different cur-

rent paths of the first secondary conductor 120. In FIG. 4A, all of the first switch S1, the second switch S2 and the third switch S3 operated to be open. The first secondary conductor 120 is formed a single-loop structure with a main branch M.

**[0034]** In FIG. 4B, only the first switch S1 is operated to be closed. The first secondary conductor 120 is formed a single-loop structure with the main branch M and the current path P1.

**[0035]** In FIG. 4C, only the second switch S2 is operated to be closed. The first secondary conductor 120 is formed a single-loop structure with the main branch M and the current path P2.

**[0036]** In FIG. 4D, only the third switch S3 is operated to be closed. The first secondary conductor 120 is formed a single-loop structure with the main branch M and the current path P3.

**[0037]** In FIG. 4E, the first switch S1 and the second switch S2 are operated to be closed. The first secondary conductor 120 is formed a single-loop structure with the main branch M, the current path P1 and the current path P2.

**[0038]** In FIG. 4F, the first switch S1 and the third switch S3 are operated to be closed. The first secondary conductor 120 is formed a single-loop structure with the main branch M, the current path P1 and the current path P3.

**[0039]** In FIG. 4G, the second switch S2 and the third switch S3 are operated to be closed. The first secondary conductor 120 is formed a single-loop structure with the main branch M, the current path P2 and the current path P3.

**[0040]** In FIG. 4H, all of the first switch S1, the second switch S2 and the third switch S3 operated to be closed. The first secondary conductor 120 is formed a single-loop structure with the main branch M, the current path P1, the current path P2 and the current path P3.

**[0041]** The first secondary conductor 120 is formed a single-loop structure with eight changeable current paths which are determined by the state of the first switch S1, the second switch S2 and third switch S3. The inductance of the variable inductor 100 is varied by closing and opening the first switch S1, the second switch S2 and the third switch S3. Therefore, in this embodiment, the variable inductor 100 has an adjustable inductance range which

includes eight different inductance values corresponding to eight different current paths (as shown as FIG. 4A through 4H), respectively. FIG. 5 is an illustratively equivalent circuit of the variable inductor of FIG. 3. The inductance from the first node N1 through the second node N2 of the primary conductor 110 is changed according to the state of the switch S1 through S3 of the first secondary conductor 120.

**[0042]** FIGS. 6A and 6B show two different arrangements of a variable inductor according to two embodiments of the present disclosure. In FIG. 6A, the first secondary conductor 120 is disposed on the top of the primary conductor 110, and the substrate or printed circuit board 140 is disposed under the bottom of the primary

conductor 110. In FIG. 6B, the first secondary conductor 120 is disposed under the bottom of the primary conductor 110, and the substrate or printed circuit board 140 is disposed under the bottom of first secondary conductor 120.

**[0043]** In other one embodiment, the third switch S3 can be eliminated. In that embodiment, the first secondary conductor 120 is formed a single-loop structure with four changeable current paths which are operated by the states of the first switch S1 and the second switch S2.

**[0044]** In the other one embodiment, both the second switch S2 and the third switch S3 can be eliminated. In that embodiment, the first secondary conductor 120 is formed a single-loop structure with two changeable current paths which are determined by the state of the first switch S1.

**[0045]** In still the other one embodiment, the number of the switches can be  $N_1$  and the first secondary conductor 120 is formed a single-loop structure with  $M_1$  changeable current paths which are determined by the state of the  $N_1$  switches, wherein  $N_1$  is more than 3 and  $M_1$  is more than 8.

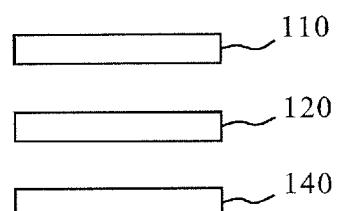

**[0046]** Referring to FIG. 7, FIG. 7 is schematic diagrams of a variable inductor according to another one embodiment of the present disclosure. The variable inductor 200 has a primary conductor 210, a first secondary conductor 220, a second secondary conductor 230, a first switch S1, a second switch S2, a third switch S3, a fourth switch S4, a fifth switch S5 and a sixth switch S6.

**[0047]** In FIG. 7, the second secondary conductor 230 is disposed under the bottom of the primary conductor 210. The fourth switch S4, the fifth switch S5 and the sixth switch S6 can be implemented on a substrate or printed circuit board 240. The printed circuit board 240 can be disposed under the bottom of the primary conductor 210.

**[0048]** The fourth switch S4 has two sides connected to the second secondary conductor 230, respectively. The fifth switch S5 has two sides connected to the second secondary conductor 230, respectively. The sixth switch S6 has two sides connected to the second secondary conductor 230, respectively. The fourth switch S4, the fifth switch S5 and the sixth switch S6 are formed on another three current paths, respectively.

**[0049]** The second secondary conductor 230 is formed a single-loop structure. The three current paths are formed as three different bypasses of the single-loop structure. Therefore, if the state of anyone of the fourth switch S4, the fifth switch S5 and the sixth switch S6 are changed, then the current paths of the second secondary conductor is changed.

**[0050]** The structure of the first secondary conductor 220 and the second secondary conductor 230 are roughly the same as the structure of the first secondary conductor 120. Therefore, the detailed description of the first secondary conductor 220 and the second secondary conductor 230 is omitted.

**[0051]** The first secondary conductor 220 is formed a

single-loop structure with eight changeable current paths which are determined by the state of the first switch S1, the second switch S2 and third switch S3. The second secondary conductor 230 is also formed a single-loop structure with eight changeable current paths which are determined by the state of the fourth switch S4, the fifth switch S5 and the sixth switch S6. The inductance of the variable inductor 200 is varied by closing and opening the first switch S1, the second switch S2, the third switch

S3, the fourth switch S4, the fifth switch S5 and the sixth switch S6. Therefore, in this embodiment, the variable inductor 200 has an adjustable inductance range which includes 64 different inductance values corresponding to 8\*8 different current paths, respectively. FIG. 8 is an illustratively equivalent circuit of the variable inductor of FIG. 7.

**[0052]** FIGS. 9A and 9B show two different arrangements of a variable inductor according to two embodiments of the present disclosure. In FIG. 9A, the second

secondary conductor 230 is disposed on the top of the primary conductor 210, the first secondary conductor 220 is disposed under the bottom of the primary conductor 210, and the printed circuit board 240 is disposed under the bottom of the first secondary conductor 220. In FIG. 9B, the first secondary conductor 220 is disposed on the top of the primary conductor 210, the second secondary conductor 230 is disposed under the bottom of the primary conductor 210, and the printed circuit board 240 is disposed under the bottom of the second secondary conductor 230.

**[0053]** In other one embodiment, the sixth switch S6 can be eliminated. In that embodiment, the second secondary conductor 230 is formed a single-loop structure with four changeable current paths which are operated by the states of the fourth switch S4 and the fifth switch S5.

**[0054]** In the other one embodiment, both the fifth switch S5 and the sixth switch S6 can be eliminated. In that embodiment, the second secondary conductor 230 is formed a single-loop structure with two changeable current paths which are determined by the state of the fourth switch S4.

**[0055]** In still the other one embodiment, the number of the switches can be  $N_2$  and the second secondary conductor 230 is formed a single-loop structure with  $M_2$  changeable current paths which are determined by the state of the  $N_2$  switches, wherein  $N_2$  is more than 3 and  $M_2$  is more than 8.

**[0056]** The variable inductor is suitable for being integrated in an integrated circuit, for example, a radio frequency integrated circuit. A first node N1 of the variable inductor can be disposed on one end of the primary conductor of the variable inductor and a second node N2 of the variable inductor can be disposed on another end of the primary conductor of the variable inductor. The first node N1 can connect to a first external component, for example, a first component of the integrated circuit. The second node N2 can connect to a second external com-

ponent, for example, a second component of the integrated circuit.

**[0057]** Referring to FIG. 10, FIG. 10 shows a simulation result of FIG. 3. In FIG. 10, three switches are implemented by 28nm CMOS (complementary metal oxide semiconductor). The adjustable inductance range is 187pH-277pH.

**[0058]** In conclusion, the aforesaid variable inductor and integrated circuit, the present disclosure feature a wider adjustable inductance range, a better inductance resolution, a higher Q value, fewer durability issues or no bias concern.

## Claims

1. A variable inductor (100, 200) being used to connect a first external component and a second external component, the variable inductor (100, 200) comprising:

a primary conductor (110, 210) having a first node (N1) and a second node (N2), the first node (M1) being used to connect the first external component, the second node (N2) being used to connect the second external component; a first secondary conductor (120, 220), magnetically coupling to the primary conductor (110, 210); a first switch (S1) having two sides connected to the first secondary conductor (110, 220), respectively; wherein the first secondary conductor (110, 210) is formed a single-loop structure with two changeable current paths (M, "M and P1") which are operated by the states of the first switch (S1).

2. The variable inductor (100, 200) of claim 1 further comprises a second switch (S2) having two sides connected to the first secondary conductor (120, 220), respectively, and the first secondary conductor (120, 220) is formed a single-loop structure with four changeable current paths (M, "M and P1", "M and P2", "M, P1 and P2") which are operated by the states of the first and second switches (S1, S2).

3. The variable inductor (100, 200) of claim 2 further comprises a third switch (S3) having two sides connected to the first secondary conductor (120, 220), respectively, and the first secondary conductor (120, 220) is formed a single-loop structure with eight changeable current paths (M, "M and P1", "M and P2", "M and P3", "M, P1 and P2", "M, P1 and P3", "M, P2 and P3", "M, P1, P2 and P3") which are operated by the states of the first, second and third switches (S1, S2, S3).

4. The variable inductor (100, 200) of claim 1, wherein

the first node (N1) is disposed on one end of the primary conductor (110, 210) and the second node (N2) is disposed on another end of the primary conductor (110, 210).

5. The variable inductor (100, 200) of claim 1, wherein the variable inductor (100, 200) is integrated in a radio frequency integrated circuit.

10 6. The variable inductor (100, 200) of claim 5, wherein the first switch (S1) is implemented by a CMOS (complementary metal oxide semiconductor) or PCB (printed circuit board) lump component.

15 7. An integrated circuit comprising:

a first component;

a second component; and

a variable inductor (100, 200) connected the first component and the second component, wherein the variable inductor (100, 200) comprises a primary conductor (110, 210), a first secondary conductor (120, 220) and a first switch (S1), the primary conductor (110, 210) has a first node N1 and a second node N2, the first node N1 connects to the first component, the second node (N2) connects to the second component, the first secondary conductor (120, 220) magnetically couples to the primary conductor (110, 210), the first switch (S1) has two sides connected to the first secondary conductor (110, 220), respectively, and the first secondary conductor (110, 220) is formed a single-loop structure with two changeable current paths (M, "M and P1") which are operated by the states of the first switch (S1).

8. The integrated circuit of claim 7, wherein the variable inductor (100, 200) further comprises a second switch (S2) having two sides connected to the first secondary conductor (120, 220), respectively, and the first secondary conductor (120, 220) is formed a single-loop structure with four changeable current paths (M, "M and P1", "M and P2", "M, P1 and P2") which are operated by the states of the first and second switches (S1, S2).

9. The integrated circuit of claim 8, wherein the variable inductor (100, 200) further comprises a third switch (S3) having two sides connected to the first secondary conductor (120, 220), respectively, and the first secondary conductor (120, 220) is formed a single-loop structure with eight changeable current paths (M, "M and P1", "M and P2", "M and P3", "M, P1 and P2", "M, P1 and P3", "M, P2 and P3", "M, P1, P2 and P3") which are operated by the states of the first, second and third switches (S1, S2, S3).

10. The integrated circuit of claim 7, wherein the first node (N1) is disposed on one end of the primary conductor (110, 210) and the second node (N2) is disposed on another end of the primary conductor (110, 210). 5

11. The integrated circuit of claim 7, wherein the integrated circuit is used for radio frequency.

12. The integrated circuit of claim 7, wherein the first switch (S1) is implemented by a CMOS (complementary metal oxide semiconductor). 10

15

20

25

30

35

40

45

50

55

1000

FIG. 1A (related art)

1000

FIG. 1B (related art)

FIG. 2 (related art)

100

FIG. 3

FIG. 4A

FIG. 4B

FIG. 4C

FIG. 4D

FIG. 4E

FIG. 4F

FIG. 4G

FIG. 4H

FIG. 5

FIG. 6A

FIG. 6B

200

FIG. 7

FIG. 8

FIG. 9A

FIG. 9B

FIG. 10

## EUROPEAN SEARCH REPORT

Application Number

EP 18 18 7744

5

| DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |                                         |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------|

| Category                            | Citation of document with indication, where appropriate, of relevant passages                                                                                                                                                                                                                                                                                                                                                                      | Relevant to claim                                   | CLASSIFICATION OF THE APPLICATION (IPC) |

| X                                   | CN 104 637 920 B (UNIV WENZHOU)<br>15 August 2017 (2017-08-15)<br>* abstract *<br>* paragraphs [0003], [0006], [0026] - [0030] *<br>-----<br>X US 2012/223796 A1 (HUANG KAI-YI [TW] ET AL) 6 September 2012 (2012-09-06)<br>* abstract *<br>* paragraphs [0004], [0017], [0019], [0020], [0023], [0024] *<br>-----<br>A CN 105 244 345 A (UNIV WENZHOU)<br>13 January 2016 (2016-01-13)<br>* abstract *<br>* paragraphs [0021] - [0023] *<br>----- | 1-12<br>1,4-7,<br>10-12<br>1-12                     | INV.<br>H01F21/12                       |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     | TECHNICAL FIELDS<br>SEARCHED (IPC)      |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     | H01F                                    |

| 1                                   | The present search report has been drawn up for all claims                                                                                                                                                                                                                                                                                                                                                                                         |                                                     |                                         |

| 50                                  | Place of search<br>Munich                                                                                                                                                                                                                                                                                                                                                                                                                          | Date of completion of the search<br>10 January 2019 | Examiner<br>Gols, Jan                   |

| 55                                  | CATEGORY OF CITED DOCUMENTS<br>X : particularly relevant if taken alone<br>Y : particularly relevant if combined with another document of the same category<br>A : technological background<br>O : non-written disclosure<br>P : intermediate document                                                                                                                                                                                             |                                                     |                                         |

|                                     | T : theory or principle underlying the invention<br>E : earlier patent document, but published on, or after the filing date<br>D : document cited in the application<br>L : document cited for other reasons<br>.....<br>& : member of the same patent family, corresponding document                                                                                                                                                              |                                                     |                                         |

**ANNEX TO THE EUROPEAN SEARCH REPORT

ON EUROPEAN PATENT APPLICATION NO.**

EP 18 18 7744

5 This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

10-01-2019

| 10 | Patent document cited in search report | Publication date | Patent family member(s) |               | Publication date |

|----|----------------------------------------|------------------|-------------------------|---------------|------------------|

|    | CN 104637920 B                         | 15-08-2017       | NONE                    |               |                  |

| 15 | US 2012223796 A1                       | 06-09-2012       | CN                      | 102655139 A   | 05-09-2012       |

|    |                                        |                  | TW                      | 201237895 A   | 16-09-2012       |

|    |                                        |                  | US                      | 2012223796 A1 | 06-09-2012       |

| 20 | CN 105244345 A                         | 13-01-2016       | NONE                    |               |                  |

| 25 |                                        |                  |                         |               |                  |

| 30 |                                        |                  |                         |               |                  |

| 35 |                                        |                  |                         |               |                  |

| 40 |                                        |                  |                         |               |                  |

| 45 |                                        |                  |                         |               |                  |

| 50 |                                        |                  |                         |               |                  |

| 55 |                                        |                  |                         |               |                  |

EPO FORM P0459

For more details about this annex : see Official Journal of the European Patent Office, No. 12/82