## (11) **EP 3 531 348 A8**

## (12) CORRECTED EUROPEAN PATENT APPLICATION

(15) Correction information:

Corrected version no 1 (W1 A1) Corrections, see

Bibliography INID code(s) 54

(48) Corrigendum issued on:

06.05.2020 Bulletin 2020/19

(43) Date of publication:

28.08.2019 Bulletin 2019/35

(21) Application number: 19159082.7

(22) Date of filing: 25.02.2019

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

Designated Extension States:

**BA ME**

**Designated Validation States:**

KH MA MD TN

(30) Priority: 27.02.2018 US 201862636009 P

(71) Applicants:

STMicroelectronics International N.V. 1118 BH Schiphol (NL) (51) Int Cl.:

G06N 3/04 (2006.01)

G06N 3/063 (2006.01)

STMicroelectronics S.r.l.

20864 Agrate Brianza (MB) (IT)

(72) Inventors:

SINGH, Surinder Pal 201301 NOIDA (IN)

BOESCH, Thomas 6821 Rovio (CH)

DESOLI, Giuseppe

22042 San Fermo Della Battaglia (IT)

(74) Representative: Smith, Gary John

Page White & Farrer Bedford House John Street

London, WC1N 2BF (GB)

## (54) ARITHMETIC UNIT FOR DEEP LEARNING ACCELERATION

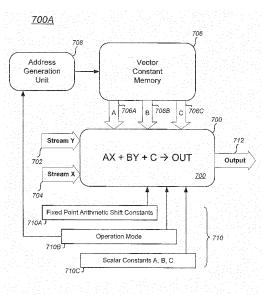

(57) Embodiments of a device include an integrated circuit, a reconfigurable stream switch formed in the integrated circuit, and an arithmetic unit (700) coupled to the reconfigurable stream switch. The arithmetic unit (700) has a plurality of inputs and at least one output, and the arithmetic unit (700) is solely dedicated to performance of a plurality of parallel operations. Each one of the plurality of parallel operations carries out a portion of the formula: output = AX + BY + C.

Fig. 7A

EP 3 531 348 A8