# (11) EP 3 550 550 A1

(12)

#### **DEMANDE DE BREVET EUROPEEN**

(43) Date de publication:

09.10.2019 Bulletin 2019/41

(51) Int CI.:

G09G 3/20 (2006.01) G09G 3/32 (2016.01) G09G 3/3225 (2016.01)

(21) Numéro de dépôt: 19167485.2

(22) Date de dépôt: 05.04.2019

(84) Etats contractants désignés:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

Etats d'extension désignés:

**BA ME**

Etats de validation désignés:

KH MA MD TN

(30) Priorité: 05.04.2018 FR 1852972

- (71) Demandeur: Commissariat à l'énergie atomique et aux énergies alternatives 75015 Paris (FR)

- (72) Inventeur: DUPONT, Bertrand 38054 GRENOBLE CEDEX 09 (FR)

- (74) Mandataire: Brevalex 95, rue d'Amsterdam 75378 Paris Cedex 8 (FR)

# (54) DISPOSITIF ET PROCEDE D'AFFICHAGE D'IMAGES AVEC UNE MEMORISATION DE DONNEES REALISEE DANS LES PIXELS

- (57) Dispositif d'affichage comprenant une matrice de pixels comportant chacun :

- une unité d'affichage affichant un mot binaire de type BCM codé sur N bits, avec N entier supérieur ou égal à 2,

- une unité mémoire (106) mémorisant au moins trois bits, comprenant en outre une unité de séquencement délivrant à l'unité mémoire de chaque pixel, pendant l'affichage d'une première image :

- un signal de mémorisation d'au moins deux bits du mot

binaire d'une deuxième image à afficher après la première image et/ou du mot binaire de la première image,

• un signal d'affichage déclenchant des envois successifs des bits mémorisés à l'unité d'affichage,

dans lequel la mémorisation est déclenchée pendant au moins une partie de l'affichage d'au moins un bit du mot binaire de la première image.

40

45

50

55

#### Description

#### DOMAINE TECHNIQUE ET ART ANTÉRIEUR

**[0001]** L'invention concerne un dispositif d'affichage d'images comprenant une matrice active de pixels pilotés par modulation de code binaire (BCM pour « Binary Code Modulation »), ainsi qu'un procédé d'affichage d'images, dans lesquels une mémorisation des signaux de pixels, ou mots binaires, à afficher est réalisée au sein de la matrice de pixels, dans chaque pixel.

[0002] Dans un écran à matrice active classique, chaque pixel comporte au moins un transistor commandant l'affichage d'un signal lumineux par le pixel. Une capacité de stockage (ou la capacité parasite de la grille du transistor) est également intégrée dans le pixel afin de maintenir durant une période d'affichage une tension de donnée permettant d'obtenir l'intensité lumineuse désirée. Lorsque l'affichage lumineux est réalisé par des diodes électroluminescentes, chaque pixel peut comporter au moins un deuxième transistor alimentant électriquement la diode électroluminescente du pixel en fonction de la tension de donnée.

[0003] Les diodes électroluminescentes de l'écran peuvent requérir des tensions de polarisation élevées. C'est le cas notamment des diodes électroluminescentes réalisées avec du GaN qui, en raison de leur forte variabilité à faible polarisation, ne sont utilisées qu'avec une forte polarisation (en tension ou en courant), et donc n'émettent des signaux lumineux qu'avec une forte luminance.

[0004] Avec de telles diodes électroluminescentes, l'affichage d'une image est commandé de façon binaire (chaque diode électroluminescente est éteinte ou émet avec une forte intensité lumineuse), et le contrôle de la luminosité de chaque pixel, pendant l'affichage de chaque image, est réalisé en commandant le rapport entre la durée pendant laquelle la diode électroluminescente est allumée et la durée totale d'affichage de l'image sur l'écran. Une telle commande des diodes électroluminescentes peut être obtenue en utilisant des mots binaires, (c'est-à-dire un code binaire sur un certain nombre de bits permettant de contrôler l'affichage de l'image) de type BCM dans lesquels la luminosité de chaque pixel est codée sous la forme d'un signal binaire. Chaque bit d'un tel mot binaire pilote l'allumage ou l'extinction de l'une des diodes électroluminescentes pendant une durée proportionnelle au poids du bit. Par exemple, le bit de poids fort (MSB pour « Most Significant Bit ») pilote la diode électroluminescente pendant la moitié de la durée d'affichage de l'image (par exemple 10 ms pour un dispositif d'affichage fonctionnant à une fréquence de 50 images/seconde). Le bit suivant (appelé MSB-1) représente le quart de cette durée, et ainsi de suite jusqu'au bit de poids faible (appelé LSB pour « Less Significant Bit »). Lors de l'affichage d'une image, il est possible que tous les pixels affichent simultanément un bit de même poids.

[0005] Avec ce type de signaux de commande, il est nécessaire d'accéder à chaque pixel N fois par image, avec N correspondant au nombre de bits du signal BCM, afin d'écrire successivement, dans chaque pixel, les N bits du signal du pixel. Or, lors de l'affichage du LSB des mots binaires transmis à tous les pixels, la durée disponible pour écrire dans tous les pixels le bit suivant est inférieure ou égale à la durée d'affichage du LSB. La fréquence avec laquelle tous les pixels doivent être adressés à ce moment-là peut alors être problématique. [0006] Le document FR 3 034 902 propose une solution à ce problème qui consiste, lors de l'affichage d'une image, à écrire sur toutes les lignes de l'écran non pas le bit de même poids, mais des bits de poids différents. Ainsi, à un instant d'affichage d'une image, certaines lignes de pixels affichent le MSB des mots binaires, d'autres lignes de pixels affichent le MSB-1 des mots binaires, etc. Cela permet de réduire la fréquence d'adressage des pixels puisque lors de l'affichage d'une image, une partie seulement des lignes de pixels affichent simultanément le LSB des mots binaires de ces lignes et seules ces lignes nécessitent d'être adressées rapidement après la durée d'affichage du LSB sur les pixels de ces lignes. Le procédé proposé dans ce document a également pour avantage de rendre homogène la fréquence avec laquelle les lignes de pixels sont adressées puisque, à un même instant, les durées d'affichage des bits sont différentes d'une ligne de pixels à l'autre et que les poids des bits affichés sont choisis afin d'équilibrer le nombre de lignes de pixels à adresser tout au long de la durée d'affichage de l'image.

[0007] Le procédé proposé dans le document FR 3 034 902 a toutefois pour inconvénient que l'affichage simultané de bits de poids différents de signaux d'une même image implique de réaliser une mémorisation préalable de tous les bits des mots binaires de tous les pixels de l'image, ainsi que tous ceux de l'image suivante destinée à être affichée. De plus, ce procédé nécessite de faire appel à des blocs de contrôle de l'adressage ligne non standards. En outre, avec ce procédé, le flux vidéo envoyé aux pixels n'est constant que lorsque le nombre de lignes de l'écran est égal à un multiple de 2<sup>n</sup>, avec n correspondant au nombre de bits des mots binaires utilisés, ce qui est rarement le cas. Lorsque le nombre de lignes de l'écran n'est pas égal à un multiple de 2<sup>n</sup>, des « temps morts » pendant lesquels aucune ligne de pixels n'est adressée sont donc nécessaires.

### **EXPOSÉ DE L'INVENTION**

**[0008]** Un but de la présente invention est de proposer un dispositif d'affichage d'image ne présentant pas les inconvénients des dispositifs d'affichage de l'art antérieur et permettant de fonctionner avec peu d'interconnexions entre les pixels et les éléments de contrôle de pixels (lignes et colonnes).

[0009] Pour cela, la présente invention propose un dispositif d'affichage d'images comprenant au moins une

matrice de pixels, dans lequel chaque pixel comporte au moins :

- une unité d'affichage configurée pour émettre, pendant l'affichage par la matrice de pixels d'une image codée sous la forme de plusieurs mots binaires de type BCM comprenant N bits, avec N nombre entier supérieur ou égal à 2, au moins un signal lumineux pendant une durée correspondant à une valeur codée dans un des mots binaires de l'image, chacun des N bits dudit un des mots binaires de l'image représentant une durée d'affichage du signal lumineux proportionnelle au poids du bit,

- une unité mémoire configurée pour mémoriser au moins trois bits, comprenant une sortie couplée à une entrée de l'unité d'affichage, et une entrée configurée pour recevoir les mots binaires des images à afficher par ladite unité d'affichage,

le dispositif d'affichage d'images comprenant en outre une unité de séquencement configurée pour délivrer à l'unité mémoire de chaque pixel, pendant l'affichage d'une première image par la matrice de pixels :

- un signal de mémorisation déclenchant, pendant l'affichage d'un des bits d'un des mots binaires de la première image par l'unité d'affichage du pixel, une mémorisation d'au moins deux autres bits d'un des mots binaires d'une deuxième image destinée à être affichée après la première image et/ou dudit un des mots binaires de la première image (c'est-àdire au moins deux autres bits d'un des mots binaires de la deuxième image et/ou au moins deux autres bits dudit un des mots binaires de la première image), dans ladite unité mémoire du pixel,

- un signal d'affichage déclenchant des envois successifs de chacun des bits dudit un des mots binaires de la première image mémorisés dans l'unité mémoire du pixel à l'unité d'affichage du pixel.

[0010] Il est également décrit un dispositif d'affichage d'images comprenant au moins une matrice de pixels agencés en formant plusieurs lignes et plusieurs colonnes de pixels, dans lequel chaque pixel comporte au moins :

- une unité d'affichage configurée pour émettre, pendant l'affichage d'une image formée de plusieurs mots binaires de type BCM codés sur N bits, avec N nombre entier supérieur ou égal à 2, un signal lumineux représentatif d'un des mots binaires,

- une unité mémoire configurée pour mémoriser au moins trois bits, comprenant en outre une unité de séquencement configurée pour délivrer à l'unité mémoire de chaque pixel, pendant l'affichage d'une première image :

- un signal de mémorisation déclenchant une mémorisation d'au moins deux bits du mot binaire d'une

deuxième image destinée à être affichée après la première image et/ou du mot binaire de la première image dans l'unité mémoire du pixel,

un signal d'affichage déclenchant des envois successifs de chacun des bits mémorisés dans l'unité mémoire à l'unité d'affichage,

et dans lequel les signaux d'affichage et de mémorisation sont tels que la mémorisation desdits au moins deux bits du mot binaire de la deuxième image et/ou du mot binaire de la première image est déclenchée pendant au moins une partie de l'affichage d'au moins un bit du mot binaire de la première image.

[0011] Dans ce dispositif d'affichage, la mémorisation des mots binaires à afficher est réalisée directement dans les pixels, dans des unités mémoire intégrées aux pixels. De plus, l'unité de séquencement est configurée pour réaliser la mémorisation d'au moins une partie des bits des mots binaires d'une image au cours de l'affichage de bits précédents et/ou de l'affichage d'une image précédente. Grâce à cette configuration, il est possible de réaliser, pour chaque pixel, la mémorisation d'au moins une partie d'un mot binaire d'une image lors de l'affichage d'un ou plusieurs bits précédents de ce mot binaire et/ou de l'affichage d'un ou plusieurs bits d'un mot binaire de l'image précédente. En choisissant judicieusement le ou les bits pendant lesquels la mémorisation est déclenchée, la durée disponible pour réaliser cette mémorisation peut donc être plus importante que celle permise dans les dispositifs d'affichage de l'art antérieur, ce qui permet de réduire la fréquence avec laquelle les pixels doivent être adressés.

**[0012]** L'unité mémoire et l'unité d'affichage font partie du pixel, c'est-à-dire sont réalisées sur un même substrat et sont disposées sur une surface limitée du substrat correspondant à la surface d'un pixel.

[0013] Cette réduction de la fréquence d'adressage des pixels est particulièrement intéressante lorsque le dispositif d'affichage d'image forme un écran de dimensions importantes, par exemple de diagonale égale à 1 ou plusieurs mètres. L'utilisation de l'invention pour former des écrans de grande taille est également avantageuse car elle permet de limiter le nombre de fils requis reliés aux pixels.

[0014] De plus, ce dispositif d'affichage d'image ne nécessite pas de réaliser une mémorisation complète de deux images successives.

**[0015]** L'expression « fréquence d'adressage des pixels » désigne la fréquence d'envoi des mots binaires aux pixels, c'est-à-dire après la décompression d'un flux vidéo reçu par le dispositif d'affichage.

**[0016]** Les mots binaires peuvent correspondre à des signaux qui, ensemble, forment une image complète occupant la totalité ou une partie seulement de la surface d'écran du dispositif d'affichage, ou sont associés à une partie ou la totalité des lignes du dispositif d'affichage (l'image peut correspondre à une trame).

[0017] Ce dispositif d'affichage permet de limiter le

35

40

45

50

nombre d'interconnexions reliées à chaque pixel, avec toutefois en contrepartie une surface occupée par les éléments formant ces pixels qui peut être plus importante selon les éléments utilisés. Cette surface occupée plus importante n'est toutefois pas un inconvénient lorsque le dispositif d'affichage correspond à un écran de grande taille.

[0018] De manière avantageuse, l'unité d'affichage de chaque pixel comporte au moins une diode électroluminescente comprenant du GaN. L'utilisation de telles diodes électroluminescentes dans ce dispositif d'affichage est avantageuse car elles sont tout à fait compatible avec un affichage de mots binaires de type BCM, et offrent de plus une surface de semi-conducteur libre importante autour et/ou en dessous d'elles pour permettre la réalisation de l'unité mémoire au sein de chaque pixel.

[0019] Ledit un des bits d'un des mots binaires de la première image peut correspondre avantageusement au bit de poids fort dudit un des mots binaires de la première image. Autrement dit, l'unité de séquencement peut être configurée pour déclencher la mémorisation pendant l'affichage du bit de poids fort dudit un des mots binaires de la première image. Ainsi, la durée disponible pour réaliser la mémorisation correspond à la moitié de la durée d'affichage de la première image. Le dispositif peut dans ce cas fonctionner dans un mode interlacé. Par exemple, pendant une durée correspondant à une première moitié de la durée d'affichage d'une image, les mots binaires peuvent être envoyés aux lignes paires de pixels, et pendant la deuxième moitié de la durée d'affichage d'une image, les mots binaires peuvent être envoyés à lignes impaires de pixels. Ainsi, le flux des mots binaires envoyés aux pixels peut être sensiblement constant.

**[0020]** De manière générale, l'invention peut s'appliquer quel que soit l'ordre dans lequel arrivent les bits des mots binaires dans l'unité mémoire de chaque pixel.

[0021] L'unité mémoire de chaque pixel peut comporter au moins trois bascules couplées en série les unes aux autres et telles qu'une entrée d'une première des bascules soit couplée à une entrée du pixel destinée à recevoir les mots binaires, et qu'une sortie d'une dernière des bascules soit couplée à une entrée de l'unité d'affichage. Une telle unité mémoire est particulièrement avantageuse car le nombre de bascules nécessaire à sa réalisation est limité. Ces bascules forment un registre à décalage dans lequel les bits à afficher sont mémorisés séquentiellement dans les bascules.

**[0022]** Selon un premier mode de réalisation, le dispositif d'affichage d'images peut être tel que :

- l'unité mémoire de chaque pixel comporte en outre au moins un multiplexeur comprenant au moins :

- a) deux entrées de données dont l'une est couplée à une première sortie de l'unité de séquencement sur laquelle le signal d'affichage est destiné à être envoyé et dont l'autre est couplée à une deuxième sortie de l'unité de séquence-

ment sur laquelle le signal de mémorisation est destiné à être envoyé,

b) une sortie couplée à une entrée de commande de chacune d'au moins deux premières bascules de l'unité mémoire correspondant à celles, parmi les bascules de l'unité mémoire, dans lesquelles lesdits au moins deux autres bits d'un des mots binaires de la deuxième image et/ou dudit un des mots binaires de la première image sont destinés à être mémorisés pendant ledit affichage d'un des bits d'un des mots binaires de la première image,

c) une entrée de commande couplée à une troisième sortie de l'unité de séquencement sur laquelle un signal de sélection est destiné à être envoyé, permettant de coupler la sortie du multiplexeur à l'une ou l'autre des deux entrées de données du multiplexeur en fonction de la valeur du signal de sélection,

- une entrée de commande de la dernière des bascules de l'unité mémoire de chaque pixel est couplée à la première sortie de l'unité de séquencement,

- l'unité de séquencement est configurée telle que, pour chaque pixel, le signal de sélection commande le multiplexeur tel que pendant ledit affichage d'un des bits d'un des mots binaires de la première image, le signal de mémorisation est délivré sur la sortie du multiplexeur et déclenche la mémorisation desdits au moins deux autres bits d'un des mots binaires de la deuxième image et/ou dudit un des mots binaires de la première image, et que pour l'affichage des autres bits mémorisés, le signal d'affichage est délivré sur la sortie du multiplexeur et déclenche les affichages successifs de chacun des autres bits mémorisés.

[0023] Selon un deuxième mode de réalisation, le dispositif d'affichage d'images peut être tel que :

- l'unité mémoire de chaque pixel comporte en outre au moins :

- a) une porte OU comprenant deux entrées sont couplées à des première et deuxième sorties de l'unité de séquencement sur lesquelles les signaux d'affichage et de mémorisation sont destinés à être envoyés, et dont une sortie est couplée à une entrée de commande de chacune d'au moins deux premières bascules de l'unité mémoire correspondant à celles, parmi les bascules de l'unité mémoire, dans lesquelles lesdits au moins deux autres bits d'un des mots binaires de la deuxième image et/ou dudit un des mots binaires de la première image sont destinés à être mémorisés pendant ledit affichage d'un des bits d'un des mots binaires de la première image,

15

20

35

40

45

50

55

b) un multiplexeur comprenant deux entrées de données dont l'une est couplée à la sortie de la porte OU et dont l'autre est couplée à un potentiel électrique de référence, une entrée de commande couplée à une troisième sortie de l'unité de séquencement sur laquelle un signal de sélection est destiné à être envoyé et permettant de coupler la sortie du multiplexeur à l'une ou l'autre des deux entrées de données du multiplexeur en fonction de la valeur du signal de sélection, et une sortie couplée à une entrée de commande de la dernière des bascules de l'unité mémoire,

l'unité de séquencement est configurée telle que, pour chaque pixel, le signal de sélection commande le multiplexeur tel que pendant ledit affichage d'un des bits d'un des mots binaires de la première image, le potentiel électrique de référence soit délivré sur le sortie du multiplexeur pendant que le signal de mémorisation délivré sur l'entrée de commande de chacune des premières bascules de l'unité mémoire déclenche la mémorisation desdits au moins deux autres bits d'un des mots binaires de la deuxième image et/ou dudit un des mots binaires de la première image, et que pour l'affichage des autres bits mémorisés, le signal obtenu à la sortie de la porte OU soit délivré sur les entrées de commande des bascules de l'unité mémoire et déclenche les affichages successifs de chacun des autres bits mémorisés.

**[0024]** Selon une variante du deuxième mode de réalisation, le dispositif d'affichage d'images peut être tel que :

- l'unité de séquencement délivre sur une seule sortie le signal d'affichage et le signal de mémorisation sous la forme d'un seul et même signal appelé signal d'affichage et de mémorisation, ladite sortie étant couplée à une entrée de commande de chacune d'au moins deux premières bascules de l'unité mémoire correspondant à celles, parmi les bascules de l'unité mémoire, dans lesquelles lesdits au moins deux autres bits d'un des mots binaires de la deuxième image et/ou dudit un des mots binaires de la première image sont mémorisés pendant ledit affichage d'un des bits d'un des mots binaires de la première image,

- l'unité mémoire de chaque pixel comporte en outre au moins un multiplexeur comprenant deux entrées de données, dont l'une est couplée à la sortie de l'unité de séquencement sur laquelle le signal d'affichage et de mémorisation est destiné à être délivré et dont l'autre est couplée à un potentiel électrique de référence, une entrée de commande couplée à une troisième sortie de l'unité de séquencement sur laquelle un signal de sélection est destiné à être envoyé et permettant de coupler la sortie du multi-

plexeur à l'une ou l'autre des deux entrées de données du multiplexeur en fonction de la valeur du signal de sélection, et une sortie couplée à une entrée de commande de la dernière des bascules de l'unité mémoire.

l'unité de séquencement est configurée telle que, pour chaque pixel, le signal de sélection commande le multiplexeur tel que pendant ledit affichage d'un des bits d'un des mots binaires de la première image, le potentiel électrique de référence soit délivré sur la sortie du multiplexeur pendant que le signal d'affichage et de mémorisation délivré sur l'entrée de commande de chacune des premières bascules de l'unité mémoire déclenche la mémorisation desdits au moins deux autres bits d'un des mots binaires de la deuxième image et/ou dudit un des mots binaires de la première image, et que pour l'affichage des autres bits mémorisés, le signal d'affichage et de mémorisation soit délivré sur les entrées de commande des bascules de l'unité mémoire et déclenche les affichages successifs de chacun des autres bits mémorisés.

**[0025]** Dans l'unité de séquencement, le signal d'affichage et de mémorisation peut être obtenu en sortie d'une porte OU recevant en entrée le signal d'affichage et le signal de mémorisation.

[0026] Selon une variante de réalisation des premier et deuxième modes de réalisation, dans chaque pixel, la sortie de la dernière des premières bascules de l'unité mémoire du pixel peut être couplée à l'entrée de la première des bascules de l'unité mémoire du pixel par l'intermédiaire d'un interrupteur commandé par l'unité de séquencement qui est configurée pour fermer l'interrupteur lorsque le mot binaire de la première image est similaire au mot binaire de la deuxième image. Cet interrupteur peut également être contrôlé par le signal de sélection (qui peut être commun à une ligne de pixels ou propre au pixel). Dans ce cas, lorsque le signal de sélection est à zéro, le rebouclage est actif, et à chaque impulsion du signal d'affichage et de mémorisation, les données se déplacent mais sont conservées dans une des bascules. S'il n'y a pas de changement entre deux images successives, alors le signal de sélection reste à zéro et après N impulsions du signal d'affichage et de mémorisation (par exemple 8 pour 8 bits mémorisés), on retrouve le mot binaire de l'image précédente.

**[0027]** Selon un troisième mode de réalisation, le dispositif d'affichage d'images peut être tel que :

- l'unité mémoire de chaque pixel comporte :

- a) au moins deux premières bascules couplées en série l'une à l'autre et telles qu'une entrée de données d'une première desdites au moins deux premières bascules soit couplée à une entrée du pixel destinée à recevoir les mots binaires,

10

15

20

35

40

50

b) au moins deux deuxièmes bascules couplées en série l'une à l'autre et telles qu'une entrée de données d'une première desdites au moins deux deuxièmes bascules soit couplée à ladite entrée du pixel,

c) un circuit de commutation comprenant deux entrées de données, dont l'une est couplée à une première sortie de l'unité de séquencement sur laquelle le signal d'affichage est destiné à être envoyé et dont l'autre est couplée à une deuxième sortie de l'unité de séquencement sur laquelle le signal de mémorisation est destiné à être envoyé, une entrée de commande couplée à une troisième sortie de l'unité de séguencement sur laquelle un signal de sélection est destiné à être envoyé, une première sortie couplée à une entrée de commande de chacune des premières bascules et une deuxième sortie couplée à une entrée de commande de chacune des deuxièmes bascules, et configuré tel qu'en fonction de la valeur du signal de sélection, la première sortie soit couplée à la première entrée de données et la deuxième sortie soit couplée à la deuxième entrée de données, ou la première sortie soit couplée à la deuxième entrée de données et la deuxième sortie soit couplée à la première entrée de données,

d) un multiplexeur comprenant deux entrées de données dont l'une est couplée à la sortie d'une dernière desdites au moins deux premières bascules et dont l'autre est couplée à la sortie d'une dernière desdites au moins deux deuxièmes bascules, une entrée de commande couplée à la troisième sortie de l'unité de séquencement, et une sortie couplée à une entrée de l'unité d'affichage,

l'unité de séquencement est configurée telle que, pour chaque pixel, le signal de sélection commande le circuit de commutation et le multiplexeur tels que pendant ledit affichage d'un des bits d'un des mots binaires de la première image via les premières bascules, le signal de mémorisation est délivré aux entrées de commande des deuxièmes bascules et déclenche la mémorisation desdits au moins deux autres bits d'un des mots binaires de la deuxième image et/ou dudit un des mots binaires de la première image dans les deuxièmes bascules.

**[0028]** Selon un quatrième mode de réalisation, le dispositif d'affichage d'images peut être tel que l'unité mémoire de chaque pixel comporte au moins :

- au moins trois éléments mémoires comprenant chacun une entrée sur laquelle un bit à mémoriser est destiné à être appliqué et une sortie sur laquelle un bit mémorisé est destiné à être délivré,

- un premier circuit d'adressage comprenant une en-

trée de donnée couplée à une entrée du pixel destinée à recevoir les mots binaires des images à afficher, au moins trois sorties chacune couplée à une entrée de l'un des éléments mémoires, et au moins une entrée de commande couplée à au moins une première sortie de l'unité de séquencement sur laquelle le signal de mémorisation est destiné à être délivré.

un deuxième circuit d'adressage comprenant au moins trois entrées de donnée chacune couplée à une sortie de l'un des éléments mémoires, une sortie couplée à une entrée de l'unité d'affichage, et au moins une entrée de commande couplée à au moins une deuxième sortie de l'unité de séquencement sur laquelle le signal d'affichage est destiné à être délivré,

et dans lequel l'unité de séquencement est configurée telle que, pour chaque pixel :

- lors de la mémorisation d'un bit déclenchée par le signal de mémorisation, le premier circuit d'adressage délivre sur l'entrée de l'un des trois éléments mémoires le bit reçu sur son entrée de donnée,

- lors de l'affichage d'un des bits mémorisés déclenché par le signal d'affichage, le deuxième circuit d'adressage délivre sur une entrée de l'unité d'affichage l'un des bits mémorisés dans les trois éléments mémoires.

**[0029]** Selon une première configuration du quatrième mode de réalisation, le premier circuit d'adressage peut comporter :

- un premier générateur d'adresse comprenant une entrée couplée à la première sortie de l'unité de séquencement,

- un démultiplexeur comprenant une entrée de donnée couplée à l'entrée du pixel destinée à recevoir les mots binaires des images à afficher, au moins trois sorties chacune couplée à l'entrée d'un des éléments mémoires, et une entrée de commande couplée à une sortie du premier générateur d'adresse,

- 45 le deuxième circuit d'adressage peut comporter :

- un deuxième générateur d'adresse comprenant une entrée couplée à la deuxième sortie de l'unité de séquencement,

- un multiplexeur comprenant au moins trois entrées de donnée chacune couplée à la sortie d'un des éléments mémoires, une sortie couplée à l'entrée de l'unité d'affichage, et une entrée de commande couplée à une sortie du deuxième générateur d'adresse,

et l'unité de séquencement peut être configurée telle que, pour chaque pixel :

25

30

35

45

lors de la mémorisation d'un bit déclenchée par le signal de mémorisation, le premier générateur d'adresse délivre au démultiplexeur un premier signal d'adresse codant sur plusieurs bits l'adresse d'un des éléments mémoires dans lequel ledit bit est destiné à être mémorisé,

lors de l'affichage d'un des bits mémorisés déclenché par le signal d'affichage, le deuxième générateur d'adresse délivre au multiplexeur un deuxième signal d'adresse codant sur plusieurs bits l'adresse d'un des éléments mémoires depuis lequel ledit un des bits mémorisés est lu.

[0030] Selon une deuxième configuration du quatrième mode de réalisation, l'unité de séquencement peut être configurée telle que le signal de mémorisation soit formé d'au moins trois premiers signaux d'adressage commandant chacun une mémorisation dans l'un des éléments mémoires, et telle que le signal d'affichage soit formé d'au moins trois deuxièmes signaux d'adressage commandant chacun une lecture d'un bit mémorisé dans l'un des éléments mémoires.

**[0031]** Selon une troisième configuration du quatrième mode de réalisation, le premier circuit d'adressage peut comporter :

- un premier compteur comprenant une entrée couplée à la première sortie de l'unité de séquencement,

- un premier décodeur d'adresse comprenant une entrée de donnée couplée à l'entrée du pixel destinée à recevoir les mots binaires, au moins trois sorties chacune couplée à l'entrée d'un des éléments mémoires, et une entrée de commande couplée à une sortie du premier compteur,

le deuxième circuit d'adressage peut comporter :

- un deuxième compteur comprenant une entrée couplée à la deuxième sortie de l'unité de séquencement,

- un deuxième décodeur d'adresse comprenant au moins trois entrées de donnée chacune couplée à la sortie d'un des éléments mémoires, une sortie couplée à l'entrée de l'unité d'affichage, et une entrée de commande couplée à une sortie du deuxième compteur.

[0032] Le dispositif peut être tel que :

- l'unité mémoire est configurée pour mémoriser au moins N+1 bits ; et

- pendant ledit affichage d'un des bits d'un des mots binaires de la première image, le signal de mémorisation déclenche la mémorisation des N bits du mot binaire de la deuxième image ou la mémorisation de N-1 bits suivants du mot binaire de la première image et d'un bit du mot binaire de la deuxième image.

[0033] En variante, lorsque l'unité mémoire de chaque pixel n'a pas une capacité de mémorisation au moins équivalente au nombre de bits de chaque mot binaire, seule une partie des bits des mots binaires d'une image sont mémorisés pendant l'affichage d'un bit, les autres bits étant mémorisés au cours de l'affichage d'un ou plusieurs autres bits de ce mot.

[0034] L'unité d'affichage de chaque pixel peut comporter M diodes électroluminescentes, et l'unité mémoire de chaque pixel peut comporter un nombre d'entrées configurées pour recevoir les mots binaires des images à afficher par l'unité d'affichage du pixel qui est supérieur ou égal à 1 et qui est inférieur ou égal à M, avec M correspondant à un nombre entier supérieur ou égal à 1.

[0035] Les pixels peuvent être formés par des modules réalisés sur un substrat, chaque module comportant au moins :

- une première partie se trouvant du côté du substrat et formant un circuit électronique comprenant au moins l'unité mémoire du pixel;

- une deuxième partie telle que la première partie soit disposée entre le substrat et la deuxième partie, et formant au moins une partie de l'unité d'affichage du pixel.

[0036] Dans ce cas, il est possible que :

- la deuxième partie de chaque module corresponde à seule diode électroluminescente, ou

- chaque module comporte plusieurs deuxièmes parties formant chacune une diode électroluminescente et disposées sur une première partie commune auxdites plusieurs deuxièmes parties.

[0037] Chaque pixel peut comporter un seul module, ou chaque pixel peut comporter plusieurs modules et un circuit électronique couplé au substrat, à côté desdits plusieurs modules, et formant une partie de l'unité mémoire du pixel.

[0038] Il est également proposé un procédé d'affichage d'images par un dispositif d'affichage d'images comprenant au moins une matrice de pixels agencés en formant plusieurs lignes et plusieurs colonnes de pixels, réalisant un affichage successif d'images chacune formée de plusieurs mots binaires de type BCM codé sur N bits, avec N nombre entier supérieur ou égal à 2, chaque pixel affichant, pendant l'affichage d'une image, l'un des mots binaires,

le procédé comprenant, pendant l'affichage d'une première image et pour chaque pixel, une mémorisation, dans une unité mémoire disposée dans le pixel, d'au moins deux bits du mot binaire d'une deuxième image destinée à être affichée après la première image et/ou du mot binaire de la première image, déclenchée pendant au moins une partie de l'affichage d'au moins un bit du mot binaire de la première image.

[0039] L'invention porte également sur un procédé

20

35

d'affichage d'images par un dispositif d'affichage d'images comprenant au moins une matrice de pixels, réalisant un affichage successif d'images chacune codée sous la forme de plusieurs mots binaires de type BCM codé sur N bits, avec N nombre entier supérieur ou égal à 2, chaque pixel affichant, pendant l'affichage d'une image, un signal lumineux pendant une durée correspondant à une valeur codée dans un des mots binaires de l'image, chacun des N bits dudit un des mots binaires de l'image représentant une durée d'affichage proportionnelle au poids du bit,

le procédé comprenant, pendant l'affichage d'un des bits d'un des mots binaires de la première image par l'unité d'affichage du pixel et pour chaque pixel, une mémorisation, dans une unité mémoire disposée dans le pixel et comprenant une entrée configurée pour recevoir les mots binaires des images à afficher, d'au moins deux autres bits d'un des mots binaires d'une deuxième image destinée à être affichée après la première image et/ou dudit un des mots binaires de la première image.

[0040] Lesdits au moins deux autres bits d'un des mots binaires de la deuxième image et/ou dudit un des mots binaires de la première image peuvent être mémorisés séquentiellement dans l'unité mémoire pendant ledit affichage d'un des bits d'un des mots binaires de la première image.

**[0041]** Le signal d'affichage et le signal de mémorisation peuvent correspondre à, ou être combinés dans, un seul signal d'affichage et de mémorisation.

**[0042]** Lorsque le mot binaire est destiné à être le même dans les première et deuxième images, les bits du mot binaire de la première image peuvent être mémorisés de nouveau dans l'unité mémoire pour former le mot binaire de la deuxième image.

[0043] Le procédé d'affichage d'images peut être tel que :

- l'unité mémoire est configurée pour mémoriser au moins N+1 bits : et

- pendant ledit affichage d'un des bits d'un des mots binaires de la première image, le signal de mémorisation déclenche la mémorisation des N bits du mot binaire de la deuxième image ou la mémorisation de N-1 bits du mot binaire de la première image et d'un bit du mot binaire de la deuxième image.

#### **BRÈVE DESCRIPTION DES DESSINS**

**[0044]** La présente invention sera mieux comprise à la lecture de la description d'exemples de réalisation donnés à titre purement indicatif et nullement limitatif en faisant référence aux dessins annexés sur lesquels :

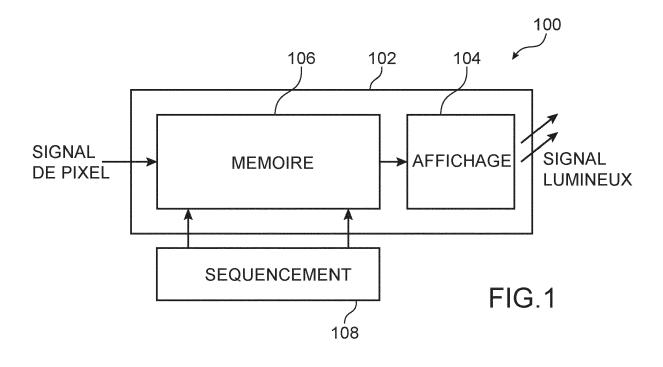

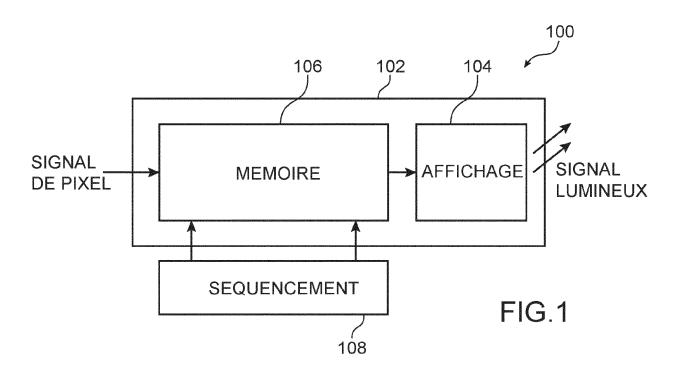

- les figures 1 et 2 représentent schématiquement une partie d'un dispositif d'affichage d'images, objet de la présente invention,

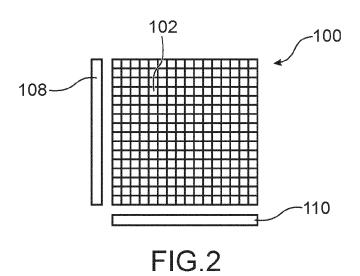

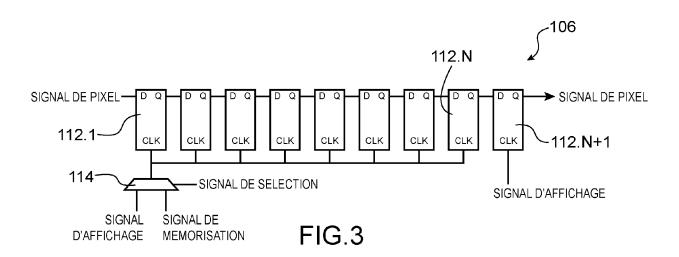

- la figure 3 représente un exemple de réalisation d'une unité mémoire d'un pixel d'un dispositif d'affi-

- chage d'images, objet de la présente invention, selon un premier mode de réalisation,

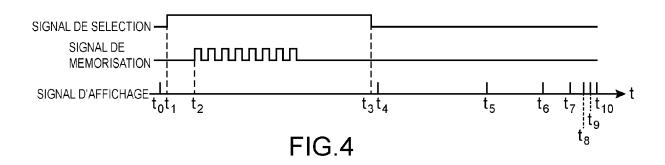

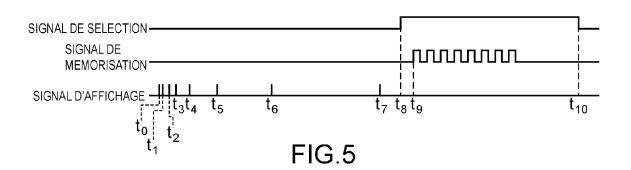

- les figures 4 et 5 représentent des chronogrammes de signaux utilisés dans le dispositif d'affichage d'images selon le premier mode de réalisation,

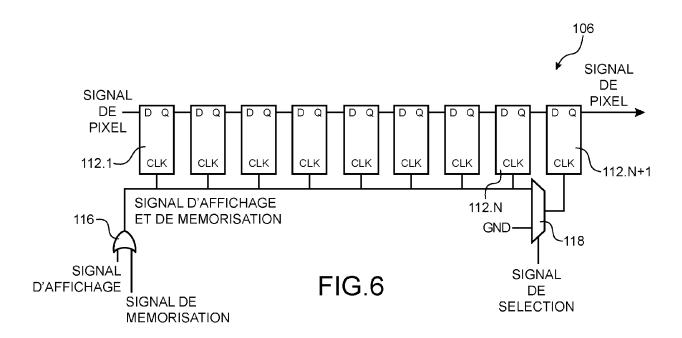

- la figure 6 représente un exemple de réalisation d'une unité mémoire d'un pixel d'un dispositif d'affichage d'images, objet de la présente invention, selon un deuxième mode de réalisation,

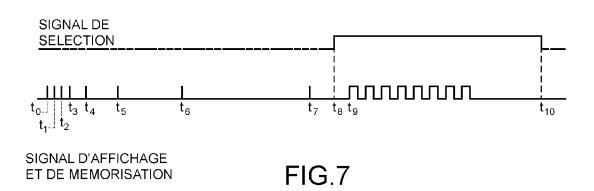

- la figure 7 représente des chronogrammes de signaux utilisés dans le dispositif d'affichage d'images selon le deuxième mode de réalisation,

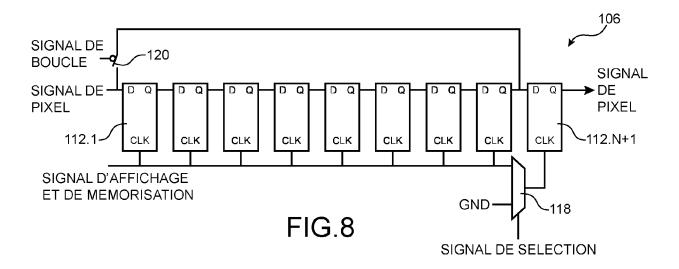

- la figure 8 représente un exemple de réalisation d'une unité mémoire d'un pixel d'un dispositif d'affichage d'images, objet de la présente invention, selon une variante du deuxième mode de réalisation,

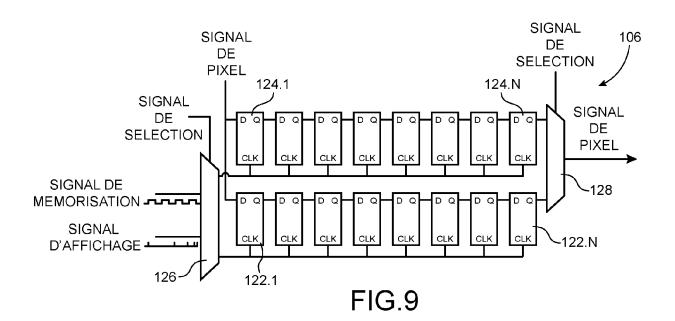

- la figure 9 représente un exemple de réalisation d'une unité mémoire d'un pixel d'un dispositif d'affichage d'images, objet de la présente invention, selon un troisième mode de réalisation,

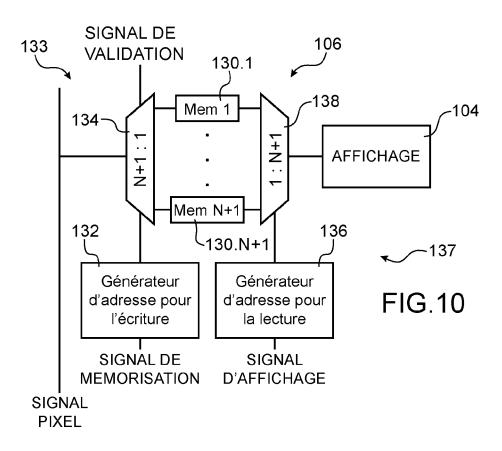

- la figure 10 représente un exemple de réalisation d'une unité mémoire d'un pixel d'un dispositif d'affichage d'images, objet de la présente invention, selon un quatrième mode de réalisation,

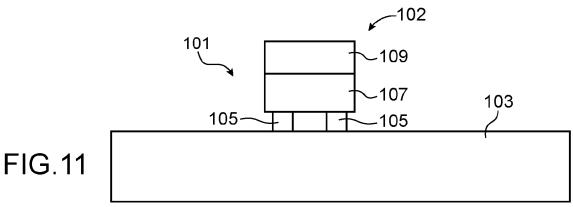

- la figure 11 représente schématiquement un exemple de réalisation d'un pixel d'un dispositif d'affichage d'images, objet de la présente invention,

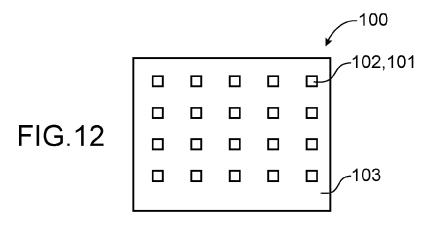

- la figure 12 représente schématiquement une vue de dessus d'un dispositif d'affichage d'images, objet de la présente invention,

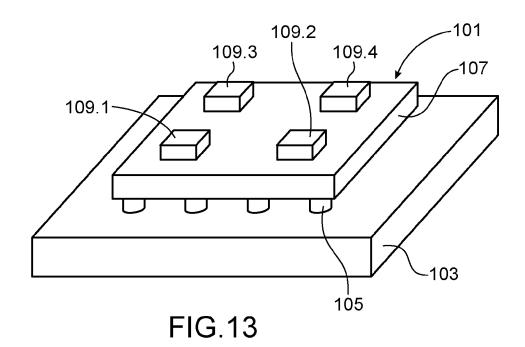

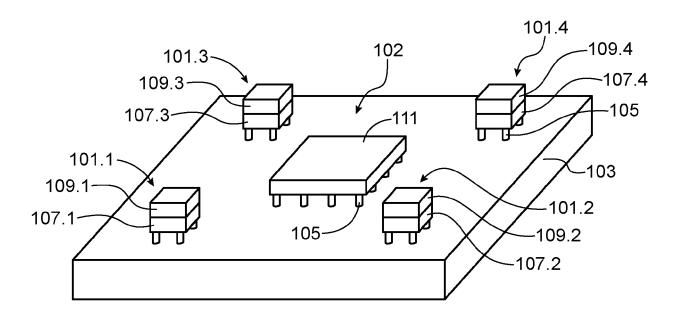

- les figures 13 et 14 représentent schématiquement des configurations particulières d'un pixel d'un dispositif d'affichage d'images, objet de la présente invention

- la figure 15 représente schématiquement un exemple de réalisation d'une unité mémoire couplées à deux diodes électroluminescentes d'une unité d'affichage d'un pixel d'un dispositif d'affichage d'images, objet de la présente invention.

**[0045]** Des parties identiques, similaires ou équivalentes des différentes figures décrites ci-après portent les mêmes références numériques de façon à faciliter le passage d'une figure à l'autre.

[0046] Les différentes parties représentées sur les figures ne le sont pas nécessairement selon une échelle uniforme, pour rendre les figures plus lisibles.

**[0047]** Les différentes possibilités (variantes et modes de réalisation) doivent être comprises comme n'étant pas exclusives les unes des autres et peuvent se combiner entre elles.

# EXPOSÉ DÉTAILLÉ DE MODES DE RÉALISATION PARTICULIERS

**[0048]** On se réfère tout d'abord à la figure 1 qui représente schématiquement, sous la forme de blocs fonctionnels, une partie d'un dispositif d'affichage d'images

20

25

40

45

100, et notamment un des pixels 102 du dispositif 100 ainsi qu'une unité de séquencement 108 à laquelle les pixels 102 sont couplés.

[0049] Le pixel 102 comporte une unité d'affichage 104 configurée pour émettre, pendant l'affichage d'une image formée de plusieurs mots binaires, au moins un signal lumineux représentatif d'au moins un mot binaire que le pixel 102 reçoit. Cette unité d'affichage 104 comporte par exemple une diode électroluminescente, et par exemple de type LED (diode électroluminescente) ou μLED (micro-diode électroluminescente), réalisé à partir de GaN, couplée à un élément de commande comprenant par exemple au moins un transistor MOS configuré pour alimenter électriquement la diode électroluminescente en fonction d'un signal d'affichage binaire reçu en entrée de l'unité d'affichage 104. Différents exemples de réalisation d'une diode électroluminescente couplée à un tel élément de commande sont par exemple décrits dans le document FR 3 034 902.

[0050] Les mots binaires reçus par les pixels 102 sont de type BCM et sont codés sur N bits, N étant un nombre entier supérieur ou égal à 2. Ainsi, pour réaliser l'affichage de chaque image, chaque pixel 102 reçoit en entrée un mot binaire codé sur N bits, avec par exemple N compris entre 6 et 10 bits et par exemple égal à 8 bits, dans lequel est codé la durée pendant laquelle l'unité d'affichage 104 du pixel 102 doit émettre un signal lumineux. [0051] Le mot binaire est binaire, ce qui signifie que l'unité d'affichage 104 est commandée de manière binaire. Avec un signal d'affichage de pixel de type BCM, le signal lumineux est émis par l'unité d'affichage 104 de chaque pixel 102, pour chaque bit du mot binaire reçu, pendant une durée proportionnelle au poids de chacun de ces bits. Ainsi, le bit de poids fort, également appelé MSB, du mot binaire d'une image commande l'émission ou non du signal lumineux pendant une durée égale à la moitié de la durée d'affichage de l'image (par exemple 5 ms pour un dispositif 100 fonctionnant à une fréquence de 100 images/seconde). Le bit suivant, appelée MSB-1, représente le quart de cette durée, et ainsi de suite jusqu'au bit de poids faible, appelé LSB.

[0052] Le pixel 102 comporte également une unité mémoire 106 configurée pour mémoriser au moins deux bits du mot binaire reçu en entrée du pixel 102. Dans les différents modes de réalisation décrits plus loin, l'unité mémoire 106 de chaque pixel 102 est configurée pour mémoriser N+1 bits. Toutefois, la capacité de mémorisation de l'unité mémoire 106 de chaque pixel 102 est adaptée notamment en fonction de la place disponible dans chaque pixel 102 pour la réalisation de l'unité mémoire 106.

[0053] L'unité mémoire 106 reçoit en entrée un signal de mémorisation envoyé depuis une unité de séquencement 108. L'unité mémoire 106 est configurée pour mémoriser au moins une partie des bits du mot binaire appliqué sur l'entrée de l'unité mémoire 106, sur la commande du signal de mémorisation.

[0054] L'unité mémoire 106 reçoit également en entrée

un signal d'affichage envoyé depuis l'unité de séquencement 108. L'unité mémoire 106 est configurée pour envoyer successivement sur l'entrée de l'unité d'affichage 104 chacun des bits mémorisés, sur la commande du signal d'affichage.

**[0055]** Le pixel 102 représenté sur la figure 1 correspond à un des pixels du dispositif 100 représenté schématiquement sur la figure 2, sur laquelle les pixels 102 sont agencés en formant une matrice de plusieurs lignes et plusieurs colonnes de pixels 102.

[0056] Le dispositif 100 peut correspondre à un écran monochrome ou un écran couleur. Un dispositif 100 correspondant à un écran couleur peut comporter une matrice de « pixels couleur » chacun formé par la juxtaposition de plusieurs pixels 102 adaptés pour émettre des signaux lumineux de couleurs différentes. Chacun des pixels 102 est par exemple associé à un filtre coloré, ou comporte au moins une diode électroluminescente dont les matériaux permettent une émission lumineuse à la longueur d'onde souhaitée, ou bien est associé à un élément de conversion de longueur d'onde. Chaque pixel 102 reçoit un mot binaire représentatif de la luminosité à afficher pour la couleur associée au pixel 102 pendant l'affichage d'une image. En variante, plusieurs pixels 102 peuvent former ensemble un module apte à émettre un signal lumineux couleur et recevant, sur une entrée, les mots binaires destinés aux pixels du module.

[0057] Le dispositif 100 comporte également un registre 110 envoyant aux pixels 102, par l'intermédiaire de lignes de données chacune couplée aux pixels 102 d'une même colonne, les mots binaires. L'adressage des lignes de la matrice de pixels 102 est par exemple réalisé par l'unité de séquencement 108.

[0058] Comme indiqué précédemment, l'unité d'affichage 104 de chaque pixel 102 comporte avantageusement une ou plusieurs diodes électroluminescentes réalisées à partir de GaN et couplées à un élément de commande de type CMOS configuré notamment pour alimenter électriquement la ou les diodes électroluminescentes en fonction d'un ou plusieurs signaux d'affichage binaires reçus en entrée de l'unité d'affichage 104. La figure 11 représente schématiquement un exemple de réalisation d'un pixel 102. Chaque pixel 102 est réalisé sous la forme d'un module 101 réalisé et hybridé sur un substrat 103 servant de support, par des éléments 105 de connexion électrique et mécanique. Ces éléments 105 correspondent par exemple à des microbilles, des micro-tubes, ou bien à des portions de matériau(x) métallique(s) solidarisées les unes aux autres par collage direct (comprenant par exemple du cuivre).

[0059] Le module 101 correspondant à chaque pixel 102 comporte une première partie 107 se trouvant du côté du substrat 103 et formant un circuit électronique par exemple réalisé en technologie CMOS, comprenant notamment l'unité mémoire 106 du pixel 102 ainsi que l'élément de commande de la diode du pixel 102 (qui commande l'émission lumineuse du pixel 102). Cette première partie 107 est par exemple réalisée à partir de

25

40

50

silicium ou tout autre semi-conducteur adapté à la réalisation de transistors MOS.

[0060] Le module 101 comporte également une deuxième partie 109 formant l'unité d'affichage 104 du pixel 102 et réalisée à partir du semi-conducteur correspondant au matériau émissif de la diode ou des diodes du pixel 102, ici avantageusement du GaN.

[0061] Les modules 101 correspondant aux pixels 102 sont réalisés collectivement à partir d'une plaque de semi-conducteur sur lequel les composants électroniques, notamment les transistors MOS, de la première partie 107 de chaque module 101 sont réalisés. Le matériau émissif, par exemple le GaN, est ensuite déposé sur l'ensemble de la plaque comprenant les premières parties 107 des modules 101. Les deuxièmes parties 109 sont ensuite réalisées pour former les unités d'affichage 104 des pixels 102. La plaque est ensuite découpée afin de séparer individuellement les modules 101. Les modules 101 sont ensuite hybridés sur le substrat 103.

[0062] Lorsque les unités d'affichage 104 comportent des diodes de GaN, la forte luminance de ces diodes permet de réaliser les modules avec des dimensions réduites. Après leur hybridation sur le substrat 103, les modules 101 formant les pixels 102 sont espacés les uns des autres d'une distance par exemple supérieure ou égale aux dimensions d'un ou plusieurs modules 101, comme cela est représenté schématiquement sur la figure 12.

[0063] Réaliser de tels pixels 102 avec des dimensions réduites représente une importante économie de coût. Par contre, cela implique que la place disponible pour réaliser les différents composants CMOS au sein de la première partie 107 des modules 101 est limitée. De plus, une grande partie de cette place est occupée par les vias conducteurs correspondant aux éléments 105. Afin de limiter la place occupée par ces vias, la plaque de semiconducteur sur laquelle les premières parties 107 des modules 101 sont réalisées est amincie, par exemple avec une épaisseur de l'ordre de 10 μm, ce qui permet de réduire les dimensions des sections des vias.

[0064] Les différents éléments du dispositif 100 décrits ci-dessous permettent de répondre à cette contrainte, c'est-à-dire permettre un fonctionnement des pixels 102 avec peu d'interconnexions entre les pixels 102 et les éléments de contrôle des pixels 102.

**[0065]** En variante, il est également possible d'avoir une partie de l'électronique de commande et/ou de mémorisation des pixels qui soit formée par des puces indépendantes des modules 101 et hybridées sur le substrat 103 à côté des modules 101.

[0066] Les pixels 102 sont ici agencés en lignes et en colonnes. De plus, les lignes conductrices sur lesquelles circulent les signaux peuvent être communes aux pixels 102 appartenant à une même ligne ou à une même colonne. Par exemple, il est possible d'avoir un fil commun à tous les pixels 102 d'une même colonne et sur lequel les signaux de pixels (dont les bits correspondent aux images à afficher) sont envoyés, ainsi que des fils com-

muns à tous les pixels d'une même ligne et sur lesquels les signaux de commande sont envoyés.

[0067] En considérant un dispositif 100 fonctionnant à une fréquence de 100 images/seconde, dont l'écran est formé par 1080 lignes de pixels et 1920 colonnes de pixels, et des mots binaires chacun codé sur 8 bits, le débit de données des mots binaires est de 1660 Mb/s, en considérant ce flux de données comme étant constant. Etant donné que les mots binaires sont envoyés parallèlement sur les colonnes de pixels 102 par le registre 110, le débit de données sur chaque colonne de pixels est donc de 864 Kb/s.

[0068] L'unité de séquencement 108 est configurée pour que les signaux de mémorisation et d'affichage envoyés à l'unité mémoire 106 soient tels que, pendant au moins une partie de l'affichage d'au moins un bit du mot binaire d'une première image, au moins deux bits du mot binaire d'une deuxième image destinée à être affichée après la première image et/ou du mot binaire de la première image (reçus donc après le bit affiché) soient mémorisés dans l'unité mémoire 106. Lorsque l'unité mémoire 106 de chaque pixel 102 est configurée pour mémoriser N+1 bits, N bits du mot binaire de la deuxième image, ou N-1 bits du mot binaire de la première image et un bit du mot binaire de la deuxième image, sont mémorisés dans l'unité mémoire 106.

**[0069]** La figure 3 représente un exemple de réalisation de l'unité mémoire 106 de chaque pixel 102 du dispositif 100 selon un premier mode de réalisation.

[0070] L'unité mémoire 106 comporte N+1 bascules 112 couplées en série les unes aux autres. Ces bascules correspondent par exemple à des bascules D. Une première de ces N+1 bascules 112, référencée 112.1 sur la figure 3, comporte une entrée de données sur laquelle le mot binaire reçu en entrée du pixel 102 est envoyé. La sortie d'une dernière des N+1 bascules 112, référencée 112.N+1 sur la figure 3, est couplée à une entrée de l'unité d'affichage 104. Sur l'exemple de la figure 3, l'unité mémoire 106 comporte 9 bascules 112, les mots binaires reçus par le pixel 102 comportant chacun 8 bits (N = 8) destinés à être mémorisés par l'unité mémoire 106.

[0071] L'unité mémoire 106 du pixel 102 comporte également un multiplexeur 114 comprenant deux entrées de données couplées à l'unité de séquencement 108. L'une de ces deux entrées est couplée à une première sortie de l'unité de séquencement 108 sur laquelle le signal d'affichage est envoyé. L'autre de ces deux entrées est couplée à une deuxième sortie de l'unité de séquencement 108 sur laquelle le signal de mémorisation est envoyé. Le multiplexeur 114 comporte également une entrée de commande couplée à une troisième sortie de l'unité de séquencement 108 sur laquelle un signal de sélection est envoyé. Enfin, la sortie du multiplexeur 114 est couplée à une entrée de commande de chacune de N premières bascules 112, c'est-à-dire les bascules 112.1 à 112.N. lci, seule l'entrée de commande de la dernière bascule 112.N+1 n'est pas couplée à la sortie du multiplexeur 114. L'entrée de commande de la der-

nière bascule 112.N+1 est couplée à la première sortie de l'unité de séquencement 108 sur laquelle le signal d'affichage est délivré.

[0072] Selon une première configuration du dispositif 100 comportant l'unité mémoire 106 représentée sur la figure 3, les signaux d'affichage et de mémorisation peuvent être tels que pendant au moins une partie de l'affichage d'un bit du mot binaire d'une première image, ici le MSB de ce mot binaire, la mémorisation des N-1 autres bits du mot binaire de la première image et d'un bit du mot binaire d'une deuxième image destinée à être affichée après la première image, ici le MSB du mot binaire de la deuxième image, est déclenchée. Dans cette première configuration, les mots binaires reçus par les pixels 102 sont tels que les N bits de chaque mot binaire envoyés successivement, en série, à l'entrée de l'unité mémoire 106, sont ordonnés tels que le poids des bits reçus soit décroissant avec l'ordre d'arrivée sur l'entrée de l'unité mémoire 106, et donc que le MSB du mot binaire soit reçu en premier et que le LSB du mot binaire soit reçu en dernier sur l'entrée de l'unité mémoire 106.

[0073] Le chronogramme représenté sur la figure 4 correspond aux signaux de sélection, de mémorisation et d'affichage envoyés par l'unité de séquencement 108 à l'unité mémoire 106 dans cette première configuration. A un instant t0, une impulsion du signal d'affichage déclenche le décalage du MSB du mot binaire de la première image de la bascule 112.N dans la bascule 112.N+1. Le pixel 102 envoi ou non, pendant la durée correspondant à ce MSB (correspondant à l'intervalle de temps entre les instants t0 et t4 représentés sur la figure 4), un signal lumineux. Pendant cette durée d'affichage du MSB du mot binaire de la première image, à l'instant t1, le signal de sélection change de valeur afin que le signal de mémorisation soit transmis sur les entrées de commande des N bascules 112.1 à 112.N. Toujours pendant cette durée d'affichage du MSB du mot binaire de la première image, à l'instant t2, le signal de mémorisation comporte 8 impulsions déclenchant la mémorisation, dans les N bascules 112.N à 112.1, des 7 bits restants (du MSB-1 au LSB) du mot binaire de la première image ainsi que du MSB du mot binaire de la deuxième image. Le MSB-1 du mot binaire de la première image est mémorisé dans la bascule 112.N, le LSB du mot binaire de la première image est mémorisé dans la bascule 112.2, et le MSB du mot binaire de la deuxième image est mémorisé dans la bascule 112.1. A un instant t3, le signal de sélection change de valeur afin que le signal d'affichage soit de nouveau transmis sur les entrées de commande des N bascules 112.1 à 112.N. Des impulsions du signal d'affichage apparaissant aux instants t4 à t10 provoquent le décalage des bits stockés dans les bascules 112.1 à 112.N afin que chacun de ces bits se retrouve stocké dans la bascule 112.N+1 pendant la durée correspondant au poids de chacun de ces bits (du MSB-1 au LSB). A partir de l'instant t10, la séquence des signaux décrite ci-dessus recommence en utilisant les mots binaires de l'image suivante.

[0074] Selon une deuxième configuration du dispositif 100 comportant l'unité mémoire représentée sur la figure 3, les signaux d'affichage et de mémorisation peuvent être tels que pendant au moins une partie de l'affichage d'un bit du mot binaire d'une première image, ici le MSB de ce mot binaire, la mémorisation des N bits du mot binaire de la deuxième image destinée à être affichée après la première image est déclenchée. Dans cette deuxième configuration, les mots binaires reçus par les pixels 102 sont tels que les N bits de chaque mot binaire envoyés successivement, en série, à l'entrée de l'unité mémoire 106, sont ordonnés tels que le poids des bits reçus soit croissant avec l'ordre d'arrivée sur l'entrée de l'unité mémoire 106, et donc que le LSB du mot binaire soit reçu en premier et que le MSB du mot binaire soit reçu en dernier sur l'entrée de l'unité mémoire 106.

[0075] Le chronogramme représenté sur la figure 5 correspond aux signaux de sélection, de mémorisation et d'affichage envoyés par l'unité de séquencement 108 à l'unité mémoire 106 dans cette première configuration. Dans cette configuration, avant l'instant t0, les N bits du mot binaire de la première image sont mémorisés dans les bascules 112.1 à 112.N. Des impulsions du signal d'affichage apparaissant aux instants t0 à t6 provoquent le décalage des bits stockés dans les bascules 112.1 à 112.N afin que chacun de ces bits se retrouve stocké dans la bascule 112.N+1 pendant la durée correspondant au poids de chacun de ces bits (du LSB au MSB-1). A l'instant t7, une impulsion du signal d'affichage déclenche le décalage du MSB du mot binaire de la première image de la bascule 112.N dans la bascule 112.N+1. Pendant cette durée d'affichage du MSB du mot binaire de la première image, à l'instant t8, le signal de sélection change de valeur afin que le signal de mémorisation soit transmis sur les entrées de commande des N bascules 112.1 à 112.N. Toujours pendant cette durée d'affichage du MSB du mot binaire de la première image, à l'instant t9, le signal de mémorisation comporte 8 impulsions déclenchant la mémorisation, dans les N bascules 112.N à 112.1, des 8 bits (du LSB au MSB) du mot binaire de la deuxième image. Le LSB du mot binaire de la deuxième image est mémorisé dans la bascule 112.N et le MSB du mot binaire de la deuxième image est mémorisé dans la bascule 112.1. A l'instant t10, le signal de sélection change de valeur afin que le signal d'affichage soit de nouveau transmis sur les entrées de commande des N bascules 112.1 à 112.N. A partir de l'instant t10, la séquence des signaux décrite ci-dessus recommence en utilisant les mots binaires de l'image suivante dont les N bits seront mémorisés lors de l'affichage du MSB de la deuxième image.

[0076] En variante du premier mode de réalisation décrit ci-dessus, l'unité mémoire 106 de chaque pixel 102 peut comporter un nombre de bascules 112 inférieur à N+1 et supérieur ou égal à 3.

[0077] A titre d'exemple, en considérant des mots binaires identiques à ceux précédemment décrits, c'est-àdire comportant chacun 8 bits, l'unité mémoire 106 de

40

45

20

25

40

45

chaque pixel 102 peut comporter 5 bascules 112.1 à 112.5. Dans ce cas, lors de l'affichage du 1<sup>er</sup> bit (par exemple le MSB) mémorisé dans la dernière bascule 112.5, les quatre bits suivants (2ème, 3ème, 4ème et 5ème bits du mot binaire) sont mémorisés dans les quatre autres bascules 112.1 à 112.4. Ensuite, après l'affichage des 2ème, 3ème et 4ème bits du mot binaire, et lors de l'affichage du 5ème bit qui est alors mémorisé dans la dernière bascule 112.5, les trois derniers bits du mot binaire ainsi que le 1<sup>er</sup> bit du mot binaire de l'image suivante sont mémorisés dans les quatre bascules 112.1 à 112.4. Dans cet exemple, les bits de chaque mot binaire sont donc mémorisés au cours de deux phases successives de mémorisation.

[0078] L'exemple de réalisation donné ci-dessus peut être appliqué pour un nombre différent de bascules 112 et/ou pour des mots binaires ayant un nombre différent de bits. Cet exemple peut s'appliquer autant pour des mots binaires où le premier bit reçu dans l'unité mémoire 106 correspond au bit de poids fort que pour des mots binaires où le premier bit reçu dans l'unité mémoire 106 correspond au bit de poids faible, ou tout autre ordre d'arrivée des bits.

[0079] Dans le premier mode de réalisation décrit cidessus, l'unité d'affichage 104 comporte une seule diode électroluminescente et l'unité mémoire 106 comprend une seule entrée configurée pour recevoir les mots binaires des images à afficher et trois entrées de commande sur lesquelles sont reçus le signal d'affichage, le signal de mémorisation et le signal de sélection.

**[0080]** La figure 6 représente un exemple de réalisation de l'unité mémoire 106 de chaque pixel 102 du dispositif 100 selon un deuxième mode de réalisation.

**[0081]** Comme dans le premier exemple de réalisation représenté sur la figure 3, l'unité mémoire 106 comporte les N+1 bascules 112.

[0082] Les signaux d'affichage et de mémorisation sont combinés pour former un seul et même signal d'affichage et de mémorisation. Cette combinaison est par exemple réalisée par une porte OU 116 recevant sur chacune de ses deux entrées l'un des signaux d'affichage et de mémorisation. La porte OU 116 peut être formée au sein de l'unité de séquencement 108 ou en dehors de l'unité de séquencement 108. Le signal d'affichage et de mémorisation obtenu en sortie de la porte OU 116 est envoyé à une entrée de commande de chacune des N premières bascules 112.1 à 112.N. Ici, seule l'entrée de commande de la dernière des N+1 bascules 112.N+1 ne reçoit pas le signal d'affichage et de mémorisation.

[0083] L'unité mémoire 106 comporte également un multiplexeur 118 comprenant deux entrées de données dont l'une reçoit le signal d'affichage et de mémorisation et dont l'autre est couplée à un potentiel électrique de référence, par exemple la masse appelée GND. Le multiplexeur 118 comporte également une entrée de commande couplée à la troisième sortie de l'unité de séquencement sur laquelle le signal de sélection est envoyé. La sortie du multiplexeur 118 est couplée à l'entrée de com-

mande de la dernière bascule 112.N+1.

[0084] Comme dans le premier mode de réalisation, l'unité d'affichage 104 comporte ici une seule diode électroluminescente et l'unité mémoire 106 comprend une seule entrée configurée pour recevoir les mots binaires des images à afficher.

[0085] Pendant la phase d'affichage des bits LSB à MSB-1, le signal d'affichage et de mémorisation est envoyé sur l'entrée de contrôle des N+1 bascules 112 et les impulsions issues du signal d'affichage initial qui sont reçues par les bascules 112.1 à 112.N+1 décalent les bits stockés dans ces bascules dans le sens allant de la première bascule 112.1 à la dernière bascule 112.N+1 afin que chacun de ces bits soient affichés pendant une durée correspondant à leur poids respectif. Pendant la durée d'affichage du MSB, le signal de sélection change de valeur afin que l'entrée de commande de la dernière bascule 112.N+1 ne reçoive plus le signal d'affichage et de mémorisation mais reçoive le potentiel électrique de référence appliqué sur l'autre entrée du multiplexeur 118. Les impulsions issues du signal de mémorisation initial et se trouvant dans le signal d'affichage et de mémorisation sont alors appliquées sur les N premières bascules 112.1 à 112.N afin de déclencher la mémorisation, dans ces bascules, des bits suivants à afficher. La séquence décrite ci-dessus recommence ensuite en utilisant les mots binaires de l'image suivante.

[0086] La figure 7 représente le signal de sélection et le signal d'affichage et de mémorisation lors de l'affichage d'une image, lorsque les mots binaires reçus par les pixels 102 sont tels que les N bits de chaque mot binaire envoyés successivement, en série, à l'entrée de l'unité mémoire 106, sont ordonnés tels que le poids des bits reçus soit croissant avec l'ordre d'arrivée sur l'entrée de l'unité mémoire 106, et donc que le LSB du mot binaire soit reçu en premier et que le MSB du mot binaire soit reçu en dernier sur l'entrée de l'unité mémoire 106.

[0087] Comme dans le premier mode de réalisation, ce deuxième mode de réalisation est compatible avec des mots binaires tels que les N bits de chaque mot binaire envoyés successivement, en série, à l'entrée de l'unité mémoire 106, sont ordonnés tels que le poids des bits reçus soit décroissant avec l'ordre d'arrivée sur l'entrée de l'unité mémoire 106, et donc que le MSB du mot binaire soit reçu en premier et que le LSB du mot binaire soit reçu en dernier sur l'entrée de l'unité mémoire 106. [0088] Dans le deuxième mode de réalisation décrit cidessus, le signal d'affichage et de mémorisation est obtenu en réalisant une opération logique OU entre le signal d'affichage et le signal de mémorisation au sein de l'unité de séguencement 108. Ainsi, l'unité mémoire 106 comprend seulement deux entrées de commande sur lesquelles sont reçues le signal d'affichage et de mémorisation, et le signal de sélection.

**[0089]** En variante, l'opération logique permettant l'obtention du signal d'affichage et de mémorisation pourrait être réalisée au sein des pixels 102, ou bien être obtenu à partir du signal d'affichage et du signal de mémorisation

15

en utilisant un ou plusieurs éléments autres qu'une porte OU, dans l'unité de séquencement 108 ou en dehors de l'unité de séquencement 108.

**[0090]** En variante, l'unité mémoire 106 de chaque pixel 102 peut comporter un nombre de bascules 112 inférieur à N+1 et supérieur ou égal à 3, comme cela a été précédemment décrit pour le premier mode de réalisation.

[0091] Selon une variante des deux modes de réalisation précédemment décrits en lien avec les figures 3 et 6, il est possible, dans l'unité mémoire 106 du pixel 102, de coupler la sortie de la dernière des N premières bascules 112.N à l'entrée de la première bascule 112.1 par l'intermédiaire d'un interrupteur 120 commandé par l'unité de séquencement 108, via un signal de boucle appliqué sur l'interrupteur 120, qui est configurée pour fermer l'interrupteur 120 lorsque le mot binaire de l'image affichée est similaire au mot binaire de l'image suivante à afficher. Lorsque l'interrupteur 120 est en position fermée que les impulsions du signal de mémorisation sont appliquées sur les entrées de commandes des bascules 112.1 à 112.N, les valeurs mémorisées dans les bascules 112.1 à 112.N sont successivement mémorisées à la fois dans la dernière bascule 112.N+1 mais sont également recopiées dans les bascules 112.1 à 112.N. La figure 8 représente une telle variante appliquée au deuxième mode de réalisation précédemment décrit en lien avec la figure 6.

**[0092]** La figure 9 représente un exemple de réalisation de l'unité mémoire 106 de chaque pixel 102 du dispositif 100 selon un troisième mode de réalisation.

[0093] Dans ce troisième mode de réalisation, l'unité mémoire 106 de chaque pixel 102 comporte N premières bascules 122.1 à 122.N couplées en série les unes aux autres. Une entrée de données d'une première des N premières bascules 122.1 est couplée à une entrée du pixel 102 destinée à recevoir les mots binaires des images à afficher.

[0094] L'unité mémoire 106 comporte également N deuxièmes bascules 124.1 à 124.N couplées en série les unes aux autres. Une entrée de données d'une première des N deuxièmes bascules 124.1 est couplée à l'entrée du pixel 102.

[0095] Comme dans les précédents modes de réalisation, l'unité d'affichage 104 comprend ici une seule diode électroluminescente et l'unité mémoire 106 comprend ici une seule entrée configurée pour recevoir les mots binaires des images à afficher.

[0096] L'unité mémoire 106 comporte également un circuit de commutation 126 comprenant deux entrées de données couplées à l'unité de séquencement 108. Une première de ces deux entrées de données est destinée à recevoir le signal d'affichage et une deuxième de ces deux entrées de données est destinée à recevoir le signal de mémorisation. Le circuit de commutation 126 comporte également une entrée de commande couplée à la troisième sortie de l'unité de séquencement 108 sur laquelle le signal de sélection est destiné à être envoyé.

Le circuit de commutation 126 comporte également une première sortie couplée à une entrée de commande de chacune des N premières bascules 122.1 à 122.N et une deuxième sortie couplée à une entrée de commande de chacune des N deuxièmes bascules 124.1 à 124.N. Ce circuit de commutation 126 est tel qu'en fonction de la valeur du signal de sélection appliqué sur son entrée de commande, le circuit 126 se trouve dans l'une des deux configurations suivantes :

- la première sortie est couplée à la première entrée de données et la deuxième sortie est couplée à la deuxième entrée de données, ou

- la première sortie est couplée à la deuxième entrée de données et la deuxième sortie est couplée à la première entrée de données.

[0097] L'unité mémoire 106 comporte en outre un multiplexeur 128 comprenant deux entrées de données dont l'une est couplée à la sortie d'une dernière des N premières bascules 122.N et dont l'autre est couplée à la sortie d'une dernière des N deuxièmes bascules 124.N. Le multiplexeur 128 comporte également une entrée de commande couplée à la troisième sortie de l'unité de séquencement sur laquelle le signal de sélection est délivré, et une sortie couplée à l'entrée de l'unité d'affichage 104.

[0098] Dans une telle configuration, les signaux envoyés par l'unité de séquencement 108 sont tels que lorsque les N premières bascules 122 reçoivent sur leurs entrées de commande le signal d'affichage, la sortie du multiplexeur 128 est couplée à l'entrée de données qui est couplée à la sortie de la dernière de N premières bascules 122.N. Ainsi les bits mémorisés dans les N premières bascules 122 sont affichés successivement par l'unité d'affichage 104 sur la commande des impulsions du signal d'affichage. Pendant l'affichage d'un ou plusieurs des bits mémorisés dans les N premières bascules 122, le circuit de commutation 126 envoie le signal de mémorisation sur les entrées de commande des N deuxièmes bascules 124 qui mémorisent les bits du mot binaire appliqué sur l'entrée de la première des N deuxièmes bascules 124.1.

[0099] A l'issu de l'affichage des N bits mémorisés dans les N premières bascules 122, le signal de sélection change de valeur, inversant ainsi le rôle des N premières bascules 122 et des N deuxièmes bascules 124. Les N deuxièmes bascules 124 reçoivent sur leurs entrées de commande le signal d'affichage, et la sortie du multiplexeur 128 est couplée à l'entrée de données qui est couplée à la sortie de la dernière de N deuxièmes bascules 124.N. Ainsi les bits mémorisés dans les N deuxièmes bascules 124 sont affichés successivement par l'unité d'affichage 104 sur la commande des impulsions du signal d'affichage. Pendant l'affichage d'un ou plusieurs des bits mémorisés dans les N deuxièmes bascules 124, le circuit de commutation 126 envoie le signal de mémorisation sur les entrées de commande des N

20

25

30

35

45

premières bascules 122 qui mémorisent les bits du mot binaire appliqué sur l'entrée de la première des N premières bascules 122.1.

**[0100]** A l'issu de l'affichage des N bits mémorisés dans les N deuxièmes bascules 124, le signal de sélection change à nouveau de valeur, inversant le rôle des N premières bascules 122 et des N deuxièmes bascules 124.

**[0101]** Les N premières bascules 122 et les N deuxièmes bascules 124 remplissent donc alternativement le rôle de mémoire dans laquelle les bits du mot binaire d'une prochaine image à afficher sont mémorisés et le rôle de mémoire depuis laquelle les bits du mot binaire d'une image à afficher sont envoyés à l'unité d'affichage 104.

[0102] Comme dans les précédents modes de réalisation, ce troisième mode de réalisation est compatible avec des mots binaires tels que les N bits de chaque mot binaire envoyés successivement, en série, à l'entrée de l'unité mémoire 106, sont ordonnés tels que le poids des bits reçus soit décroissant avec l'ordre d'arrivée sur l'entrée de l'unité mémoire 106, et donc que le MSB du mot binaire soit reçu en premier et que le LSB du mot binaire soit reçu en dernier sur l'entrée de l'unité mémoire 106, ou tels que le poids des bits reçus soit croissant avec l'ordre d'arrivée sur l'entrée de l'unité mémoire 106, et donc que le LSB du mot binaire soit reçu en premier et que le MSB du mot binaire soit reçu en premier et que le MSB du mot binaire soit reçu en dernier sur l'entrée de l'unité mémoire 106.

**[0103]** En variante, l'unité mémoire 106 de chaque pixel 102 peut comporter moins de 2.N bascules 122, 124, avec au moins deux premières bascules 122 et au moins deux deuxièmes bascules 124, comme précédemment décrit en lien avec le premier mode de réalisation.

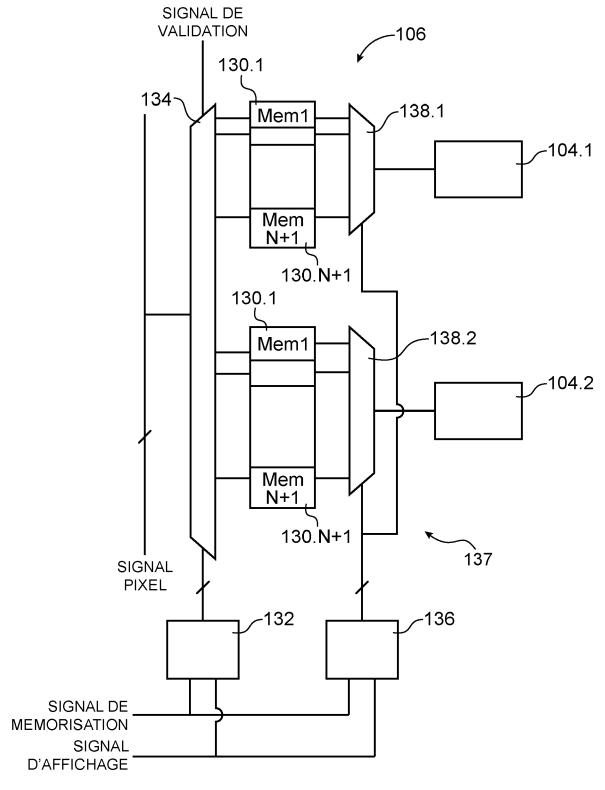

**[0104]** La figure 10 représente un exemple de réalisation de l'unité mémoire 106 de chaque pixel 102 du dispositif 100 selon un quatrième mode de réalisation.

**[0105]** L'unité mémoire 106 comporte N+1 éléments mémoires 130.

[0106] L'unité mémoire 106 comporte également un premier circuit d'adressage 133 comprenant une entrée de donnée couplée à une entrée du pixel 102 destinée à recevoir les mots binaires des images à afficher, N+1 sorties chacune couplée à une entrée de l'un des N+1 éléments mémoires 130, et au moins une entrée de commande couplée à au moins une première sortie de l'unité de séquencement 108 sur laquelle le signal de mémorisation est destiné à être délivré.

[0107] Selon une première configuration correspondant à celle représentée sur la figure 10, le premier circuit d'adressage 133 comporte un premier générateur d'adresse 132 comprenant une entrée couplée à la première sortie de l'unité de séquencement 108 sur laquelle le signal de mémorisation est destiné à être délivré.

[0108] Le premier circuit d'adressage 133 comporte en outre un démultiplexeur 134 comprenant une entrée de donnée couplée à l'entrée du pixel 102 destinée à

recevoir les mots binaires des images à afficher, N+1 sorties chacune couplée à une entrée de l'un des N+1 éléments mémoires 130, et une entrée de commande couplée à une sortie du premier générateur d'adresse 132. Dans cet exemple de réalisation particulier, le démultiplexeur 134 comporte également une deuxième entrée de commande sur laquelle un signal de validation est appliquée, autorisant ou non le transfert de données depuis l'entrée du démultiplexeur 134 jusqu'à une sortie du démultiplexeur 134.

[0109] L'unité mémoire 106 comporte également un deuxième circuit d'adressage 137 comprenant N+1 entrées de donnée chacune couplée à une sortie de l'un des N+1 éléments mémoires 130, une sortie couplée à une entrée de l'unité d'affichage 104, et au moins une entrée de commande couplée à au moins une deuxième sortie de l'unité de séquencement 108 sur laquelle le signal d'affichage est destiné à être délivré.

[0110] Selon la première configuration, le deuxième circuit d'adressage 137 comporte un deuxième générateur d'adresse 136 comprenant une entrée couplée à la deuxième sortie de l'unité de séquencement 108 sur laquelle le signal d'affichage est destiné à être délivré.

[0111] Le deuxième circuit d'adressage 137 comporte également un multiplexeur 138 comprenant N+1 entrées de donnée chacune couplée à une sortie de l'un des N+1 éléments mémoires 130, une sortie couplée à l'entrée de l'unité d'affichage 104, et une entrée de commande couplée à une sortie du deuxième générateur d'adresse 136.

**[0112]** Comme dans les précédents modes de réalisation, l'unité d'affichage 104 comporte une diode électroluminescente et l'unité mémoire 106 comprend une seule entrée configurée pour recevoir les mots binaires des images à afficher.

[0113] Avec une telle unité mémoire 106, lors de la mémorisation d'un des N bits d'un mot binaire déclenchée par le signal de mémorisation, le premier générateur d'adresse 132 délivre au démultiplexeur 134 un premier signal d'adresse codant sur plusieurs bits l'adresse de l'un des N+1 éléments mémoires 130 dans lequel ledit un des N bits du mot binaire est mémorisé. En outre, lors de l'affichage d'un des N bits d'un mot binaire déclenché par le signal d'affichage, le deuxième générateur d'adresse 136 délivre au multiplexeur 138 un deuxième signal d'adresse codant sur plusieurs bits l'adresse de l'un des N+1 éléments mémoires 130 depuis lequel un des N bits du mot binaire est lu. Comme dans les précédents exemples de réalisation, la mémorisation des bits d'un mot binaire d'une image à afficher est réalisée pendant l'affichage d'un bit par l'unité d'affichage, voire pendant l'affichage de plusieurs bits par l'unité d'affichage comme c'est le cas pour le troisième mode de réalisation précédemment décrit.

**[0114]** Les premier et deuxième générateurs d'adresse 132, 136 correspondent par exemple à des générateurs pseudo-aléatoires configurés pour délivrer des signaux codés sur plusieurs bits correspondant aux adresser

ses des éléments mémoires 130.

[0115] Selon une deuxième configuration, il est possible que l'unité de séquencement 108 soit configurée telle que le signal de mémorisation soit formée de plusieurs premiers signaux d'adressage commandant chacun une mémorisation dans l'un des éléments mémoires 130. Dans ce cas, le premier circuit d'adressage 133 ne comporte pas le premier générateur d'adresse 132 puisque l'adressage en écriture est réalisé directement par ces premiers signaux d'adressage.

[0116] Dans cette deuxième configuration, l'unité de séquencement 108 peut être configurée telle que le signal d'affichage soit formé de plusieurs deuxièmes signaux d'adressage commandant chacun une lecture d'un bit mémorisé dans l'un des éléments mémoires 130. Dans ce cas, le deuxième circuit d'adressage 137 ne comporte pas le deuxième générateur d'adresse 136 puisque l'adressage en lecture est réalisé directement par les deuxièmes signaux d'adressage.

**[0117]** Cette deuxième configuration permet d'économiser la surface active occupée par les premier et deuxième générateurs d'adresse 132, 136, avec toutefois pour contrepartie d'augmenter le nombre d'interconnexions reliées aux pixels 102.

[0118] Selon une troisième configuration, le premier circuit d'adressage 133 peut comporter un premier compteur comprenant une entrée couplée à la première sortie de l'unité de séquencement 108, et un premier décodeur d'adresse comprenant une entrée de donnée couplée à l'entrée du pixel 102 destinée à recevoir les mots binaires, plusieurs sorties chacune couplée à l'entrée d'un des éléments mémoires 130, et une entrée de commande couplée à une sortie du premier compteur. De manière analogue, le deuxième circuit d'adressage 137 comporte un deuxième compteur comprenant une entrée couplée à la deuxième sortie de l'unité de séquencement 108, un deuxième décodeur d'adresse comprenant plusieurs entrées de donnée chacune couplée à la sortie d'un des éléments mémoires 130, une sortie couplée à l'entrée de l'unité d'affichage 104, et une entrée de commande couplée à une sortie du deuxième compteur.

**[0119]** Les différentes configurations du quatrième mode de réalisation peuvent être combinées entre elles, c'est-à-dire que le premier circuit d'adressage 133 peut être réalisé selon l'une des première, deuxième et troisième configurations, et le deuxième circuit d'adressage 137 peut être réalisé selon une autre de ces trois configurations.

**[0120]** Ce quatrième mode de réalisation a pour avantage de permettre le choix de l'ordre dans lequel la lecture et l'écriture sont réalisés dans les éléments mémoires 130.

[0121] Comme dans les précédents modes de réalisation, ce quatrième mode de réalisation est compatible avec des mots binaires tels que les N bits de chaque mot binaire envoyés successivement, en série, à l'entrée de l'unité mémoire 106, sont ordonnés tels que le poids des bits reçus soit décroissant avec l'ordre d'arrivée sur l'en-