(19)

Europäisches

Patentamt

European

Patent Office

Office européen

des brevets

(11)

EP 3 579 332 A1

(12)

## EUROPEAN PATENT APPLICATION

(43) Date of publication:

11.12.2019 Bulletin 2019/50

(51) Int Cl.:

*H01P 3/16 (2006.01)*      *H01P 5/08 (2006.01)*

(21) Application number: 18176342.6

(22) Date of filing: 06.06.2018

(84) Designated Contracting States:

**AL AT BE BG CH CY CZ DE DK EE ES FI FR GB

GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO

PL PT RO RS SE SI SK SM TR**

Designated Extension States:

**BA ME**

Designated Validation States:

**KH MA MD TN**

(71) Applicant: **IMEC vzw**

**3001 Leuven (BE)**

(72) Inventor: **Ocket, Mr. Ilja**

**3001 Leuven (BE)**

(74) Representative: **Patent Department IMEC**

**IMEC vzw**

**Patent Department**

**Kapeldreef 75**

**3001 Leuven (BE)**

### (54) A WAVEGUIDE INTERCONNECT

(57) The present disclosure relates to a waveguide interconnect made of dielectric layer and a method thereof. The waveguide interconnect comprises at least one pair of elongated through-holes with a longitudinal axis

parallel to one another, thereby forming an elongated stripe of dielectric layer extending in the direction of longitudinal axis and such that the dielectric layer in between the elongated through-holes forms a waveguide.

FIG.1A

## Description

### Technical field

**[0001]** The present disclosure relates to a waveguide interconnect for interfacing a chip to other components. Furthermore, the present disclosure relates to a method for making such waveguide interconnect.

### Background

**[0002]** Two main technical challenges need to be tackled in order for dielectric waveguides to become a viable option for chip-to-chip as well as chip-to-component interconnects. The first is the integration/assembly of dielectric waveguides and their couplers into standard manufacturing processes, for example standard Printed Circuit Board (PCB) processes. The second is related to the field confinement of the waveguide mode, which is crucial especially when used as a cable substitute, but also relevant for board level integration when e.g. multiple parallel communication channels are desired without excessive crosstalk.

### Summary

**[0003]** The present disclosure aims at providing a waveguide interconnect which can be easily integrated with a support element, such as a PCB, a metal waveguide split-block assembly or a glass substrate. Additionally, the waveguide interconnect can form an integral part of a flexible PCB, silicon or a glass substrate. This obviates the need to fabricate the waveguide separately from the substrate and then assemble it together, for example, after PCB fabrication. Moreover, it allows low-cost fabrication as standard manufacturing technologies can be used to produce the interconnect and hence mass production becomes possible. Finally, this integration approach ensures precise alignment of the waveguide to the coupler and thus well-controlled mode conversion performance. The waveguide interconnect can be used for interfacing a chip to other components, such as chip-to-chip, chip-to-antenna, chip to rigid hollow metal waveguide, chip to on-wafer probe, chip to remote sensor probe, etc. Additionally, the waveguide interconnect can be directly connected to the analog front-end circuitry of the chip, given that the waveguide coupler is realized in the same metal layer as where the chip solder balls are attached to.

**[0004]** This object is achieved according to the disclosure with a waveguide interconnect made of a dielectric layer and comprising a pair of elongated through-holes with a longitudinal axis parallel to one another, thereby forming an elongated stripe of dielectric layer extending in the direction of longitudinal axis and such that the dielectric stripe in between the elongated through-holes forms a waveguide.

**[0005]** Depending on the application, the waveguide

is dimensioned to propagate signals within certain frequencies range, such as communication signals with base frequency or radio frequency signals. Depending on the frequency range of the signals, the width of the waveguide is varied. The length of the waveguide is defined by the distance between the chip and the component. For example, the proposed waveguide interconnect can replace a baseband copper bus on a PCB thereby providing a smaller and cheaper PCB.

**[0006]** In one embodiment of the present disclosure, the waveguide interconnect comprises at each end of the dielectric waveguide a coupler for coupling the dielectric waveguide to a passive or an active module which is provided by printing or depositing a metal layer on a surface of the dielectric layer.

**[0007]** The coupler design determines how much of the signal is transferred from the waveguide to a module and vice versa thus providing a flexible design depending on the relative fraction of the signal required for transferal to and from a module.

**[0008]** An active module can be a semiconductor chip such as a radio or a radar. A passive module can be for example an antenna or a sensor. When the waveguide is used to couple an active module to a passive module, such as antenna or a sensor, the waveguide is used for communicating RF signals to and from the antenna. In some embodiments, the passive module may also be located on another planar PCB or on a metal waveguide structure. When coupling active modules, such as chips, the waveguide is used for chip-to-chip communication.

**[0009]** By printing or depositing a metal layer over the dielectric layer, the coupler structure is easily integrated into the waveguide interconnect using standard manufacturing processes.

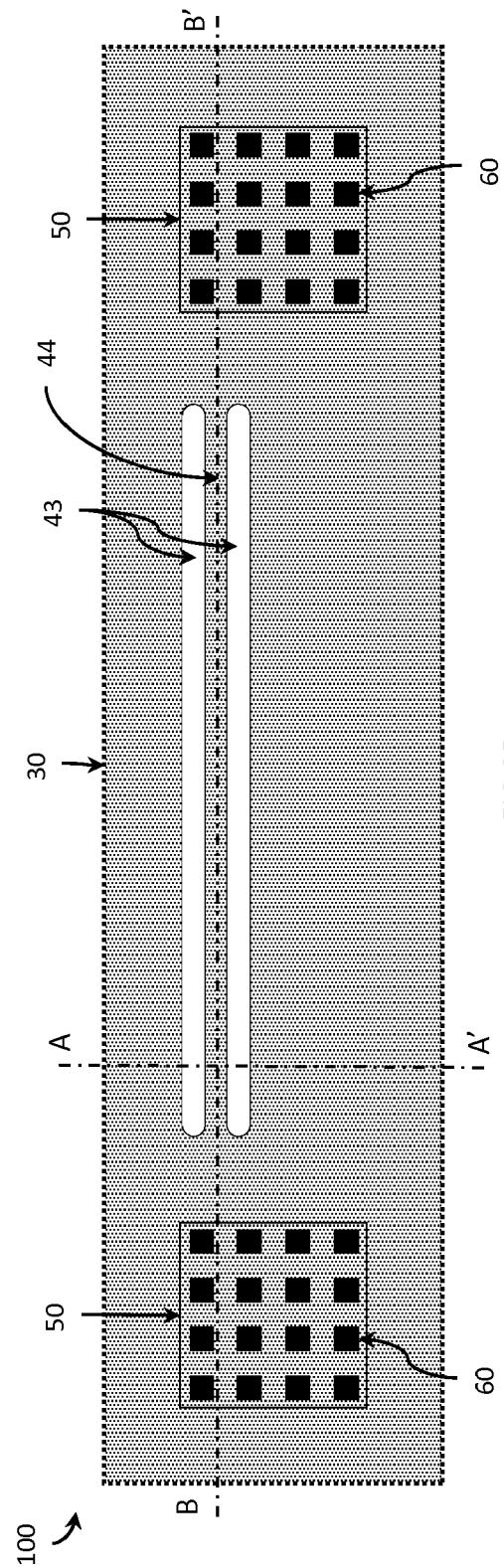

**[0010]** Possible coupler topologies include Vivaldi-style, differential dipole, loop, or a metal horn placed around the waveguide, or a combination of the above to launch one or multiple modes in the waveguide. A coupler such as a planar Vivaldi-style coupler with elliptical tapering is preferred as it allows for easy printing or depositing using standard manufacturing processes and offers a wide bandwidth and good mode field match.

**[0011]** In an embodiment of the present disclosure, the dielectric layer is flexible. The dielectric layer may be made of a polyimide, a liquid crystal polymer or polypropylene. Preferably, a low-loss polymer such as PTFE is used.

**[0012]** The flexible waveguide interconnect increases the design options depending on the specific structure in which the waveguide interconnect needs to be installed. The waveguide interconnect can be bent with radii of curvature to a certain extent without introducing excessive bending loss. For example, at 100 GHz a bending radius of 30 cm can be tolerated. This value for the tolerable bending radius scales inversely proportional to the operating frequency.

**[0013]** In other embodiments of the present disclosure, the waveguide interconnect is provided on top of a first

support element or between a first and a second support elements and arranged so that a continuous air channel enclosing the waveguide is provided. The support element may be a glass or Printed Circuit Board (PCB) substrate.

**[0014]** In further embodiments of the present disclosure, the dielectric layer comprises at least one through-hole around each end of the dielectric waveguide for attaching and/or positioning the dielectric layer to the first support element or to the first and second support elements.

**[0015]** The though-hole provides an easy way of attaching and positioning the waveguide interconnect to the support element(s).

**[0016]** In an embodiment of the present disclosure, at least one through-hole extends into and through at least one of the support elements.

**[0017]** The extended through-hole serves to align the waveguide within for example a two-part metal enclosing structure for clamping the waveguide, but also serves as an electromagnetic shielding structure to avoid radiation loss from the coupler to the waveguide.

**[0018]** In certain embodiments of the present disclosure, the waveguide interconnect may comprise one or more waveguides which may have different length and/or width. The waveguides may be dimensioned so that propagation of signals with different frequencies, such as communication signals or radio frequency signals, is possible. Depending on the frequency range of the signals to be propagated, the width of the waveguide can be varied. The width of the waveguide is inversely proportional to the frequency of operation. For example, for operation in the 100 GHz range, the width of the waveguide will be in the range of 3 mm, for operation in the 1 THz range the waveguide width will be in the 300 micron range. The length, as mentioned above, is defined by the distance between the chip and the component.

**[0019]** By providing multiple waveguides for the propagation of signals with different frequency range, the waveguide interconnect can be used both as a communication and a data interconnect.

**[0020]** In an embodiment of the present disclosure, at least one metal line is provided by printing or depositing a metal layer on a surface of the dielectric layer.

**[0021]** By printing or depositing metal lines on the dielectric layer, the interconnect can in addition to the above be used for baseband I/O signaling and electrical power distribution.

**[0022]** Another object of the present disclosure relates to a method for making a waveguide interconnect, the method comprising a) providing a layer of a dielectric material and b) cutting in the dielectric layer at least one pair of elongated through-holes with a longitudinal axis parallel to one another thereby forming a waveguide.

**[0023]** The method uses standard manufacturing process steps which allows for a cheap and easy production of a waveguide interconnect.

**[0024]** In an embodiment of the present disclosure, the

method further comprises providing at each end of the waveguide a coupler for coupling the waveguide to a passive or an active module by printing or depositing a metal layer on a surface of the dielectric layer.

**[0025]** In embodiments of the present disclosure, step a) of the method further comprises providing the dielectric layer on a first support element or between a first and a second support elements and wherein step b) further comprises removing the support elements around the at least one formed waveguide, thereby forming a continuous air channel enclosing the formed waveguide. Depending on the material, the support element may be removed by methods such as laser cutting, stamping, mechanical milling/routing, chemical or reactive ion etching and others.

**[0026]** In an embodiment of the present disclosure, the support element is a glass substrate, Printed Circuit Board (PCB) substrate or silicon substrate.

**[0027]** This method has the same advantages as the waveguide interconnect discussed above.

### Brief description of the drawings

**[0028]** For a better understanding of the present disclosure, some exemplary embodiments are described below in conjunction with the appended FIG.1 and FIG.5 description, wherein:

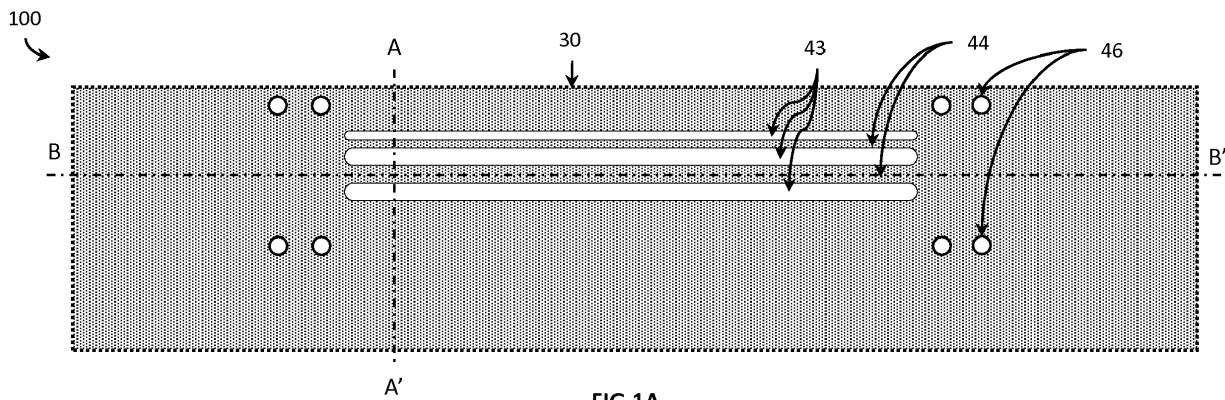

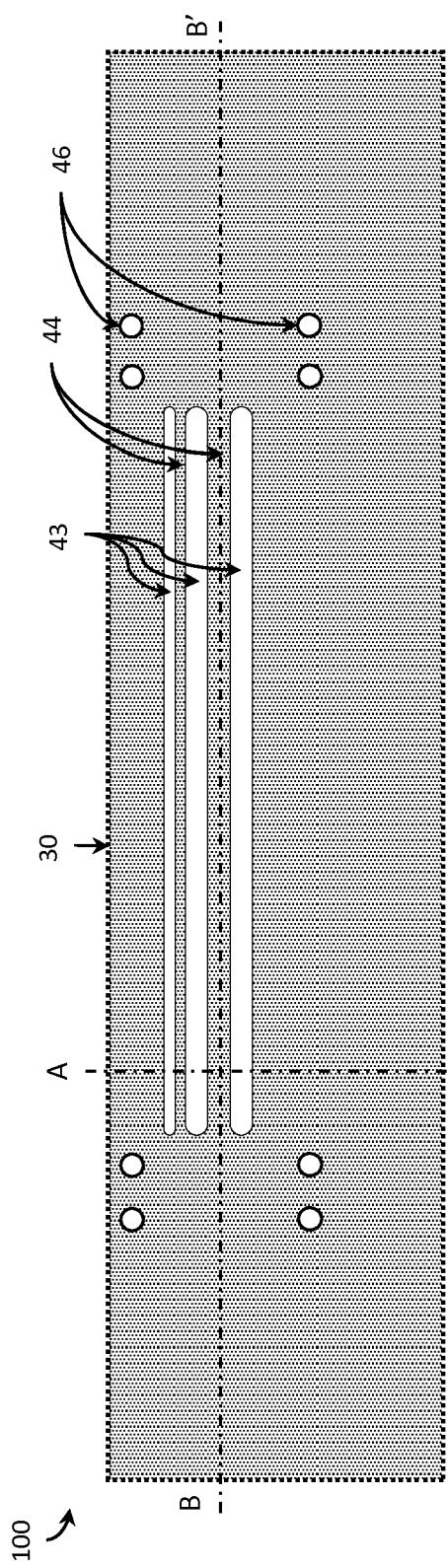

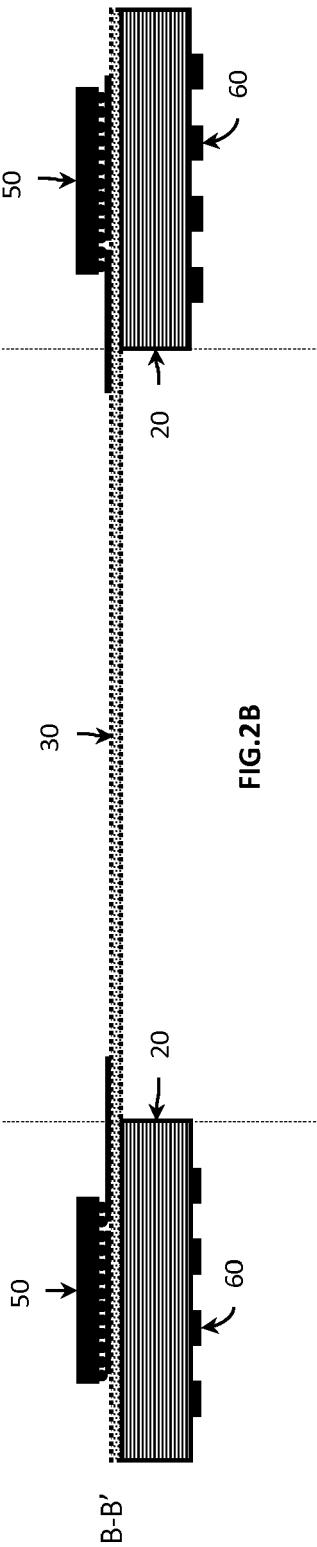

**[0029]** FIG.1 illustrates a top view and cross-sectional views along B-B' and A-A' of a waveguide interconnect of FIG.1 provided on a top of a support element, respectively.

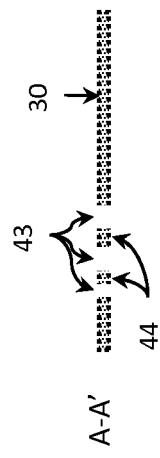

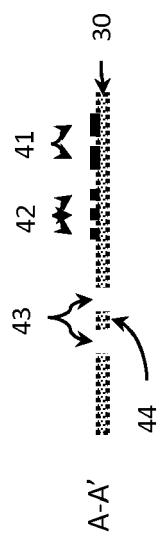

**[0030]** FIG.2 illustrates a top view, cross-sectional views along B-B' and A-A' and a bottom view of a multichip arrangement employing the proposed waveguide interconnect as a chip-to-chip interconnect.

**[0031]** FIG.3 illustrates a planar Vivaldi-style coupler with elliptical tapering.

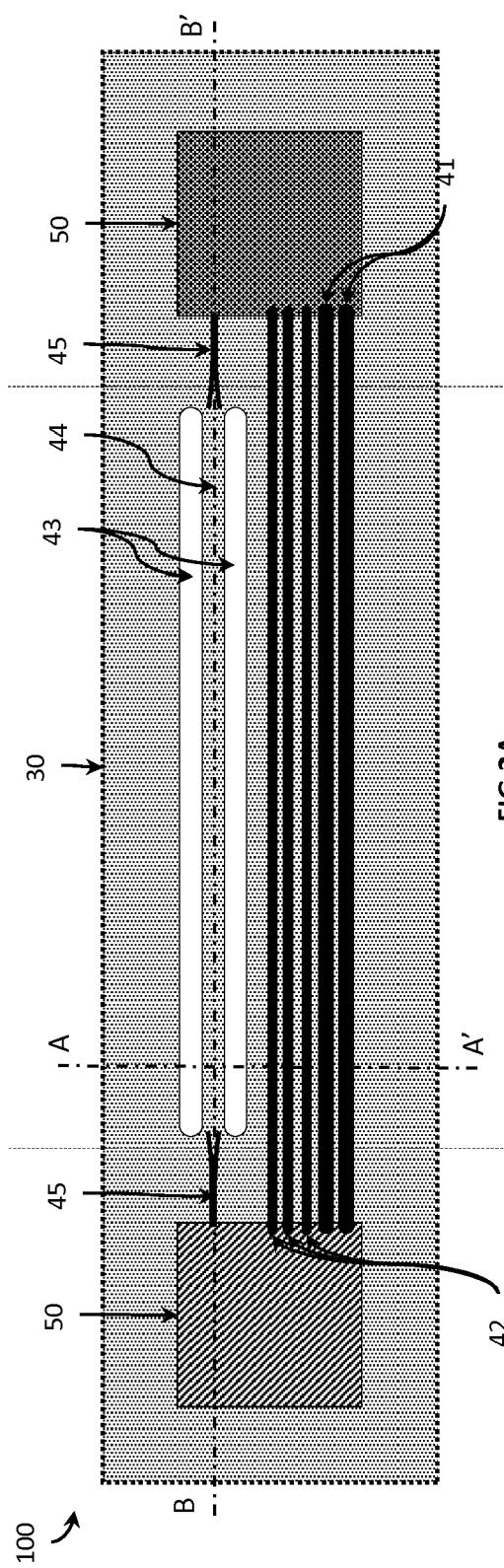

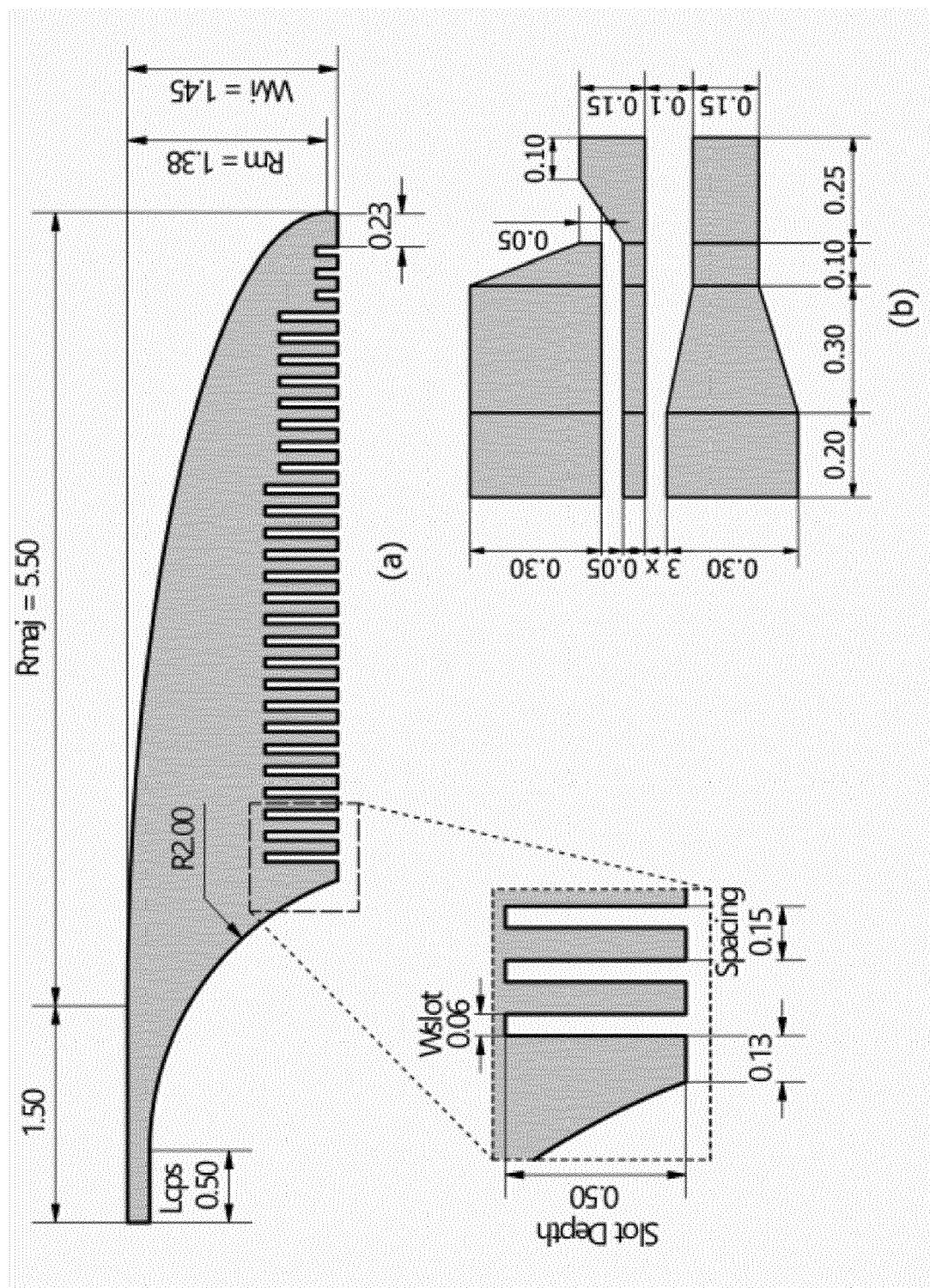

**[0032]** FIG.4 illustrates a split-boat adapter comprising the proposed waveguide interconnect.

### Detailed description

**[0033]** The present disclosure will be described with respect to particular embodiments and with reference to certain drawings but the disclosure is not limited thereto but only by the claims. The drawings described are only schematic and are non-limiting. In the drawings, the size of some of the elements may be exaggerated and not drawn on scale for illustrative purposes. The dimensions and the relative dimensions do not necessarily correspond to actual reductions to practice of the disclosure. **[0034]** A waveguide interconnect 100 according to the present disclosure can be used as a communication interconnect between modules, such as semiconductor

chips for RF communication or radar, distribution of reference signals, interconnect to remote antennas or near-field sensors etc.

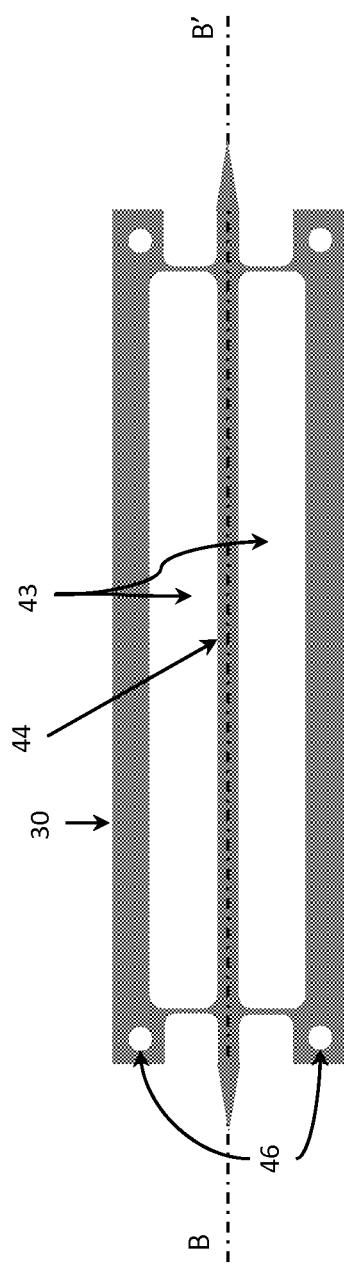

**[0031]** The waveguide interconnect is made of a dielectric layer 30 with a pair of elongated though-holes 43 with a longitudinal axis parallel to one another which form an elongated stripe 44 extending in the direction of longitudinal axis of the through-holes. The formed elongated dielectric stripe 44 has dimensions such that stripe of the dielectric layer in between the elongated through-holes forms a waveguide.

**[0032]** The width of the waveguide is inversely proportional to the frequency of operation. For example, for operation in the 100 GHz range, the width of the waveguide will be in the range of 3 mm, for operation in the 1 THz range the waveguide width will be in the 300 micron range. Application examples include reference signal distribution between modules(e.g. semiconductor chips) for millimeter wave automotive radar in the 76-81 GHz band or higher frequency bands (e.g. 140 GHz, and higher), cabling for medium range (up to 30m)wired millimeter wave communication systems, chip to antenna connections in consumer electronics using millimeter wave frequencies for communications, millimeter to THz imaging systems for security portals, non-commercial millimeter wave radar systems where reference signals need to be distributed over multiple units, millimeter wave radio astronomy systems relying on local oscillator signal distribution between antennas.

**[0033]** FIG.1 illustrates a waveguide interconnect 100 with two pairs of elongated through-holes 43 which form two dielectric stripes 44 which function as waveguides. The waveguides 44 have same length, L, but different widths, W. The thickness, H, of the waveguide is determined by the thickness of the dielectric layer 30. The cross-sectional shape of the waveguides is rectangular. However, the polygonal, elliptical or circular cross-sectional shapes are also possible. Naturally, depending on the distance between the modules to be coupled with the waveguide and the frequency range of the signal propagating through the waveguide, the length and the width of the waveguide will vary. As described above, for communication signal with frequency range of 100 GHz the waveguide may have dimension in the range of 3 mm, with this waveguide width scaling inversely proportional to the operating frequency. The waveguide interconnect may comprise waveguides configured to act as a communication channel and/or an interconnect for reference signal distribution between separate chips or modules that should share the same reference tone.

**[0034]** To avoid unwanted crosstalk between adjacent waveguides, the cutout between them should be sufficiently wide. For example, in the case of 100 GHz where the optimum width is in the 3 mm range, the width of the cutout between adjacent waveguides should also be roughly in the same range. Depending on the crosstalk requirements when using multiple adjacent waveguides, one may choose to make this cutout narrower or wider,

resulting in more or less crosstalk.

**[0035]** The waveguide interconnect 100 may be provided with a coupler 45 at each end of the dielectric waveguide 44. Each coupler 45 couples the waveguide to a signal source 50 which may be a semiconductor chip 50. The impedance of the couplers and the waveguide should be matched and should have substantially similar high-pass frequency responses. The waveguide has a high-pass characteristics with a cut-off frequency of the being dependent on its cross-sectional area. Possible coupler topologies include Vivaldi-style, differential dipole, loop, or a metal horn placed around the waveguide, or a combination of the above to launch one or multiple modes in the waveguide.

**[0036]** In addition to the waveguide, the waveguide interconnect may further comprises one or metal lines 41 for supplying power or metal lines 42 for electrical signaling between chips. The metal lines (also commonly called metal tracks) may be provided on the top surface 20 of the dielectric layer using the same standard manufacturing processes as for the coupler. Thus, the coupler and the power lines may be provided in a single manufacturing step.

**[0037]** The dielectric layer 30 may be a flexible dielectric layer. For example, the dielectric layer may be made of a low-loss polymer such as PTFE, liquid crystal polymer, polypropylene, etc.

**[0038]** The waveguide interconnect 100 may be placed on top of a support element 20, such as a PCB or a glass substrate. For the waveguide to function properly a continuous air channel enclosing the waveguide should be provided, for example by removing part of the support element(s) enclosing the waveguide as shown in FIG.1B and FIG.1C. The PCB substrate around the waveguide 44 can be removed using a subtractive manufacturing technique that is suitable for the material used, such as laser cutting, stamping, mechanical milling/routing, chemical or reactive ion etching. As shown in the figure, the support element 20 below the two already formed waveguides 44 is removed, leaving the two waveguides entirely surrounded by air and the dielectric layer supported partly by the support element.

**[0039]** Alternatively, the dielectric layer may be placed between two support elements. Similarly to above, to maintain the waveguide propagation properties, the part of the substrates around the waveguide 44 has to be removed so that a continuous air channel enclosing each waveguide is formed.

**[0040]** Additionally, the waveguide interconnect 100 may comprise a through-hole 46 around each end of the dielectric waveguide for easy attaching and/or positioning the dielectric layer to the support element(s). Alternatively, multiple through-holes as shown in FIG.1 can be used as well. If the dielectric layer is placed between two support elements, some of the though-holes may be used for aligning the dielectric layer to the first support element and the remaining ones for aligning to the second support element.

**[0041]** The through-hole may further extend into and through one or both the support elements to align the bottom support element to the coupler. Such an extended through-hole also act as a shielding structure for the coupler.

**[0042]** FIG.2 Illustrate a multichip arrangement employing the proposed waveguide interconnect as a chip-to-chip interconnect. The waveguide 44 couples two semiconductor chips 50 placed on top of the dielectric layer 30 which is supported on a PCB substrate 20. RF communication signals from one of the chips are fed into one end of the waveguide 44 using a first coupler 45 and received by the other chip at the other end of the waveguide using a second coupler 45. Each coupler includes a metal layer. The shape and dimensions of the coupler are merely illustrative and should not be taken to be restrictive. The coupler may be provided using standard manufacturing processes, for example by printing or depositing a metal layer on the top surface of the dielectric layer. For better alignment of the coupler relative to the waveguide, the coupler is provided before the waveguide is formed. The coupler converts a transverse electromagnetic mode (TEM) from a coaxial feed port to a transverse magnetic (TM) surface-wave mode. The coupler may be a planar Vivaldi-style coupler with elliptical tapering. The coplanar Vivaldi-type coupler comprises a planar structure which is easily deposited or printed on the dielectric layer. FIG.3 shows one part of a coplanar Vivaldi-style coupler. The toothed section of the coupler should be positioned within the formed waveguide so that the wave is fed into the waveguide.

**[0043]** An example of a possible full system integration is illustrated where a four-by-four antenna array 60 for each respective semiconductor chip is placed on the bottom of the PCB substrate 20.

**[0044]** The waveguide interconnect is easily fabricated by simply cutting elongated through-holes within a dielectric layer thereby forming a waveguide. Depending on the dielectric material, the cutting step may involve methods such as laser cutting, stamping, mechanical milling/routing, chemical or reactive ion etching and others.

**[0045]** After a waveguide is formed a coupler at each end of the waveguide is printed or deposited. However, to ensure precise alignment of the waveguide to the coupler and thus well-controlled mode conversion performance it is preferred that the coupler is deposited on the dielectric layer prior the formation of the waveguide.

**[0046]** In some embodiments, the dielectric layer may be provided on a first support element or between a first and a second support element for example by using standard bonding techniques. Subsequently, the support elements around the at least one formed waveguide are removed by for example laser cutting, stamping, mechanical milling/routing, chemical or reactive ion etching and others so that a continuous air channel surrounds the formed waveguide.

**[0047]** When a flexible PCB substrate, fPCB, is used, the dielectric layer of the waveguide interconnect forms

part of the support element. A fPCB consists of a rigid section and a flexible section. The flexible section comprises a dielectric layer and is typically located on top of the rigid section. The inventors have realized that the flexible section of the fPCB can be used as a interconnect by forming a waveguide in the flexible section as described above and then removing the rigid section of the fPCB underneath an already formed waveguide. Subsequently, at each end of the waveguide, a coupler is printed or deposited on top of the flexible section in the same manner as detailed above. This way the waveguide interconnect forms an integral part of a fPCB. This obviates the need to fabricate the waveguide separately from the substrate and then assemble it together, for example, after PCB fabrication. Since excellent alignment precision can be achieved between the topology of the metals comprising the coupler and the cutouts realizing the waveguide, this integration approach ensures precise alignment of the waveguide to the coupler and thus well-controlled mode conversion performance. Moreover, it allows low-cost fabrication as standard manufacturing technologies can be used to produce the interconnect and hence a mass production becomes possible.

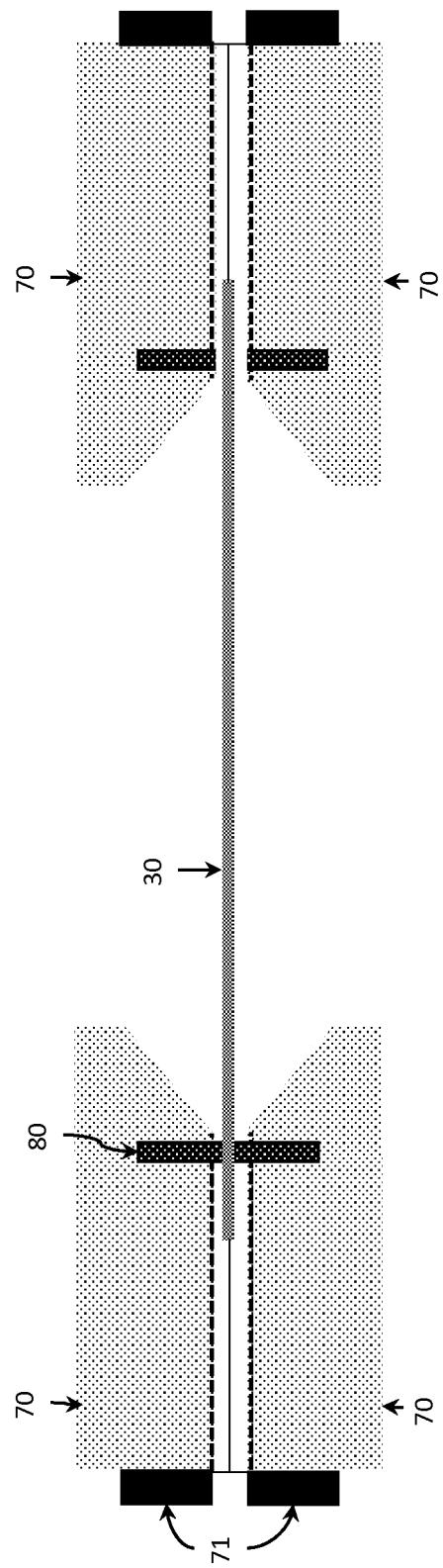

**[0048]** FIG.4 illustrates the split block adapter employing the proposed waveguide interconnect. To for the split block adapter, a waveguide interconnect 100 with a single waveguide 44 is placed between two metal parts 70 on each side of the waveguide which provide a transition to air-filled metal waveguide flanges 71 (e.g. WR-10, WR-8, WR-6, etc.). The metal parts are aligned to the waveguide using pins 80 and fixed together using screws (not shown in the figure). FIG.4A shows a top view of the waveguide interconnect and FIG.4B shows a side view of the split block adapter employing the waveguide interconnect of FIG.4A. This arrangement can be used to replace metal waveguide interconnect over certain lengths of the signal path, e.g. for on-wafer metrology applications where short connections are needed (typically less than 1m) between the measurement equipment front-end and the on-wafer probe. Such an arrangement allows convenient re-assembly of waveguides with different lengths with the same pair of split-block adapters.

#### 45 **Claims**

1. A waveguide interconnect made of dielectric layer comprising at least one pair of elongated through-holes with a longitudinal axis parallel to one another, thereby forming an elongated stripe of dielectric layer extending in the direction of longitudinal axis and such that the dielectric layer in between the elongated through-holes forms a waveguide.

- 55 2. The waveguide interconnect as in any preceding claims, wherein at least one of the formed waveguides has a different length and/or a different width.

3. The waveguide interconnect as in claim 1 or 2, wherein at each end of the dielectric waveguide a coupler for coupling the dielectric waveguide to a passive or an active module is provided by printing or depositing a metal layer on a surface of the dielectric layer.

4. The waveguide interconnect as in claim 3, where the coupler is a planar Vivaldi-style launcher with elliptical tapering.

5. The waveguide interconnect as in any preceding claims, wherein at least one power line is provided by printing or depositing a metal layer on a surface of the dielectric layer.

6. The waveguide interconnect as in any preceding claims, wherein the dielectric layer is flexible.

7. The waveguide interconnect as in claim 6, wherein the dielectric layer is made of a polyimide or a Liquid crystal polymer.

8. A waveguide interconnect as in any of claims 1 to 7, wherein the waveguide interconnect is provided on top of a first support element or between a first and a second support elements and arranged so that a continuous air channel enclosing the waveguide is provided.

9. The waveguide interconnect as in any preceding claims, wherein the dielectric layer comprises at least one through-hole around each end of the dielectric waveguide for attaching and/or positioning the dielectric layer to the first support element or to the first and second support elements.

10. A waveguide interconnect as in claim 9, wherein the at least one through-hole extends into and through at least one of the support elements.

11. A waveguide interconnect as in claims 9 or 10, comprising at least one waveguide configured to act as a communication interconnect and/or at least one waveguide configured to act as a radio frequency interconnect.

12. A method for making a waveguide interconnect, the method comprising :

a) providing a layer of a dielectric material, and

b) cutting, in the dielectric layer, at least one pair of elongated through-holes with a longitudinal axis parallel to one another thereby forming a waveguide.

13. The method as in claim 12, further comprises providing a coupler at each end of the waveguide for coupling the waveguide to a passive or an active module by printing or depositing a metal layer on a surface of the dielectric layer.

5 14. The method as in claims 12 or 13 , wherein step a) further comprises providing the dielectric layer on a first support element or between a first and a second support elements and wherein step b) further comprises removing the support elements around the at least one formed waveguide, thereby forming a continuous air channel enclosing the formed waveguide.

10 15. The method as in claim 14, wherein the support element is a glass substrate or Printed Circuit Board (PCB) substrate.

15

20

25

30

35

40

45

50

55

FIG.1A

FIG.1B

FIG.1C

FIG.2A

FIG.2B

FIG.2C

FIG.2D

FIG. 4A

FIG. 4B

## EUROPEAN SEARCH REPORT

Application Number

EP 18 17 6342

5

| DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                   |                                                     |                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------|

| Category                                                                                                                                                                                                                                                                              | Citation of document with indication, where appropriate, of relevant passages                                                                                                                                                                                                                     | Relevant to claim                                   | CLASSIFICATION OF THE APPLICATION (IPC) |

| 10 X                                                                                                                                                                                                                                                                                  | US 9 705 174 B2 (TEXAS INSTRUMENTS INC [US]) 11 July 2017 (2017-07-11)<br>* column 4, line 4 - column 4, line 6 *<br>* column 4, line 10 - column 4, line 38;<br>figure 3 *<br>* column 5, line 28 - column 6, line 50;<br>figure 5A *<br>* column 7, line 12 - column 7, line 22;<br>figure 6B * | 1-3,5-7,<br>12,13<br>4,8-11,<br>14,15               | INV.<br>H01P3/16<br>H01P5/08            |

| 15 Y                                                                                                                                                                                                                                                                                  | -----                                                                                                                                                                                                                                                                                             |                                                     |                                         |

| 20 Y                                                                                                                                                                                                                                                                                  | JP 2011 024176 A (KEYCOM CORP)<br>3 February 2011 (2011-02-03)<br>* page 3, paragraph 5 - page 3, paragraph 6; figures 1, 2 *<br>* page 3, paragraph 8; figure 4 *<br>* page 3, paragraph 10; figure 6 *                                                                                          | 4                                                   | 1,3                                     |

| 25 Y                                                                                                                                                                                                                                                                                  | -----                                                                                                                                                                                                                                                                                             |                                                     |                                         |

| 30 A                                                                                                                                                                                                                                                                                  | US 2016/178843 A1 (FUJITA MASAYUKI [JP] ET AL) 23 June 2016 (2016-06-23)<br>* page 5, paragraph 105 - page 5, paragraph 111; figure 2 *                                                                                                                                                           | 4                                                   | 1,3                                     |

| 35 Y                                                                                                                                                                                                                                                                                  | -----                                                                                                                                                                                                                                                                                             |                                                     | TECHNICAL FIELDS<br>SEARCHED (IPC)      |

| 40 Y                                                                                                                                                                                                                                                                                  | US 2014/285277 A1 (HERBSOMMER JUAN ALEJANDRO [US] ET AL)<br>25 September 2014 (2014-09-25)<br>* page 8, paragraph 123; figure 26 *                                                                                                                                                                | 8-11,14,<br>15                                      | H01P                                    |

| 45 Y                                                                                                                                                                                                                                                                                  | -----                                                                                                                                                                                                                                                                                             |                                                     |                                         |

| 50 1                                                                                                                                                                                                                                                                                  | The present search report has been drawn up for all claims                                                                                                                                                                                                                                        |                                                     |                                         |

| 55                                                                                                                                                                                                                                                                                    | Place of search<br>The Hague                                                                                                                                                                                                                                                                      | Date of completion of the search<br>5 December 2018 | Examiner<br>Blech, Marcel               |

| CATEGORY OF CITED DOCUMENTS                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                   |                                                     |                                         |

| X : particularly relevant if taken alone<br>Y : particularly relevant if combined with another document of the same category<br>A : technological background<br>O : non-written disclosure<br>P : intermediate document                                                               |                                                                                                                                                                                                                                                                                                   |                                                     |                                         |

| T : theory or principle underlying the invention<br>E : earlier patent document, but published on, or after the filing date<br>D : document cited in the application<br>L : document cited for other reasons<br>.....<br>& : member of the same patent family, corresponding document |                                                                                                                                                                                                                                                                                                   |                                                     |                                         |

ANNEX TO THE EUROPEAN SEARCH REPORT

ON EUROPEAN PATENT APPLICATION NO.

EP 18 17 6342

5 This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

05-12-2018

| 10 | Patent document cited in search report |    | Publication date |                                        | Patent family member(s)                                                                                    |  | Publication date                                                                               |

|----|----------------------------------------|----|------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------|--|------------------------------------------------------------------------------------------------|

|    | US 9705174                             | B2 | 11-07-2017       | US<br>US                               | 2015295298 A1<br>2017271736 A1                                                                             |  | 15-10-2015<br>21-09-2017                                                                       |

| 15 | JP 2011024176                          | A  | 03-02-2011       |                                        | NONE                                                                                                       |  |                                                                                                |

|    | US 2016178843                          | A1 | 23-06-2016       | JP<br>US                               | 2015187716 A<br>2016178843 A1                                                                              |  | 29-10-2015<br>23-06-2016                                                                       |

| 20 | US 2014285277                          | A1 | 25-09-2014       | US<br>US<br>US<br>US<br>US<br>US       | 2014285277 A1<br>2014285281 A1<br>2014285289 A1<br>2014285290 A1<br>2014285291 A1<br>2014285292 A1         |  | 25-09-2014<br>25-09-2014<br>25-09-2014<br>25-09-2014<br>25-09-2014<br>25-09-2014               |

| 25 |                                        |    |                  | US<br>US<br>US<br>US<br>US<br>US       | 2014285293 A1<br>2014285294 A1<br>2014287701 A1<br>2014287702 A1<br>2014287703 A1                          |  | 25-09-2014<br>25-09-2014<br>25-09-2014<br>25-09-2014<br>25-09-2014                             |

| 30 |                                        |    |                  | US<br>US<br>WO                         | 2016006101 A1<br>2016072173 A1<br>2014153391 A2                                                            |  | 07-01-2016<br>10-03-2016<br>25-09-2014                                                         |

|    |                                        |    |                  | WO                                     | 2014153393 A2                                                                                              |  | 25-09-2014                                                                                     |

| 35 | EP 2958187                             | A1 | 23-12-2015       | CN<br>EP<br>JP<br>JP<br>KR<br>US<br>WO | 106463810 A<br>2958187 A1<br>6147447 B1<br>2017518700 A<br>20170012394 A<br>2017077581 A1<br>2015180850 A1 |  | 22-02-2017<br>23-12-2015<br>14-06-2017<br>06-07-2017<br>02-02-2017<br>16-03-2017<br>03-12-2015 |

| 40 |                                        |    |                  |                                        |                                                                                                            |  |                                                                                                |

| 45 |                                        |    |                  |                                        |                                                                                                            |  |                                                                                                |

| 50 |                                        |    |                  |                                        |                                                                                                            |  |                                                                                                |

| 55 |                                        |    |                  |                                        |                                                                                                            |  |                                                                                                |

EPO FORM P0459

For more details about this annex : see Official Journal of the European Patent Office, No. 12/82