#

#### EP 4 020 442 A1 (11)

### (12)

# DEMANDE DE BREVET EUROPEEN

(43) Date de publication: 29.06.2022 Bulletin 2022/26

(21) Numéro de dépôt: 22157934.5

(22) Date de dépôt: 06.12.2018

(51) Classification Internationale des Brevets (IPC): G09G 3/20 (2006.01) G09G 3/32 (2016.01) G09G 3/3233 (2016.01) G09G 3/3291 (2016.01)

(52) Classification Coopérative des Brevets (CPC): G09G 3/2014; G09G 3/32; G09G 3/3233; G09G 3/3291; G09G 2300/0809; G09G 2300/0842; G09G 2300/0861; G09G 2330/025

(84) Etats contractants désignés:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

(30) Priorité: 28.12.2017 FR 1763313

(62) Numéro(s) de document de la (des) demande(s) initiale(s) en application de l'article 76 CBE: 18811319.5 / 3 732 671

(71) Demandeur: Aledia 38130 Echirolles (FR) (72) Inventeurs:

CHARBONNIER, Matthieu 38600 FONTAINE (FR)

· MERCIER, Frédéric 38500 SAINT NICOLAS DE MACHERIN (FR)

(74) Mandataire: Cabinet Beaumont 4, Place Robert Schuman **B.P. 1529** 38025 Grenoble Cedex 1 (FR)

### Remarques:

Cette demande a été déposée le 22.02.2022 comme demande divisionnaire de la demande mentionnée sous le code INID 62.

#### (54)ÉCRAN D'AFFICHAGE À DIODES ÉLECTROLUMINESCENTES

L'invention concerne un écran d'affichage (10) comprenant des circuits d'affichage  $(12_{i,i})$ , chaque circuit d'affichage comprenant une diode électroluminescente (LED<sub>i i</sub>), une source de courant commandable (CS<sub>i i</sub>) alimentant la diode électroluminescente et un circuit de commande (14<sub>i,i</sub>) adapté à fournir un signal (PWM<sub>i,i</sub>), modulé en largeur d'impulsions, de commande de la source de courant à partir d'un signal périodique (ST). L'écran d'affichage comprend, en outre, des premières électrodes (18<sub>i</sub>) reliées aux circuits de commande, un circuit de fourniture d'un signal de sélection (Vselecti) successivement sur chaque première électrode, et un circuit oscillant (OSC) ou des circuits oscillants adaptés à fournir les signaux périodiques (ST), les signaux périodiques n'étant pas synchrones avec les signaux de sélection des circuits d'affichage.

EP 4 020 442 A1

#### Description

[0001] La présente demande de brevet revendique la priorité de la demande de brevet français FR17/63313 qui sera considérée comme faisant partie intégrante de la présente description.

1

#### Domaine

[0002] La présente demande concerne un écran d'affichage dont les pixels d'affichage comprennent des diodes électroluminescentes, quel que soit leur type de technologie (diode électroluminescente 2D, 3D, diode électroluminescente organique, etc...)

## Exposé de l'art antérieur

[0003] Les pixels d'affichage d'un écran d'affichage à diodes électroluminescentes peuvent comprendre, pour chaque pixel d'affichage, un circuit de commande de la diode électroluminescente ou des diodes électroluminescentes du pixel d'affichage.

[0004] Il est connu de commander une diode électroluminescente par modulation de largeur d'impulsions, appelée également PWM. Ce type de commande consiste à faire circuler des impulsions successives de courant constant dans la diode électroluminescente, les impulsions étant répétées de façon cyclique, le rapport cyclique déterminant l'intensité lumineuse émise par la diode électroluminescente. Une telle commande permet de façon avantageuse de faire fonctionner la diode électroluminescente à son point de fonctionnement optimum où l'efficacité de la diode électroluminescente, égale au rapport entre la puissance lumineuse émise par la diode électroluminescente et la puissance électrique consommée par la diode électroluminescente, est maximale.

[0005] La tendance est à la réduction des dimensions des pixels d'affichage des écrans d'affichage à diodes électroluminescentes. Ceci entraîne une réduction de la place disponible pour la réalisation des circuits de commande des pixels d'affichage. Un inconvénient est que les circuits de commande mettant en oeuvre une modulation de largeur d'impulsions occupent généralement plus de place que d'autres types de circuits de commande.

# Résumé

[0006] Un objet d'un mode de réalisation est de prévoir un écran d'affichage à diodes électroluminescentes palliant tout ou partie des inconvénients des écrans d'affichage à diodes électroluminescentes existants.

[0007] Un autre objet d'un mode de réalisation est que les circuits de commande de l'écran d'affichage mettent en oeuvre une modulation de largeur d'impulsions.

[0008] Un autre objet d'un mode de réalisation est que les pixels d'affichage ont des dimensions inférieures à 200 μm.

[0009] Ainsi, un mode de réalisation prévoit un écran d'affichage comprenant des circuits d'affichage, chaque circuit d'affichage comprenant une diode électroluminescente, une source de courant commandable alimentant la diode électroluminescente et un circuit de commande adapté à fournir un signal, modulé en largeur d'impulsions, de commande de la source de courant à partir d'un signal périodique, l'écran d'affichage comprenant, en outre, des premières électrodes reliées aux circuits de commande, un circuit de fourniture d'un signal de sélection successivement sur chaque première électrode, et un circuit oscillant ou des circuits oscillants adaptés à fournir les signaux périodiques, les signaux périodiques n'étant pas synchrones avec les signaux de sélection des circuits d'affichage.

[0010] Selon un mode de réalisation, l'écran d'affichage comprend, au moins deux circuits oscillants adaptés à fournir les signaux périodiques.

[0011] Selon un mode de réalisation, les au moins deux circuits oscillants sont adaptés à fournir les signaux périodiques non synchrones entre eux.

[0012] Selon un mode de réalisation, chacun desdits au moins deux circuits oscillants est relié à au moins deux desdits circuits de commande.

[0013] Selon un mode de réalisation, chacun desdits au moins deux circuits oscillants est relié à au moins dix desdits circuits de commande.

[0014] Selon un mode de réalisation, l'écran comprend au moins mille circuits d'affichage et chacun desdits au moins deux circuits oscillants est relié à moins de cent desdits circuits de commande.

[0015] Selon un mode de réalisation, l'écran comprend, en outre, des deuxièmes électrodes reliées aux circuits de commande et un circuit de fourniture de signaux de données sur les deuxièmes électrodes et le circuit de commande de chaque circuit d'affichage comprend un circuit de mémorisation du signal de données recu par le circuit de commande et un circuit de comparaison du signal de données et du signal périodique adapté à fournir le signal de commande modulé en largeur d'impulsions.

[0016] Selon un mode de réalisation, la fréquence de chaque signal périodique est supérieure à deux fois la fréquence du signal de sélection sur l'une des premières électrodes.

[0017] Selon un mode de réalisation, la fréquence de chaque signal périodique est supérieure à dix fois la fréquence du signal de sélection sur l'une des premières électrodes.

[0018] Selon un mode de réalisation, la fréquence de chaque signal périodique est inférieure à 1 MHz.

#### Brève description des dessins

[0019] Ces caractéristiques et avantages, ainsi que d'autres, seront exposés en détail dans la description suivante de modes de réalisation particuliers faite à titre non limitatif en relation avec les figures jointes parmi

40

45

#### lesquelles:

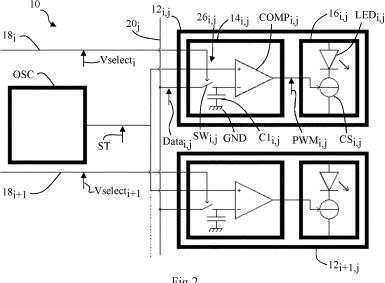

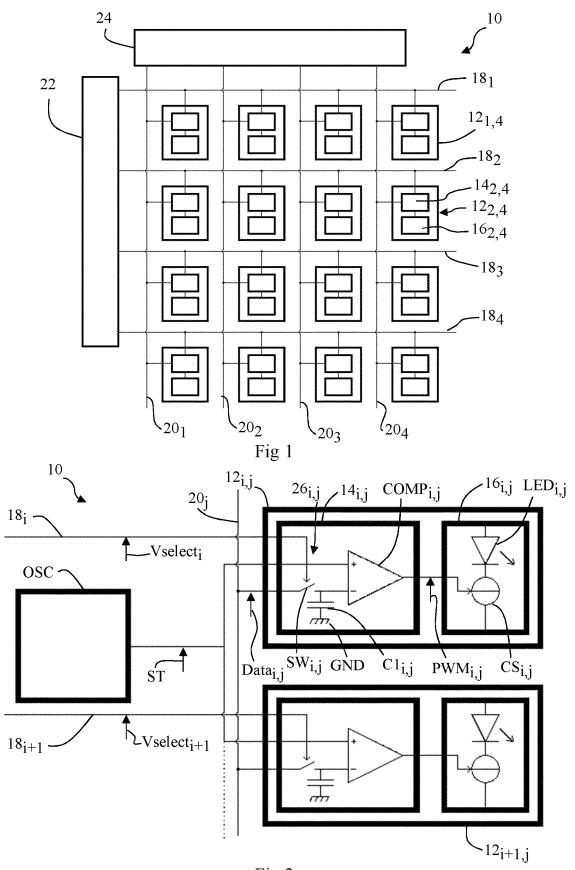

la figure 1 représente, de façon partielle et schématique, un mode de réalisation d'un écran d'affichage; la figure 2 représente un mode de réalisation plus détaillé d'une partie de l'écran d'affichage de la figure 1;

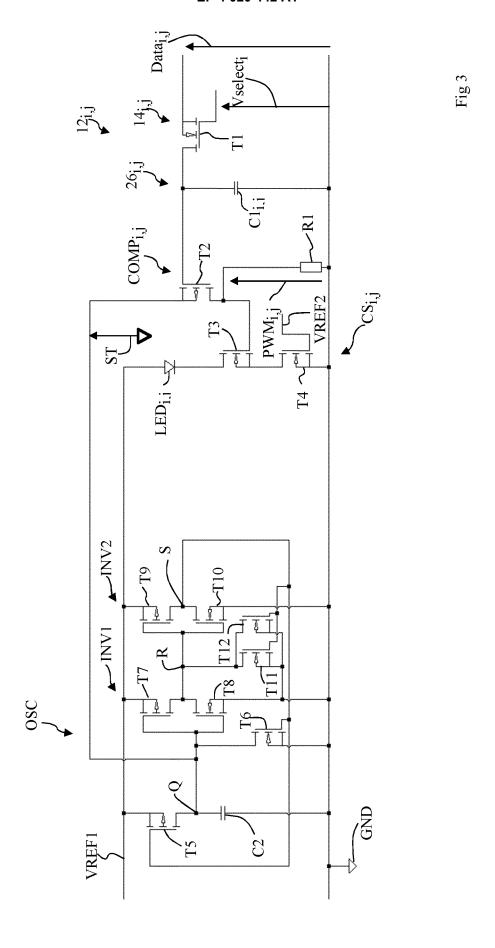

la figure 3 représente un mode de réalisation d'un circuit oscillant et d'un circuit d'affichage de l'écran d'affichage de la figure 1;

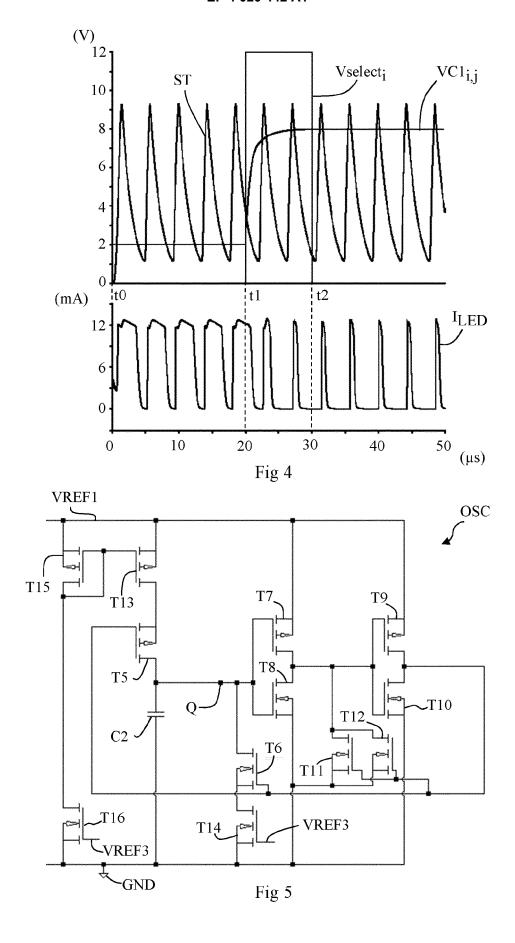

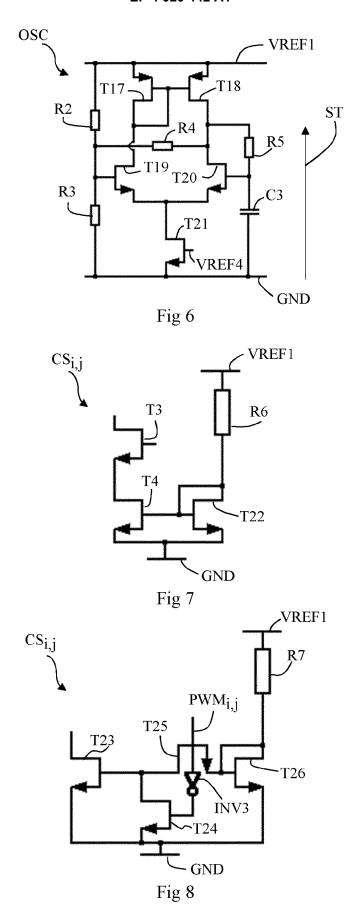

la figure 4 représente un chronogramme de signaux obtenus lors du fonctionnement du circuit oscillant et du circuit d'affichage représentés en figure 3 ; les figures 5 et 6 représentent d'autres modes de réalisation du circuit oscillant de la figure 2 ; et les figures 7 et 8 représentent d'autres modes de réalisation de la source de courant du circuit d'affichage de la figure 2.

#### Description détaillée

**[0020]** De mêmes éléments ont été désignés par de mêmes références dans les différentes figures et, de plus, les diverses figures ne sont pas tracées à l'échelle. Par souci de clarté, seuls les éléments utiles à la compréhension des modes de réalisation décrits ont été représentés et sont détaillés. Sauf précision contraire, les expressions "approximativement", "sensiblement", "environ" et "de l'ordre de" signifient à 10 % près, de préférence à 5 % près.

[0021] De plus, on appelle "signal binaire" un signal qui alterne entre un premier état constant, par exemple un état bas, noté "0", et un deuxième état constant, par exemple un état haut, noté "1". Les états haut et bas de signaux binaires différents d'un même circuit électronique peuvent être différents. En pratique, les signaux binaires peuvent correspondre à des tensions ou à des courants qui peuvent ne pas être parfaitement constants à l'état haut ou bas. En outre, dans la suite de la description, on appelle "bornes de puissance" d'un transistor à effet de champ à grille isolée, ou transistor MOS, la source et le drain du transistor MOS. De plus, dans la présente description, on utilise le terme "relié", pour désigner soit une liaison électrique directe sans composant électronique intermédiaire, par exemple au moyen d'une piste conductrice (le terme "relié" signifiant alors "connecté") soit une liaison via un ou plusieurs composants intermédiaires (résistance, condensateur, etc.). En outre, un premier signal binaire est dit "synchrone" avec un deuxième signal binaire lorsque les fronts montants et/ou descendants du premier signal se produisent au même moment que les fronts montants et/ou descendants du deuxième signal ou se produisent à intervalles réguliers par rapport aux fronts montants et/ou descendants du deuxième signal. En particulier, des signaux binaires synchrones dérivent d'une horloge commune. Inversement, des premier et deuxième signaux binaires sont dits "asynchrones" ou "non synchrones" lorsque les fronts montants

et/ou descendants du premier signal ne se produisent ni au même moment que les fronts montants et/ou descendants du deuxième signal ni à intervalles réguliers par rapport aux fronts montants et/ou descendants du deuxième signal. En particulier, des signaux binaires asynchrones ne dérivent pas d'une même horloge.

[0022] Un pixel d'une image correspond à l'élément unitaire de l'image affichée par un écran d'affichage. Lorsque l'écran d'affichage est un écran d'affichage d'images couleur, il comprend en général pour l'affichage de chaque pixel de l'image au moins trois composants d'émission et/ou de régulation de l'intensité lumineuse, également appelées sous-pixels d'affichage, qui émettent chacun un rayonnement lumineux sensiblement dans une seule couleur (par exemple, le rouge, le vert et le bleu). La superposition des rayonnements émis par ces trois sous-pixels d'affichage fournit à l'observateur la sensation colorée correspondant au pixel de l'image affichée. Lorsque l'écran d'affichage est un écran d'affichage d'images monochromes, l'écran d'affichage comprend en général une seule source lumineuse pour l'affichage de chaque pixel de l'image.

[0023] La figure 1 représente, de façon partielle et schématique, un mode de réalisation d'un écran d'affichage 10. L'écran d'affichage 10 comprend des circuits d'affichage 12<sub>i,j</sub> par exemple agencés en M rangées et en N colonnes, M étant un nombre entier variant de 1 à 16000 et N étant un nombre entier variant de 1 à 8000, i étant un nombre entier variant de 1 à M et j étant un nombre entier variant de 1 à N. A titre d'exemple, en figure 1, M et N sont égaux à 4. Chaque circuit d'affichage 12<sub>i,j</sub> comprend un circuit de commande 14<sub>i,j</sub> et un souspixel d'affichage 16<sub>i,j</sub>. Chaque sous-pixel d'affichage 16<sub>i,j</sub>. Chaque sous-pixel d'affichage 16<sub>i,j</sub>. comprend au moins une diode électroluminescente, non représentée.

$\begin{tabular}{l} \begin{tabular}{l} \begin{tab$

**[0026]** La figure 2 représente un mode de réalisation plus détaillé de deux circuits d'affichage  $12_{i,j}$  et  $12_{i+1,j}$  de l'écran d'affichage 10.

**[0027]** Selon un mode de réalisation, l'écran d'affichage 10 comprend un circuit oscillant OSC de fourniture d'un signal oscillant et périodique ST relié aux circuits d'affichage  $12_{i,j}$  et  $12_{i+1,j}$ . Chaque sous-pixel d'affichage  $16_{i,j}$  comprend une diode électroluminescente LED $_{i,j}$  reliée en série à une source de courant commandable CS $_{i,j}$ . Chaque circuit de commande  $14_{i,j}$  comprend un circuit de mémorisation  $26_{i,j}$  reliée à l'électrode de rangée  $18_i$

et à l'électrode de colonne 20<sub>i</sub>. Le circuit de mémorisation 26<sub>i i</sub> est commandé par le signal VSelect<sub>i</sub> fourni par l'électrode de rangée 18<sub>i</sub> et est adapté à stocker le signal Data<sub>i, i</sub> fourni par l'électrode de colonne 20<sub>i</sub>. Selon un mode de réalisation, le circuit de mémorisation 26<sub>i,j</sub> comprend un interrupteur SW<sub>i,j</sub> commandé par le signal VSelect<sub>i</sub> et un condensateur C1<sub>i,i</sub>. La première borne de l'interrupteur SW<sub>i,i</sub> est reliée à l'électrode de colonne 20<sub>i</sub> et la deuxième borne de l'interrupteur SW<sub>i,j</sub> est reliée à la première électrode du condensateur  $C1_{i,j}^{\cdot}$ , la deuxième électrode du condensateur  $C1_{i,i}$  étant reliée à une source GND d'un potentiel de référence bas, par exemple la masse. Chaque circuit de commande  $14_{i,j}$  comprend, en outre, un circuit de comparaison COMPi, relié à une première entrée (+) au circuit oscillant OSC et relié à une deuxième entrée (-) à la première électrode du condensateur C1; i. Le circuit de comparaison COMP<sub>i,j</sub> fournit un signal PW-M<sub>i,i</sub> de commande de la source de courant CS<sub>i,i</sub>

[0028] Un mode de réalisation d'un procédé de fonctionnement de l'écran d'affichage 10 va maintenant être décrit. Le signal Vselect, est un signal binaire. Lorsque le signal Vselect<sub>i</sub> est dans un premier état, par exemple l'état bas, l'interrupteur  $SW_{i,j}$  est ouvert et lorsque le signal Vselecti est dans un deuxième état, par exemple l'état haut, l'interrupteur SW<sub>i,j</sub> est fermé. Les signaux Datai, sont des signaux analogiques représentatifs des intensités lumineuses souhaitées devant être émises par les diodes électroluminescentes LED<sub>i,j</sub>. Lorsque l'interrupteur SW<sub>i,j</sub> est fermé, la tension aux bornes du condensateur C1<sub>i,j</sub> devient sensiblement égale au signal Da $ta_{i,i}$ . Le signal PWM $_{i,j}$  est un signal binaire qui dépend de la comparaison entre le signal ST et la tension aux bornes du condensateur  $C1_{i,j}$ , c'est-à-dire le signal  $Data_{i,j}$ . A titre d'exemple, le signal  $PWM_{i,j}$  est à un premier état, par exemple l'état haut, lorsque le signal ST est supérieur au signal Data<sub>i,i</sub> et le signal PWM<sub>i,i</sub> est à un deuxième état, par exemple l'état bas, lorsque le signal ST est inférieur au signal Data<sub>i,j</sub>. De préférence, le signal ST est un signal périodique qui, sur chaque période, croît de façon continue ou décroît de façon continue sensiblement sur la totalité de la période. A titre d'exemple, le signal ST est un signal en dents de scie qui, sur chaque période, croît ou décroît à pente sensiblement constante. Le signal PWM<sub>i,i</sub> obtenu est alors un signal cyclique modulé en largeur d'impulsions, la durée du signal PWM<sub>i,i</sub> à l'état haut sur un cycle étant proportionnelle au signal Data<sub>i i</sub>

**[0029]** La source de courant  $CS_{i,j}$  est commandée par le signal  $PWM_{i,j}$ . A titre d'exemple, la source de courant  $CS_{i,j}$  est activée, c'est-à-dire qu'elle alimente la diode électroluminescente  $LED_{i,j}$  en courant, lorsque le signal  $PWM_{i,j}$  est dans le premier état, par exemple l'état haut, et la source de courant  $CS_{i,j}$  est désactivée, c'est-à-dire que la diode électroluminescente  $LED_{i,j}$  n'est pas traversée par un courant, lorsque le signal  $PWM_{i,j}$  est dans le deuxième état, par exemple l'état bas. Lorsqu'elle est activée, le courant fourni par la source de courant  $CS_{i,j}$  est de préférence sensiblement constant et égal au cou-

rant pour lequel l'efficacité de la diode électroluminescente  $\mathsf{LED}_{i,j}$  est maximale. La diode électroluminescente  $\mathsf{LED}_{i,j}$  est donc soit alimentée à courant constant soit éteinte. Une commande de la diode électroluminescente  $\mathsf{LED}_{i,j}$  par modulation de largeur d'impulsions est ainsi obtenue.

[0030] Dans le mode de réalisation illustré en figure 2, le circuit oscillant OSC est à titre d'exemple relié à deux circuits d'affichage  $12_{i,j}$  et  $12_{i+1,j}$ . De façon générale, l'écran d'affichage 10 peut comprendre un ou plusieurs circuits oscillants OSC, chaque circuit oscillant OSC étant relié à un nombre K de circuits d'affichage  $12_{i,j}$ , K étant un nombre entier variant de 1 à N\*M, de préférence variant de 1 à 8000\*4000. Le cas où K est égal à 1 correspond au cas où l'écran d'affichage 10 comprend un circuit oscillant OSC pour chaque circuit d'affichage  $12_{i,j}$  et le cas où K est égal à N\*M correspond au cas où l'écran d'affichage 10 comprend un seul circuit oscillant OSC pour l'ensemble des circuits d'affichage  $12_{i,j}$ .

[0031] Selon un mode de réalisation, les rangées de sous-pixels d'affichage sont activées successivement. Les signaux Vselect<sub>1</sub> à VSelect<sub>M</sub> sont alors successivement mis à l'état haut pendant une durée  $\Delta T$ , les signaux Vselect<sub>1</sub> à VSelect<sub>i-1</sub> et Vselect<sub>i+1</sub> à VSelect<sub>M</sub> étant à l'état bas lorsque le signal Vselect, est à l'état haut. On appelle F la fréquence de rafraîchissement de l'écran d'affichage. La fréquence F est égale à 1/∆T. A titre d'exemple, la fréquence F varie de 25 Hz à 120 Hz. La fréquence F' du signal ST est supérieure à 2 fois la fréquence F, de préférence supérieure à 10 fois la fréquence F, plus préférentiellement supérieure à 100 fois la fréquence F. A titre d'exemple, la fréquence F' est supérieure à 1 kHz, de préférence supérieure à 10 kHz, encore plus préférentiellement supérieure à 100 kHz. La fréquence F' du signal ST est de préférence inférieure à 1 MHz. De façon avantageuse, la structure du circuit oscillant OSC peut alors être simple. En outre, lorsque le circuit oscillant OSC met en oeuvre des interrupteurs. les pertes dues aux commutations des interrupteurs sont faibles.

[0032] Selon un mode de réalisation, le signal ST n'est pas synchrone par rapport aux signaux VSelect, et Data, j. Ceci signifie que le début de chaque période du signal ST n'est pas synchrone avec les instants auxquels les signaux Vselect, changent d'état. En outre, lorsque plusieurs circuits oscillants OSC sont présents, les signaux ST fournis par les circuits oscillants OSC ne sont de préférence pas synchrones entre eux. La conception de l'écran d'affichage 10 est alors simplifiée puisqu'il n'y a pas à maintenir les signaux ST synchrones entre eux et avec les signaux VSelect, et Data, j. En outre, les appels de courant lors du fonctionnement de l'écran d'affichage 10 sont de façon avantageuse étalés dans le temps.

**[0033]** En outre, les nombre de pistes conductrices reliant le circuit oscillant OSC et chaque circuit de commande 14<sub>i,j</sub> associé est réduit. De plus, lorsque l'écran d'affichage 10 comprend plusieurs circuits oscillants OSC, la distance parcourue par le signal ST entre chaque

circuit oscillant OSC et les circuits d'affichage  $12_{i,j}$  auxquels le circuit oscillant OSC est relié peut être réduite par rapport au cas où un signal d'horloge doit être fourni à chaque circuit d'affichage  $12_{i,i}$ .

**[0034]** Les sous-pixels d'affichage  $16_{i,j}$  peuvent être formés sur un premier circuit électronique et les circuits de commande  $14_{i,j}$  et le circuit oscillant OSC ou les circuits oscillants OSC peuvent être formés sur un deuxième circuit électronique, les premier et deuxième circuits électroniques étant fixés l'un à l'autre. Les circuits de commande  $14_{i,j}$  et le circuit oscillant OSC ou les circuits oscillants OSC peuvent être formés selon une technologie CMOS. A titre de variante, Les circuits de commande  $14_{i,j}$  et le circuit oscillant OSC ou les circuits oscillants OSC peuvent être formés avec des transistors en couches minces.

**[0035]** La figure 3 représente un mode de réalisation d'un circuit oscillant OSC et d'un circuit d'affichage 12<sub>i,j</sub> de l'écran d'affichage 10 de la figure 1.

**[0036]** Dans le présent mode de réalisation, l'interrupteur  $SW_{i,j}$  du circuit de mémorisation  $26_{i,j}$  du circuit de commande  $14_{i,j}$  correspond à un transistor MOS T1, par exemple à canal N, dont la grille reçoit le signal Vselect, dont la première borne de puissance reçoit le signal Data $_{i,j}$  et dont la deuxième borne de puissance est reliée à une première électrode du condensateur  $C1_{i,i}$ .

**[0037]** Dans le présent mode de réalisation, le circuit de comparaison  $COMP_{i,j}$  comprend un transistor MOS T2, par exemple à canal P, dont la grille est reliée à la première électrode du condensateur  $C1_{i,j}$ , dont la première borne de puissance reçoit le signal ST et dont la deuxième borne de puissance est reliée à la source GND du potentiel de référence bas par l'intermédiaire d'une résistance R1. Le signal  $PWM_{i,j}$  fourni par le circuit de comparaison  $COMP_{i,j}$  correspond à la tension à la deuxième borne de puissance du transistor T2.

[0038] Dans le présent mode de réalisation, la source de courant commandable CS<sub>i,j</sub> comprend deux transistors MOS en série T3 et T4, par exemple à canal N. La grille du transistor T3 est reliée à la deuxième borne de puissance du transistor T2. La première borne de puissance du transistor T3 est reliée à la cathode de la diode électroluminescente LED<sub>i,i</sub> et la deuxième borne de puissance du transistor T3 est reliée à la première borne de puissance du transistor T4. La grille du transistor T3 reçoit le signal PWM<sub>i.i</sub>. L'anode de la diode électroluminescente LED<sub>i,i</sub> est reliée à une source VREF1 d'un premier potentiel de référence haut, par exemple la tension d'alimentation de l'écran d'affichage 10. La grille du transistor T4 est reliée à une source VREF2 d'un deuxième potentiel de référence haut. La deuxième borne de puissance du transistor T4 est reliée à la source GND du potentiel de référence bas.

[0039] Dans ce mode de réalisation, la source de courant commandable créée par les transistors T4 et T3 est conçue pour tirer un courant depuis la cathode de la LED vers la masse GND, l'anode de la LED étant connectée au potentiel haut d'alimentation VREF1. Cette structure

est particulièrement adaptée à une technologie de LED dont la représentation électrique équivalente des pixels serait une structure à anode commune. L'homme de l'art pourra aisément modifier la structure de la source de courant ainsi que de son pilotage pour l'adapter à une technologie de LED/OLED dont la représentation électrique serait une structure de type cathode commune ou plus généralement une structure où la cathode de la LED serait connectée à la masse. La source de courant devrait alors être placée entre l'anode de la LED et un potentiel haut (VREF1 par exemple)

[0040] Dans le présent mode de réalisation, le circuit oscillant OSC comprend un transistor MOS T5, par exemple à canal P, dont la première borne de puissance est reliée à la source VREF1 du premier potentiel de référence haut et dont la deuxième borne de puissance est reliée à un noeud Q fournissant le signal ST. Le circuit oscillant OSC comprend, en outre, un condensateur C2 dont la première électrode est reliée au noeud Q et dont la deuxième électrode est reliée à la source GND du potentiel de référence bas. Le circuit oscillant OSC comprend, en outre, un transistor MOS T6, par exemple à canal N, dont la première borne de puissance est reliée au noeud Q et dont la deuxième borne de puissance est reliée à la source GND du potentiel de référence bas. Le circuit oscillant OSC comprend, en outre, un premier inverseur INV1 dont l'entrée est reliée au noeud Q et dont la sortie est reliée à un noeud R. Le premier inverseur INV1 peut comprendre un transistor MOS T7, par exemple à canal P, en série avec un transistor MOS T8, par exemple à canal N. La première borne de puissance du transistor T7 est reliée à la source VREF1 du premier potentiel de référence haut et la deuxième borne de puissance du transistor T7 est reliée au noeud R. La première borne de puissance du transistor T8 est reliée au noeud R et la deuxième borne de puissance du transistor T8 est reliée à la source GND du potentiel de référence bas. Les grilles des transistors T7 et T8 sont reliées au noeud Q. Le circuit oscillant OSC comprend en outre un deuxième inverseur INV2 dont l'entrée est reliée au noeud R et dont la sortie est reliée à un noeud S. Le deuxième inverseur INV2 peut comprendre un transistor MOS T9, par exemple à canal P, en série avec un transistor MOS T10, par exemple à canal N. La première borne de puissance du transistor T9 est reliée à la source VREF1 du premier potentiel de référence haut et la deuxième borne de puissance du transistor T9 est reliée au noeud S. La première borne de puissance du transistor T10 est reliée au noeud S et la deuxième borne de puissance du transistor T10 est reliée à la source GND du potentiel de référence bas. Les grilles des transistors T9 et T10 sont reliées au noeud S. Le circuit oscillant OSC comprend, en outre, un transistor MOS T11, par exemple à canal N, dont la première borne de puissance est reliée au noeud R et dont la deuxième borne de puissance est reliée à la source GND du potentiel de référence bas et un transistor MOS T12, par exemple à canal N, dont la première borne de puissance est reliée au noeud R et

40

25

dont la deuxième borne de puissance est reliée à la source GND du potentiel de référence bas. Les grilles des transistors T5, T6, T11 et T12 sont reliées au noeud S. [0041] Selon un mode de réalisation, la source VREF1 du premier potentiel de référence haut est commune à l'ensemble des circuits d'affichage 12<sub>i,i</sub> et des circuits oscillants OSC de l'écran d'affichage 10. Selon un mode de réalisation, la source VREF2 du deuxième potentiel de référence haut est commune à l'ensemble des circuits d'affichage 12<sub>i i</sub> de l'écran d'affichage 10. Selon un autre mode de réalisation, l'écran d'affichage 10 comprend plusieurs sources VREF2 du deuxième potentiel de référence haut qui sont communes aux circuits d'affichage 12<sub>i i</sub> émettant la même couleur. A titre d'exemple, l'écran d'affichage 10 comprend une première source VREF2 du deuxième potentiel de référence haut pour les circuits d'affichage 12<sub>i,j</sub> émettant de la lumière rouge, une deuxième source VREF2 du deuxième potentiel de référence haut pour les circuits d'affichage 12<sub>i,j</sub> émettant de la lumière bleue et une troisième source VREF2 du deuxième potentiel de référence haut pour les circuits d'affichage 12<sub>i,i</sub> émettant de la lumière verte. Ceci permet notamment de faire varier différemment les deuxièmes potentiels de référence haut selon la couleur de la lumière émise par les circuits d'affichage 12<sub>i,i</sub>. Selon un mode de réalisation, les sources VREF1 et VREF2 peuvent être confondues.

**[0042]** Le mode de réalisation du circuit de commande  $14_{i,j}$  représenté en figure 3 présente l'avantage que la structure du circuit de comparaison  $COMP_{i,j}$  est particulièrement simple puisqu'elle ne comprend qu'un seul transistor MOS.

[0043] La figure 4 représente un chronogramme obtenu par simulation des tensions ST, Vselect<sub>i</sub>, de la tension VC1<sub>i,i</sub> aux bornes du condensateur C1<sub>i,i</sub> et du courant I<sub>LED</sub> circulant dans la diode électroluminescente LED<sub>i i</sub> illustrant le fonctionnement du circuit oscillant OSC et du circuit d'affichage 12<sub>i,j</sub> représentés en figure 3. Les instants t0, t1 et t2 sont successifs. Dans le présent exemple, la fréquence du signal ST est de 230 kHz et la fréquence de rafraichissement de l'écran d'affichage est de 20 ms. Dans le présent exemple, le signal Vselect, est à l'état bas (0 V) de l'instant t0 à l'instant t1. Le transistor MOS T1 est donc non passant et la tension VC1<sub>i,i</sub> aux bornes du condensateur C1<sub>i,j</sub> est constante à un premier niveau (2 V) correspondant au dernier niveau mémorisé du signal Data<sub>i,i</sub>. De l'instant t1 à l'instant t2, le signal Vselect<sub>i</sub> est à l'état haut (12 V). Le transistor MOS T1 est donc passant et la tension  $VC1_{i,j}$  aux bornes du condensateur C1<sub>i,i</sub> évolue jusqu'à un deuxième niveau (8 V) égal à la tension Data; i fournie au circuit d'affichage 12; i. Après l'instant t2, le signal Vselect, est à l'état bas. Le transistor MOS T1 est donc non passant et la tension VC1<sub>i,i</sub> aux bornes du condensateur C1<sub>i,i</sub> reste constante au deuxième niveau.

**[0044]** Le courant  $I_{LED}$  circulant dans la diode électroluminescente  $LED_{i,j}$  a sensiblement la forme d'un signal en créneaux, alternant entre un premier niveau à environ 12 mA et un deuxième niveau à environ 0 mA, qui est périodique de l'instant t0 à l'instant t1 et après l'instant t2, avec un rapport cyclique, égal au rapport entre la durée au premier niveau et la durée de la période, qui dépend de la tension VC1<sub>i,j</sub>. Le premier niveau d'intensité du courant I<sub>LED</sub> est déterminé notamment par le niveau du deuxième potentiel de référence haut et les caractéristiques du transistor T4.

[0045] Le circuit oscillant OSC fournit un signal ST oscillant et périodique, qui de préférence évolue de façon sensiblement monotone sur chaque période. Un mode de réalisation du circuit oscillant OSC est représenté en figure 3. Toutefois, tout type de circuit oscillant OSC adapté à fournir un signal ST oscillant et périodique, qui évolue de préférence de façon sensiblement monotone sur chaque période, peut être utilisé.

[0046] La figure 5 représente un autre mode de réalisation du circuit oscillant OSC.

[0047] Le circuit oscillant OSC représenté en figure 5 comprend l'ensemble des éléments du circuit oscillant OSC représenté en figure 3 à la différence que le transistor T5 est monté en série avec un transistor MOS T13, par exemple à canal P, dont la première borne de puissance est reliée à la source VREF1 du premier potentiel de référence haut et dont la deuxième borne de puissance est reliée à la première borne de puissance du transistor T5 et à la différence que le transistor T6 est monté en série avec un transistor MOS T14, par exemple à canal N, dont la première borne de puissance est reliée à la deuxième borne de puissance du transistor T6, dont la deuxième borne de puissance est reliée à la source GND du potentiel de référence bas et dont la grille est reliée à une source VREF3 d'un troisième potentiel de référence haut.

[0048] Le circuit oscillant OSC représenté en figure 5 comprend, en outre, un transistor MOS T15, par exemple à canal P, en série avec un transistor MOS T16, par exemple à canal N. La première borne de puissance du transistor T15 est reliée à la source VREF1 du premier potentiel de référence haut. La deuxième borne de puissance du transistor T15 est reliée à la première borne de puissance du transistor T16 et la deuxième borne de puissance du transistor T16 est reliée à la source GND du potentiel de référence bas. La grille du transistor T15 est reliée à la grille du transistor T15 est reliée à la grille du transistor T16 est reliée à la source VREF3 du troisième potentiel de référence haut.

**[0049]** Le mode de réalisation du circuit oscillant OSC représenté en figure 5 présente l'avantage d'une meilleure linéarisation de la charge et de la décharge du condensateur C2 par rapport au mode de réalisation du circuit oscillant OSC représenté en figure 3.

**[0050]** La figure 6 représente un autre mode de réalisation du circuit oscillant OSC.

[0051] Le circuit oscillant OSC représenté en figure 6 comprend deux transistors MOS T17 et T18, par exemple à canal P, dont les premières bornes de puissance sont reliées à la source VREF1 du premier potentiel de réfé-

rence haut et dont les grilles sont reliées l'une à l'autre. Le circuit oscillant OSC représenté en figure 6 comprend, en outre, des transistors MOS T19, T20 et T21, par exemple à canal N. La première borne de puissance du transistor T19 est reliée à la deuxième borne de puissance du transistor T17 ainsi qu'à la grille du transistor T17. La première borne de puissance du transistor T20 est reliée à la deuxième borne de puissance du transistor T18. La première borne de puissance du transistor T21 est reliée aux deuxièmes bornes de puissance des transistors T19 et T20. La deuxième borne de puissance du transistor T21 est reliée à la source GND du potentiel de référence bas. La grille du transistor T21 est reliée à une source VREF4 d'un quatrième potentiel de référence haut. Le circuit oscillant OSC représenté en figure 6 comprend, en outre, quatre résistances R2, R3, R4 et R5. La résistance R2 est reliée entre la source VREF1 du premier potentiel de référence haut et la grille du transistor T19. La résistance R3 est reliée entre la grille du transistor T19 et la source GND du potentiel de référence bas. La résistance R4 est reliée entre la grille du transistor T19 et la première borne de puissance du transistor T20. La résistance R5 est reliée entre la première borne de puissance du transistor T20 et la grille du transistor T20. Le circuit oscillant OSC représenté en figure 6 comprend, en outre, un condensateur C3 dont la première électrode est reliée à la grille du transistor T20 et dont la deuxième électrode est reliée à la source GND du potentiel de référence bas. Le signal ST oscillant correspond par exemple à la tension aux bornes de l'ensemble formé par la résistance R5 et le condensateur C3. Un avantage du circuit oscillant OSC représenté en figure 6 est que les instants de commutation peuvent être commandés avec une précision améliorée.

[0052] La source de courant commandable  $CS_{i,j}$  fournit, lorsqu'elle est activée, un courant sensiblement constant qui alimente la diode électroluminescente  $LED_{i,j}$ . Un mode de réalisation de source de courant commandable  $CS_{i,j}$  est représenté en figure 3. Toutefois, tout type de source de courant commandable  $CS_{i,j}$  est adapté à fournir un courant sensiblement constant qui alimente la diode électroluminescente  $LED_{i,j}$  peut être utilisé.

**[0053]** La figure 7 représente un autre mode de réalisation de la source de courant commandable CS<sub>i,i</sub>.

**[0054]** La source de courant commandable CS<sub>i,j</sub> représentée en figure 7 comprend l'ensemble des éléments de la source de courant commandable CS<sub>i,j</sub> représentée en figure 3 à la différence que la grille du transistor T4 est reliée à la grille d'un transistor MOS T22, par exemple à canal N. La source de courant commandable CS<sub>i,j</sub> représentée en figure 7 comprend, en outre, une résistance R6 dont une borne est reliée à la source VREF1 du premier potentiel de référence haut et dont la deuxième borne est reliée à la première borne de puissance du transistor T22. La deuxième borne de puissance du transistor T22 est reliée à la source GND du potentiel de référence bas. La première borne de puissance du transistor T22 est, en outre, reliée à la grille du transistor T22. Un avan-

tage de la source de courant représentée en figure 7 est qu'elle ne nécessite pas l'utilisation de la source VREF2 du deuxième potentiel de référence haut. Elle peut donc facilement être réalisée au niveau du circuit d'affichage 12: ...

12<sub>i.i</sub>. [0055] La figure 8 représente un autre mode de réalisation de la source de courant commandable CS<sub>i,i</sub>. [0056] La source de courant commandable CS<sub>i,i</sub> représentée en figure 8 comprend des transistors MOS T23, T24, T25 et T26, par exemple à canal N. La première borne de puissance du transistor T23 est reliée à la cathode de la diode électroluminescente LED<sub>i,j</sub>, non représentée. La deuxième borne de puissance du transistor T23 est reliée à la source GND du potentiel de référence bas. La première borne de puissance du transistor T24 est reliée à la grille du transistor T23. La deuxième borne de puissance du transistor T24 est reliée à la source GND du potentiel de référence bas. La première borne de puissance du transistor T25 est reliée à la grille du transistor T23. La grille du transistor T25 reçoit le signal PWM<sub>i,i</sub>. La source de courant commandable CS<sub>i,i</sub> représentée en figure 8 comprend, en outre, une résistance R7 dont une borne est reliée à la source VREF1 du premier potentiel de référence haut et dont la deuxième borne est reliée à la première borne de puissance du transistor T26. La deuxième borne de puissance du transistor T26 est reliée à la source GND du potentiel de référence bas. La première borne de puissance du transistor T26 est, en outre, reliée à la grille du transistor T26. La grille du transistor T26 est reliée à la deuxième borne de puissance du transistor T25. La source de courant commandable CS<sub>i i</sub> représentée en figure 8 comprend, en outre, un inverseur INV3 dont l'entrée est reliée à la grille du transistor T25 et dont la sortie est reliée à la grille du transistor

**[0057]** Des modes de réalisation particuliers ont été décrits. Diverses variantes et modifications apparaîtront à l'homme de l'art. En outre, divers modes de réalisation avec diverses variantes ont été décrits ci-dessus. On note que divers éléments de ces divers modes de réalisation et variantes peuvent être combinés. A titre d'exemple, le mode de réalisation de la source de courant commandable CS<sub>i,j</sub> représenté sur les figures 7 ou 8 peut être mis en oeuvre avec le circuit oscillant OSC représenté sur les figures 5 ou 6.

#### Revendications

T24.

1. Ecran d'affichage (10) comprenant des circuits d'affichage (12<sub>i,j</sub>), chaque circuit d'affichage comprenant une diode électroluminescente (LED<sub>i,j</sub>), une source de courant commandable (CS<sub>i,j</sub>) alimentant la diode électroluminescente et un circuit de commande (14<sub>i,j</sub>) adapté à fournir un signal (PWM<sub>i,j</sub>), modulé en largeur d'impulsions, de commande de la source de courant à partir d'un signal périodique (ST), l'écran d'affichage comprenant, en outre, des premières

électrodes (18<sub>i</sub>) reliées aux circuits de commande, un circuit (22) de fourniture d'un signal de sélection (Vselect<sub>i</sub>) successivement sur chaque première électrode, caractérisé en ce qu'il comprend, en outre, des circuits oscillants (OSC) adaptés à fournir les signaux périodiques (ST), les signaux périodiques n'étant pas synchrones avec les signaux de sélection des circuits d'affichage et n'étant pas synchrones entre eux.

2. Ecran d'affichage selon la revendication 1, dans lequel chacun des circuits oscillants (OSC) est relié à au moins deux desdits circuits de commande (14; i).

3. Ecran d'affichage selon la revendication 1, dans lequel chacun des circuits oscillants (OSC) est relié à au moins dix desdits circuits de commande (14; i).

4. Ecran d'affichage selon l'une quelconque des revendications 1 à 3, comprenant au moins mille circuits d'affichage (12<sub>i,i</sub>) et dans lequel chacun des circuits oscillants (OSC) est relié à moins de cent desdits circuits de commande (14<sub>i,i</sub>).

5. Ecran d'affichage selon l'une quelconque des revendications 1 à 4, comprenant, en outre, des deuxièmes électrodes (20<sub>i</sub>) reliées aux circuits de commande (14<sub>i i</sub>) et un circuit (22) de fourniture de signaux de données (Data<sub>i,i</sub>) sur les deuxièmes électrodes et dans lequel le circuit de commande (14<sub>i,j</sub>) de chaque circuit d'affichage (12<sub>i,i</sub>) comprend un circuit de mémorisation (26<sub>i,i</sub>) du signal de données reçu par le circuit de commande et un circuit de comparaison (COMP<sub>i,i</sub>) du signal de données et du signal périodique (ST) adapté à fournir le signal de commande

(PWM<sub>i i</sub>) modulé en largeur d'impulsions.

6. Ecran d'affichage selon l'une quelconque des revendications 1 à 5, dans lequel la fréquence de chaque signal périodique (ST) est supérieure à deux fois la fréquence du signal de sélection (Vselecti) sur l'une des premières électrodes (18<sub>i</sub>).

7. Ecran d'affichage selon l'une quelconque des revendications 1 à 6, dans lequel la fréquence de chaque signal périodique (ST) est supérieure à dix fois la fréquence du signal de sélection (Vselecti) sur l'une des premières électrodes (18<sub>i</sub>).

8. Ecran d'affichage selon l'une quelconque des revendications 1 à 6, dans lequel la fréquence de chaque signal périodique (ST) est inférieure à 1 MHz.

5

#### RAPPORT DE RECHERCHE EUROPEENNE

Numéro de la demande

EP 22 15 7934

**DOCUMENTS CONSIDERES COMME PERTINENTS** CLASSEMENT DE LA DEMANDE (IPC) Citation du document avec indication, en cas de besoin, Catégorie des parties pertinentes concernée 10 2 Х US 2017/039935 A1 (YANG WU-CHANG [TW] ET INV. AL) 9 février 2017 (2017-02-09) G09G3/20 \* alinéas [0003], [0042] - [0043], G09G3/32 [0053] - [0060]; figures 2,3A,4A,4B,4C,5,6 G09G3/3233 G09G3/3291 15 US 2010/245401 A1 (SMITH EUAN C [GB] ET 1 A 1-8 AL) 30 septembre 2010 (2010-09-30) \* alinéas [0032] - [0035]; figures 4,5,6 \* 1 X US 7 187 355 B2 (SEIKO EPSON CORP [JP]) 1-8 20 6 mars 2007 (2007-03-06) \* colonne 4, ligne 39 - ligne 67; figures 1,2,6,7 \* 1 X US 2005/067968 A1 (YAMASHITA ATSUHIRO 1-8 25 [JP]) 31 mars 2005 (2005-03-31) \* alinéas [0087] - [0089], [0092]; figures 1,2,3A-3D,4,5A-5E,8A-8F \* DOMAINES TECHNIQUES RECHERCHES (IPC) US 2004/263095 A1 (MIN BYOUNG OWN [KR] ET 9 1-8 A AL) 30 décembre 2004 (2004-12-30) 30 \* alinéas [0002], [0013] - [0017]; G09G figures 3,11 \* 35 40 45 Le présent rapport a été établi pour toutes les revendications 1 Lieu de la recherche Date d'achèvement de la recherche Examinateur 50 EPO FORM 1503 03.82 (P04C02) La Haye 25 février 2022 Ladiray, Olivier CATEGORIE DES DOCUMENTS CITES T : théorie ou principe à la base de l'invention E : document de brevet antérieur, mais publié à la X : particulièrement pertinent à lui seul Y : particulièrement pertinent : date de dépôt ou après cette date Dicité dans la demande particulièrement pertinent a lui seul particulièrement pertinent en combinaison avec un autre document de la même catégorie L : cité pour d'autres raisons arrière-plan technologique 55 O : divulgation non-ecine P : document intercalaire & : membre de la même famille, document correspondant

# EP 4 020 442 A1

# ANNEXE AU RAPPORT DE RECHERCHE EUROPEENNE RELATIF A LA DEMANDE DE BREVET EUROPEEN NO.

5

10

15

20

25

30

35

40

45

50

55

EP 22 15 7934

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités dans le rapport de

recherche européenne visé ci-dessus. Lesdits members sont contenus au fichier informatique de l'Office européen des brevets à la date du Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets.

25-02-2022

|                         | cument brevet cité |    | Date de     |    | Membre(s) de la     |            | Date de     |

|-------------------------|--------------------|----|-------------|----|---------------------|------------|-------------|

| au rapport de recherche |                    |    | publication |    | famille de brevet(s | 5)         | publication |

| US                      | 2017039935         | A1 | 09-02-2017  | CN | 106469539           | A          | 01-03-20    |

|                         |                    |    |             | EP | 3128511             | <b>A1</b>  | 08-02-20    |

|                         |                    |    |             | TW | 201706978           | A          | 16-02-20    |

|                         |                    |    |             | បន | 2017039935          | A1         | 09-02-20    |

| US                      | 2010245401         | A1 | 30-09-2010  | CN | 101816033           | A          | 25-08-20    |

|                         |                    |    |             | EP | 2208193             | A1         | 21-07-20    |

|                         |                    |    |             | GB | 2453375             | A          | 08-04-20    |

|                         |                    |    |             | JP | 5468544             | в2         | 09-04-20    |

|                         |                    |    |             | JP | 2010541015          | A          | 24-12-20    |

|                         |                    |    |             | KR | 20100089068         | A          | 11-08-20    |

|                         |                    |    |             | US | 2010245401          | A1         | 30-09-20    |

|                         |                    |    |             | WO | 2009044122          | A1         | 09-04-20    |

| US                      | <br>7187355        | B2 | 06-03-2007  | CN | 1397058             | <br>А      | 12-02-20    |

|                         |                    |    |             | DE | 60131552            | Т2         | 23-10-20    |

|                         |                    |    |             | EP | 1320846             | <b>A</b> 2 | 25-06-20    |

|                         |                    |    |             | GB | 2367413             | A          | 03-04-20    |

|                         |                    |    |             | JP | 2004510208          | A          | 02-04-20    |

|                         |                    |    |             | KR | 20020059432         | A          | 12-07-20    |

|                         |                    |    |             | TW | 1235012             | в          | 21-06-20    |

|                         |                    |    |             | US | 2003030629          | <b>A1</b>  | 13-02-20    |

|                         |                    |    |             | WO | 0227700             | <b>A</b> 2 | 04-04-20    |

| US                      | <br>2005067968     | A1 | 31-03-2005  | CN | 1604472             | <br>A      | 06-04-20    |

|                         |                    |    |             | JP | 3935891             | B2         | 27-06-20    |

|                         |                    |    |             | JP | 2005130432          | A          | 19-05-20    |

|                         |                    |    |             | បន | 2005067968          | <b>A1</b>  | 31-03-20    |

| US                      | <br>2004263095     | A1 | 30-12-2004  | CN | 1575082             | <br>А      | 02-02-20    |

|                         |                    |    |             | JP | 2005019375          | A          | 20-01-20    |

|                         |                    |    |             | KR | 20050000773         | A          | 06-01-20    |

|                         |                    |    |             | US | 2004263095          | <b>A1</b>  | 30-12-20    |

Pour tout renseignement concernant cette annexe : voir Journal Officiel de l'Office européen des brevets, No.12/82

# EP 4 020 442 A1

# RÉFÉRENCES CITÉES DANS LA DESCRIPTION

Cette liste de références citées par le demandeur vise uniquement à aider le lecteur et ne fait pas partie du document de brevet européen. Même si le plus grand soin a été accordé à sa conception, des erreurs ou des omissions ne peuvent être exclues et l'OEB décline toute responsabilité à cet égard.

# Documents brevets cités dans la description

• FR 1763313 [0001]