# (11) EP 4 060 650 A1

## (12)

# **DEMANDE DE BREVET EUROPEEN**

(43) Date de publication: 21.09.2022 Bulletin 2022/38

(21) Numéro de dépôt: 22162187.3

(22) Date de dépôt: 15.03.2022

(51) Classification Internationale des Brevets (IPC): G09G 3/00 (2006.01) G09G 3/20 (2006.01) G09G 3/32 (2016.01)

(52) Classification Coopérative des Brevets (CPC): G09G 3/32; G09G 3/003; G09G 3/2003; G09G 3/2011; G09G 3/2014; G09G 3/2081; G09G 2300/06; G09G 2310/0272; G09G 2310/0275; G09G 2310/0297

(84) Etats contractants désignés:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

Etats d'extension désignés:

**BA ME**

Etats de validation désignés:

KH MA MD TN

(30) Priorité: 18.03.2021 FR 2102701

(71) Demandeur: Commissariat à l'énergie atomique et aux énergies alternatives 75015 Paris (FR)

(72) Inventeur: VIGIER, Margaux 38054 GRENOBLE CEDEX 09 (FR)

(74) Mandataire: Cabinet Beaumont 4, Place Robert Schuman B.P. 1529 38025 Grenoble Cedex 1 (FR)

# (54) DISPOSITIF D'AFFICHAGE ÉMISSIF À LED

(57) La présente description concerne un module élémentaire (100) d'un dispositif d'affichage permettant d'afficher au moins un pixel d'une image, le module comportant :

- un premier ensemble de N LED (101(i,j)) réparties en M groupes (G(i)), au moins l'un des M groupes comportant au moins deux LED, où N et M sont des entiers, avec

M supérieurs ou égal à 2 ; et

- un circuit de commande comportant M circuits de polarisation (103(i)) associés respectivement aux M groupes de LED, chaque circuit de polarisation (103(i)) étant partagé par les LED du groupe (G(i)) correspondant et étant adapté à commander successivement en émission les LED du groupe.

Fig 1

## Description

### Domaine technique

[0001] La présente description concerne la réalisation d'un dispositif d'affichage d'images émissif à diodes électroluminescentes (LED), par exemple un écran de télévision, d'ordinateur, de smartphone, de tablette numérique, etc. Elle concerne plus particulièrement la réalisation d'un module élémentaire d'un tel dispositif.

# Technique antérieure

[0002] Il a déjà été proposé, par exemple dans la demande de brevet WO2017089676 ou dans les demandes de brevet WO2018185433 et WO2018185434, un dispositif d'affichage d'images comportant une pluralité de puces électroniques élémentaires, que l'on appellera ci-après modules élémentaires, disposées en matrice sur un même substrat de report. Les modules sont montés solidaires du substrat de report et connectés à des éléments de connexion électrique du substrat de report pour leur commande. Chaque module comporte une ou plusieurs LED et un circuit de commande de ladite une ou plusieurs LED et correspond à un pixel du dispositif. Plus particulièrement, chaque module comprend une première puce appelée puce de LED intégrant ladite une ou plusieurs LED du module, et une deuxième puce appelée puce de contrôle comportant le circuit de commande de ladite une ou plusieurs LED du module. La puce de LED et la puce de contrôle sont accolées et connectées électriquement l'une à l'autre, l'ensemble formant un module dit monolithique, autrement dit assemblage compact, comportant des bornes de connexion destinées à être connectées à des bornes de connexion correspondantes du substrat de report.

**[0003]** Il serait souhaitable de pouvoir améliorer au moins en partie certains aspects d'un dispositif d'affichage d'images de ce type.

# 25 Résumé de l'invention

[0004] Un mode de réalisation prévoit un module élémentaire d'un dispositif d'affichage permettant d'afficher au moins un pixel d'une image, le module comportant :

- un premier ensemble de N LED réparties en M groupes, au moins l'un des M groupes comportant au moins deux LED, où N et M sont des entiers, avec M supérieurs ou égal à 2 ; et

- un circuit de commande comportant M circuits de polarisation associés respectivement aux M groupes de LED, chaque circuit de polarisation étant partagé par les LED du groupe correspondant et étant adapté à commander successivement en émission les LED du groupe.

**[0005]** Selon un mode de réalisation, le module forme un assemblage compact d'une ou plusieurs puces électroniques, le module comportant une face de connexion comportant des plots de connexion destinés à être fixés et connectés électriquement à des plots de connexion correspondant d'un substrat de report.

[0006] Selon un mode de réalisation, chacun des M groupes comprend un même nombre L de LED, avec L entier supérieur ou égal à 2.

**[0007]** Selon un mode de réalisation, les circuits de polarisation sont configurés pour que, dans chaque groupe, pour chaque LED du groupe, une période d'émission de la LED soit concomitante à une période d'émission d'une LED correspondante de chaque autre groupe.

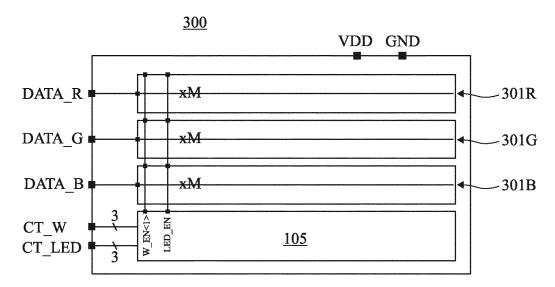

**[0008]** Selon un mode de réalisation, le circuit de commande est configuré pour, lors d'une période T\_TRAME, régler individuellement les puissances d'émission respectives des N LED.

**[0009]** Selon un mode de réalisation, la période T\_TRAME est divisée en L périodes successives Tj, avec j entier allant de 1 à L, chaque période Tj comportant une période d'initialisation T\_INIT suivie d'une période d'émission T\_E, le circuit de commande étant configuré pour, à chaque période Tj, pendant la période d'initialisation T\_INIT, appliquer successivement aux M circuits de polarisation un signal de réglage individuel de la puissance d'émission souhaitée de la LED de rang j du groupe de LED G(i) correspondant, puis, pendant la période d'émission, commander simultanément en émission les M LED de rang j en fonction desdits signaux de réglage individuels.

**[0010]** Selon un mode de réalisation, le module comporte au moins une borne de connexion à un dispositif extérieur, ladite borne étant destinée à recevoir des signaux de réglage individuels des puissances d'émission des N LED de la puce, multiplexés temporellement.

**[0011]** Selon un mode de réalisation, chaque circuit de polarisation comprend un interrupteur reliant ladite borne à un noeud de réglage de puissance lumineuse, et un ensemble d'interrupteurs, reliant respectivement les LED du groupe correspondant à un noeud de fourniture d'un courant de polarisation.

[0012] Selon un mode de réalisation, chaque circuit de polarisation comprend une source de courant de polarisation

35

45

50

10

réglable en intensité, la puissance d'émission de chacune des LED du groupe correspondant étant réglée en faisant varier le courant délivré par ladite source de courant.

**[0013]** Selon un mode de réalisation, chaque circuit de polarisation comprend une source de tension de polarisation fixe, la puissance d'émission de chacune des LED du groupe correspondant étant réglée par modulation du temps d'émission de la LED, par exemple selon une modulation à codage binaire.

**[0014]** Selon un mode de réalisation, chaque circuit de polarisation comprend une source de courant de polarisation réglable en intensité, la puissance d'émission de chacune des LED du groupe correspondant étant réglée en faisant varier le courant délivré par ladite source de courant et par modulation du temps d'émission de la LED, par exemple selon une modulation à codage binaire.

[0015] Selon un mode de réalisation, les N LED du premier ensemble sont d'une même première couleur, le module comportant en outre un deuxième ensemble de N LED d'une même deuxième couleur réparties en M groupes, au moins l'un des M groupes comportant au moins deux LED, et un troisième ensemble de N LED d'une même troisième couleur réparties en M groupes, au moins l'un des M groupes comportant au moins deux LED.

**[0016]** Selon un mode de réalisation, le premier ensemble de LED forme une puce de LED et le circuit de commande est un circuit intégré de type CMOS formant une puce de contrôle accolée à une face de la puce de LED.

**[0017]** Selon un mode de réalisation, le module est configuré pour afficher un unique pixel de même coordonnée spatiale pour un ensemble de N images de mêmes dimensions, les N LED du module correspondant à N sous-pixels d'un même pixel, chaque sous-pixel permettant d'afficher un pixel d'une des N images correspondant respectivement à N angles de vues d'un dispositif d'affichage multi-vues.

[0018] Un autre mode de réalisation prévoit un dispositif d'affichage comportant un substrat de report et une pluralité de modules tels que définis ci-dessus disposés en matrice sur le substrat de report, les modules étant montés solidaires du substrat de report et connectés à des éléments de connexion électrique du substrat de report, destinés à amener des signaux d'alimentation et de contrôle des modules.

# 25 Brève description des dessins

10

15

35

40

45

50

55

**[0019]** Ces caractéristiques et avantages, ainsi que d'autres, seront exposés en détail dans la description suivante de modes de réalisation particuliers faite à titre non limitatif en relation avec les figures jointes parmi lesquelles :

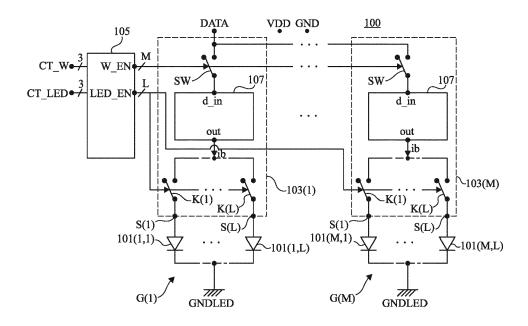

30 la figure 1 est un schéma électrique des circuits d'un exemple d'un module élémentaire d'un dispositif d'affichage selon un mode de réalisation;

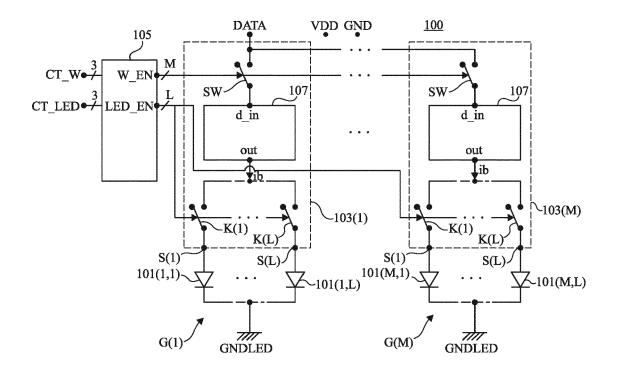

la figure 2 est un chronogramme illustrant un exemple de fonctionnement du module élémentaire de la figure 1;

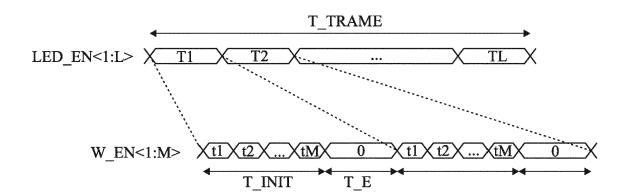

la figure 3 est une représentation schématique simplifiée d'un autre exemple d'un module élémentaire d'un dispositif d'affichage selon un mode de réalisation ;

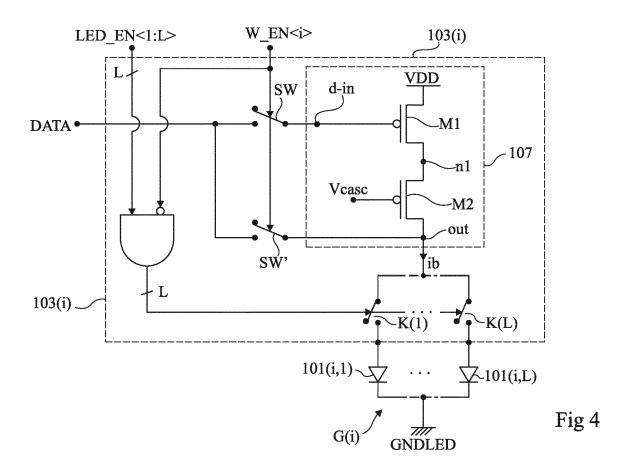

la figure 4 illustre plus en détail un exemple d'un circuit de commande d'un module élémentaire selon un mode de réalisation ;

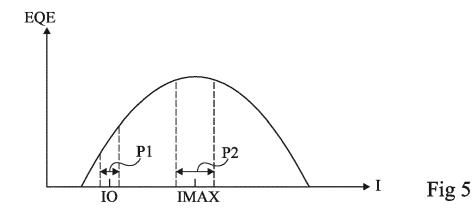

la figure 5 représente un exemple d'une courbe caractéristique du rendement quantique d'une LED;

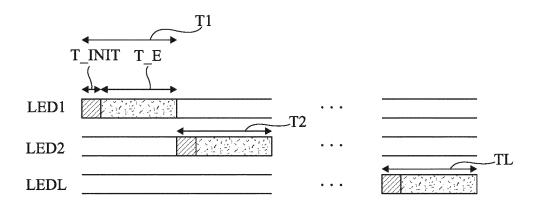

la figure 6 illustre un exemple de fonctionnement d'un module élémentaire selon un mode de réalisation ;

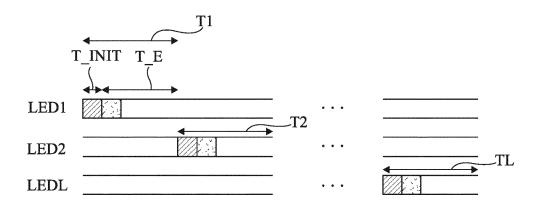

la figure 7 illustre un autre exemple de fonctionnement d'un module élémentaire selon un mode de réalisation ;

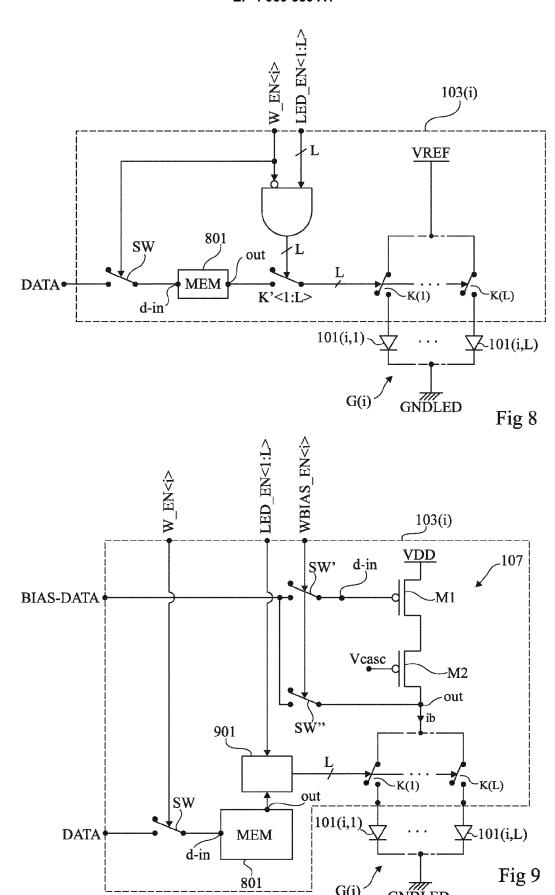

la figure 8 illustre plus en détail un autre exemple d'un circuit de commande d'un module élémentaire selon un mode de réalisation ; et

la figure 9 illustre plus en détail un autre exemple d'un circuit de commande d'un module élémentaire selon un mode de réalisation.

## Description des modes de réalisation

**[0020]** De mêmes éléments ont été désignés par de mêmes références dans les différentes figures. En particulier, les éléments structurels et/ou fonctionnels communs aux différents modes de réalisation peuvent présenter les mêmes références et peuvent disposer de propriétés structurelles, dimensionnelles et matérielles identiques.

[0021] Par souci de clarté, seuls les étapes et éléments utiles à la compréhension des modes de réalisation décrits

ont été représentés et sont détaillés. En particulier, la fabrication des modules élémentaires des dispositifs d'affichage décrits n'a pas été détaillée, la fabrication de tels modules étant à la portée de l'homme du métier à partir des enseignements de la présente description. Chaque module élémentaire est destiné à être monté solidaire d'un substrat de report et connecté à des éléments de connexion électrique du substrat de report pour sa commande. Chaque module élémentaire comprend une puce monolithique ou un assemblage de plusieurs puces monolithiques connectées électriquement. De façon générale, un module élémentaire est un assemblage compact d'une ou plusieurs puces électroniques avantageusement obtenues selon des procédés de fabrication de composants microélectroniques. Une pluralité de modules, par exemple identiques ou similaires, peuvent être montés sur un même substrat de report, chaque module correspondant par exemple à un pixel du dispositif d'affichage. A titre d'exemple, les modules élémentaires des dispositifs d'affichage décrits, comportent chacun une pluralité de LED et un circuit de commande à base de transistors, et peuvent être fabriqués selon des procédés identiques ou similaires à ceux décrits dans la demande de brevet WO2017089676 susmentionnée.

10

30

35

40

45

50

55

[0022] Sauf précision contraire, lorsque l'on fait référence à deux éléments connectés entre eux, cela signifie directement connectés sans éléments intermédiaires autres que des conducteurs, et lorsque l'on fait référence à deux éléments reliés (en anglais "coupled") entre eux, cela signifie que ces deux éléments peuvent être connectés ou être reliés par l'intermédiaire d'un ou plusieurs autres éléments.

**[0023]** Sauf précision contraire, les expressions "environ", "approximativement", "sensiblement", et "de l'ordre de" signifient à 10 % près, de préférence à 5 % près.

[0024] La figure 1 est un schéma électrique des circuits d'un exemple d'un pixel 100 d'un dispositif d'affichage selon un mode de réalisation. Dans cet exemple, le module 100 est un module monolithique constitué par un assemblage d'une puce de contrôle et d'une puce de LED. La puce de LED est par exemple disposée sur et en contact avec la puce de contrôle. A titre d'exemple, la puce de LED comporte, du côté de sa face inférieure, des bornes de connexion électrique connectées électriquement à des bornes de connexion électrique disposées du côté de la face supérieure de la puce de contrôle.

[0025] On considère plus particulièrement, dans cet exemple, la réalisation d'un dispositif d'affichage dit multi-vues, c'est-à-dire dans lequel l'image à afficher est divisée en pixels comportant chacun une pluralité de sous-pixels correspondant à des vues différentes de la scène que l'on souhaite reproduire. A titre d'exemple, les différents sous-pixels d'un même pixel correspondent respectivement à un même pixel de différentes images d'une même scène, prises sous des angles de vue différents. Un dispositif d'affichage multi-vues peut par exemple être utilisé dans des applications dans lesquelles on souhaite donner à l'utilisateur une impression de visualisation en trois dimensions.

[0026] Dans l'exemple de la figure 1, le dispositif d'affichage est un dispositif monochromatique. Chaque module 100 comprend en ensemble de N LED élémentaires 101 de même couleur, c'est-à-dire ayant une même longueur d'onde centrale d'émission, avec N entier, de préférence supérieur ou égal à 4, formant la puce de LED du module. Les N LED 101 sont par exemple identiques aux dispersions de fabrication près. Les N LED du module sont contrôlables individuellement et correspondent respectivement à N sous-pixels d'un pixel multi-vues. Chaque module comprend en outre, accolé et connecté électriquement à la puce de LED, un circuit intégré de commande des N LED, par exemple un circuit CMOS (de l'anglais "Complementary Metal Oxyde Semiconductor" - métal oxyde semiconducteur complémentaire), formant la puce de contrôle du module.

[0027] Un dispositif d'affichage peut comprendre une pluralité de modules élémentaires 100, identiques ou similaires, disposés sur un même substrat de report, par exemple selon un agencement matriciel. Le substrat de report est par exemple un substrat de report passif, comportant des éléments de connexion électrique pour l'alimentation et la commande des modules.

[0028] Dans l'exemple de la figure 1, les N LED 101 du module 100 sont répartie en M groupes G(1),..., G(M) de L LED chacun, avec M et L entiers supérieurs ou égaux à 2. On désigne ci-après par la référence 101(i,j) la LED 101 de rang j du groupe G(i), avec i entier allant de 1 à M et j entier allant de 1 à L.

**[0029]** Dans l'exemple de la figure 1, le circuit de commande du module 100 comprend M circuits de polarisation 103(1),..., 103(M) associés respectivement aux M groupes de LED G(1),..., G(M). Le circuit de commande du module 100 comprend en outre un circuit 105 de contrôle des M circuits de polarisation 103(i).

[0030] Les M circuits de polarisation 103(1),..., 103(M) sont par exemple identiques, aux dispersions de fabrication près. Chaque circuit de polarisation 103(i) comprend L noeuds de sortie S(1),..., S(L) reliés, de préférence connectés, respectivement aux anodes des L LED 101(i,1),..., 101(i,L) du groupe G(i) correspondant. Dans cet exemple, dans chaque groupe G(i) de LED, les cathodes des LED sont reliées, de préférence connectées, à un même noeud d'application d'un potentiel de référence fixe GNDLED du module, par exemple la masse. A titre de variante (non représentée), les orientations des LED peuvent être inversées. Autrement dit, chaque LED 101(i,j) peut avoir sa cathode reliée, par exemple connectée, au noeud de sortie correspondant S(j) du circuit de polarisation 103(i), et son anode reliée, par exemple connectée, à une borne d'application d'un potentiel de référence. Le circuit de polarisation 103 peut alors être un circuit CMOS complémentaire de celui décrit précédemment.

[0031] Dans l'exemple de la figure 1, chaque circuit de polarisation 103(i) comprend une source de courant de pola-

risation 107 commune aux L LED 101(j) du groupe G(i) correspondant. La source de courant de polarisation 107 comprend un noeud d'entrée d\_in destiné à recevoir un signal de consigne de réglage du courant de polarisation délivré par la source 107. La source de polarisation 107 comprend en outre un noeud de sortie out destiné à fournir un courant de polarisation ib fonction de la valeur du signal de consigne appliqué sur le noeud d\_in.

[0032] Dans cet exemple, chaque circuit de polarisation 103(i) comprend en outre L interrupteurs k(1),..., k(L) commandables individuellement, reliant respectivement les L nœuds de sortie S(1),..., S(L) du circuit 103(i) au noeud de sortie out de la source de courant de polarisation 107 du circuit 103(i). Chaque interrupteur K(j) a un premier noeud de conduction relié, par exemple connecté, au noeud out de la source de courant de polarisation 107 du circuit 103(i), et un deuxième noeud de conduction relié, par exemple connecté, au noeud de sortie S(j) de même rang j du circuit 103(i). [0033] Dans l'exemple de la figure 1, chaque circuit de polarisation 103(i) comprend en outre un interrupteur SW. L'interrupteur SW relie le noeud de commande d\_in de la source de courant 107 à une borne DATA d'application d'un signal de commande du module 100. Plus particulièrement, l'interrupteur SW a un premier noeud de conduction relié, par exemple connecté, à la borne DATA, et un deuxième noeud de conduction relié, par exemple connecté, au noeud d\_in. La borne d'entrée DATA est commune à toutes les LED du module 100. Les signaux de réglage de luminosité individuels des M\*L LED 101 sont multiplexés temporellement sur la borne DATA. Les M interrupteurs SW et les M\*L interrupteurs K(j) du module permettent de démultiplexer les signaux de réglage de luminosité de façon à commander individuellement les M\*L LED 101.

[0034] Le circuit de contrôle 105 permet de commander les M interrupteurs SW et les M\*L interrupteurs K(j). Plus particulièrement, dans cet exemple, le circuit de contrôle 105 génère un signal de commande W\_EN sur M bits pour commander respectivement les M interrupteurs SW. Dans cet exemple, le signal W\_EN est fourni sur un port parallèle de M nœuds de sortie du circuit 105, connectés respectivement aux nœuds de commande des M interrupteurs SW. Le circuit de contrôle 105 génère en outre un signal de commande LED\_EN sur L bits pour contrôler respectivement les L interrupteurs K(j) de chaque circuit de polarisation 103(i). Dans cet exemple, le même signal de commande LED\_EN est appliqué en parallèle aux M circuits de polarisation 103(i). Le signal LED\_EN est fourni sur un port parallèle de L nœuds de sortie du circuit 105, connectés respectivement aux nœuds de commande des L interrupteurs K(j) de chacun des M circuits de polarisation 103(i). Ainsi, chaque bit LED\_EN<j> du signal LED\_EN est appliqué simultanément sur les nœuds de commande des M interrupteurs K(j) de même rang j du circuit de commande. Autrement dit, pour chaque rang j allant de 1 à L, les M interrupteurs K(j) de même rang j sont tous commandés simultanément dans le même état. Ainsi, pour chaque rang j allant de 1 à L, les M LED 101(i,j) de même rang j sont toutes simultanément activées en émission ou sont toutes simultanément désactivées.

[0035] La figure 2 est un chronogramme illustrant un exemple de fonctionnement du module 100 de la figure 1.

30

35

50

[0036] On a représenté schématiquement sur la figure 2 l'évolution, en fonction du temps, des signaux de commande W EN (M bits) et LED EN (L bits) fournis par le circuit de contrôle 105.

[0037] On définit ci-après une période T\_TRAME correspondant au temps disponible pour commander individuellement les M\*L LED 101 du module 100 selon respectivement M\*L niveaux de luminosités spécifiques. A chaque nouvelle période T\_TRAME, les niveaux de luminosités des M\*L LED 101 peuvent être modifiés.

**[0038]** La période T\_TRAME est divisées en L périodes successives T1, T2, ... TL, par exemple sensiblement de même durée, par exemple sensiblement égale à T\_TRAME/L.

**[0039]** Pendant chaque période Tj, les M LED 101(1,j), ... 101(M,j) de même rang j du module sont commandées simultanément en émission. Les autres LED 101 sont désactivées.

**[0040]** Plus particulièrement, dans cet exemple, chaque période Tj est divisée en deux périodes successives T\_INIT et T\_E. La période T\_INIT est une période d'initialisation et la période T\_E est une période d'émission.

[0041] Pendant la période T\_INIT, les signaux de réglage des M LED 101(1,j),..., 101(M,j), reçus séquentiellement sur la borne d'entrée DATA du module, sont successivement appliqués sur les bornes d'entrée d\_in des sources de courant de polarisation 107 respectives des M circuits de polarisation 103(i). Plus particulièrement, dans cet exemple, la période T\_INIT est divisée en M périodes successives t1,..., tM, par exemple sensiblement de même durée, par exemple sensiblement égale à T\_INIT/M. A chaque période ti, avec i allant de 1 à M, l'interrupteur SW du circuit de polarisation 103(i) est commandé à l'état fermé (passant), les autres interrupteurs SW étant maintenus ouverts (bloqués). Le signal de réglage appliqué sur la borne DATA est ainsi transmis sur la borne d'entrée d\_in de la source de polarisation 107 du circuit de polarisation 103(i). Ainsi, les sources de courant de polarisation 107 des M circuits de polarisation 103(i) sont successivement réglées à des valeurs de courant correspondant aux niveaux de luminosité respectifs souhaités des LED 101(1,j), ..., 101(M,j).

**[0042]** Pendant la période d'émission T\_E, les interrupteurs K(j) des M circuits de polarisation 103(i) sont simultanément fermés, tandis que les autres interrupteurs K sont tous maintenus ouverts. Ainsi, les LED 101(1,j), ..., 101(M,j) émettent simultanément à des niveaux de luminosités fixés individuellement lors de la période T\_INIT. Les autres LED 101 restent inactives. Pendant la période d'émission T\_E, les M interrupteurs SW peuvent être tous commandés simultanément à l'état ouvert.

[0043] A l'issue de la période d'émission T\_E, une nouvelle période Tj+1 débute, au cours de laquelle les LED

101(1,j+1), ..., 101(M,j+1) sont réglées individuellement puis commandées simultanément en émission.

10

30

35

50

[0044] On réalise ainsi, en parallèle dans les M groupes de LED G(i), un balayage séquentiel des L LED 101 de chaque groupe G(i).

[0045] Un avantage de l'architecture de la figure 1 et du fonctionnement décrit en relation avec la figure 2 est lié à la prévision de circuits de polarisation 103(i) partagés par groupes de L LED 101. Ceci permet de limiter l'encombrement global du circuit de commande des LED. En particulier, la taille du circuit de contrôle 105 est relativement restreinte. A titre d'exemple, le circuit de contrôle 105 peut comporter deux registres à décalage, non détaillés sur la figure, de respectivement L bits et M bits, pour générer respectivement les signaux LED\_EN et W\_EN.

[0046] Le nombre de bornes de connexion à l'extérieur du module 100 est en outre relativement faible du fait du multiplexage temporel des signaux de données sur une unique borne DATA. A titre d'exemple, en plus de la borne DATA, le module 100 peut comprendre une borne VDD de connexion à un potentiel d'alimentation haut et une borne GND de connexion à un potentiel d'alimentation bas. Chaque source de courant de polarisation 107 peut avoir un noeud d'alimentation relié, par exemple connecté, à la borne VDD (connexions non détaillées sur la figure 1). La borne GND peut être reliée, par exemple connectée, au noeud GNDLED (connexion non détaillée sur la figure 1). Le module 100 peut en outre comprendre une ou plusieurs bornes d'applications de signaux de contrôle. A titre d'exemple, le module 100 peut comprendre un port CT\_W constitué de trois bornes (non détaillées sur la figure 1) d'application de signaux de contrôle du registre à décalage générant le signal W\_EN, et un port CT\_LED constitué de trois bornes (non détaillées sur la figure 1) d'application de signaux de contrôle du registre à décalage générant le signal LED EN. Le port CT W comprend par exemple une première borne d'application d'un signal d'horloge du registre à décalage générant le signal W\_EN, une deuxième borne d'application d'un signal de réinitialisation du registre à décalage générant le signal W\_EN, et une troisième borne d'application d'un signal d'initialisation du registre à décalage générant le signal W\_EN. Le port CT\_LED comprend par exemple une première borne d'application d'un signal d'horloge du registre à décalage générant le signal LED\_EN, une deuxième borne d'application d'un signal de réinitialisation du registre à décalage générant le signal LED EN, et une troisième borne d'application d'un signal d'initialisation du registre à décalage générant le signal LED\_EN. Ainsi, dans cet exemple, le module 100 présente, en plus des connexions électriques internes entre la puce de LED et la puce de contrôle, 9 bornes de connexion électrique, destinées à être connectées respectivement à des bornes de connexion correspondantes du substrat de report.

[0047] La figure 3 est une représentation schématique simplifiée d'un autre exemple d'un module 300 d'un dispositif d'affichage selon un mode de réalisation.

[0048] Le module 300 de la figure 3 diffère du module 100 de la figure 1 principalement en ce que, dans le module 300, la puce de LED comprend des LED de plusieurs couleurs, c'est-à-dire ayant des longueurs d'ondes centrales d'émission distinctes. Dans l'exemple de la figure 3, la puce de LED du module 300 comprend des LED de trois couleurs distinctes, par exemple des premières adaptées à émettre majoritairement de la lumière rouge, des deuxièmes adaptées à émettre majoritairement de la lumière bleue. Comme dans l'exemple de la figure 1, le module 300 comprend, accolée et connectée électriquement à la puce de LED, une puce de contrôle adaptée à commander individuellement les LED de la puce de LED.

[0049] Dans l'exemple de la figure 3, l'ensemble comportant les M\*L LED élémentaires 101, les M circuits de polarisation 103(i) et la borne d'entrée de donnée DATA du module de la figure 1 est répliqué trois fois (une fois par couleur), avec respectivement trois types de LED élémentaires de couleurs différentes. Les M circuits de polarisation 103(i) peuvent éventuellement être adaptés à fournir des courants moyens différents selon qu'ils sont connectés aux LED rouges, bleues ou vertes, mais leur structure reste inchangée.

[0050] Sur la figure 3, les bornes d'entrée de donnée correspondant aux trois couleurs d'émission sont désignées respectivement par les références DATA\_R, DATA\_G et DATA\_B. De plus, on désigne par la référence 301R l'ensemble des M\*L LED 101 rouges et des circuits de polarisation 103(i) correspondants, par la référence 301G l'ensemble des M\*L LED 101 vertes et des circuits de polarisation 103(i) correspondants, et par la référence 301B l'ensemble des M\*L LED 101 bleues et des circuits de polarisation 103(i) correspondants.

**[0051]** Dans l'exemple de la figure 3, le circuit de contrôle 105 est partagé par les trois couleurs. Ce circuit et son fonctionnement sont par exemple identiques ou similaires à ce qui a été décrit en relation avec les figures 1 et 2.

**[0052]** Ainsi, si l'on se réfère à la figure 2, pendant chaque période Tj de la période T\_TRAME, les M LED 101 de même rang j de l'ensemble 301R, les M LED 101 de même rang j de l'ensemble 301B sont commandées simultanément en émission, les autres LED 101 étant désactivées.

[0053] Plus particulièrement, pendant la période d'initialisation T\_INIT de la phase Tj, les signaux de réglage des M LED 101(1,j),..., 101(M,j) de l'ensemble 301R, reçus séquentiellement sur la borne d'entrée DATA\_R du module, sont successivement appliqués sur les bornes d'entrée d\_in des sources de courant de polarisation 107 respectives des M circuits de polarisation 103(i) de l'ensemble 301R, de façon identique ou similaire à ce qui a été décrit ci-dessus. En parallèle, et de façon similaire, les signaux de réglage des M LED 101(1,j),..., 101(M,j) de l'ensemble 301G, reçus séquentiellement sur la borne d'entrée DATA\_G du module, sont successivement appliqués sur les bornes d'entrée d\_in des sources de courant de polarisation 107 respectives des M circuits de polarisation 103(i) de l'ensemble 301G,

et les signaux de réglage des M LED 101(1,j),..., 101(M,j) de l'ensemble 301B, reçus séquentiellement sur la borne d'entrée DATA\_B du module, sont successivement appliqués sur les bornes d'entrée d\_in des sources de courant de polarisation 107 respectives des M circuits de polarisation 103(i) de l'ensemble 301B.

[0054] Plus particulièrement, à chaque période ti de la période T\_INIT de la phase Tj, avec i allant de 1 à M, dans chacun des ensembles 301R, 301G et 301B, l'interrupteur SW du circuit de polarisation 103(i) est commandé à l'état fermé (passant), les autres interrupteurs SW étant maintenus ouverts (bloqués). Le signal de réglage appliqué sur la borne DATA\_R, respectivement DATA\_G, respectivement DATA\_B, est ainsi transmis sur la borne d'entrée d\_in de la source de polarisation 107 du circuit de polarisation 103(i) de l'ensemble 301R, respectivement 301G, respectivement 301B. Ainsi, dans chacun des ensembles 301R, 301G et 301B, les sources de courant de polarisation 107 des M circuits de polarisation 103(i) sont successivement réglées à des valeurs de courant correspondant aux niveaux de luminosité respectifs souhaités des LED 101(1,j), ..., 101(M,j) de l'ensemble.

[0055] Pendant la période d'émission T\_E, dans chacun des ensembles 301R, 301G et 301B, les interrupteurs K(j) des M circuits de polarisation 103(i) sont simultanément fermés, tandis que les autres interrupteurs K sont tous maintenus ouverts. Ainsi, les LED 101(1,j), ..., 101(M,j) de l'ensemble émettent simultanément à des niveaux de luminosités fixés individuellement lors de la période T\_INIT. Les autres LED 101 restent inactives. Pendant la période d'émission T\_E, les M interrupteurs SW peuvent être tous commandés simultanément à l'état ouvert.

**[0056]** Dans l'exemple de la figure 3, le module 300 présente, en plus des connexions électriques internes entre la puce de LED et la puce de contrôle, 11 bornes de connexion électrique, destinées à être connectées respectivement à des bornes de connexion correspondantes du substrat de report.

[0057] La figure 4 illustre plus en détail un exemple d'un circuit de commande d'un module selon un mode de réalisation. La figure 4 illustre plus particulièrement un exemple de réalisation d'un circuit de polarisation 103(i) du module 100 de la figure 1.

[0058] Dans cet exemple, le circuit de polarisation 103(i) comprend deux transistors M1 et M2 formant une source de courant cascodée. Dans l'exemple représenté, les transistors M1 et M2 sont des transistors MOS à canal P. Le transistor M1 a sa source reliée, par exemple connectée, au noeud VDD et son drain relié, par exemple connecté, à un noeud intermédiaire n1. Le transistor M2 a sa source reliée, par exemple connectée, au noeud n1 et son drain relié, par exemple connecté, au noeud out. La grille du transistor M1 est reliée, par exemple connectée, au noeud d\_in. La grille du transistor M2 est reliée, par exemple connectée, à un noeud d'application d'une tension fixe Vcasc. Dans cet exemple, chaque circuit de polarisation 103(i) comprend en outre un interrupteur SW' reliant le noeud de sortie out de la source de courant 107 à la borne DATA. L'interrupteur SW' a un premier noeud de conduction relié, par exemple connecté, à la borne DATA, et un deuxième noeud de conduction relié, par exemple connecté, au noeud out. L'interrupteur SW' a un noeud de commande relié, par exemple connecté, au noeud W\_EN<i>. Dans chaque circuit de polarisation 103(i), les interrupteurs SW et SW' du circuit de polarisation sont par exemple commandés simultanément dans le même état. Lorsque les interrupteurs SW et SW' sont à l'état fermé, le drain du transistor M2 se trouve relié, par exemple connecté, à la grille du transistor M1. La différence de potentiel appliquée entre les noeuds d\_in et VDD définit l'intensité du courant de polarisation ib délivré par la source de courant 107 sur son noeud de sortie out, et donc l'intensité lumineuse d'émission de la LED 101(i,j) à laquelle est appliqué le courant ib. La capacité grille-source du transistor M1 (non détaillée sur la figure) permet de maintenir la tension entre les nœuds d in et VDD sensiblement constante pendant toute la durée d'émission de la LED.

30

35

[0059] A titre de variante, le montage cascode peut être remplacé par un simple transistor. Dans ce cas, le transistor M2 est omis, le drain du transistor M1 étant alors directement relié, par exemple connecté, au noeud out. Plus généra-lement, la personne du métier saura prévoir d'autres implémentations de la source de courant 107. Dans une autre variante, un contrôle en tension peut être prévu. Dans ce cas, le transistor M2 peut être omis et le transistor M1 peut être remplacé par un transistor MOS à canal N agissant en suiveur de tension.

[0060] Dans l'exemple de la figure 4, le signal de contrôle W\_EN<i> commande directement l'interrupteur SW reliant le noeud d'entrée d\_in de la source de courant 107 à la borne DATA et l'interrupteur SW' reliant le noeud de sortie out de la source de courant 107 à la borne DATA. Par ailleurs, dans cet exemple, les interrupteurs K(1), ..., K(L) sont commandés non pas directement par le signal LED\_EN<1:L> mais par une combinaison du signal LED\_EN<1:L> et du signal W\_EN(i) complémenté. Autrement dit, chaque interrupteur K(j) est commandé à l'état fermé (passant) uniquement lorsque le signal LED\_EN<j> est à l'état haut et que le signal W\_EN<i> est à l'état bas (interrupteur SW du circuit 103(i) ouvert).

[0061] Dans les exemples décrits ci-dessus, si l'on néglige le temps d'initialisation des circuits de polarisation des LED, le temps d'émission T\_E de chaque LED est sensiblement égal à T\_TRAME/L. Ainsi, par rapport à un dispositif d'affichage non multiplexé, c'est-à-dire dans lequel toutes les LED émettent simultanément pendant toute la période T\_TRAME, l'intensité du courant de polarisation ib doit être multipliée par L pour obtenir un niveau de luminosité équivalent. Ceci constitue un avantage dans la mesure où les LED présentent généralement une meilleure efficacité quantique externe (EQE) pour des courants de polarisation élevés. Le nombre M de circuits de polarisation 103(i) et par conséquent le nombre L de LED élémentaires adressées par chaque circuit de polarisation 103(i) peuvent être choisis de façon à

maximiser l'efficacité quantique externe.

[0062] La figure 5 est un diagramme représentant de façon schématique l'évolution de l'efficacité quantique externe EQE (en ordonnée) d'une LED en fonction de la densité I (en abscisse) de courant de polarisation appliqué à la LED.

**[0063]** Comme cela apparait sur la figure, l'efficacité quantique externe présente une forme en cloche avec un maximum pour une valeur de courant IMAX. On désigne par l0 l'intensité moyenne de la plage P1 dans laquelle on souhaiterait polariser les LED dans le cas d'une émission continue pendant toute la durée T\_TRAME (i.e. dans un dispositif non multiplexé). Dans cet exemple, la valeur I0 est inférieure à la valeur IMAX.

[0064] En considérant l'exemple de la figure 1, si le rapport IMAX/I0 est inférieur à N-1, N étant le nombre de souspixels, correspondant au nombre de vues différentes, du pixel multi-vues, on choisira de préférence L égal à E[IMAX/I0] +1, où E[IMAX/I0] désigne la partie entière de IMAX/I0, et M égal à E[(N-1)/L]+1. On aura alors un temps d'émission par LED sensiblement égal à T\_TRAME/L et par conséquent un courant de polarisation moyen ILED de chaque LED sensiblement égal à I0\*L, c'est à dire sensiblement égal à I0\*(E[IMAX/I0]+1). Ainsi, le courant ILED approche le courant IMAX par valeur supérieure. Ceci permet de maximiser l'efficacité quantique externe des LED.

**[0065]** Cette configuration est illustrée schématiquement par la figure 6 (en considérant les durées des phases d'initialisation T\_INIT comme négligeables).

[0066] Si le rapport IMAX/I0 est supérieur à N-1, il est préférable que le temps d'émission de chaque LED soit inférieur à T\_TRAME/L pour avoir un courant de polarisation moyen I0 approchant le courant IMAX. Chaque période Tj de la période T\_TRAME peut alors comprendre une période d'extinction de la LED. Autrement dit, chaque LED émet pendant une partie seulement de la période T\_E impartie pour l'émission.

[0067] Cette configuration est illustrée schématiquement par la figure 7 (en considérant là encore les durées des phases d'initialisation T\_INIT comme négligeables).

[0068] Sur la figure 5, on a représenté schématiquement une plage P2 centrée sur le courant IMAX, correspondant à la transposition de la plage P1 autour de la valeur IMAX du fait de la réduction du temps d'émission effectif de chaque LFD.

[0069] La figure 8 illustre plus en détail un autre exemple d'un circuit de commande d'un module selon un mode de réalisation. La figure 8 illustre plus particulièrement une variante de réalisation d'un circuit de polarisation 103(i) du module 100 de la figure 1. Dans la suite de la description, seules les différences par rapport au circuit de polarisation 103(i) de la figure 1 seront mises en exergue.

[0070] Dans cet exemple, le circuit 103(i) est un circuit de polarisation temporel. Autrement dit, la tension de polarisation appliquée aux LED a une valeur fixe. Les niveaux de luminosités individuels des LED sont contrôlés par modulation du temps d'émission de chaque LED. Avec un taux de rafraichissement suffisamment élevé, par exemple supérieur ou égal à 50 trames par secondes, la persistance rétinienne permet de moyenner la luminance perçue en provenance de chaque LED pendant chaque période T\_TRAME. A titre d'exemple, la modulation des temps d'émission de chaque LED est une modulation à codage binaire, par exemple une modulation de type BCM (de l'anglais "Binary Code Modulation" - modulation codée binaire). En désignant par L\_PERCUE la luminance perçue, par L0 la luminance fixe définie par la tension de polarisation fixe VREF appliquée aux LED, par n le nombre de bits sur lequel est codée l'information de luminosité, et par bk le bit de poids k du codage, avec k entier allant de 1 à n, on a :

[Math 1]

$L_{PERCUE} = \sum_{k=1}^{n} bk \frac{L0}{M * 2^{n+1-k}}$

45

50

30

35

40

**[0071]** Dans l'exemple de la figure 8, la source de courant 107 est omise, et les interrupteurs K(1), ... K(L) relient directement les anodes respectives des LED 101(i,1), ... 101(i,L) à un même noeud d'application d'un potentiel de polarisation fixe VREF.

[0072] Dans cet exemple, l'information de luminosité est stockée sous forme binaire dans un circuit mémoire ou un registre 801 (MEM) du circuit 103(i), pendant la période ti de la phase T\_INIT de chaque période Tj de la période T TRAME.

[0073] L'interrupteur SW relie la borne DATA à un noeud d'entrée d\_in du circuit mémoire 801. Pendant la phase d'émission T\_E de chaque LED 101(i,j) du groupe G(i), l'interrupteur K(j) correspondant (c'est-à-dire de même rang j) est commandé alternativement à l'état fermé et à l'état ouvert selon un motif de modulation fixé par le code numérique de n bits stocké dans le circuit mémoire 801. Les autres interrupteurs K(j) sont maintenus ouverts.

**[0074]** Dans l'exemple de la figure 8, le circuit de polarisation 103(i) comprend L interrupteurs K'<1>, ... K'<L>. Chaque interrupteur K'<j> a un premier noeud de conduction relié, par exemple connecté, à un noeud de sortie out du circuit mémoire 801, et un deuxième noeud de conduction relié, par exemple connecté, à un noeud de commande de l'inter-

rupteur K(j) de même rang j. Pendant la phase d'émission T\_E de chaque LED 101(i,j), l'interrupteur K'(j) correspondant est maintenu fermé, les autres interrupteurs K' du circuit 103(i) étant maintenus ouverts. Ainsi les n bits du code de luminosité sont appliqués successivement sur le noeud de commande de l'interrupteur K(j), ce qui permet de contrôler la puissance lumineuse moyenne émise par la LED 101(i,j).

[0075] Dans l'exemple de la figure 8, le signal de contrôle W\_EN<i> commande directement l'interrupteur SW reliant la borne DATA au noeud d'entrée d\_in du circuit mémoire 801. Par ailleurs, dans cet exemple, les interrupteurs K'(1), ..., K'(L) sont commandés non pas directement par le signal LED\_EN<1:L> mais par une combinaison du signal LED\_EN<1:L> et du signal W\_EN(i) complémenté. Autrement dit, chaque interrupteur K' (j) est commandé à l'état fermé (passant) uniquement lorsque le signal LED\_EN<j> est à l'état haut et que le signal W\_EN<i> est à l'état bas (interrupteur SW du circuit 103(i) ouvert).

**[0076]** Plus généralement, la personne du métier saura adapter les modes de réalisation décrits à d'autres types de circuits de polarisation à modulation temporelle du temps d'émission des LED, par exemple des circuits du type décrit dans la demande de brevet FR3076396A1.

[0077] La figure 9 illustre plus en détail un autre exemple d'un circuit de commande d'un module selon un mode de réalisation. La figure 9 illustre plus particulièrement une variante de réalisation d'un circuit de polarisation 103(i) du module 100 de la figure 1. Dans la suite de la description, seules les différences par rapport au circuit de polarisation 103(i) de la figure 1 seront mises en exergue.

**[0078]** Dans cet exemple, le circuit 103(i) combine un contrôle de luminosité par réglage de l'intensité du courant de polarisation des LED, tel que décrit en relation avec les figures 1 et 4, et par modulation temporelle, tel que décrit en relation avec la figure 8.

[0079] Plus particulièrement, dans l'exemple de la figure 9, le circuit 103(i) comprend les mêmes éléments que dans l'exemple de la figure 8, agencés sensiblement de la même manière, et comprend en outre une source de courant réglable 107 identique ou similaire à ce qui a été décrit en relation avec les figures 1 et 4. Le noeud de sortie out de la source de courant est relié, par exemple connecté, aux extrémités des interrupteurs K(1), ... K(L) opposées aux LED 101. Le circuit 103(i) comprend en outre un interrupteur SW' reliant le noeud d'entrée d\_in de la source de courant 107 à une borne d'entrée de donnée supplémentaire BIAS\_DATA du module, et un interrupteur SW" reliant le noeud de sortie out de la source de courant 107 à la borne BIAS\_DATA.

**[0080]** Les interrupteurs SW' et SW" des M circuits 103(i) sont commandés par un signal WBIAS\_EN sur M bits, par exemple identique au signal W\_EN. Dans chaque circuit 103(i), les interrupteurs SW' et SW" sont par exemple commandés simultanément dans le même état par le signal WBIAS\_EN<i>.

30

35

45

50

55

[0081] Sur la figure 9, on a en outre représenté un circuit logique 901, intégrant notamment les interrupteurs K'<j> de la figure 8. Le circuit logique 901 reçoit le signal de commande LED\_EN (sur L bits) et les codes de modulation binaires fournis sur le noeud de sortie out du circuit mémoire 801, et génère les signaux de commande des interrupteurs K(j). Le circuit logique 901 permet notamment de sélectionner la LED émettrice, de façon similaire à ce qui a été décrit en relation avec la figure 8.

[0082] La polarisation en courant permet de régler individuellement, pour chaque LED, un point de luminance moyen L0, par exemple identique pour toutes les LED. Ceci permet par exemple de compenser d'éventuelles dispersions de fabrication entre les LED. A titre d'exemple, la valeur de réglage appliquée sur la borne BIAS\_DATA est codées sur 5 bits, ce qui donne 32 valeurs possibles d'intensité du courant de polarisation ib. La modulation temporelle commandée via la borne DATA permet de régler les niveaux de gris souhaités pour chaque LED élémentaire du module.

**[0083]** Divers modes de réalisation et variantes ont été décrits. La personne du métier comprendra que certaines caractéristiques de ces divers modes de réalisation et variantes pourraient être combinées, et d'autres variantes apparaîtront à la personne du métier. En particulier, les modes de réalisation décrits ne se limitent pas à l'application susmentionnées à des dispositifs d'affichage multi-vues, mais peuvent être appliqués à tout dispositifs d'affichage comportant des modules élémentaires comportant chacun plusieurs LED.

**[0084]** Par ailleurs, les modes de réalisation décrits ne se limitent au cas particulier décrit ci-dessus dans lequel chaque ensemble de N LED réparties en M groupes G(i) comprend uniquement des LED de même couleur. A titre de variante, chaque ensemble de N LED et/ou chaque groupe G(i) peut comprendre des LED de couleurs différentes.

[0085] Par ailleurs, les modes de réalisation décrits ne se limitent pas aux exemples préférentiels décrits ci-dessus dans lesquels un ensemble de N LED est divisé en M groupes comportant chacun un même nombre L de LED. A titre de variante, différents groupes peuvent contenir des nombres de LED différents, au moins un groupe comportant au moins deux LED. On prévoit alors un circuit de polarisation 103(i) par groupe de LED (soit M circuits de polarisation), de façon similaire à ce qui a été décrit ci-dessus. Les circuits de polarisation 103(i) et leur fonctionnement sont identiques ou similaires à ce qui a été décrit précédemment, à la différence près que, dans les groupes comprenant moins de LED, les LED manquantes ne sont pas adressées. En particulier, le nombre d'interrupteurs K(j) ou K'(j) peut être différent dans les différents circuits de polarisation 103(i).

[0086] Par ailleurs, on a décrit ci-dessus en relation avec la figure 3 un exemple d'un module couleur dans lequel le nombre de LED de chaque couleur est identique. A titre de variante, le nombre de LED peut varier d'une couleur à une

autre. La personne du métier saura adapter le circuit de contrôle 105 en conséquence. Dans l'exemple de la figure 3, on peut par ailleurs prévoir de dupliquer l'un des ensembles de LED, par exemple en vue d'avoir une polarisation plus homogène dans le cas où l'une des couleurs aurait un rendement différent des autres.

[0087] On notera que dans la présente description, on entend par pixel un pixel de l'image que l'on souhaite afficher. Dans le cas où un module élémentaire intègre plusieurs sous-pixels, par exemple N sous-pixels, chaque sous-pixels correspond à un pixel d'une des N images que l'on souhaite restituer (avec N angles de vue différents). Si une image est constituée d'une matrice de X\*Y pixels, alors le i-ème sous-pixel associé à un pixel donné correspond à un pixel de même coordonnée (x,y) dans la i-ième image.

[0088] A titre de variante, un module élémentaire au sens de la présente demande peut intégrer plusieurs pixels d'une même image à afficher. Dans le cas de modules élémentaires comportant chacun un unique pixel, les modules peuvent être espacés les uns des autres sur le substrat de report. La surface de la puce de contrôle de chaque module peut alors être supérieure à la surface de la puce de LED du module. Ceci permet d'économiser la surface de matériau de LED par rapport à la surface de silicium de la puce de contrôle. Dans le cas de modules élémentaires comportant chacun plusieurs pixels, on peut prévoir d'accoler latéralement plusieurs modules élémentaires pour constituer un écran d'affichage de plus grandes dimensions. La puce de contrôle de chaque module aura alors de préférence sensiblement les mêmes dimensions latérales que la puce de LED du module. A titre de variante, la puce de contrôle de chaque module peut avoir une surface inférieure à la surface de la puce de LED, même si cette variante est peu probable étant donné que la surface de la puce de contrôle est généralement contrainte, notamment quand la puce de contrôle comporte une unique couche semiconductrice et non un circuit « 3D ».

**[0089]** En outre, dans la présente description, le terme « puce » a été utilisé pour désigner la présence dans chaque module d'une puce de contrôle et d'une puce de LED. En pratique, chaque puce comprend des composants semiconducteurs formés dans et/ou sur une couche d'un matériau semi-conducteur. Ainsi, la puce de contrôle comprend entre autre des transistors, par exemple de type MOS, comprenant, comme cela est bien connu, des portions formées dans une couche semiconductrice (par exemple du silicium) et des portions (par exemple métalliques, isolantes) formées audessus de la couche semiconductrice, et recouvertes de matériaux diélectriques dans lesquels sont formés des lignes métalliques de connexion entre composants. De même, la puce de LEDs comprend des diodes électroluminescentes formées au moins en partie dans une ou plusieurs couches semiconductrices superposées. La puce de LEDs peut en outre comprendre un ensemble d'autres couches pour former des filtres colorés par exemple, ou des éléments de conversion lumineuse.

[0090] Les puces de contrôle et de LEDs peuvent être fabriquées séparément puis collées l'une à l'autre. Alternativement, l'une des puces peut être construite directement sur l'autre puce selon un procédé de fabrication séquentiel.

[0091] On notera en outre, qu'une puce, notamment la puce de contrôle peut en pratique être constituée de plusieurs « étages » ou autrement dit de plusieurs puces superposées pour former un circuit « 3D ». Le mot anglais de « tier » est souvent utilisé pour désigner les différents étages comprenant chacun une couche semiconductrice avec des composants (transistors, résistances...), également appelé « front-end » en anglais, et une alternance de couches diélectriques et conductrices pour former un réseau d'interconnexion électrique, également appelé « back-end » en anglais.

[0092] Enfin, la mise en oeuvre pratique des modes de réalisation et variantes décrits est à la portée de la personne du métier à partir des indications fonctionnelles données ci-dessus. En particulier, la réalisation des LED élémentaires et des circuits de commande des modules est à la portée de la personne du métier à partir des indications fonctionnelles de la présente description.

#### Revendications

10

15

20

30

35

40

45

50

55

- 1. Dispositif d'affichage comportant un substrat de report et une pluralité de modules élémentaires (100 ; 300) disposés en matrice sur le substrat de report, chaque module formant un assemblage compact d'une ou plusieurs puces électroniques, chaque module comportant une face de connexion comportant des plots de connexion fixés et connectés électriquement à des plots de connexion correspondant du substrat de report, destinés à amener des signaux d'alimentation et de contrôle du module, chaque module permettant d'afficher au moins un pixel d'une image, chaque module comportant :

- un premier ensemble de N LED (101(i,j)) réparties en M groupes (G(i)), au moins l'un des M groupes comportant au moins deux LED, où N et M sont des entiers, avec M supérieurs ou égal à 2 ; et

- un circuit de commande comportant M circuits de polarisation (103(i)) associés respectivement aux M groupes de LED, chaque circuit de polarisation (103(i)) étant partagé par les LED du groupe (G(i)) correspondant et étant adapté à commander successivement en émission les LED du groupe,

dans lequel chaque module comporte au moins un plot (DATA; DATA\_R, DATA\_G, DATA\_B) de connexion,

dit plot de données, destiné à recevoir des signaux de réglage individuels des puissances d'émission des N LED (101(i,j)) du module, multiplexés temporellement,

et dans lequel dans chaque module, chaque circuit de polarisation (103(i)) du module comprend un premier interrupteur de sélection (SW) reliant ledit plot de de données du module à un noeud de réglage de puissance lumineuse (d in) du circuit de polarisation, et comprend un ensemble de seconds interrupteurs de sélection (K(1), ... K(L)) reliant respectivement les LED (101(i,j)) du groupe (G(i)) correspondant à un même noeud de fourniture d'un courant de polarisation (ib) du circuit de polarisation (103(i)), ledit courant de polarisation reçu par une LED sélectionnée étant fonction du signal de réglage transmis sur ledit nœud de réglage de puissance lumineuse (d in).

10

5

2. Dispositif d'affichage selon la revendication 1, dans lequel, dans chaque module (100; 300), chacun des M groupes (G(i)) comprend un même nombre de LED.

15

3. Dispositif d'affichage selon la revendication 1 ou 2, dans leguel, dans chaque module (100 : 300), les circuits de polarisation (103(i)) sont configurés pour que, dans chaque groupe (G(i)), pour chaque LED (101(i,j)) du groupe, une période d'émission (T\_E) de la LED soit concomitante à une période d'émission (T\_E) d'une LED (101(i,j)) correspondante de chaque autre groupe.

20 25

Dispositif d'affichage selon l'une quelconque des revendications 1 à 3, dans lequel, dans chaque module (100;  $300), le\,circuit\,de\,commande\,est\,configur\'e\,pour, lors\,d'une\,p\'eriode\,T\_TRAME, r\'egler\,individuellement\,les\,puissances$ d'émission respectives des N LED (101(i,j)), la période T\_TRAME étant divisée en L périodes successives Tj, avec L entier et j entier allant de 1 à L, chaque période Tj comportant une période d'initialisation T\_INIT suivie d'une période d'émission T\_E, le circuit de commande étant configuré pour, à chaque période Tj, pendant la période d'initialisation T INIT, appliquer successivement aux M circuits de polarisation (103(i)) un signal de réglage individuel de la puissance d'émission souhaitée de la LED de rang j du groupe de LED G(i) correspondant, puis, pendant la période d'émission (T E), commander simultanément en émission les M LED de rang j en fonction desdits signaux de réglage individuels.

30

teurs (SW) des circuits de polarisation sont successivement rendus conducteurs pour transmettre un signal reçu sur ledit plot de données à un nœud de réglage de puissance lumineuse (d\_in) du groupe sélectionné par ledit premier interrupteur (SW) rendu conducteur, les seconds interrupteur (K(1), ... K(L)) étant alors non conducteurs, et dans lequel, dans chaque circuit de polarisation, durant chaque période d'émission T E, un seul interrupteur parmi les seconds interrupteurs (K(1), ... K(L)) est rendu conducteur pour sélectionner une seule LED par groupe et lui appliquer un courant de polarisation fonction du signal de réglage transmis sur ledit nœud de réglage de puissance lumineuse du circuit de polarisation associé.

Dispositif selon la revendication 4, dans lequel, durant chaque période d'initialisation T INIT, les premiers interrup-

35

40

6. Dispositif d'affichage selon l'une quelconque des revendications 1 à 5, dans leguel, dans chaque module (100; 300), chaque circuit de polarisation (103(i)) comprend une source de courant (107) de polarisation réglable en intensité, la puissance d'émission de chacune des LED (101(i,j)) du groupe correspondant étant réglée en faisant varier le courant délivré par ladite source de courant (107).

45

7. Dispositif d'affichage selon l'une quelconque des revendications 1 à 5, dans leguel, dans chaque module (100; 300), chaque circuit de polarisation (103(i)) comprend une source de tension de polarisation fixe, la puissance d'émission de chacune des LED (101(i,j)) du groupe correspondant étant réglée par modulation du temps d'émission de la LED, par exemple selon une modulation à codage binaire.

50

Dispositif d'affichage selon l'une quelconque des revendications 1 à 5, dans lequel, dans chaque module (100; 300), chaque circuit de polarisation (103(i)) comprend une source de courant de polarisation réglable en intensité, la puissance d'émission de chacune des LED (101(i,j)) du groupe correspondant étant réglée en faisant varier le courant délivré par ladite source de courant (107) et par modulation du temps d'émission de la LED, par exemple selon une modulation à codage binaire.

55

9. Dispositif d'affichage selon l'une quelconque des revendications 1 à 8, dans lequel, dans chaque module (100; 300), les N LED du premier ensemble sont d'une même première couleur, le module comportant en outre un deuxième ensemble de N LED (101(i,j)) d'une même deuxième couleur réparties en M groupes (G(i)), au moins l'un des M groupes comportant au moins deux LED, et un troisième ensemble de N LED (101(i,j)) d'une même troisième couleur réparties en M groupes (G(i)), au moins l'un des M groupes comportant au moins deux LED.

- **10.** Dispositif d'affichage selon l'une quelconque des revendications 1 à 12, dans lequel, dans chaque module (100 ; 300), le premier ensemble de LED forme une puce de LED et le circuit de commande est un circuit intégré de type CMOS formant une puce de contrôle accolée à une face de la puce de LED.

- 11. Dispositif d'affichage selon l'une quelconque des revendications 1 à 10, dans lequel chaque module (100 ; 300) est configuré pour afficher un unique pixel de même coordonnée spatiale pour un ensemble de N images de mêmes dimensions, les N LED du module correspondant à N sous-pixels d'un même pixel, chaque sous-pixel permettant d'afficher un pixel d'une des N images correspondant respectivement à N angles de vues d'un dispositif d'affichage multi-vues.

**12.** Dispositif d'affichage selon l'une quelconque des revendications 1 à 11, dans lequel chaque module (100 ; 300) comprend en outre au moins un autre plot de connexion, dit plot de contrôle, permettant la réception de signaux de contrôle utilisés pour générer des signaux de commande interne des premiers et seconds interrupteurs de sélection.

13. Dispositif selon les revendications 9 et 12, dans lequel, les mêmes signaux de commande interne sont utilisés pour commander les interrupteurs des premier, deuxième et troisième ensembles de LEDs, et dans lequel des premier, deuxième et troisième plots de données sont reliés respectivement aux premier, deuxième et troisième ensembles de LEDs pour transférer en parallèle des signaux de réglage d'intensité lumineuse à chacun des trois ensembles de LEDs.

Fig 1

Fig 2

Fig 3

Fig 6

Fig 7

**DOCUMENTS CONSIDERES COMME PERTINENTS**

des parties pertinentes

Citation du document avec indication, en cas de besoin,

Catégorie

# RAPPORT DE RECHERCHE EUROPEENNE

Revendication concernée

Numéro de la demande

EP 22 16 2187

CLASSEMENT DE LA DEMANDE (IPC)

5

15

20

25

30

35

40

45

50

55

|                                                   | des parties pertinentes                                                                                                                                                                                                  |                                                                                                                     | CONCENTICE                                                                                                                                                                                                                                           | DEMANDE (IFC)                            |  |  |  |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--|--|--|

| X<br>A                                            | US 2015/339998 A1 (YEN S<br>AL) 26 novembre 2015 (20<br>* alinéas [0003], [0032<br>[0041] - [0046], [0049]<br>[0061], [0066] - [0068]<br>[0084], [0096], [0100]<br>1,2A-2C,3,4,5,6 *                                     | 15-11-26)<br>], [0038],<br>, [0053] -<br>, [0072] -                                                                 | 1-4,6,7,<br>9,10,12,<br>13<br>5                                                                                                                                                                                                                      | INV.<br>G09G3/00<br>G09G3/20<br>G09G3/32 |  |  |  |

| x                                                 | US 6 317 138 B1 (YANO MO<br>13 novembre 2001 (2001-1<br>* colonne 1, ligne 5 - 1<br>* colonne 4, ligne 14 -<br>* colonne 5, ligne 35 -<br>* colonne 6, ligne 21 -<br>* figures 2A-2C,6,8,11,1<br>* colonne 8, ligne 24 - | 1-13) igne 45 * ligne 48 * ligne 67 * ligne 48 * 2,13,15,16,17 *                                                    | 1-4,6,<br>8-13                                                                                                                                                                                                                                       |                                          |  |  |  |

| x                                                 | US 2018/247586 A1 (VAHID<br>[US] ET AL) 30 août 2018                                                                                                                                                                     |                                                                                                                     | 1-3,6,<br>8-10,12,                                                                                                                                                                                                                                   | DOMAINES TECHNIQUE<br>RECHERCHES (IPC)   |  |  |  |

|                                                   | * alinéas [0002], [0051 [0063] - [0065], [0101] [0107], [0110]; figures                                                                                                                                                  | - [0104],                                                                                                           |                                                                                                                                                                                                                                                      | G09G                                     |  |  |  |

| •                                                 | résent rapport a été établi pour toutes les r                                                                                                                                                                            | evendications ate d'achèvement de la recherche                                                                      | -                                                                                                                                                                                                                                                    | Examinateur                              |  |  |  |

|                                                   | La Haye                                                                                                                                                                                                                  | 26 avril 2022                                                                                                       | Lad                                                                                                                                                                                                                                                  | iray, Olivier                            |  |  |  |

| X : par<br>Y : par<br>auti<br>A : arri<br>O : div | CATEGORIE DES DOCUMENTS CITES  ticulièrement pertinent à lui seul ticulièrement pertinent en combinaison avec un e document de la même catégorie ère-plan technologique ulgation non-écrite tument intercalaire          | T : théorie ou princip<br>E : document de bre<br>date de dépôt ou<br>D : cité dans la dem<br>L : cité pour d'autres | T : théorie ou principe à la base de l'invention E : document de brevet antérieur, mais publié à la date de dépôt ou après cette date D : cité dans la demande L : cité pour d'autres raisons  & : membre de la même famille, document correspondant |                                          |  |  |  |

- X : particulièrement pertinent à lui seul

Y : particulièrement pertinent en combinaison avec un autre document de la même catégorie

A : arrière-plan technologique

O : divulgation non-écrite

P : document intercalaire

- T: théorie ou principe à la base de l'invention E: document de brevet antérieur, mais publié à la date de dépôt ou après cette date D: cité dans la demande L: cité pour d'autres raisons

- & : membre de la même famille, document correspondant

# ANNEXE AU RAPPORT DE RECHERCHE EUROPEENNE RELATIF A LA DEMANDE DE BREVET EUROPEEN NO.

5

10

15

20

25

30

35

40

45

50

55

EP 22 16 2187

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités dans le rapport de recherche européenne visé ci-dessus.

Lesdits members sont contenus au fichier informatique de l'Office européen des brevets à la date du

Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets.

26-04-2022

| Do    | cument brevet cité  |           |                        |        |                                       |    | Date   | e de  |

|-------|---------------------|-----------|------------------------|--------|---------------------------------------|----|--------|-------|

| au ra | apport de recherche |           | Date de<br>publication |        | Membre(s) de la<br>famille de brevet( |    | public |       |

| US    | 2015339998          | A1        | 26-11-2015             | CN     | 104134421                             | Α  | 05-11  | -201  |

|       |                     |           |                        | TW     | 201545323                             |    | 01-12  |       |

|       |                     |           |                        | US     | 2015339998                            |    | 26-11  |       |

|       |                     |           |                        |        |                                       |    |        |       |

| US    | 6317138             | В1        | 13-11-2001             |        | 19990078440                           |    | 25-10  |       |

|       |                     |           |                        | us<br> | 6317138                               |    | 13-11  |       |

|       | 2018247586          | <b>A1</b> | 30-08-2018             | US     | 2018247586                            | A1 | 30-08  | 3-201 |

|       |                     |           |                        | WO     |                                       |    | 30-03  |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

|       |                     |           |                        |        |                                       |    |        |       |

Pour tout renseignement concernant cette annexe : voir Journal Officiel de l'Office européen des brevets, No.12/82

# RÉFÉRENCES CITÉES DANS LA DESCRIPTION

Cette liste de références citées par le demandeur vise uniquement à aider le lecteur et ne fait pas partie du document de brevet européen. Même si le plus grand soin a été accordé à sa conception, des erreurs ou des omissions ne peuvent être exclues et l'OEB décline toute responsabilité à cet égard.

# Documents brevets cités dans la description

- WO 2017089676 A **[0002] [0021]**

- WO 2018185433 A **[0002]**

- WO 2018185434 A **[0002]**

- FR 3076396 A1 **[0076]**