(11)

EP 4 068 376 A1

(12)

## EUROPEAN PATENT APPLICATION

published in accordance with Art. 153(4) EPC

(43) Date of publication:

05.10.2022 Bulletin 2022/40

(21) Application number: 19945451.3

(22) Date of filing: 29.11.2019

(51) International Patent Classification (IPC):

H01L 27/32 (2006.01)

(52) Cooperative Patent Classification (CPC):

H01L 27/32

(86) International application number:

PCT/CN2019/122157

(87) International publication number:

WO 2021/102989 (03.06.2021 Gazette 2021/22)

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB

GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO

PL PT RO RS SE SI SK SM TR

Designated Extension States:

BA ME

Designated Validation States:

KH MA MD TN

(71) Applicants:

- BOE Technology Group Co., Ltd.

Beijing 100015 (CN)

- Hefei Boe Joint Technology Co., Ltd.

Xinzhan District

Hefei

Anhui 230012 (CN)

(72) Inventors:

- YUAN, Can

Beijing 100176 (CN)

• LI, Yongqian

Beijing 100176 (CN)

• LI, Meng

Beijing 100176 (CN)

• YUAN, Zhidong

Beijing 100176 (CN)

• ZHANG, Dacheng

Beijing 100176 (CN)

• LIU, Lang

Beijing 100176 (CN)

(74) Representative: Maiwald Patent- und Rechtsanwaltsgesellschaft mbH

Elisenhof

Elisenstraße 3

80335 München (DE)

## (54) DISPLAY SUBSTRATE AND MANUFACTURING METHOD THEREFOR, AND DISPLAY DEVICE

(57) A display substrate, a manufacturing method thereof and a display device are provided. The display substrate includes a base substrate and sub-pixels on the base substrate. The sub-pixels are arranged in a sub-pixel array in a first direction and a second direction, the first direction intersecting with the second direction. The display substrate further includes data lines extended in the first direction, and the data lines are connected in one-to-one correspondence with the sub-pixels in columns in each row of sub-pixels, so as to provide data signals respectively; the display substrate further includes auxiliary electrode lines extended in the first direction which are configured to be electrically connected with a second electrode of the light emitting element to provide a second power voltage; each of the auxiliary electrode lines is spaced from any one of the plurality of data lines by at least one column of sub-pixels. The display substrate can effectively improve display density and meanwhile optimize the wiring.

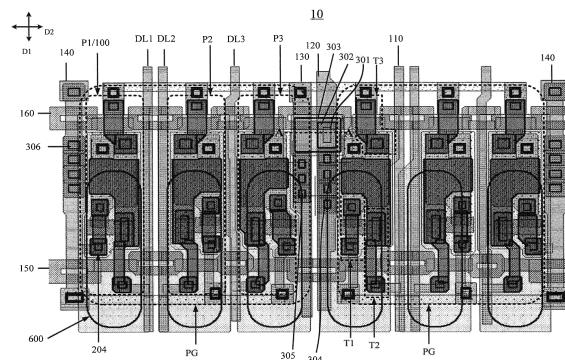

FIG. 2A

## Description

### TECHNICAL FIELD

**[0001]** The present disclosure relates to a display substrate and manufacturing method thereof, and a display device.

### BACKGROUND

**[0002]** In the field of Organic Light Emitting Diode (OLED) display, with the rapid development of high-resolution products, higher requirements are put forward on the structural design of a display substrate, such as the arrangement of pixels and signal lines.

### SUMMARY

**[0003]** At least an embodiment of the present disclosure provides a display substrate, comprising a base substrate, and a plurality of sub-pixels on the base substrate. The plurality of sub-pixels are arranged in a sub-pixel array in a first direction and a second direction, the first direction intersecting with the second direction, and each of the plurality of sub-pixels comprises a first transistor, a second transistor, a third transistor, and a storage capacitor on the base substrate. A first electrode of the second transistor is electrically connected to both a first capacitor electrode of the storage capacitor and a gate electrode of the first transistor, a second electrode of the second transistor is configured to receive a data signal, a gate electrode of the second transistor is configured to receive a first control signal, and the second transistor is configured to write the data signal to the gate electrode of the first transistor and the storage capacitor in response to the first control signal. A first electrode of the first transistor is electrically connected to a second capacitor electrode of the storage capacitor and is configured to be electrically connected to a first electrode of a light emitting element, a second electrode of the first transistor is configured to receive a first power voltage, and the first transistor is configured to control a current for driving the light emitting element under control of a voltage of the gate electrode of the first transistor. A first electrode of the third transistor is electrically connected with both the first electrode of the first transistor and the second capacitor electrode of the storage capacitor, a second electrode of the third transistor is configured to be connected with a detection circuit, a gate electrode of the third transistor is configured to receive a second control signal, and the third transistor is configured to detect an electrical characteristic of the sub-pixel to which the third transistor belongs by the detection circuit in response to the second control signal. The display substrate further comprises a plurality of data lines extended in the first direction, and the plurality of data lines are connected in one-to-one correspondence with the sub-pixels in a plurality of columns in each row of sub-pixels,

so as to provide a plurality of data signals respectively; each row of sub-pixels is divided into a plurality of sub-pixel groups, and each of the plurality of sub-pixel groups comprises a first sub-pixel, a second sub-pixel and a third sub-pixel arranged in the second direction successively; correspondingly, the plurality of data lines are divided into a plurality of data line groups, each data line group comprising a first data line, a second data line, and a third data line connected to the first sub-pixel, the second sub-pixel, and the third sub-pixel respectively; for each of the plurality of sub-pixel groups, the first data line, the second data line and the third data line correspondingly connected to the each sub-pixel group are all between the first sub-pixel and the third sub-pixel; the display substrate further comprises a plurality of auxiliary electrode lines extended in the first direction, and the plurality of auxiliary electrode lines are configured to be electrically connected with a second electrode of the light emitting element to provide a second power voltage; each of the plurality of auxiliary electrode lines is spaced from any one of the plurality of data lines by at least one column of sub-pixels.

**[0004]** In some examples, the display substrate further comprises a plurality of first detection lines; for each row of sub-pixels, in the second direction, an n-th sub-pixel group and an (n+1)th sub-pixel group form a first sub-pixel group unit, so as to define a first sub-pixel group unit array comprising a plurality of first sub-pixel group units, wherein n is an odd number or an even number greater than 0; a column direction of the first sub-pixel group unit array is the first direction, the plurality of first detection lines are correspondingly connected with a plurality of columns of first sub-pixel group units respectively, and the third transistors of the sub-pixels of the first sub-pixel group units in a same column are all electrically connected with one corresponding first detection line; each of the plurality of first detection lines is spaced from any one of the plurality of data lines by at least one column of the sub-pixels.

**[0005]** In some examples, in each of the plurality of first sub-pixel group unit, the third sub-pixel of the n-th sub-pixel group is adjacent to the first sub-pixel of the (n+1)th sub-pixel group, and the first detection line corresponding to the first sub-pixel group unit is between the third sub-pixel of the n-th sub-pixel group and the first sub-pixel of the (n+1)th sub-pixel group.

**[0006]** In some examples, the plurality of auxiliary electrode lines and the plurality of first detection lines are arranged in one-to-one correspondence, and each of the plurality of auxiliary electrode lines is directly adjacent to an adjacent first detection line without a sub-pixel therebetween.

**[0007]** In some examples, the display substrate further comprises a plurality of detection line segments extended in the second direction; the plurality of detection line segments are distributed in a detection line array and are respectively connected with the plurality of first sub-pixel group units in one-to-one correspondence, and the third

transistor of the sub-pixel in each of the plurality of first sub-pixel group units is electrically connected with one corresponding detection line segment.

**[0008]** In some examples, the plurality of first detection lines are electrically connected to a plurality of columns of detection line segments in the detection line array in one-to-one correspondence, and the detection line segments in one column intersect with and are electrically connected with one corresponding first detection line.

**[0009]** In some examples, the display substrate further comprises a plurality of first power lines extended in the first direction; the plurality of first power lines are configured to provide the first power voltage to the plurality of sub-pixels of the sub-pixel array, and the first power line is not overlapped with the detection line segment in a direction perpendicular to the base substrate.

**[0010]** In some examples, each of the plurality of first power lines is spaced from any one of the plurality of data lines by at least one column of the sub-pixels.

**[0011]** In some examples, each of the plurality of first power lines is spaced from any one of the plurality of auxiliary electrode lines by at least one of the plurality of sub-pixel groups.

**[0012]** In some examples, for each row of sub-pixels, in the second direction, an  $(n+1)$ th sub-pixel group and an  $(n+2)$ th sub-pixel group constitute a second sub-pixel group unit, thereby defining a second sub-pixel group unit array comprising a plurality of second sub-pixel group units, a column direction of the second sub-pixel group unit array is the first direction, the plurality of first power lines are correspondingly connected with the plurality of columns of second sub-pixel group units respectively, and the second electrodes of the first transistors of the sub-pixels in the second sub-pixel group units in a same column are electrically connected with one corresponding first power line.

**[0013]** In some examples, in each of the plurality of second sub-pixel groups, the third sub-pixel in the  $(n+1)$ th sub-pixel group is adjacent to the first sub-pixel in the  $(n+2)$ th sub-pixel group, and the first power line corresponding to the second sub-pixel group unit is between the third sub-pixel in the  $(n+1)$ th sub-pixel group and the first sub-pixel in the  $(n+2)$ th sub-pixel group.

**[0014]** In some examples, the display substrate further comprises a plurality of power line segments extended in the second direction; the plurality of power line segments are distributed into a power line array and are respectively connected with the plurality of second sub-pixel group units in one-to-one correspondence, and the first transistor of the sub-pixel in each of the plurality of the second sub-pixel group units is electrically connected with one corresponding power line segment.

**[0015]** In some examples, the power line segment is not overlapped with either of the first detection line and the auxiliary electrode line in the direction perpendicular to the base substrate.

**[0016]** In some examples, the plurality of first power lines are electrically connected to a plurality of columns

of power line segments in the power line array in one-to-one correspondence, and the power line segments in one column intersect with one corresponding first power line and are electrically connected with the one corresponding first power line through a first via hole.

**[0017]** In some examples, for each of the plurality of second sub-pixel group units, the first power line is electrically connected to the second electrodes of the first transistors of both the first sub-pixel and the third sub-pixel adjacent thereto through second via holes.

**[0018]** In some examples, the power line segment is electrically connected to the second electrodes of the first transistors of sub-pixel not adjacent to the first power line through third via holes, thereby electrically connecting the first power line to the second electrodes of the first transistors.

**[0019]** In some examples, the display substrate further comprises a plurality of first scan lines and a plurality of second scan lines extended in the second direction; the plurality of first scan lines are connected to gate electrodes of first transistors in the plurality of rows of sub-pixels respectively, the plurality of second scan lines are connected to gates of third transistors in the plurality of rows of sub-pixels respectively, for each row of sub-pixels, in the first direction, the corresponding first scan line and the corresponding second scan line are located on two sides of the first transistor in each row of sub-pixels respectively.

**[0020]** In some examples, each of the plurality of first scan lines or each of the plurality of second scan lines comprises a first portion and a second portion alternately connected, the second portion having a ring structure; each of the second portions intersects with at least one of the data line, the auxiliary electrode line, the first power line, and the first detection line in the direction perpendicular to the base substrate.

**[0021]** In some examples, a channel region of the third transistor is overlapped with the first portion of the second scan line in the direction perpendicular to the base substrate, and is not overlapped with the second portion of the second scan line in the direction perpendicular to the base substrate.

**[0022]** In some examples, each of the plurality of sub-pixels further comprises the light emitting element, the light emitting element comprising the first electrode, a light emitting layer, and the second electrode, the first electrode, the light emitting layer, and the second electrode being stacked successively; the first electrodes of the light emitting elements in the plurality of sub-pixels are disposed in a same layer and insulated from each other, the second electrodes of the light emitting elements in the plurality of sub-pixels are electrically connected to each other; the display substrate further comprises at least one connection electrode electrically connected with at least one of the plurality of auxiliary electrode lines; the connection electrode and the first electrodes of the light emitting elements in the plurality of sub-pixels are in the same layer and insulated from each

another, and are electrically connected with the second electrodes of the light emitting elements in the plurality of sub-pixels, so that the at least one auxiliary electrode line is electrically connected with the second electrodes of the light emitting elements.

**[0023]** In some examples, the display substrate further comprises a first insulating layer between the at least one auxiliary electrode line and the first electrodes of the light emitting elements, and a pixel defining layer between the second electrodes of the light emitting elements and the at least one connection electrode as well as the first electrodes of the light emitting element; the at least one auxiliary electrode line is electrically connected with the at least one connection electrode through a fourth via hole in the first insulating layer, the at least one connection electrode is electrically connected with the second electrodes of the light emitting elements through a fifth via hole in the pixel defining layer; an orthographic projection of the fifth via hole on the base substrate covers an orthographic projection of the fourth via hole on the base substrate.

**[0024]** In some examples, for at least one of the plurality of sub-pixels, a first capacitor electrode of the storage capacitor, an active layer of the first transistor, an active layer of the second transistor, and an active layer of the third transistor are in a same semiconductor layer, and the first capacitor electrode and the active layer of the second transistor are integrally connected to each other; the second capacitor electrode of the storage capacitor is located in a first conductive layer; the gate electrode of the first transistor, the gate electrode of the second transistor and the gate electrode of the third transistor are arranged in a same layer, insulated from one another, and are in a second conductive layer; the first electrode and the second electrode of the first transistor, the first electrode and the second electrode of the second transistor, the first electrode and the second electrode of the third transistor, the plurality of data lines and the plurality of auxiliary electrode lines are in a same layer and are in a third conductive layer, and the first electrode of the first transistor and the third electrode of the third transistor are integrated with each other; in the first direction, the first transistor and the second transistor are on a same side of the first capacitor electrode, and are on different sides of the first capacitor electrode from the third transistor; the first electrode of the third transistor is electrically connected to the active layer of the third transistor through a sixth via hole and configured to be electrically connected to the light emitting element through a seventh via hole, and the sixth via hole and the seventh via hole are at least partially overlapped in the direction perpendicular to the base substrate; the first electrode of the third transistor is electrically connected with the second capacitor electrode of the storage capacitor through an eighth via hole; in the first direction, the eighth via hole and the sixth via hole are located on a same side of the first capacitor electrode; the first electrode of the second transistor is electrically connected with the gate electrode

of the first transistor and the first capacitor electrode through a ninth through hole.

**[0025]** At least an embodiment of the present disclosure further provides a display device comprising the above display substrate.

**[0026]** At least an embodiment of the present disclosure further provides a method of manufacturing a display substrate, comprising forming a plurality of sub-pixels on a base substrate. The plurality of sub-pixels are arranged in a sub-pixel array in a first direction and a second direction, the first direction intersecting with the second direction, and each of the plurality of sub-pixels comprises a first transistor, a second transistor, a third transistor, and a storage capacitor on the base substrate.

10 A first electrode of the second transistor is electrically connected to a first capacitor electrode of the storage capacitor and a gate electrode of the first transistor, a second electrode of the second transistor is configured to receive a data signal, a gate electrode of the second

15 transistor is configured to receive a first control signal, and the second transistor is configured to write the data signal to the gate electrode of the first transistor and the storage capacitor in response to the first control signal; a first electrode of the first transistor is electrically connected to a second capacitor electrode of the storage capacitor and configured to be electrically connected to a first electrode of a light emitting element, a second electrode of the first transistor is configured to receive a first

20 power voltage, the first transistor is configured to control a current for driving the light emitting element under control of a voltage of the gate electrode of the first transistor; a first electrode of the third transistor is electrically connected with the first electrode of the first transistor and a second capacitor electrode of the storage capacitor, a second electrode of the third transistor is configured to be connected with a detection circuit, a gate electrode of

25 the third transistor is configured to receive a second control signal, and the third transistor is configured to detect an electrical characteristic of the sub-pixel by the detection circuit in response to the second control signal; the manufacturing method further comprises forming a plurality of data lines extended in the first direction, and the plurality of data lines are connected in one-to-one correspondence with the sub-pixels in a plurality of columns

30 a second electrode of the third transistor is configured to be connected with a detection circuit, a gate electrode of the third transistor is configured to receive a second control signal, and the third transistor is configured to detect an electrical characteristic of the sub-pixel by the detection circuit in response to the second control signal; the manufacturing method further comprises forming a plurality of data lines extended in the first direction, and the plurality of data lines are connected in one-to-one correspondence with the sub-pixels in a plurality of columns

35 a second electrode of the third transistor is configured to be connected with a detection circuit, a gate electrode of the third transistor is configured to receive a second control signal, and the third transistor is configured to detect an electrical characteristic of the sub-pixel by the detection circuit in response to the second control signal; the manufacturing method further comprises forming a plurality of data lines extended in the first direction, and the plurality of data lines are connected in one-to-one correspondence with the sub-pixels in a plurality of columns

40 a second electrode of the third transistor is configured to be connected with a detection circuit, a gate electrode of the third transistor is configured to receive a second control signal, and the third transistor is configured to detect an electrical characteristic of the sub-pixel by the detection circuit in response to the second control signal; the manufacturing method further comprises forming a plurality of data lines extended in the first direction, and the plurality of data lines are connected in one-to-one correspondence with the sub-pixels in a plurality of columns

45 a second electrode of the third transistor is configured to be connected with a detection circuit, a gate electrode of the third transistor is configured to receive a second control signal, and the third transistor is configured to detect an electrical characteristic of the sub-pixel by the detection circuit in response to the second control signal; the manufacturing method further comprises forming a plurality of data lines extended in the first direction, and the plurality of data lines are connected in one-to-one correspondence with the sub-pixels in a plurality of columns

50 a second electrode of the third transistor is configured to be connected with a detection circuit, a gate electrode of the third transistor is configured to receive a second control signal, and the third transistor is configured to detect an electrical characteristic of the sub-pixel by the detection circuit in response to the second control signal; the manufacturing method further comprises forming a plurality of data lines extended in the first direction, and the plurality of data lines are connected in one-to-one correspondence with the sub-pixels in a plurality of columns

55 a second electrode of the third transistor is configured to be connected with a detection circuit, a gate electrode of the third transistor is configured to receive a second control signal, and the third transistor is configured to detect an electrical characteristic of the sub-pixel by the detection circuit in response to the second control signal; the manufacturing method further comprises forming a plurality of data lines extended in the first direction, and the plurality of data lines are connected in one-to-one correspondence with the sub-pixels in a plurality of columns

pixel; the manufacturing method further comprises forming a plurality of auxiliary electrode lines extended in the first direction, and the plurality of auxiliary electrode lines are configured to be electrically connected with a second electrodes of the light emitting element to provide a second power voltage; each of the plurality of auxiliary electrode lines is spaced from any one of the data lines by at least one column of sub-pixels.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0027]** In order to clearly illustrate the technical solution of the embodiments of the present disclosure, the drawings of the embodiments will be briefly described. It is apparent that the described drawings are only related to some embodiments of the present disclosure and thus are not limitative of the present disclosure.

Fig. 1A is a first schematic diagram of a display substrate according to at least one embodiment of the present disclosure;

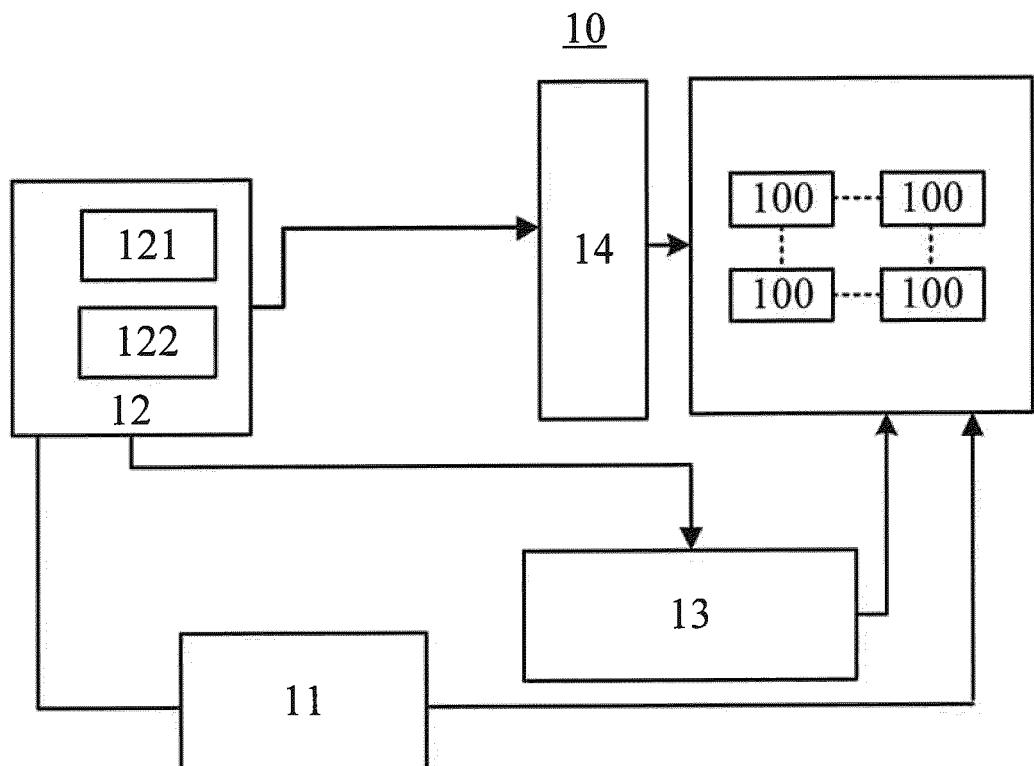

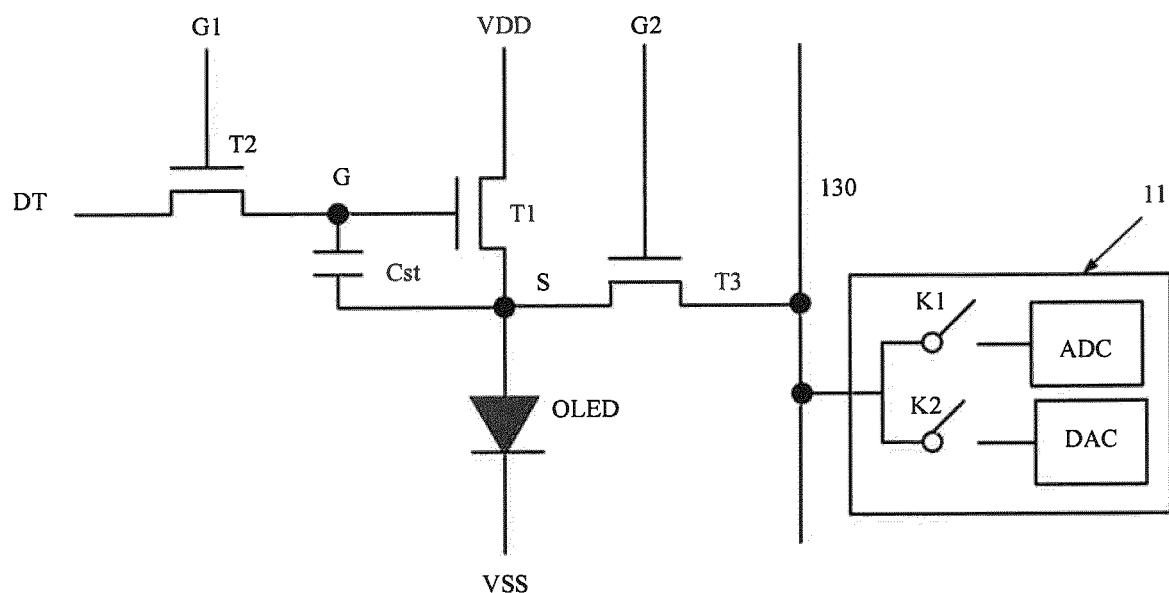

Fig. 1B is a first diagram of a pixel circuit in the display substrate according to at least one embodiment of the present disclosure;

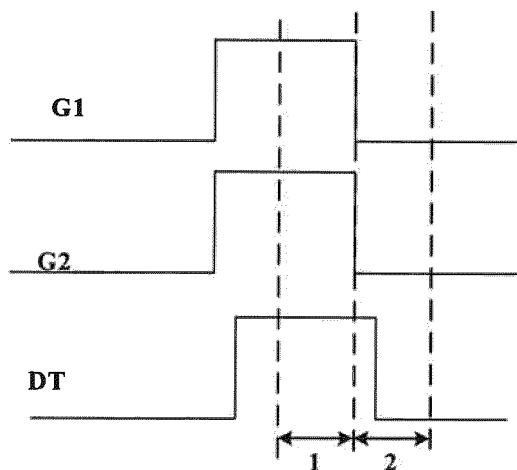

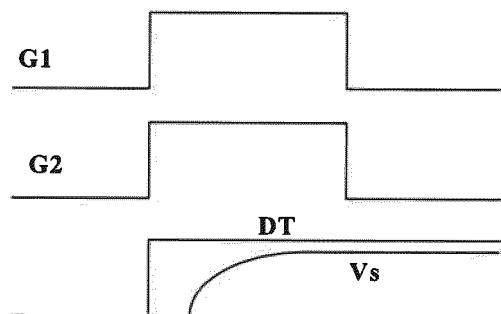

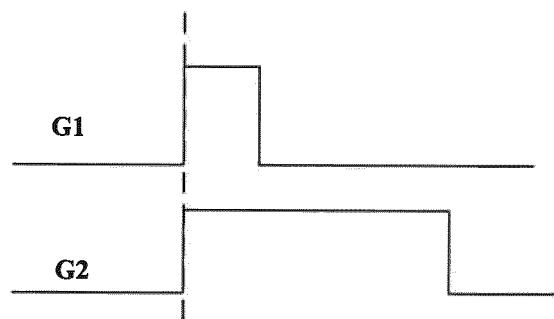

Figs. 1C to 1E are signal timing diagrams of a driving method of a pixel circuit according to embodiments of the present disclosure;

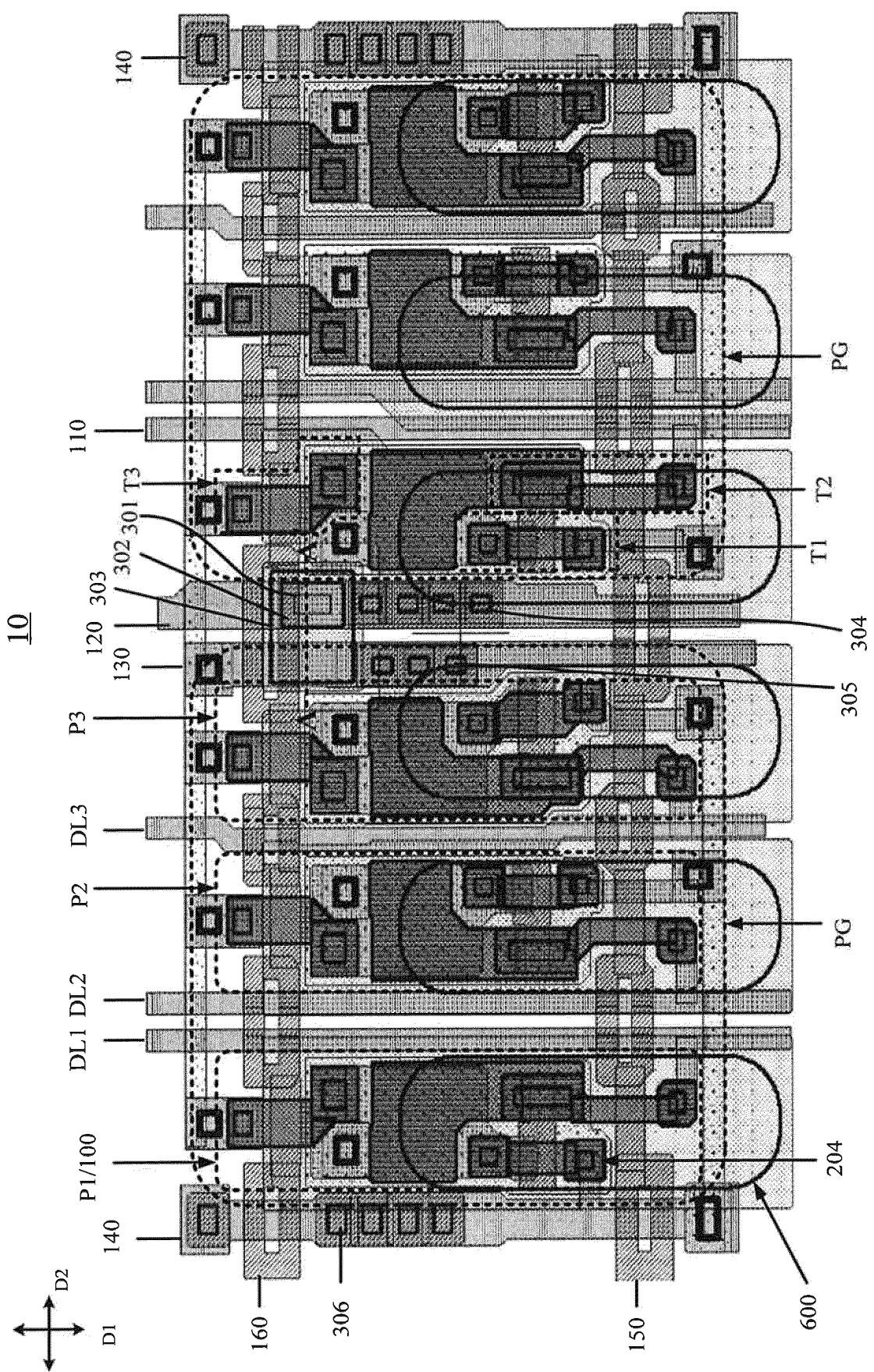

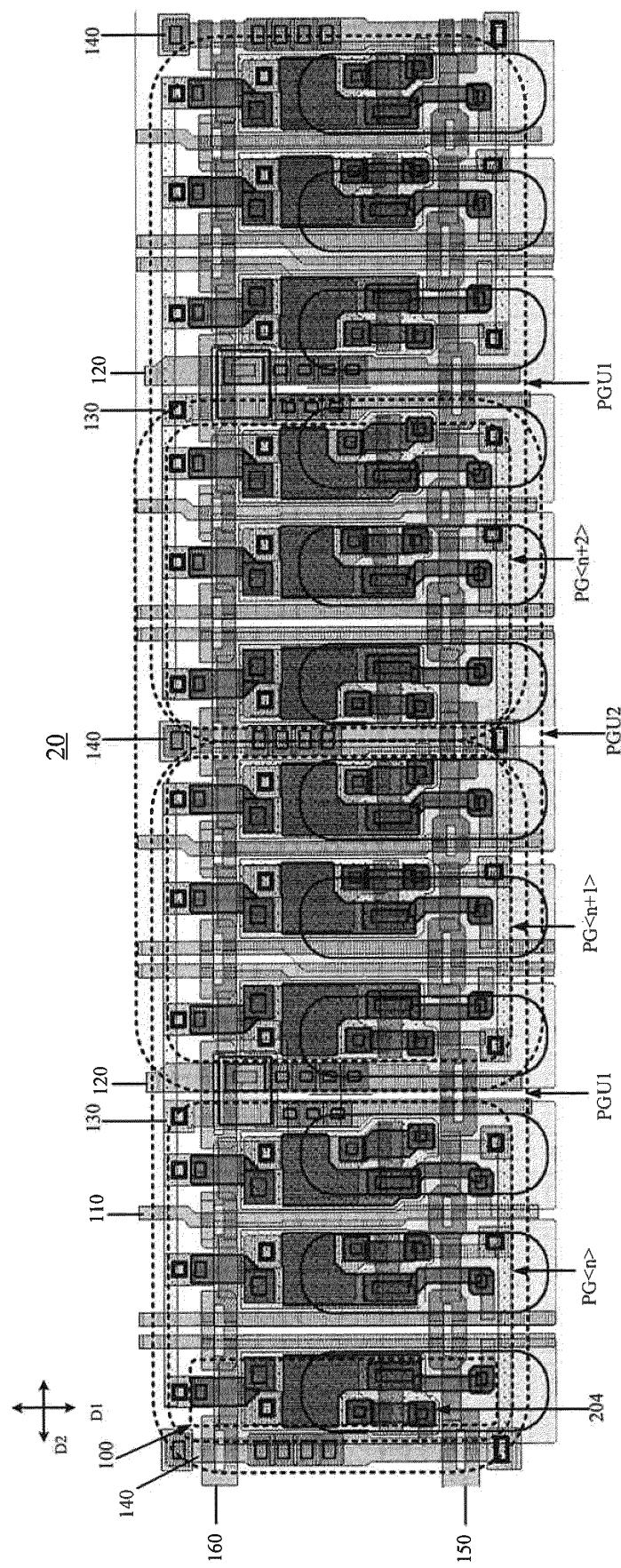

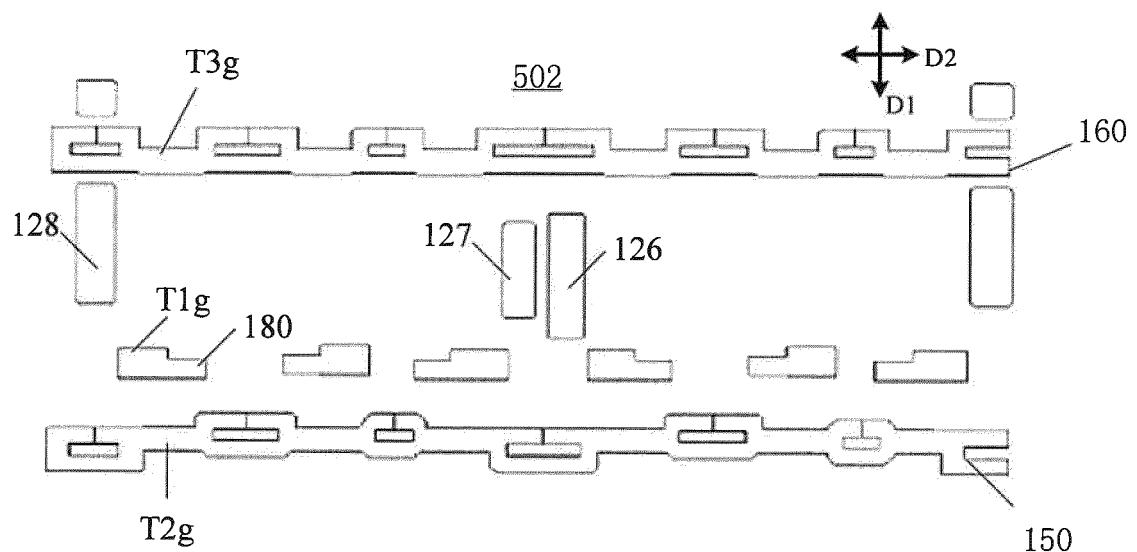

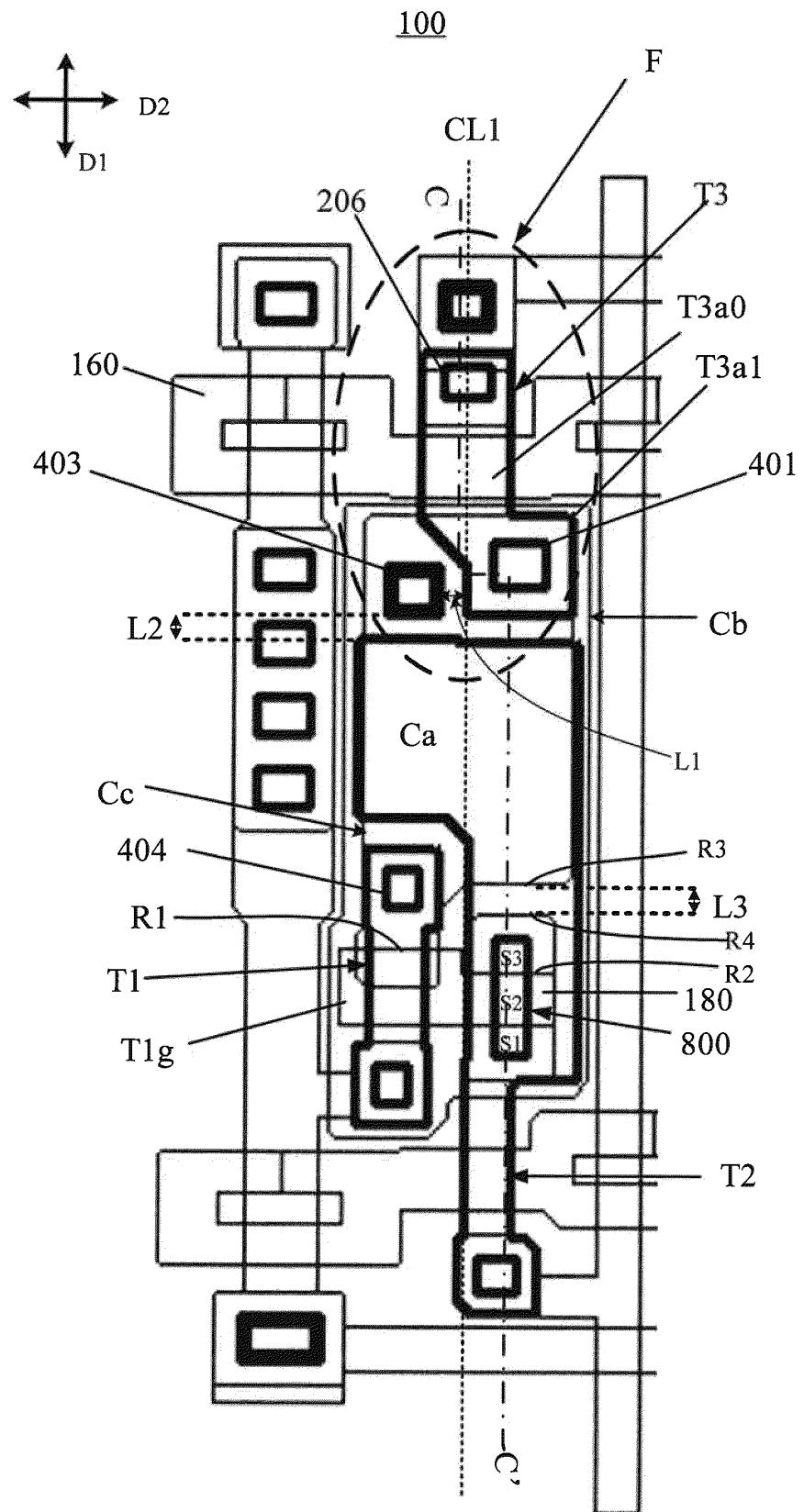

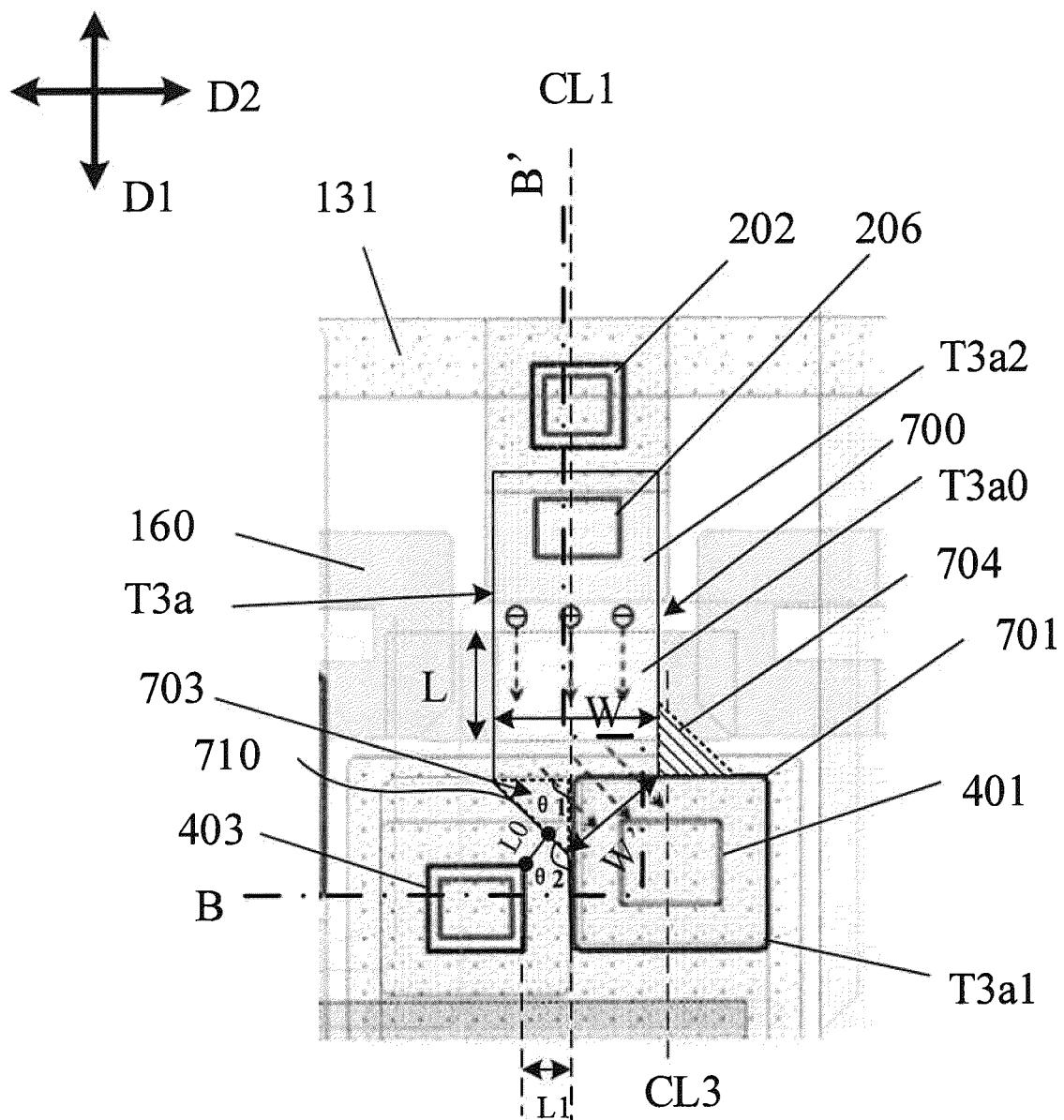

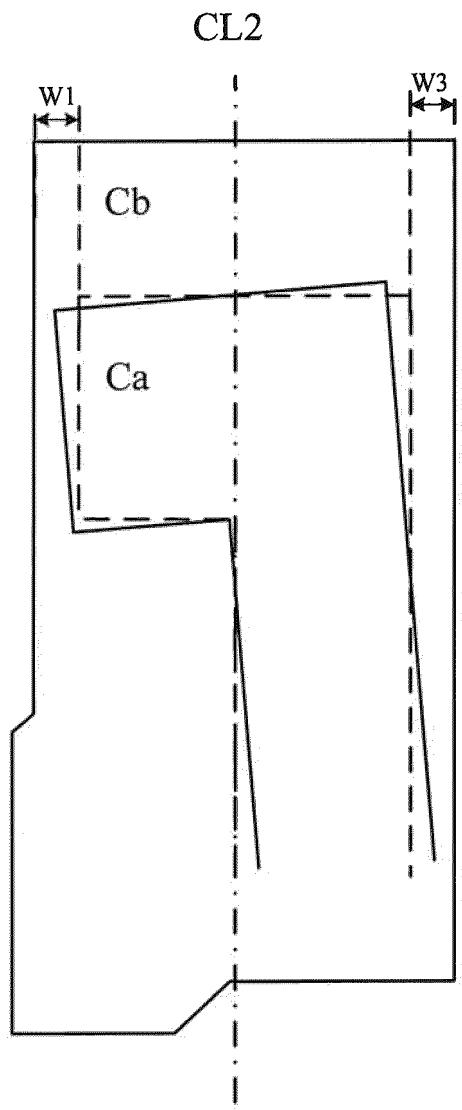

Fig. 2A is a second schematic diagram of a display substrate according to at least one embodiment of the present disclosure;

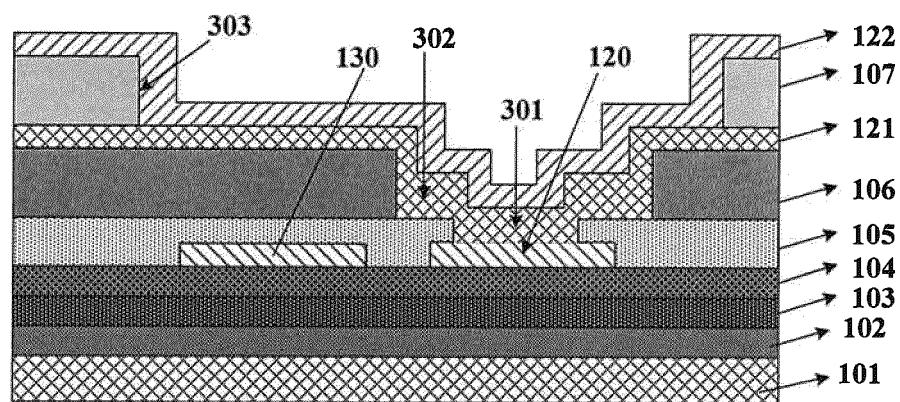

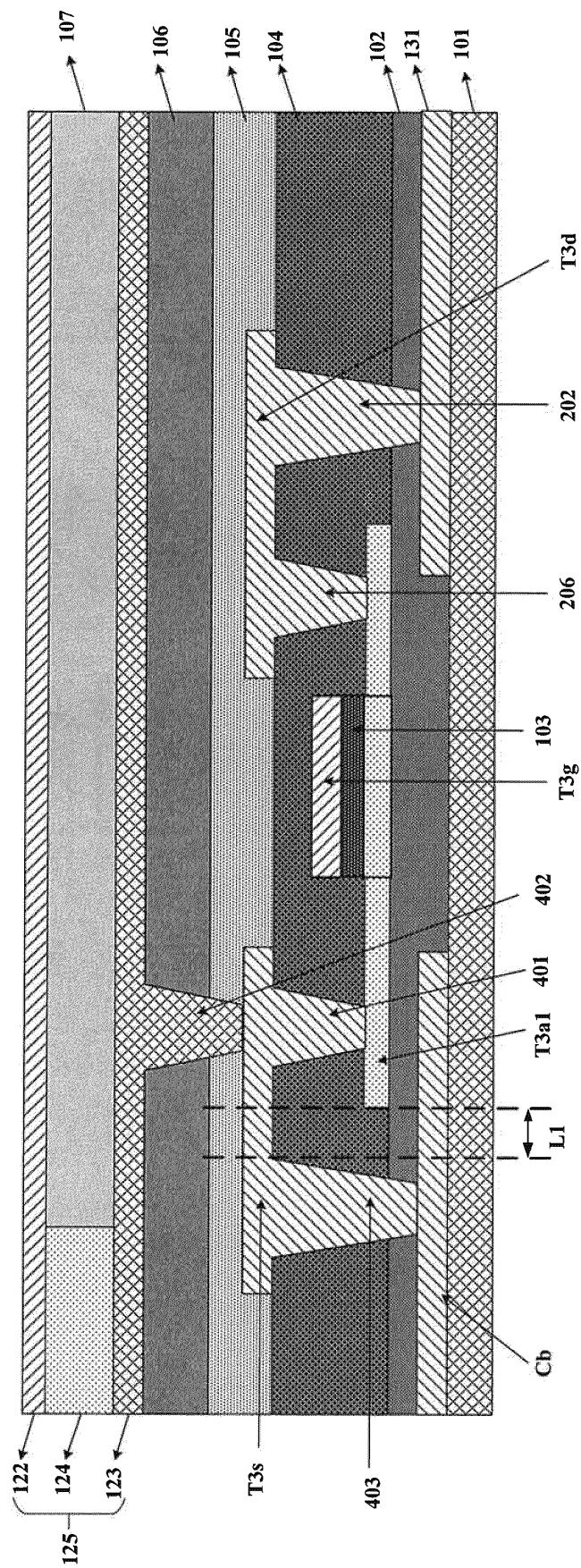

FIG. 2B is a sectional view of FIG. 2A along section line A-A';

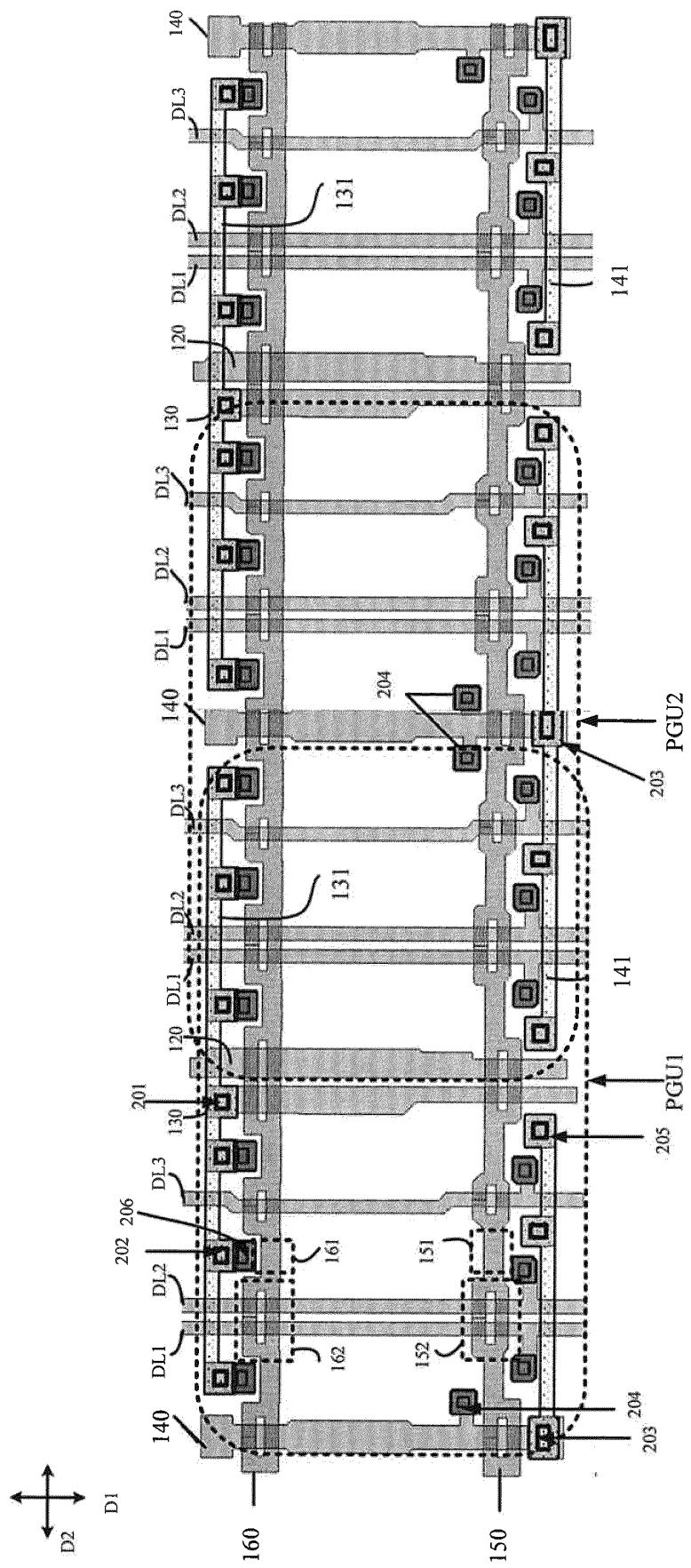

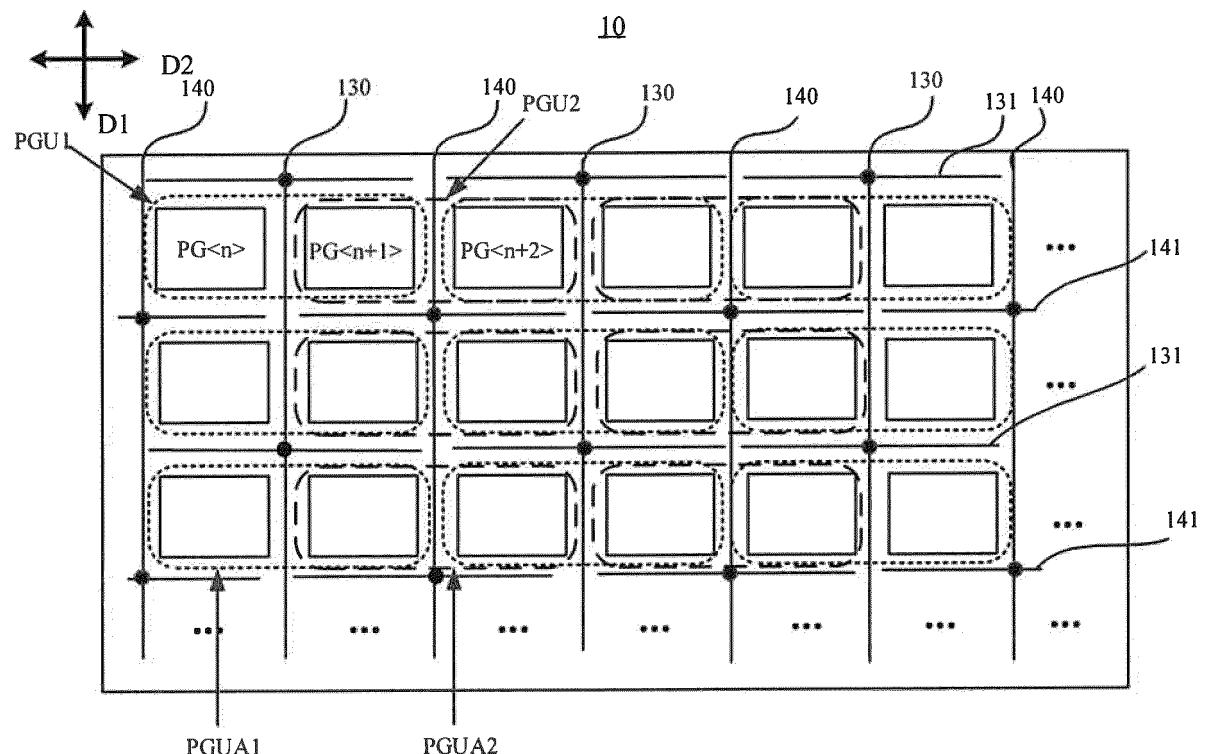

Fig. 3 is a third schematic diagram of a display substrate according to at least one embodiment of the present disclosure;

Fig. 4 is a fourth schematic diagram of a display substrate according to at least one embodiment of the present disclosure;

Fig. 5 is a fifth schematic diagram of a display substrate according to at least one embodiment of the present disclosure;

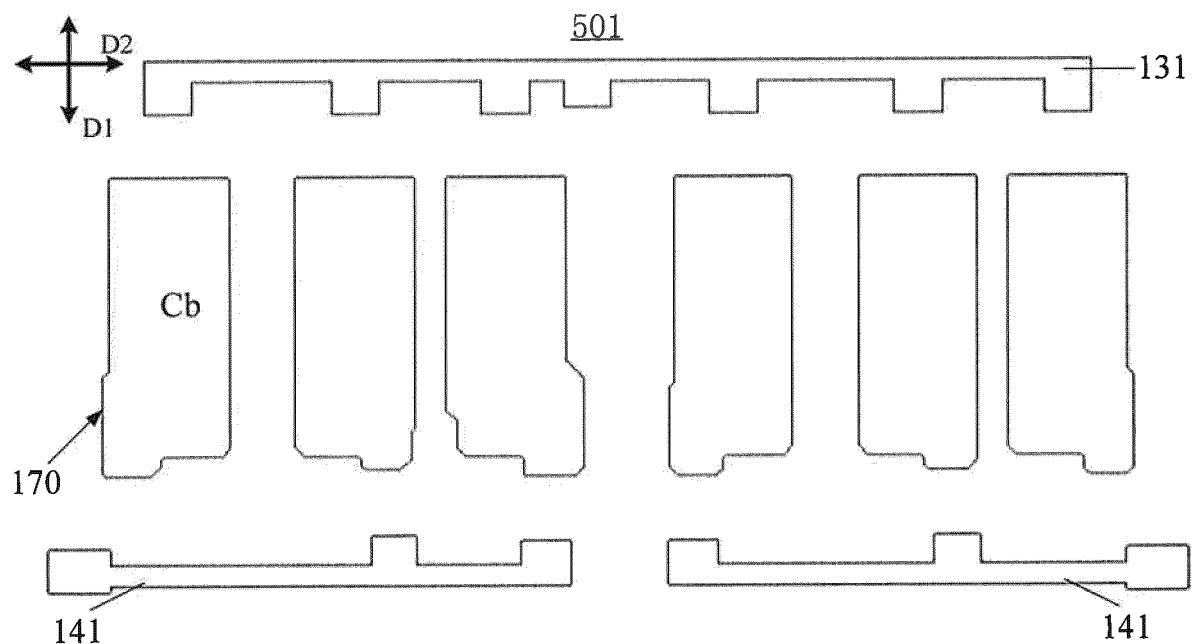

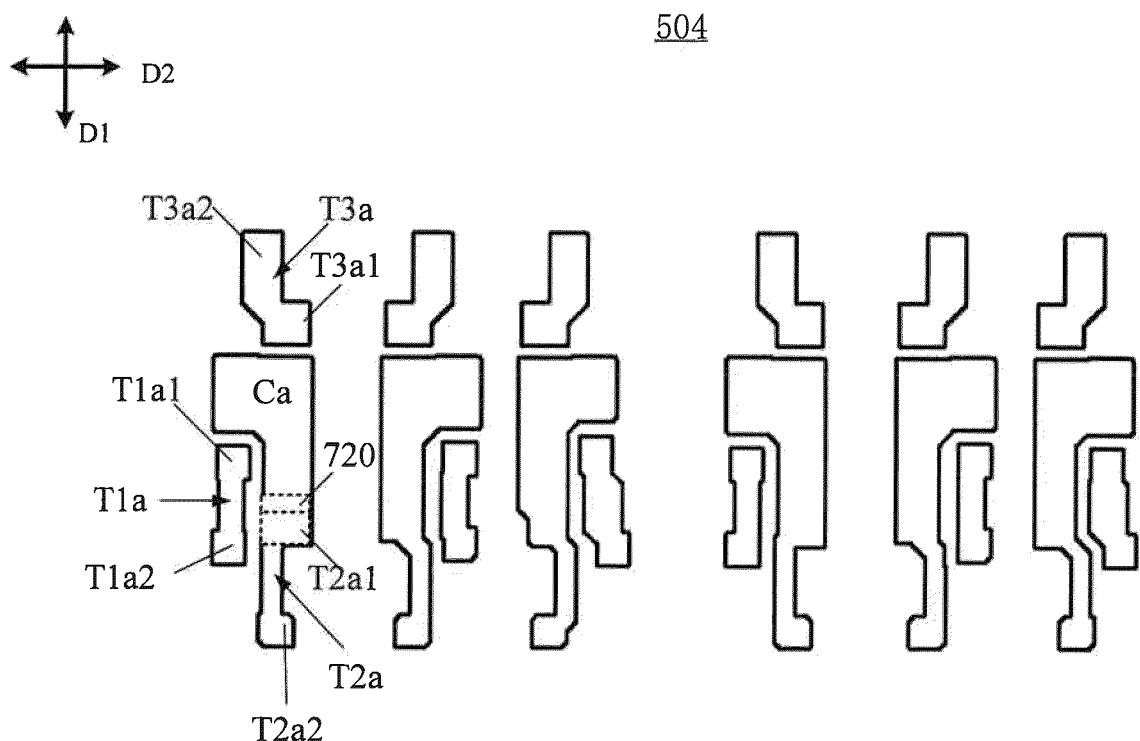

Fig. 6A is a schematic plan view of a first conductive layer in a display substrate according to at least one embodiment of the present disclosure;

Fig. 6B is a schematic plan view of a semiconductor layer in a display substrate according to at least one embodiment of the present disclosure;

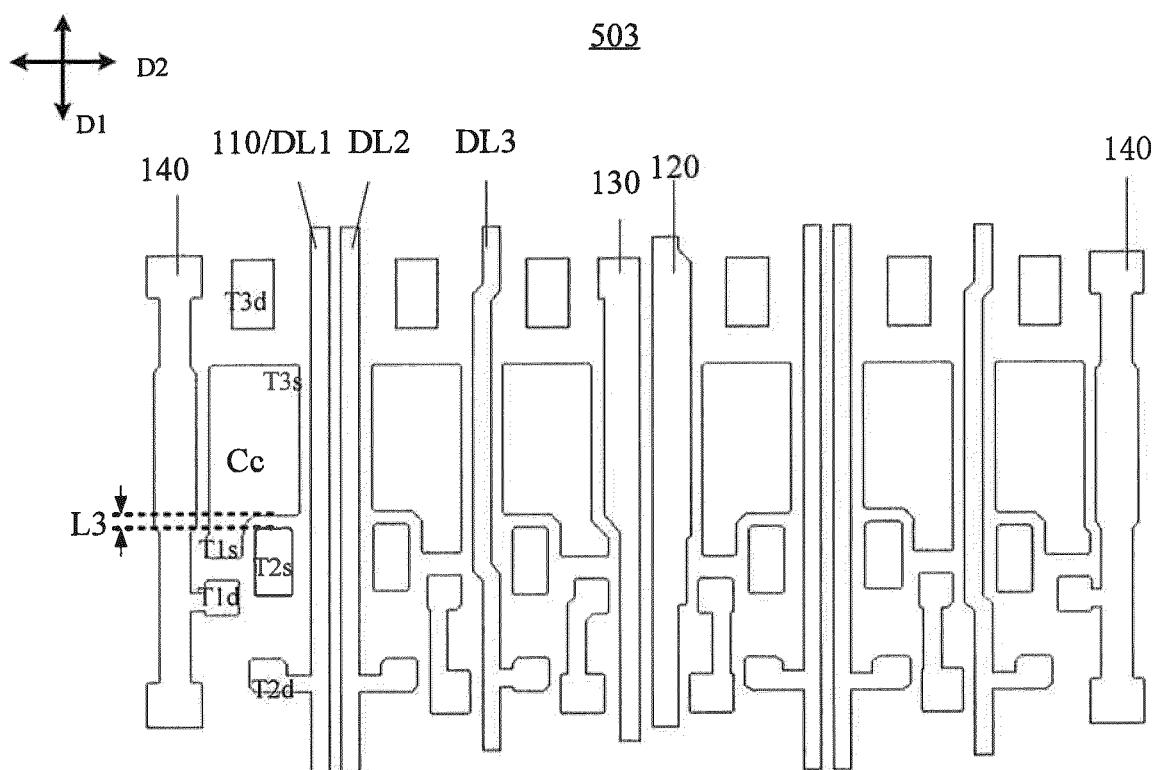

Fig. 6C is a schematic plan view of a second conductive layer in a display substrate according to at least one embodiment of the present disclosure;

Fig. 6D is a schematic plan view of a third conductive layer in a display substrate according to at least one embodiment of the present disclosure;

Fig. 7 is a sixth schematic diagram of a display substrate according to at least one embodiment of the present disclosure;

Fig. 8A is a partially enlarged view of Fig. 7;

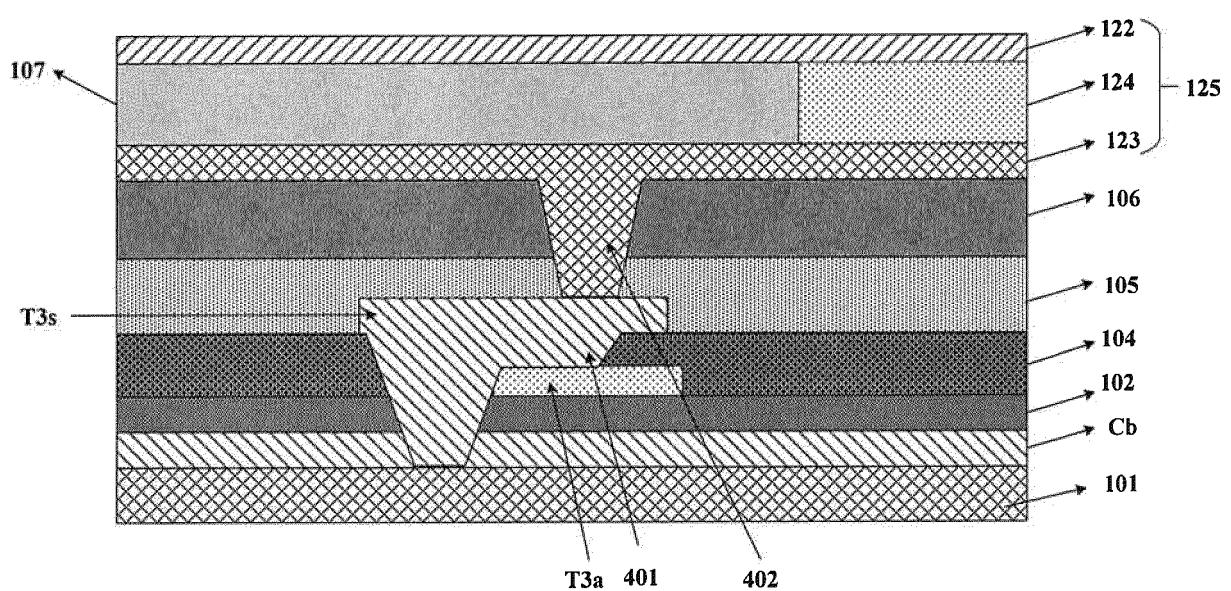

Fig. 8B is a sectional view of Fig. 8A along section

line B-B';

Fig. 8C is a sectional view of a display substrate according to another embodiment of the present disclosure;

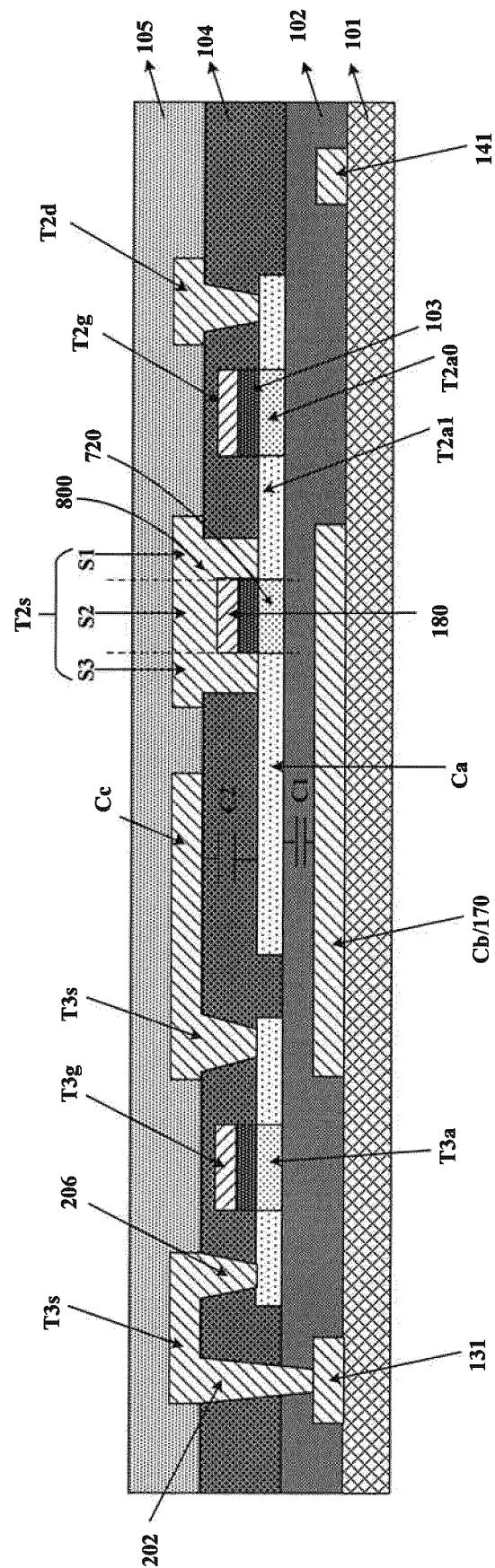

Fig. 9A is a sectional view of Fig. 7 along section line C-C';

Fig. 9B is a second diagram of a pixel circuit in a display substrate according to at least one embodiment of the present disclosure;

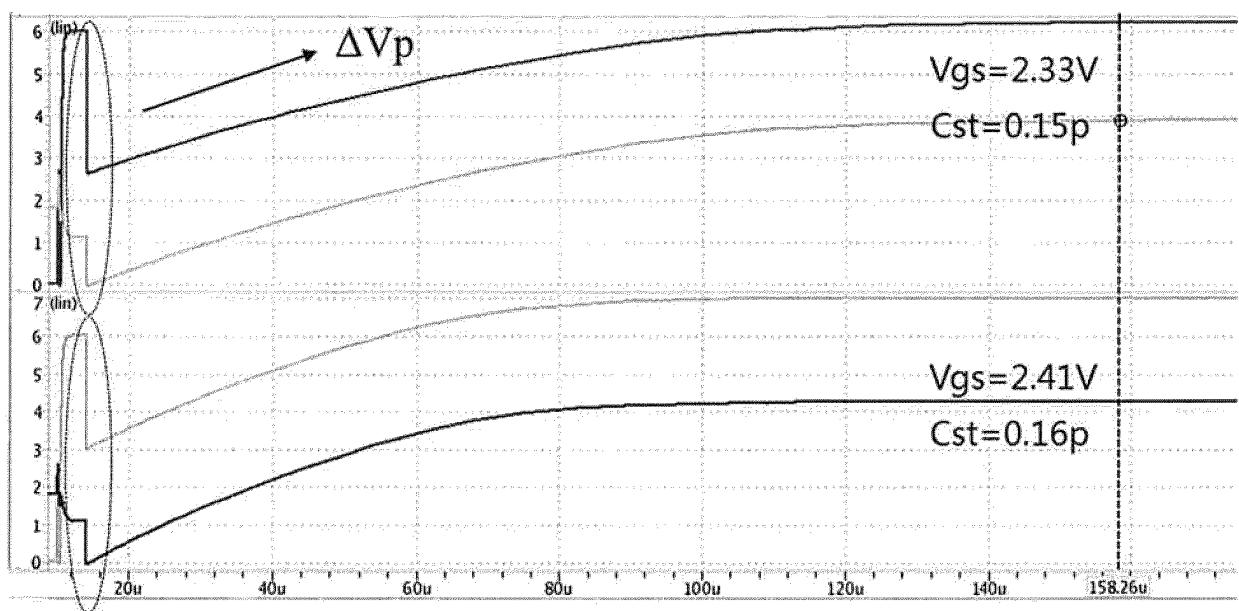

Fig. 10 illustrates the influence of fluctuation of a storage capacitor on a display gray scale;

Fig. 11A is a seventh schematic diagram of a display substrate according to at least one embodiment of the present disclosure;

Fig. 11B is a sectional view of Fig. 11A along section line D-D';

Fig. 11C illustrates misalignment of a first capacitor electrode;

Fig. 12 is a schematic diagram of a display panel according to at least one embodiment of the present disclosure; and

Fig. 13 is a schematic diagram of a display device according to at least one embodiment of the present disclosure.

#### DETAILED DESCRIPTION

**[0028]** In order to make objects, technical details and advantages of embodiments of the present disclosure clear, the technical solutions of the embodiments will be described in a clearly and fully understandable way in connection with the related drawings. It is apparent that the described embodiments are just a part but not all of the embodiments of the present disclosure. Based on the described embodiments herein, those skilled in the art can obtain, without any inventive work, other embodiment(s) which should be within the scope of the present disclosure.

**[0029]** Unless otherwise defined, all the technical and scientific terms used herein have the same meanings as commonly understood by one of ordinary skill in the art to which the present disclosure belongs. The terms "first," "second," etc., which are used in the description and claims of the present disclosure, are not intended to indicate any sequence, amount or importance, but distinguish various components. The terms "comprises," "comprising," "includes," "including," etc., are intended to specify that the elements or the objects stated before these terms encompass the elements or the objects listed after these terms as well as equivalents thereof, but do not exclude other elements or objects. The phrases "connect", "connected", etc., are not intended to define a physical connection or a mechanical connection, but may comprise an electrical connection which is direct or indirect. The terms "on," "under," "right," "left" and the like are only used to indicate relative position relationship, and in a case that the position of an object is described as being changed, the relative position relationship may

be changed accordingly.

**[0030]** In the field of Organic Light Emitting Diode (OLED) display, with the rapid development of high-resolution products, higher requirements are put forward on the structural design of a display substrate, such as the arrangement of pixels and signal lines. For example, compared with an OLED display device with a resolution of 4K, due to its doubled sub-pixel units, the OLED display device with a large size and a resolution of 8K has a doubled pixel density, a decreased line width of a signal line, and an increased resistance-capacitance load and a self-resistance caused by parasitic resistance and parasitic capacitance of the signal line. Correspondingly, signal delay (RC delay), voltage drop (IR drop), voltage rise (IR rise), or the like caused by the parasitic resistance and the parasitic capacitance may become serious. These phenomena may seriously affect display quality of a display product. For example, the resistance of a power line becomes larger, so that the voltage drop on a high power voltage (VDD) line becomes larger, and the voltage rise on a low power voltage (VSS) line becomes larger, which may lead to different power voltages received by the sub-pixels at different positions, thereby causing problems, such as color shift and non-uniform display.

**[0031]** By connecting an auxiliary electrode line with the power line in parallel, the display substrate according to at least one embodiment of the present disclosure reduces the resistance of the power line, thereby effectively relieving the voltage drop or voltage rise on the power line and improving the display quality; meanwhile, by designing the arrangement of the auxiliary electrode line, the display substrate may reduce the problems of color shift, non-uniform display, or the like caused by the resistance-capacitance load between signal lines as much as possible.

**[0032]** Fig. 1A is a block diagram of a display substrate according to at least one embodiment of the present disclosure. As shown in Fig. 1A, the display substrate 10 includes a plurality of sub-pixels 100 arranged in an array, for example, each sub-pixel 100 includes a light emitting element and a pixel circuit for driving the light emitting element to emit light. For example, the display substrate is an organic light emitting diode (OLED) display substrate and the light emitting element is an OLED. The display substrate may further include a plurality of scan lines, and a plurality of data lines for providing scan signals (control signals) and data signals for the plurality of sub-pixels to drive the plurality of sub-pixels. The display substrate may further include a power line, a detection line, or the like, as necessary.

**[0033]** The pixel circuit includes a drive sub-circuit for driving the light emitting element to emit light and a detection sub-circuit for detecting an electrical characteristic of the sub-pixel to achieve external compensation. The specific structure of the pixel circuit is not limited in the embodiments of the present disclosure.

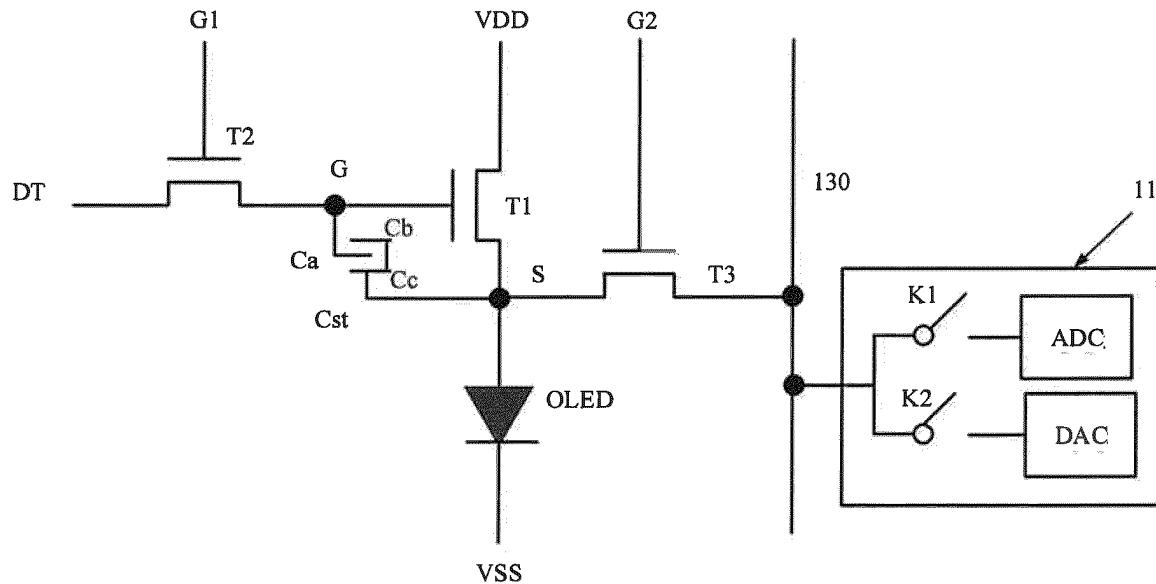

**[0034]** FIG. 1B shows a schematic diagram of a 3T1C

pixel circuit for the display substrate. The pixel circuit may further include a compensation circuit, a reset circuit, or the like as needed, which is not limited in the embodiments of the present disclosure.

**[0035]** Referring to Figs. 1B and 1C, the pixel circuit includes a first transistor T1, a second transistor T2, a third transistor T3, and a storage capacitor Cst. A first electrode of the second transistor T2 is electrically connected to a first capacitor electrode of the storage capacitor Cst and a gate electrode of the first transistor T1, a second electrode of the second transistor T2 is configured to receive a data signal GT, and the second transistor T2 is configured to write the data signal DT to the gate electrode of the first transistor T1 and the storage capacitor Cst in response to a first control signal G1; a first electrode of the first transistor T1 is electrically connected to a second capacitor electrode of the storage capacitor Cst and is configured to be electrically connected to a first electrode of the light emitting element, a second electrode of the first transistor T1 is configured to receive a first power voltage V1 (e.g., a high power voltage VDD), and the first transistor T1 is configured to control a current for driving the light emitting element under the control of a voltage of the gate electrode of the first transistor T1; a first electrode of the third transistor T3 is electrically connected to both the first electrode of the first transistor T1 and the second capacitor electrode of the storage capacitor Cst, a second electrode of the third transistor T3 is configured to be connected to a first detection line 130 so as to be connected to an external detection circuit 11, and the third transistor T3 is configured to detect an electrical characteristic of the sub-pixel the third transistor T3 belongs to in response to the second control signal G2 to achieve external compensation; the electrical characteristic includes, for example, a threshold voltage and/or carrier mobility of the first transistor T1, or a threshold voltage and a drive current of the light emitting element, or the like. The external detection circuit 11 is, for example, a conventional circuit including a digital-to-analog converter (DAC) and an analog-to-digital converter (ADC), which are not repeated in detail in the embodiment of the present disclosure.

**[0036]** The transistors used in the embodiments of the present disclosure may be thin film transistors, field effect transistors, or other switching devices with the same characteristics, and the thin film transistor is taken as an example in the embodiments of the present disclosure for illustration. The source and drain of the transistor used herein may be symmetrical in structure, so that there may be no difference in structure between the source and drain. In the embodiments of the present disclosure, in order to distinguish two electrodes of the transistor except for a gate transistor, one of the electrodes is directly described as a first electrode, and the other electrode is directly described as a second electrode. Further, the transistor may be classified into N-type and P-type transistor according to their characteristics. When the transistor is a P-type transistor, a turn-on voltage is a low

level voltage (e.g., 0V, -5V, -10V or other suitable voltages), and a turn-off voltage is a high level voltage (e.g., 5V, 10V or other suitable voltages); when the transistor is an N-type transistor, the turn-on voltage is a high level voltage (e.g., 5V, 10V, or other suitable voltages) and the turn-off voltage is a low level voltage (e.g., 0V, -5V, -10V, or other suitable voltages). It should be noted that, in the following description, the transistor in Fig. 1B is an N-type transistor as an example, which should not be construed as a limitation to the present disclosure.

**[0037]** The operating principle of the pixel circuit shown in Fig. 1B will be described with reference to the signal timing diagrams shown in Figs. 1C to 1E, wherein Fig. 1B shows the signal timing diagram of the pixel circuit during display, and Figs. 1C and 1D show the signal timing diagram of the pixel circuit during detection.

**[0038]** For example, as shown in Fig. 1B, the display process of each frame image includes a data writing and resetting phase 1 and a light emitting phase 2. Fig. 1B shows a timing waveform of each signal in each phase. One operation process of the 3T1C pixel circuit includes: in the data writing and resetting phase 1, the first control signal G1 and the second control signal G2 are both turn-on signals, the second transistor T2 and the third transistor T3 are turned on, the data signal DT is transmitted to the gate electrode of the first transistor T1 through the second transistor T2, the first switch K1 is turned off, the analog-to-digital converter writes a reset signal to the first electrode of the light emitting element (e.g., an anode of the OLED) through the first detection line 130 and the third transistor T3, the first transistor T1 is turned on and generates a drive current to charge the first electrode of the light emitting element to an operating voltage; in the light emitting period 2, the first control signal G1 and the second control signal G2 are both turn-off signals, the voltage across the storage capacitor Cst remains unchanged due to a bootstrap effect of the storage capacitor Cst, the first transistor T1 operates in a saturation state with an unchanged current, and drives the light emitting element to emit light.

**[0039]** For example, Fig. 1C shows a signal timing diagram when the pixel circuit detects a threshold voltage. One operation process of the 3T1C pixel circuit includes: the first control signal G1 and the second control signal G2 are both turn-on signals, the second transistor T2 and the third transistor T3 are turned on, and the data signal DT is transmitted to the gate electrode of the first transistor T1 through the second transistor T2; the first switch K1 is turned off, the analog-to-digital converter writes a reset signal to the first electrode (node S) of the light emitting element through the first detection line 130 and the third transistor T3, the first transistor T1 is turned on to charge the node S until the first transistor is turned off, and the digital-to-analog converter samples the voltage on the first detection line 130 to obtain the threshold voltage of the first transistor T1. This process may be performed, for example, when the display device is turned off.

**[0040]** For example, Fig. 1C shows a signal timing diagram when the pixel circuit detects the mobility. One operation process of the 3T1C pixel circuit includes: in the first phase, the first control signal G1 and the second control signal G2 are both turn-on signals, the second transistor T2 and the third transistor T3 are turned on, and the data signal DT is transmitted to the gate electrode of the first transistor T1 through the second transistor T2; the first switch K1 is turned off, and the analog-to-digital converter writes a reset signal to the first electrode (node S) of the light emitting element through the first detection line 130 and the third transistor T3; in the second phase, the first control signal G1 is a turn-off signal, the second control signal G2 is a turn-on signal, the second transistor T2 is turned off, the third transistor T3 is turned on, and the first switch K1 and the second switch K2 are turned off to float the first detection line 130; due to the bootstrap effect of the storage capacitor Cst, the voltage across the storage capacitor Cst remains unchanged, the first transistor T1 operates in a saturation state with an unchanged current and drives the light emitting element to emit light, and then the digital-to-analog converter samples the voltage on the first detection line 130 and calculates the carrier mobility in the first transistor T1 according to a magnitude of the light emitting current. For example, the process may be performed in a blanking phase between display phases.

**[0041]** The electrical characteristics of the first transistor T1 may be obtained and a corresponding compensation algorithm may be implemented by the above-mentioned detection.

**[0042]** For example, as shown in Fig. 1A, the display substrate 10 may further include a data drive circuit 13 and a scan drive circuit 14. The data drive circuit 13 is configured to send out data signals, such as the above-mentioned data signal DT, as needed (for example, for inputting an image signal to the display device); the pixel circuit of each sub-pixel is further configured to receive the data signal and apply the data signal to the gate electrode of the first transistor. The scan drive circuit 14 is configured to output various scan signals, including, for example, the above-mentioned first control signal G1 and second control signal G2, which are, for example, integrated circuit chips (ICs) or gate drive circuits directly prepared on the display substrate (GOAs).

**[0043]** For example, the display substrate 10 further includes a control circuit 12. For example, the control circuit 12 is configured to control the data drive circuit 13 to apply the data signal, and to control the gate drive circuit to apply the scan signal. An example of the control circuit 12 is a timing control circuit (T-con). The control circuit 12 may be in various forms, for example including a processor 121 and a memory 122, the memory 121 including an executable code which the processor 121 runs to perform the above-mentioned detection method.

**[0044]** For example, the processor 121 may be a Central Processing Unit (CPU) or other forms of processing devices having data processing capabilities and/or in-

struction execution capabilities, and may include, for example, a microprocessor, a programmable logic controller (PLC), or the like.

**[0045]** For example, the memory 122 may include one or more computer program products which may include various forms of computer-readable storage media, such as volatile memory and/or non-volatile memory. The volatile memory may include, for example, random access memory (RAM), and/or cache memory (cache), or the like. The non-volatile memory may include, for example, read only memory (ROM), hard disk, flash memory, etc. One or more computer program instructions may be stored on the computer-readable storage medium, and the processor 121 may execute the desired functions of the program instructions. Various applications and various data, such as electrical characteristic parameters acquired in the above-mentioned detection method, etc., may also be stored in the computer-readable storage medium.

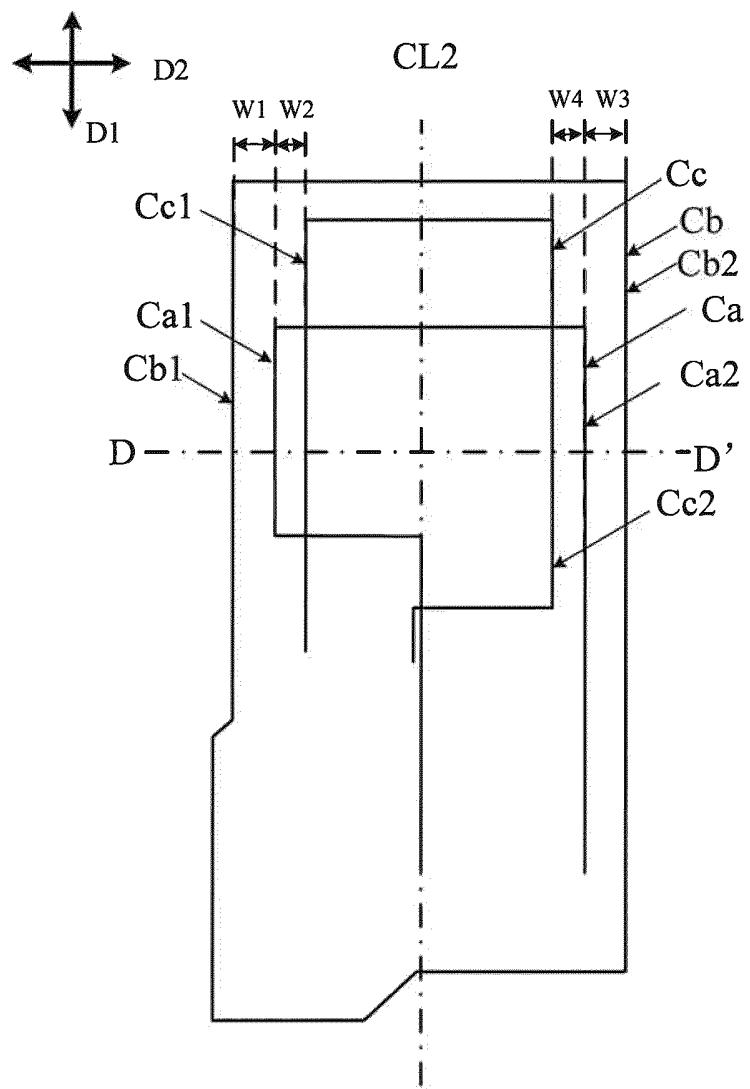

**[0046]** Fig. 2A is a schematic diagram of sub-pixels of a display substrate 10 according to at least one embodiment of the present disclosure, and as shown in Fig. 2A, the display substrate 10 includes a base substrate 101, and a plurality of sub-pixels 100 located on the base substrate 101. The plurality of sub-pixels 100 are arranged as a sub-pixel array having a column direction as a first direction D1 and a row direction as a second direction D2, the first direction D1 intersecting with, e.g., orthogonal to the second direction D2. Six adjacent sub-pixels in a row of sub-pixels are exemplarily shown in Fig. 2A, and the implementation of the present disclosure is not limited to this layout.

**[0047]** Each row of sub-pixels is divided into a plurality of sub-pixel groups PG, each sub-pixel group including a first sub-pixel P1, a second sub-pixel P2, and a third sub-pixel P3 which are sequentially arranged in the second direction. Fig. 2A only schematically shows two adjacent sub-pixel groups PG in one row of sub-pixels. For example, the first, second, and third sub-pixels P1, P2, and P3 are configured to emit light of three primary colors (RGB) respectively, so that each sub-pixel group constitutes one pixel unit. However, the number of sub-pixels included in each sub-pixel group is not limited in the embodiments of the present disclosure.

**[0048]** The display substrate 10 further includes a plurality of data lines 110 extended in the first direction D1, and the plurality of data lines 110 are connected to each column of sub-pixels in the sub-pixel array in one-to-one correspondence to provide data signals for the sub-pixels. The plurality of data lines are divided into a plurality of data line groups, corresponding to the plurality of sub-pixel groups PG in one-to-one correspondence.

**[0049]** As shown in Fig. 2A, each data line group includes a first data line DL1, a second data line DL2, and a third data line DL3 connected to the first sub-pixel P1, the second sub-pixel P2, and the third sub-pixel P3 respectively. For each sub-pixel group PG, the first data line DL1, the second data line DL2 and the third data line

DL3 connected correspondingly to the sub-pixel group PG are all located between the first sub-pixel P1 and the third sub-pixel P3 in the sub-pixel group PG

**[0050]** As shown in Fig. 2A, the display substrate 10 further includes a plurality of auxiliary electrode lines 120 extended in the first direction D1, the plurality of auxiliary electrode lines 120 being configured to be electrically connected with the second electrode of the light emitting element to provide a second power voltage V2, which is, for example, a low power voltage VSS. Each of the plurality of auxiliary electrode lines 120 is spaced from any one of the plurality of data lines 110 by at least one column of sub-pixels 100; that is, the auxiliary electrode line 120 is not directly adjacent to any one of the data lines 110.

With such an arrangement, the signal delay on the data line caused by the resistance-capacitance load due to being directly adjacent to the auxiliary electrode line is avoided, and the problems of color shift, non-uniform display, or the like caused by the delay are further avoided.

**[0051]** For example, as shown in Fig. 2A, for each row of sub-pixels, the auxiliary electrode line 120 is electrically connected to the second electrode (common electrode) of the light emitting element of each sub-pixel in the row of sub-pixels through via holes, thereby forming a parallel structure with the second electrodes of the plurality of light emitting elements, and reducing the resistance for applying the second power voltage.

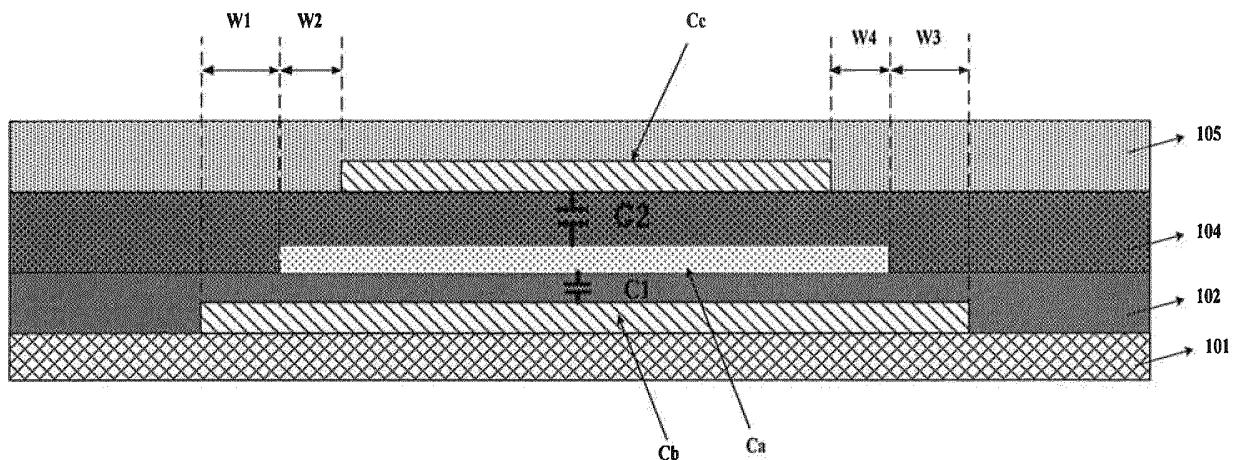

**[0052]** Fig. 2B is a sectional view of Fig. 2A along section line A-A'. With reference to Figs. 2A and 2B, the display substrate 10 includes a first insulating layer 102, a second insulating layer 103, and a third insulating layer 104 sequentially disposed on the base substrate 101, the auxiliary electrode line 120 is located on the third insulating layer 104, for example, and the display substrate 10 further includes a fourth insulating layer 105 and a fifth insulating layer 106 disposed on the auxiliary electrode line 120.

**[0053]** For example, the display substrate 10 further includes a connection electrode 121 on the fifth insulating layer 106, and the auxiliary electrode line 120 is electrically connected to the connection electrode 121 through a via hole 301 (an example of a fourth via hole of the embodiment of the present disclosure) in the fourth insulating layer 105 and a via hole 302 (another example of a fourth via hole of the embodiment of the present disclosure) in the fifth insulating layer 106, and is connected to the second electrode 122 of the light emitting element through the connection electrode 121. For example, the auxiliary electrode line 120 is in the same layer and made of the same material as the data line in the display substrate 10, and is insulated from the data line (as shown in Fig. 6D). For example, the connection electrode 121 is provided in the same layer and made of the same material as the first electrode (not shown) of the light emitting element, and is insulated from the first electrode of the light emitting element.

**[0054]** The light emitting element is, for example, an organic light emitting diode, and includes the first elec-

trode, the second electrode 122, and a light emitting layer (not shown) between the first electrode and the second electrode 122. For example, the light emitting element has a top emission structure, the first electrode is reflective and the second electrode 122 is transmissive or semi-transmissive. For example, the first electrode is made of a high work function material to act as an anode, such as an ITO/Ag/ITO stacked structure; the second electrode 122 is made of a low work function material to serve as a cathode, such as semi-transmissive metallic or metal alloy materials, such as an Ag/Mg alloy material.

**[0055]** For example, the auxiliary electrode line 120 is made of a metal material, such as gold (Au), silver (Ag), copper (Cu), aluminum (Al), molybdenum (Mo), magnesium (Mg), tungsten (W), or an alloy material of any combination thereof. For example, the auxiliary electrode line 120 may also be made of a conductive metal oxide material, such as Indium Tin Oxide (ITO), Indium Zinc Oxide (IZO), zinc oxide (ZnO), Aluminum Zinc Oxide (AZO), or the like.

**[0056]** By connecting the auxiliary electrode line 120 with the second electrode 122 in parallel, the resistance of the second electrode 122 may be reduced, thereby alleviating the problem of non-uniform display caused by the voltage rise or voltage drop on the second electrode 122.

**[0057]** In addition, the auxiliary electrode line 120 may be further in parallel connection with other electrodes to reduce the resistance of the auxiliary electrode line 120, thereby further reducing the resistance of the second electrode 122. For example, referring to Figs. 2A and 6C, the auxiliary electrode line 120 is connected in parallel with the connection electrode 126 in the second conductive layer 502 through the via hole 304, and the connection electrode 126 is in the same layer and made of the same material as the scan line in the display substrate, and is insulated from the scan line.

**[0058]** For example, the display substrate 10 further includes a pixel defining layer 107 on the first electrode of the light emitting element. As shown in Figs. 2A and 2B, the connection electrode 121 is connected to the second electrode 122 of the light emitting element through a via hole 303 (an example of a fifth via hole of the embodiment of the present disclosure) in the pixel defining layer 107. For example, the connection electrode 121 is in the same layer as the first electrode of the light emitting element and is insulated from the first electrode of the light emitting element.

**[0059]** As shown in Figs. 2A and 2B, by providing the connection electrode 121 to electrically connect the second electrode 122 of the light emitting element with the auxiliary electrode line 120, an overlarge segment difference resulting from the second electrode 122 being directly connected to the auxiliary electrode line 120 through a via hole may be avoided, and thus, a wire fracture easily caused by the huge segment difference may be avoided, and correspondingly, problems such as poor contact caused by the wire fracture may be avoided. In

addition, an orthographic projection of the via hole 302 in the fifth insulating layer 106 on the base substrate 101 covers an orthographic projection of the via hole 301 in the fourth insulating layer 105 on the base substrate 101,

so that a step is formed between the via hole 302 and the via hole 301, and the problem of poor contact caused by fracture of the connection electrode 121 due to the overlarge segment difference may be further avoided.

**[0060]** In addition, as shown in Figs. 2A and 2B, an orthogonal projection of the via hole 303 in the pixel defining layer 107 on the base substrate 101 covers an orthogonal projection of the via hole 302 in the fifth insulating layer 106 on the base substrate 101, so that a step is formed between the via hole 303 and the via hole 302, and the second electrode 122 may be prevented from being broken due to a huge segment difference in the via hole 303, thereby avoiding problems such as poor contact caused by electrode breakage.

**[0061]** For example, the first insulating layer 102, the second insulating layer 103, the third insulating layer 104, and the fourth insulating layer 105 are inorganic insulating layers, for example, oxides of silicon, nitrides of silicon or oxynitride of silicon, such as silicon oxide, silicon nitride, silicon oxynitride, or an insulating material including a metal oxynitride, such as aluminum oxide, titanium nitride, or the like. For example, the fifth insulating layer 106 and the pixel defining layer 107 are made of organic insulating materials respectively, such as Polyimide (PI), acrylate, epoxy, polymethyl methacrylate (PMMA), or the like. For example, the fifth insulating layer 106 is a planarization layer.

**[0062]** For example, the light emitting element of the display substrate 10 according to some embodiments of the present disclosure may employ a top emission structure. For example, the pixel defining layer 107 has an opening region corresponding to each sub-pixel, the opening region corresponding to a position where the light emitting layer material of the light emitting element is formed. In Fig. 2A, the opening region 600 of the pixel defining layer 107 corresponding to each sub-pixel is shown by a thick-line rounded rectangle. For example, the opening region 600 exposes the first electrode of the light emitting element, so that the light emitting material may be formed on the first electrode. For example, the shapes and sizes of the plurality of opening regions 600 corresponding to the plurality of sub-pixels are all the same, so that the printing efficiency in manufacturing the display substrate 10 may be improved. Alternatively, the shapes and sizes of the plurality of opening regions 600 corresponding to the plurality of sub-pixels may be changed according to the light emission efficiency, the service life, or the like of the light emitting materials emitting light of different colors, for example, a printing area (opening region) of the light emitting material having a short light emission life may be set to be large, thereby improving the stability of light emission. For example, the size of the opening region 600 of the green sub-pixel, the red sub-pixel, and the blue sub-pixel may be reduced

successively.

**[0063]** For example, as shown in Fig. 2A, the display substrate 10 further includes a plurality of first detection lines 130 extended in the first direction D1, the first detection lines 130 being configured to be connected to a detection sub-circuit (e.g., the third transistor T3) in the sub-pixel 100 and to connect the detection sub-circuit to an external detection circuit. For example, each first detection line 130 is spaced from any one of the plurality of data lines 110 by at least one column of the sub-pixels; that is, the first detection line 130 is not directly adjacent to any data line 110. By such an arrangement, the signal delay on the data line caused by the resistance-capacitance load of the data line due to the direct adjacency of the data line and the first detection line is avoided, and the problems of non-uniform display or the like caused by the delay are further avoided. In addition, since the signal transmitted on the data line 110 is usually a high frequency signal, the first detection line 130 is provided not to be directly adjacent to the data line 110, which may prevent sampling precision from being influenced by crosstalk of the high frequency signal on the first detection line 130 during the external compensation charging sampling process.

**[0064]** Fig. 3 shows another schematic diagram of a display substrate according to at least one embodiment of the present disclosure, Fig. 4 shows a schematic diagram of signal lines of the display substrate corresponding to Fig. 3, and Fig. 5 is a schematic diagram of a display substrate according to another embodiment of the present disclosure.

**[0065]** In Fig. 3, twelve adjacent sub-pixels 100 in a row of sub-pixels are exemplarily shown; in Fig. 4, for the sake of clarity, the specific structure of the sub-pixels is omitted; Fig. 5 schematically shows the case of a plurality of rows of sub-pixels. The arrangement of signal lines in the display substrate according to an embodiment of the present disclosure will be exemplarily described with reference to Figs. 2A and 3 to 5, but the present disclosure is not limited thereto.

**[0066]** As shown in Figs. 3 to 5, for each row of sub-pixels, in the second direction D2, the n-th sub-pixel group PG <n> and the (n+1)th sub-pixel group PG <n+1> constitute a first sub-pixel group unit PGU1, thereby defining a first sub-pixel group unit array PGUA1 including a plurality of first sub-pixel group units; the (n+1)th sub-pixel group PG <n+1> and the (n+2)th sub-pixel group PG <n+2> constitute a second sub-pixel group unit PGU2, thereby defining a second sub-pixel group unit array PGUA2 including a plurality of second sub-pixel group units; here, n is an odd or even number greater than 0. The adjacent first and second sub-pixel group units PGU1 and PGU2 share one sub-pixel group PG (PG <n+1>). The column directions of the first sub-pixel group unit array PGUA1 and the second sub-pixel group unit array PGUA2 are both in the first direction D1.

**[0067]** For example, referring to Figs. 2A and 3, the plurality of first detection lines 130 are correspondingly

connected to the plurality of columns of the first sub-pixel group unit PGU1 respectively, and the second electrodes of the third transistors T3 of the sub-pixels in the first sub-pixel group unit PGU1 located in the same column are all electrically connected to the same corresponding first detection line 130.

**[0068]** For example, each of the first detection lines 130 is located between the n-th sub-pixel group PG <n> and the (n+1)th sub-pixel group PG <n+1> of the correspondingly connected first sub-pixel group unit PGU1. As shown in Figs. 2A and 3, in each first sub-pixel group unit PGU1, a third sub-pixel P3 in the n-th sub-pixel group PG <n> is adjacent to a first sub-pixel P1 in the (n+1)th sub-pixel group PG <n+1>, and the first detection line 130 correspondingly connected to the first sub-pixel group unit PGU1 is located between the third sub-pixel P3 in the n-th sub-pixel group PG <n> and the first sub-pixel P1 in the (n+1)th sub-pixel group PG <n+1>.

**[0069]** For example, as shown in Fig. 3, the plurality of auxiliary electrode lines 120 and the plurality of first detection lines 130 are disposed in one-to-one correspondence, and each auxiliary electrode line 120 is directly adjacent to its corresponding first detection line 130 without a sub-pixel disposed therebetween.

**[0070]** For example, as shown in Fig. 2B, the first detection line 130 and the auxiliary electrode line 120 are disposed in the same layer and made of a same material, and are insulated from each other.

**[0071]** For example, the first detection line 130 may be disposed in parallel connection with other electrodes to reduce the resistance on the first detection line 130. For example, referring to Figs. 2A and 6C, the first detection line 130 is connected in parallel to the connection electrode 127 in the second conductive layer 502 through the via hole 305, and the connection electrode 127 and the scan line in the display substrate are disposed in the same layer and made of a same material, and are insulated from each other.

**[0072]** For example, as shown in Figs. 3 to 5, the display substrate 110 further includes a plurality of detection line segments 131 extended in the second direction D2. Each row of sub-pixels is correspondingly provided with a plurality of detection line segments 131 spaced apart from one another, the plurality of detection line segments 131 are connected to the plurality of first sub-pixel group units PGU1 in the row of sub-pixels in one-to-one correspondence respectively, and the second electrodes of the third transistors T3 in the sub-pixels in each first sub-pixel group unit PGU1 are both electrically connected to a corresponding detection line segment 131. As shown in Fig. 5, the plurality of detection line segments 131 corresponding to the plurality of rows of sub-pixels are arranged into a detection line array, and the column direction of the detection line array is the first direction D1. The plurality of first detection lines 130 are respectively electrically connected to the plurality of columns of detection line segments 131 in the detection line array in one-to-one correspondence, and the plurality of detec-

tion line segments 131 located in the same column respectively intersect with one corresponding first detection line 130 and are electrically connected with the corresponding first detection line 130 through the via hole 201, so as to connect the first detection line to the third transistor T3 in each corresponding sub-pixel 100. Referring to Figs. 3 and 4, each of the detection line segments 131 is electrically connected to the second electrode of the third transistor T3 of each sub-pixel in the corresponding first sub-pixel group unit PGU1 through the via hole 202.

**[0073]** For example, the display substrate 10 further includes a plurality of first power lines 140 extended in the first direction D1, and the plurality of first power lines 140 are configured to provide a first power voltage V1 for the plurality of sub-pixels; the first power voltage is exemplarily a high power voltage VDD. As shown in Figs. 3 and 4, any one of the first power lines 140 is not overlapped with the detection line segment 131 in a direction perpendicular to the base substrate 101, i.e., the first power line 140 is disposed corresponding to an interval of adjacent detection line segments 131. This arrangement reduces the overlap of signal lines and thus effectively reduces the parasitic capacitance between the signal lines and the signal delay caused thereby.

**[0074]** For example, as shown in Figs. 3 and 4, each of the first power lines 140 is spaced from any one of the plurality of data lines 110 by at least one column of sub-pixels; that is, the first power line 140 is not directly adjacent to any one of the data lines 110. With such an arrangement, the signal delay on the data line caused by the resistance-capacitance load due to the directly adjacency of the data line and the first power line is avoided, and the problems of color shift, non-uniform display, or the like caused by the delay are further avoided.

**[0075]** For example, any one of the first power lines 140 is spaced from any one of the auxiliary electrode lines 120 by at least one sub-pixel group PG. For example, as shown in Figs. 3 and 4, the first power line 140 and the auxiliary electrode line 120 are alternately disposed between adjacent sub-pixel groups PG. This arrangement may improve wiring uniformity, thereby reducing wiring density and the risk of short circuits.

**[0076]** For example, as shown in Figs. 3 and 4, the plurality of first power lines 140 are correspondingly connected to the plurality of columns of the second sub-pixel group unit PGU2 respectively, and the second electrodes of the first transistors T1 of the sub-pixels in the second sub-pixel group unit PGU2 in the same column are electrically connected to one corresponding first power line 140.

**[0077]** For example, as shown in Figs. 3 and 4, each of the first power lines 140 is located between the (n+1)th sub-pixel group PG <n+1> and the (n+2)th sub-pixel group PG <n+2> in the correspondingly connected second sub-pixel group unit PGU2. In each second sub-pixel group unit PGU2, the third sub-pixel P3 in the (n+1)th sub-pixel group PG <n+1> is adjacent to the first

sub-pixel P1 in the (n+2)th sub-pixel group PG <n+2>, and the first power line 140 correspondingly connected to the second sub-pixel group unit PGU2 is located between the third sub-pixel P3 in the (n+1)th sub-pixel group PG <n+1> and the first sub-pixel P1 in the (n+2)th sub-pixel group PG <n+2>.

**[0078]** For example, the first power line 140 may be arranged in parallel connection with other electrodes to reduce the resistance on the first power line 140. For example, referring to Figs. 2A and 6C below, the first power line 140 is connected in parallel to the connection electrode 128 in the second conductive layer 502 through the via hole 306, and the connection electrode 128 and the scan line in the display substrate are disposed in the same layer and insulated from each other, and made of the same material.

**[0079]** For example, as shown in Figs. 3 and 4, the display substrate 110 further includes a plurality of power line segments 141 extended in the second direction D2. Each row of sub-pixels is correspondingly provided with a plurality of power line segments 141 spaced apart from one another, the plurality of power line segments 141 connected to the plurality of second sub-pixel group units PGU2 in the row of sub-pixels in one-to-one correspondence respectively, and the second electrode of the first transistor T1 in the sub-pixel in each second sub-pixel group unit PGU2 is electrically connected to a corresponding detection line segment 131. As shown in Fig. 4, the plurality of power line segments 141 corresponding to the plurality of rows of sub-pixels are arranged into a power line array, and the column direction of the power line array is the first direction D1. The plurality of first power lines 140 are electrically connected to the plurality of columns of power line segments 141 in the power line array in one-to-one correspondence respectively, and the plurality of power line segments 141 located in the same column intersect with the same one corresponding first power line 140 respectively and are electrically connected through the via hole 203 (an example of the first via hole in the embodiment of the present disclosure) with the corresponding first power line 140.

**[0080]** Referring to Figs. 3 and 4, for each of the second sub-pixel group units PGU2, the first power line 140 is electrically connected to the second electrode of the first transistor T1 in the sub-pixels (the first sub-pixel in the (n+1)th sub-pixel group PG <n+1> and the third sub-pixel P3 in the (n+2)th sub-pixel group PG <n+2>) adjacent to the first power line 140 through the via hole 204 (an example of the second via hole in the embodiment of the present disclosure); each power line segment 141 is electrically connected to the second electrode of the first transistor T1 in the sub-pixels, which are not adjacent to the first power line 140, through the via hole 205 (an example of the third via hole of the embodiments of the present disclosure), thereby connecting the first power line 140 to the second electrode of the first transistor T1 in the sub-pixels. As shown in Fig. 2A, the first power line 140 is directly electrically connected to the second electrode

of the first transistor T1 in the sub-pixel through the via hole 204, so that the first transistor T1 is prevented from being extended to overlap the scan line, and the parasitic capacitance between the signal lines is reduced.

**[0081]** For example, as shown in Fig. 4, the first power line 140 is disposed closely adjacent to the sub-pixel, that is, no other signal line is present between the first power line 140 and the sub-pixel, so that the first power line 140 may be electrically connected to the sub-pixels on the left and right sides through the via hole 204.

**[0082]** Referring to Figs. 4 and 5, the power line segment 141 is not overlapped with either of the first detection line 130 and the auxiliary electrode line 120 in the direction perpendicular to the base substrate 110; that is, the first detection line 130 and the auxiliary electrode line 120 are disposed corresponding to the interval of the adjacent power line segments 141. This arrangement reduces the overlap of the signal lines and thus effectively reduces the parasitic capacitance between the signal lines and the signal delay caused thereby.

**[0083]** For example, in a display substrate, a mesh electrode may be used to provide a first power voltage, and the plurality of sub-pixels in the display substrate are connected to the mesh electrode to receive the first power voltage, and a structure using the mesh electrode is referred to as a mesh structure. When a defect (e.g., a short circuit defect or a fracture defect) occurs at any position of the mesh electrode in the display substrate having the mesh structure, all the sub-pixels in the display substrate are affected.

**[0084]** As described above, with respect to the mesh structure, the first power line 140 in the display substrate 10 according to the embodiment of the present disclosure adopts a non-mesh structure. Even when a failure occurs in one of the first power lines 140, only the sub-pixels connected to the one first power line 140 are affected, without affecting the sub-pixels connected to other first power lines 140, so that redundancy and stability of the display substrate 10 may be improved; and this configuration facilitates the detection of the defect.

**[0085]** For example, before leaving the factory, the display substrate 10 may be detected to determine whether the product requirements are met. For example, in the detection phase, whether the failure occurs may be determined by detecting parameters, such as voltages and currents on the plurality of first power lines 140, respectively. With respect to the display panel using the mesh structure, the display substrate 10 using the non-mesh structure according to the embodiment of the present disclosure may position the first power line 140 where the defect occurs, so that the defect may be eliminated.

**[0086]** Referring to Figs. 3 and 4, for example, the display substrate 10 further includes a plurality of first scan lines 150 and a plurality of second scan lines 160 extended in the second direction D2, and each row of sub-pixels is correspondingly connected to one of the first scan lines 150 and one of the second scan lines 160 respectively. The plurality of first scan lines 150 are connected to the

gate electrodes of the first transistors T1 in the plurality of rows of sub-pixels respectively to provide the first control signal G1, and the plurality of second scan lines 160 are connected to the gate electrodes of the third transistors T3 in the plurality of rows of sub-pixels respectively to provide the second control signal G2. For example, the first scan line 150 is integrated with the gate electrode of the second transistor T2 of one corresponding row of sub-pixels (the same electrode block), and the second

10 scan line 160 is integrated with the gate electrode of the third transistor T3 of one corresponding row of sub-pixels (the same electrode block).

**[0087]** It should be noted that the first scan line and the second scan line are omitted in Fig. 5 for clarity.

**[0088]** For example, as shown in Figs. 3 and 4, for each row of sub-pixels, in the first direction D1, the corresponding first scan line 150 and second scan line 160 are respectively located on two sides of the first transistor T1 in the row of sub-pixels.

**[0089]** For example, as shown in Fig. 4, each of the first scan lines 150 includes a first portion 151 and a second portion 152 connected alternately, the second portion 152 has a ring structure, and the second portion 152 has a larger size than the first portion 151 in the first direction D1. Each of the second portions 152 intersects with at least one of the data line 110, the auxiliary electrode line 120, the first detection line 130, and the first power supply line 140 in the direction perpendicular to the base substrate 101.

**[0090]** Similarly, each of the second scan lines 160 includes a first portion 161 and a second portion 162 connected alternately, the second portion 162 has a ring structure, and the size of the second portion 162 is larger than that of the first portion 161 in the first direction D1. Each of the second portions 162 intersects with at least one of the data line 110, the auxiliary electrode line 120, the first detection line 130, and the first power supply line 140 in the direction perpendicular to the base substrate 101.

**[0091]** By arranging the portions where the scan line intersects with the data line 110, the auxiliary electrode line 120, the first detection line 130, and the first power line 140 into a ring structure, i.e., a dual-channel structure, the yield of the device may be effectively improved.

**[0092]** For example, the position where the signal lines intersect is easy to cause a short-circuit failure due to electrostatic breakdown of the parasitic capacitance. During detection, when it is detected that a short-circuit failure occurs in one channel of the ring structure, the channel may be cut off (for example, by laser cutting), and the circuit structure may still normally work through the other channel.

**[0093]** Since the width of the second portion is greater than the width of the first portion, the first portion is sandwiched between adjacent second portions to form a concave structure. In the layout design, structures such as via holes may be designed corresponding to the concave structures, so that the pixel density is improved.

**[0094]** For example, as shown in Fig. 3, a channel re-

gion of the third transistor T3 is overlapped with the first portion 161 of the second scan line 160 in the direction perpendicular to the base substrate 101, and is not overlapped with the second portion 162 of the second scan line 160 in the direction perpendicular to the base substrate. For example, as shown in Fig. 4, the second electrode of the third transistor T3 is electrically connected to an active layer of the third transistor T3 through the via hole 206, and the via hole 206 corresponds to the concave structure, thereby saving layout space.

**[0094]** For example, adjacent signal lines correspond to the same second portion of the scan line, thereby reducing the second portion. For example, as shown in Fig. 4, the auxiliary electrode line 120 is adjacent to the first detection line 130, so that they may correspond to the same second portion of the scan line, thereby saving the layout space.

**[0095]** For example, the first portion 151 of the first scan line 150 is integrated with the gate electrode of the second transistor T2 of one corresponding row of sub-pixels (the same electrode block), and the first portion 161 of the second scan line 160 is integrated with the gate electrode of the third transistor T3 of one corresponding row of sub-pixels (the same electrode block).

**[0096]** By connecting the auxiliary electrode line in parallel with the second electrode of the light emitting element, the display substrate according to some embodiments of the present disclosure reduces the voltage drop (or voltage rise) on the second electrode, thereby improving the display quality of the display substrate. The display substrate according to some other embodiments of the present disclosure improves the display quality of the display substrate by reducing the voltage drop (or voltage rise) on the first electrode of the light emitting element.

**[0097]** As shown in Fig. 1B, the first electrode of the light emitting element is electrically connected to the first electrode of the first transistor T1, the first electrode of the third transistor T3, and the second capacitor electrode of the storage capacitor Cst and is connected to a node S. In this situation, if the resistances of the first electrode of the light emitting element, the first electrode of the first transistor T1, the first electrode of the third transistor T3, and the second capacitor electrode of the storage capacitor Cst are large, and a large voltage drop is caused, the potential at the node S will be lost, thereby affecting the gray scale value to be actually displayed by the corresponding sub-pixel, and causing color shift, non-uniform display, or the like.

**[0098]** Some embodiments of the present disclosure provide a display substrate which reduces a distance between via holes, shortens a charge move path, decreases the voltage drop on the wire, and improves the display effect of the display substrate by arranging the via hole connecting the first electrode of the third transistor T3 and the light emitting element in the sub-pixel to be at least overlapped with the via hole connecting the first electrode of the third transistor T3 with the active layer of the third transistor in the direction perpendicular to the

base substrate.

**[0099]** A specific structure of the sub-pixel in the display substrate 10 shown in Fig. 2A will be described below. For convenience of explanation, in the following description, the gate electrode, the first electrode, the second electrode, and the active layer of the first transistor T1 are respectively denoted by T1g, T1s, T1d, and T1a; the gate electrode, the first electrode, the second electrode, and the active layer of the second transistor T2 are respectively denoted by T2g, T2s, T2d, and T2a; the gate electrode, the first electrode, the second electrode, and the active layer of the third transistor T3 are respectively denoted by T3g, T3s, T3d, and T3a; and the first capacitor electrode, the second capacitor electrode, and the third capacitor electrode of the storage capacitor Cst are respectively denoted by Ca, Cb, and Cc.

**[0100]** It should be noted that "disposed in the same layer" in the present disclosure refers to a structure formed by two (or more) structures being formed by the same deposition process and patterned by the same patterning process, and the materials thereof may be the same or different. The "integral structure" in the present disclosure means a structure in which two (or more) structures are connected to each other by being formed through the same deposition process and patterned through the same patterning process, and their materials may be the same or different.