### (12)

# **DEMANDE DE BREVET EUROPEEN**

(43) Date de publication: 01.03.2023 Bulletin 2023/09

(21) Numéro de dépôt: 22190897.3

(22) Date de dépôt: 18.08.2022

(51) Classification Internationale des Brevets (IPC): H10B 63/00 (2023.01) H10N 70/20 (2023.01)

(52) Classification Coopérative des Brevets (CPC): H01L 27/2418; H01L 45/04; H01L 45/1233; H01L 45/146; H01L 45/1675

(84) Etats contractants désignés:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

Etats d'extension désignés:

**BA ME**

Etats de validation désignés:

KH MA MD TN

(30) Priorité: 23.08.2021 FR 2108834

(71) Demandeur: Commissariat à l'énergie atomique et aux énergies alternatives 75015 Paris (FR)

(72) Inventeurs:

GUILLAUME, Nicolas 38054 Grenoble Cedex 09 (FR)

BLONKOWSKI, Serge 38054 Grenoble Cedex 09 (FR)

CHARPIN-NICOLLE, Christelle 38054 Grenoble Cedex 09 (FR)

JALAGUIER, Eric 38054 Grenoble Cedex 09 (FR)

(74) Mandataire: INNOV-GROUP 310, avenue Berthelot 69372 Lyon Cedex 08 (FR)

# (54) PROCÉDÉ DE FABRICATION DE CELLULES MÉMOIRES RÉSISTIVES

(57) Un procédé de fabrication de cellules (C) mémoires resistives est divulgué qui comporte les étapes : a) prévoir un empilement comportant successivement un substrat (1), une première électrode (2), une première couche diélectrique (3) possédant une première rigidité diélectrique, une deuxième électrode (4), une deuxième couche diélectrique (5) possédant une deuxième rigidité diélectrique strictement inférieure à la première rigidité diélectrique, et une troisième électrode (6), la première couche diélectrique (3) et la deuxième électrode (4) présentant une première interface (I<sub>1</sub>), la deuxième couche diélectrique (5) et la deuxième électrode (4) présentant une deuxième interface (I<sub>2</sub>); et

b) graver l'empilement par un bombardement d'espèces électriquement chargées de manière à délimiter des cel·lules (C) mémoires résistives, le bombardement étant adapté de sorte que des espèces électriquement chargées s'accumulent aux première et deuxième interfaces ( $I_1$ ,  $I_2$ ) de chaque cellule mémoire résistive, de manière à générer un champ électrique qui est strictement inférieur à la première rigidité électrique et strictement supérieur à la deuxième rigidité diélectrique, notamment pour former un chemin de conduction électrique (7) au sein de la deuxième couche diélectrique (5) par claquage.

EP 4 142 451 A

20

40

45

#### Domaine technique

**[0001]** L'invention se rapporte au domaine technique des mémoires résistives (ReRAM pour « Resistive Random Access Memory » en langue anglaise). Les mémoires résistives sont des mémoires non-volatiles, c'est-àdire capables de conserver une information en l'absence d'alimentation électrique, appartenant à la famille des mémoires à commutation de résistance. Les mémoires résistives sont considérées comme une technologie émergente en raison d'un plus faible degré de maturité que les mémoires non-volatiles conventionnelles, telles que les mémoires Flash.

1

**[0002]** L'invention trouve notamment son application dans la fabrication de cellules mémoires résistives à base d'oxyde métallique (OxRAM pour « *Oxide Random Access Memory* » en langue anglaise).

#### État de l'art

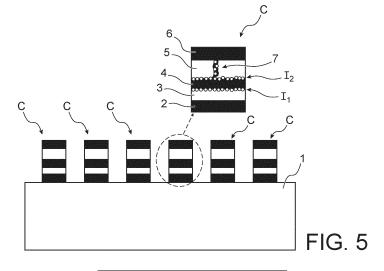

[0003] Comme illustré à la figure 1, une cellule mémoire résistive, connue de l'état de la technique, est formée à partir d'un empilement comprenant successivement un substrat 100, une première électrode 200, une couche diélectrique 300, et une deuxième électrode 400. La première électrode 200, la couche diélectrique 300 et la deuxième électrode 400 forment une structure de type Métal-Isolant-Métal (MIM).

[0004] Un procédé de fabrication de cellules mémoires résistives, connu de l'état de la technique, comporte une étape initiale d'électro-formation (« electroforming » ou « forming » en langue anglaise), consistant à appliquer une tension électrique V<sub>Forming</sub> entre les première et deuxième électrodes de l'empilement, adaptée pour générer un champ électrique supérieur à la rigidité diélectrique de la couche diélectrique. Il en résulte un claquage de la couche diélectrique, s'accompagnant de la formation d'un chemin de conduction électrique au sein de la couche diélectrique, reliant les première et deuxième électrodes.

[0005] Le fonctionnement d'une cellule mémoire résistive se traduit par des cycles de réinitialisation (« Reset» en langue anglaise) où le chemin de conduction électrique est rompu, et des cycles d'écriture (« Set» en langue anglaise) où le chemin de conduction électrique est formé de nouveau. Plus précisément, une cellule mémoire résistive présente un état de haute résistance (H<sub>RS</sub> pour «High Résistance State» en langue anglaise) lorsque le chemin de conduction électrique est rompu, et un état de basse résistance (L<sub>RS</sub> pour « Low Resistance State» en langue anglaise) lorsque le chemin de conduction électrique est formé de nouveau. Les cycles de réinitialisation se traduisent par une commutation de l'état L<sub>RS</sub> vers l'état H<sub>RS</sub>, caractérisée par l'application d'une tension électrique V<sub>Reset</sub> entre les première et deuxième électrodes de la cellule mémoire résistive. Les cycles

d'écriture se traduisent par une commutation de l'état  $H_{RS}$  vers l'état  $L_{RS}$ , caractérisée par l'application d'une tension électrique  $V_{set}$  entre les première et deuxième électrodes de la cellule mémoire résistive.

**[0006]** Les commutations entre les états H<sub>RS</sub> et L<sub>RS</sub> peuvent avoir une nature unipolaire, bipolaire, ou non-polaire selon la physique de commutation mise en œuvre et les rôles joués par la couche diélectrique et les première et deuxième électrodes de la cellule mémoire résistive. Plus précisément, les commutations entre les états H<sub>RS</sub> et L<sub>RS</sub> ont une nature :

- (i) unipolaire lorsque les tensions électriques  $V_{set}$  et  $V_{Reset}$  sont d'un seul et unique signe,

- (ii) bipolaire lorsque la tension électrique V<sub>set</sub> est d'un seul et unique signe, et la tension électrique V<sub>Reset</sub> est du signe opposé,

- (iii) non-polaire lorsque la tension électrique  $V_{set}$  peut être de signe positif ou négatif, et la tension électrique  $V_{Reset}$  est du signe opposé.

[0007] L'étape d'électro-formation de l'état de la technique n'est pas entièrement satisfaisante dans la mesure où elle implique une tension électrique V<sub>Forming</sub> élevée (très supérieure à V<sub>Set</sub>), afin de générer un champ électrique supérieur à la rigidité diélectrique de la couche diélectrique de l'empilement, et ce pour obtenir un claquage de la couche diélectrique. La couche diélectrique est donc fortement sollicitée et le matériau diélectrique risque d'être irrémédiablement endommagé. Or, le claquage de la couche diélectrique doit être réversible afin de reconstruire le chemin de conduction électrique. Pour ce faire, un transistor doit être généralement agencé en série de l'empilement afin de contrôler l'intensité du courant circulant entre les première et deuxième électrodes de l'empilement (intensité typiquement limitée à quelques centaines de μA).

## Exposé de l'invention

**[0008]** L'invention vise à remédier en tout ou partie aux inconvénients précités. A cet effet, l'invention a pour objet un procédé de fabrication de cellules mémoires résistives, comportant les étapes :

- a) prévoir un empilement comportant successivement :

- un substrat, comprenant de préférence des transistors et une structure d'interconnexions;

- une première électrode ;

- une première couche diélectrique, possédant une première rigidité électrique;

- une deuxième électrode, métallique ;

- une deuxième couche diélectrique, possédant une deuxième rigidité diélectrique strictement inférieure à la première rigidité diélectrique;

- une troisième électrode ;

2

la première couche diélectrique et la deuxième électrode présentant une première interface, la deuxième couche diélectrique et la deuxième électrode présentant une deuxième interface ;

b) graver l'empilement par un bombardement d'espèces électriquement chargées, de manière à délimiter des cellules mémoires résistives ;

le bombardement de l'étape b) étant adapté de sorte que des espèces électriquement chargées s'accumulent aux première et deuxième interfaces de chaque cellule mémoire résistive, de manière à générer un champ électrique qui est strictement inférieur à la première rigidité électrique et strictement supérieur à la deuxième rigidité diélectrique.

#### Définitions

#### [0009]

- Par « substrat », on entend un support physique autoporté, par exemple une plaquette (« wafer» en langue anglaise) découpée dans un lingot monocristallin de matériau semiconducteur.

- Par « structure d'interconnexions », on entend un empilement de niveaux d'interconnexions comprenant des pistes métalliques séparées par un matériau diélectrique. Une structure d'interconnexions peut être formée sur le substrat dans une ligne de fabrication de niveaux d'interconnexions électrique BEOL («Back-End-Of-Line» en langue anglaise, on parle également d'unité de fabrication finale). Les transistors peuvent être intégrés de manière monolithique au substrat dans une ligne de fabrication de dispositifs semi-conducteurs FEOL («Front-End-Of-Line» en langue anglaise, on parle également d'unité de fabrication initiale), en utilisant par exemple des techniques de photolithographie, gravure, diffusion et implantation de dopants, dépôts métalliques, passivation etc.

- Par « rigidité diélectrique », on entend la valeur maximale du champ électrique que la couche diélectrique correspondante peut supporter avant une rupture diélectrique (claquage).

- Par « bombardement adapté », on entend que les paramètres du bombardement (par exemple l'énergie et la dose pour une gravure ionique réactive) sont ajustés pour générer l'intensité souhaitée du champ électrique.

[0010] Ainsi, un tel procédé selon l'invention permet de s'affranchir d'une étape d'électro-formation de l'état de la technique, en profitant d'une gravure adaptée de l'empilement (délimitant les cellules mémoires résistives) pour générer un champ électrique permettant d'obtenir le claquage de la deuxième couche diélectrique (dite active). Un tel procédé selon l'invention permet donc de limiter l'intensité du courant électrique (de l'ordre du  $\mu A$

à comparer aux centaines de  $\mu$ A de l'état de la technique) circulant au sein de la deuxième couche diélectrique, via un chemin de conduction électrique obtenu par claquage, si bien qu'il est possible de s'affranchir d'un transistor pour contrôler l'intensité du courant électrique. Ceci est rendu possible grâce à la présence de la première couche diélectrique (dite passive) et de la deuxième électrode métallique, intercalaire, qui permet de piéger les espèces électriquement chargées.

[0011] Le champ électrique généré lors de l'étape b) est inférieur à la première rigidité diélectrique afin de ne pas obtenir un claquage de la première couche diélectrique. Un tel claquage serait préjudiciable car les espèces électriquement chargées accumulées aux première et deuxième interfaces pourraient alors s'évacuer vers la première électrode, et empêcheraient par là-même le claquage de la deuxième couche diélectrique et la formation du chemin de conduction électrique en son sein. [0012] Le procédé selon l'invention peut comporter une ou plusieurs des caractéristiques suivantes.

[0013] Selon une caractéristique de l'invention, les espèces électriquement chargées s'accumulent lors de l'étape b) aux première et deuxième interfaces de chaque cellule mémoire résistive, selon une densité surfacique de charge adaptée pour générer le champ électrique qui est strictement inférieur à la première rigidité électrique et strictement supérieur à la deuxième rigidité diélectrique.

[0014] Ainsi, les paramètres du bombardement (par exemple l'énergie et la dose pour une gravure ionique réactive) sont ajustés pour adapter la densité surfacique de charge à l'intensité souhaitée du champ électrique.

[0015] Selon une caractéristique de l'invention, la première couche diélectrique de l'empilement prévu lors de l'étape a) présente une épaisseur choisie en fonction du champ électrique généré lors de l'étape b) de manière à autoriser un courant tunnel circulant entre les première et deuxième électrodes.

### 40 Définition

[0016] Par « courant tunnel », on entend un courant électrique dont le mécanisme de conduction électrique implique un effet tunnel, c'est-à-dire le mécanisme dit « tunnel direct » ou le mécanisme dit « Fowler-Nordheim » selon la forme de la barrière de potentiel vue par les électrons.

[0017] Ainsi, un avantage procuré par de tels régimes de conduction électrique (impliquant une première couche diélectrique ultra-mince) est de réduire fortement la résistance électrique de la première couche diélectrique par rapport à une couche mince, tout en évitant un régime de conduction ohmique. De tels régimes de conduction par effet tunnel permettent de rendre négligeable la résistance électrique de la première couche diélectrique devant la résistance électrique, notée R<sub>off</sub>, de la deuxième couche diélectrique lorsque la cellule mémoire résistive présente un état de haute résistance H<sub>RS</sub>. En

50

d'autres termes, de tels régimes de conduction par effet tunnel permettent de limiter fortement la chute de potentiel électrique entre les première et deuxième électrodes lorsque la tension électrique V<sub>Reset</sub> est appliquée entre les première et troisième électrodes de la cellule mémoire résistive.

**[0018]** Selon une caractéristique de l'invention, le procédé comporte :

- une étape c) consistant à appliquer une première tension électrique, notée V<sub>Set</sub>, entre les première et troisième électrodes de chaque cellule mémoire résistive, adaptée pour former un chemin de conduction électrique au sein de la deuxième couche diélectrique reliant les deuxième et troisième électrodes.

- une étape d) consistant à appliquer une deuxième tension électrique, notée V<sub>Reset</sub>, entre les première et troisième électrodes de chaque cellule mémoire résistive, adaptée pour rompre le chemin de conduction électrique formé lors de l'étape c);

procédé dans lequel la deuxième couche diélectrique de chaque cellule mémoire résistive présente, à l'issue de l'étape d), une résistance électrique notée R<sub>off</sub>, de préférence comprise entre 10<sup>4</sup> et 2.10<sup>5</sup> ohms ;

et la première couche diélectrique de l'empilement prévu lors de l'étape a) est adaptée pour présenter une résistance électrique strictement inférieure à  $R_{\rm off}$ , de préférence inférieure ou égale à  $R_{\rm off}$ /10.

**[0019]** Ainsi, il a été constaté expérimentalement que les cellules mémoires résistives obtenues à l'issue de l'étape b) ne sont pas directement dans un état de basse résistance  $L_{RS}$ . Une telle étape c), exécutée après l'étape b), permet d'imposer l'état de basse résistance  $L_{RS}$ .

[0020] L'étape d) permet de commuter l'état de basse résistance  $L_{RS}$  obtenu lors de l'étape c) vers un état de haute résistance  $H_{RS}$ .

**[0021]** Une telle première couche diélectrique permet de limiter fortement la chute de potentiel électrique entre les première et deuxième électrodes lorsque la tension électrique V<sub>Reset</sub> est appliquée entre les première et troisième électrodes de la cellule mémoire résistive.

**[0022]** Selon une caractéristique de l'invention, l'étape a) est exécutée de sorte que la deuxième couche diélectrique est réalisée dans un oxyde d'hafnium; et le bombardement de l'étape b) est adapté de sorte que des espèces électriquement chargées s'accumulent aux première et deuxième interfaces de chaque cellule mémoire résistive, selon une densité surfacique de charge comprise entre 10<sup>13</sup> C par cm<sup>2</sup> et 5.10<sup>13</sup> C par cm<sup>2</sup>.

[0023] Ainsi, un avantage procuré est de générer un champ électrique de l'ordre de 3 10<sup>6</sup> V/cm, supérieur à la rigidité diélectrique d'un oxyde d'hafnium, par l'application du théorème de Gauss. Lorsque le claquage se produit au sein de la deuxième couche diélectrique, si

l'on considère que le chemin de conduction électrique créé est un filament présentant une section de 1 nm², que les espèces électriquement chargées sont des électrons ayant une vitesse de l'ordre de la vitesse de Fermi (de l'ordre de 10<sup>5</sup> m/s), le courant électrique circulant entre les deuxième et troisième électrodes est de l'ordre du μA.

**[0024]** Selon une caractéristique de l'invention, l'étape b) est exécutée par une technique de gravure choisie parmi :

- une gravure ionique réactive ;

- une gravure au plasma.

- [0025] Ainsi, un avantage procuré par de telles techniques de gravure est d'impliquer des espèces électriquement chargées.

**[0026]** L'invention a également pour objet un empilement pour fabriquer des cellules mémoires résistives, comportant successivement :

- un substrat, comprenant de préférence des transistors et une structure d'interconnexions;

- une première électrode ;

- <sup>25</sup> une première couche diélectrique, possédant une première rigidité électrique ;

- une deuxième électrode, métallique ;

- une deuxième couche diélectrique, possédant une deuxième rigidité diélectrique strictement inférieure à la première rigidité diélectrique;

- une troisième électrode.

**[0027]** Selon une caractéristique de l'invention, la deuxième électrode présente une épaisseur comprise entre 5 nm et 100 nm, de préférence comprise entre 5 nm et 40 nm.

**[0028]** Selon une caractéristique de l'invention, la deuxième électrode est réalisée dans au moins un matériau métallique choisi parmi :

- Au, Ag, Pt, Pd, Ir, Rh, Os, Ru, Cu, Re, Hg,

- TiN, TaN.

40

[0029] En particulier, un avantage procuré par Au, Ag, Pt, Pd, Ir, Rh, Os, Ru, Cu, Re, Hg est leur forte résistance à l'oxydation. Cette propriété permet de réduire les risques d'une migration d'ions métalliques vers la première électrode, qui autoriserait potentiellement l'évacuation des espèces électriquement chargées, accumulées aux première et deuxième interfaces, vers la première électrode. Une telle migration d'ions métalliques rendrait donc le claquage de la deuxième couche diélectrique, et par là-même la formation du chemin de conduction électrique en son sein, plus difficile à obtenir.

**[0030]** Selon une caractéristique de l'invention, les première et troisième électrodes sont réalisées dans au moins un matériau choisi parmi Ti, TiN, Pt, Zr, Al, Hf, Ta, TaN, C, Cu, Ag, W.

15

**[0031]** Selon une caractéristique de l'invention, la première couche diélectrique présente une épaisseur comprise entre 1 nm et 3 nm.

[0032] Ainsi, un avantage procuré est d'autoriser un régime de conduction électrique par effet tunnel.

**[0033]** Selon une caractéristique de l'invention, la deuxième couche diélectrique présente une épaisseur comprise entre 4 nm et 15 nm, de préférence comprise entre 5 nm et 10 nm.

[0034] Selon une caractéristique de l'invention, la deuxième couche diélectrique est réalisée dans un matériau choisi parmi un oxyde d'hafnium, un oxyde de titane, un oxyde de tantale, un oxyde de nickel, un oxyde de zinc, un oxyde de cuivre, le titanate de zinc, un oxyde de manganèse, un oxyde de magnésium, un oxyde de zirconium, un oxyde de silicium, un nitrure de silicium.

[0035] Selon une caractéristique de l'invention :

- la première couche diélectrique est réalisée dans un matériau choisi parmi l'alumine, un nitrure de silicium, un oxyde de silicium;

- la deuxième couche diélectrique est réalisée dans un oxyde d'hafnium.

**[0036]** Ainsi, un avantage procuré par un matériau choisi parmi l'alumine, un nitrure de silicium, un oxyde de silicium est d'avoir une rigidité diélectrique supérieure à celle d'un oxyde d'hafnium.

[0037] Selon une caractéristique de l'invention :

- la première couche diélectrique est réalisée dans un oxyde d'hafnium;

- la deuxième couche diélectrique est réalisée dans un oxyde de titane.

[0038] Ainsi, un avantage procuré par un oxyde d'hafnium est d'avoir une rigidité diélectrique supérieure à celle d'un oxyde de titane.

### Brève description des dessins

**[0039]** D'autres caractéristiques et avantages apparaîtront dans l'exposé détaillé de différents modes de réalisation de l'invention, l'exposé étant assorti d'exemples et de références aux dessins joints.

Figure 1 (déjà commentée) est une vue schématique en coupe d'un empilement de l'état de la technique pour fabriquer des cellules mémoires résistives.

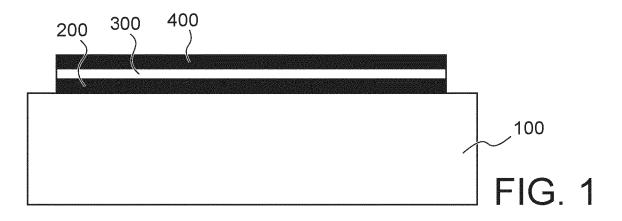

Figure 2 est une vue schématique en coupe d'un empilement selon l'invention pour fabriquer des cellules mémoires résistives.

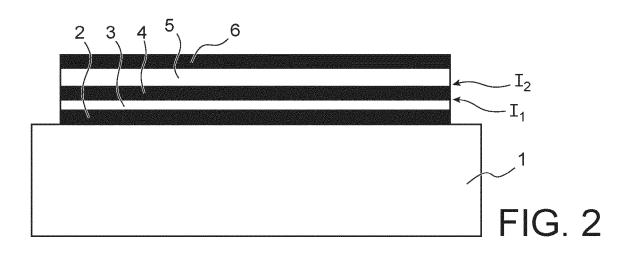

Figure 3 est une vue schématique en coupe, illustrant l'étape b) de gravure (symbolisée par les flèches) d'un procédé selon l'invention.

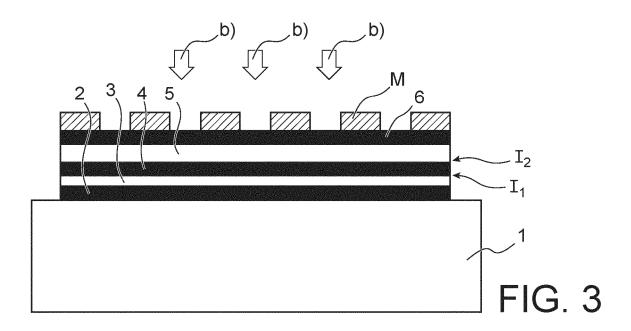

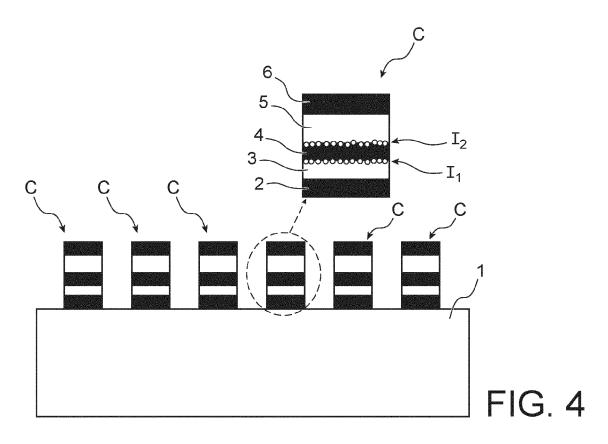

Figure 4 est une vue schématique en coupe, illustrant des cellules mémoires résistives formées par la gravure de l'étape b). L'encart illustre une cellule

mémoire résistive à l'échelle agrandie où est visible l'accumulation des espèces électriquement chargées (symbolisées par des ronds) aux première et deuxième interfaces.

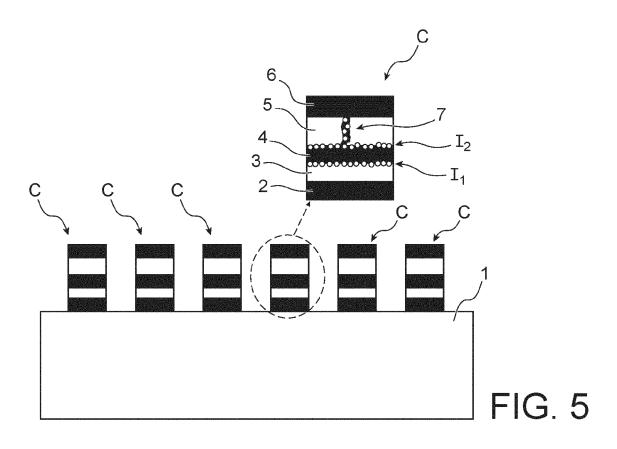

Figure 5 est une vue analogue à la figure 4. L'encart illustre la formation d'un chemin de conduction électrique au sein de la deuxième couche diélectrique, à l'issue de l'étape b).

[0040] Il est à noter que les dessins décrits ci-avant sont schématiques, et ne sont pas à l'échelle par souci de lisibilité et pour en simplifier leur compréhension.

### Exposé détaillé des modes de réalisation

[0041] Les éléments identiques ou assurant la même fonction porteront les mêmes références pour les différents modes de réalisation, par souci de simplification.

[0042] Un objet de l'invention est un procédé de fabrication de cellules C mémoires résistives, comportant les étapes :

- a) prévoir un empilement comportant successivement :

- un substrat 1, comprenant de préférence des transistors et une structure d'interconnexions (non illustrés);

- une première électrode 2;

- une première couche diélectrique 3, possédant une première rigidité électrique ;

- une deuxième électrode 4, métallique ;

- une deuxième couche diélectrique 5, possédant une deuxième rigidité diélectrique strictement inférieure à la première rigidité diélectrique;

- une troisième électrode 6 ;

la première couche diélectrique 3 et la deuxième électrode 4 présentant une première interface I<sub>1</sub>, la deuxième couche diélectrique 5 et la deuxième électrode 4 présentant une deuxième interface I<sub>2</sub>; b) graver l'empilement par un bombardement d'espèces électriquement chargées, de manière à déli-

le bombardement de l'étape b) étant adapté de sorte que des espèces électriquement chargées s'accumulent aux première et deuxième interfaces  $I_1$ ,  $I_2$  de chaque cellule C mémoire résistive, de manière à générer un champ électrique qui est strictement inférieur à la première rigidité électrique et strictement supérieur à la deuxième rigidité diélectrique.

miter des cellules C mémoires résistives ;

**[0043]** L'empilement prévu lors de l'étape a) est illustré à la figure 2. L'empilement, après l'étape de lithographie et avant l'étape b) de gravure, est illustré à la figure 3. L'accumulation des charges électriquement chargées aux première et deuxième interfaces I<sub>1</sub>, I<sub>2</sub> est illustrée à la figure 4. Le claquage de la deuxième couche diélec-

5

40

30

35

45

\_

trique 5 obtenu à l'issue de l'étape b) est illustré à la figure 5

### Etape a): substrat

**[0044]** A titre d'exemple non limitatif, l'étape a) peut être exécutée de sorte que le substrat 1 est une plaquette (*«wafer»* en langue anglaise) de silicium.

**[0045]** Le substrat 1 comprend avantageusement des transistors pouvant être intégrés de manière monolithique au substrat 1 dans une ligne de fabrication de dispositifs semi-conducteurs FEOL (*«Front-End-Of-Line»* en langue anglaise, on parle également d'unité de fabrication initiale), en utilisant par exemple des techniques de photolithographie, gravure, diffusion et implantation de dopants, dépôts métalliques, passivation etc.

**[0046]** Le substrat 1 comprend avantageusement une structure d'interconnexions pouvant être formée sur le substrat 1 dans une ligne de fabrication de niveaux d'interconnexions électrique BEOL (*«Back-End-Of-Line»* en langue anglaise, on parle également d'unité de fabrication finale).

[0047] La première électrode 2, la première couche diélectrique 3, la deuxième électrode 4, la deuxième couche diélectrique 5 et la troisième électrode 6 s'étendent avantageusement entre deux niveaux d'interconnexions (niveaux métalliques) de la structure d'interconnexions. Les transistors et la structure d'interconnexions peuvent être situés à des niveaux inférieurs par rapport à la première électrode 2, la première couche diélectrique 3, la deuxième électrode 4, la deuxième couche diélectrique 5 et la troisième électrode 6.

# Etape a) : première électrode

[0048] L'étape a) est avantageusement exécutée de sorte que la première électrode 2 est réalisée dans au moins un matériau choisi parmi Ti, TiN, Pt, Zr, Al, Hf, Ta, TaN, C, Cu, Ag, W. La première électrode 2 peut être un alliage de ces matériaux.

**[0049]** La première électrode 2 peut présenter une épaisseur supérieure ou égale à 5 nm ou supérieure ou égale à 10 nm.

**[0050]** La première électrode 2 peut être formée sur un trou d'interconnexions («via» en langue anglaise) d'un niveau métallique de la structure d'interconnexions. La première électrode 2 peut être réalisée dans le matériau du trou d'interconnexions ou dans un autre matériau (différent du matériau du trou d'interconnexions) déposé sur le trou d'interconnexions.

# Etape a) : première couche diélectrique

**[0051]** La première couche diélectrique 3 de l'empilement prévu lors de l'étape a) présente avantageusement une épaisseur choisie en fonction du champ électrique généré lors de l'étape b) de manière à autoriser un courant tunnel circulant entre les première et deuxième élec-

trodes 2, 4. L'étape a) est avantageusement exécutée de sorte que la première couche diélectrique 3 présente une épaisseur comprise entre 1 nm et 3 nm, de préférence comprise entre 1 nm et 2 nm.

[0052] La première couche diélectrique 3 de l'empilement prévu lors de l'étape a) est avantageusement adaptée pour présenter une résistance électrique strictement inférieure à R<sub>off</sub>, de préférence inférieure ou égale à R<sub>off</sub>/10 (cf. section « Mise en fonctionnement des cellules mémoires résistives » pour la définition de R<sub>off</sub>).

#### Etape a) : deuxième électrode

**[0053]** L'étape a) est avantageusement exécutée de sorte que la deuxième électrode 4 présente une épaisseur comprise entre 5 nm et 100 nm, de préférence comprise entre 5 nm et 40 nm.

**[0054]** L'étape a) est avantageusement exécutée de sorte que la deuxième électrode 4 est réalisée dans au moins un matériau métallique choisi parmi :

- Au, Ag, Pt, Pd, Ir, Rh, Os, Ru, Cu, Re, Hg,

- TiN, TaN.

**[0055]** La deuxième électrode 4 peut être réalisée dans un alliage électriquement conducteur.

#### Etape a): deuxième couche diélectrique

**[0056]** La deuxième couche diélectrique 5 forme la couche active de la cellule C mémoire résistive. Autrement dit, la deuxième couche diélectrique 5 forme la couche mémoire.

**[0057]** L'étape a) est avantageusement exécutée de sorte que la deuxième couche diélectrique 5 présente une épaisseur comprise entre 4 nm et 15 nm, de préférence comprise entre 5 nm et 10 nm.

[0058] L'étape a) est avantageusement exécutée de sorte que la deuxième couche diélectrique 5 est réalisée dans un matériau choisi parmi un oxyde d'hafnium, un oxyde de titane, un oxyde de tantale, un oxyde de nickel, un oxyde de zinc, un oxyde de cuivre, le titanate de zinc, un oxyde de manganèse, un oxyde de magnésium, un oxyde de zirconium, un oxyde de silicium, un nitrure de silicium.

**[0059]** A titre d'exemple non limitatif, lorsque la deuxième couche diélectrique 5 est réalisée dans un oxyde d'hafnium, alors la première couche diélectrique 3 peut être réalisée dans un matériau choisi parmi l'alumine, un nitrure de silicium, un oxyde de silicium.

[0060] A titre d'exemple non limitatif, lorsque la deuxième couche diélectrique 5 est réalisée dans un oxyde de titane, alors la première couche diélectrique 3 peut être réalisée dans un oxyde d'hafnium. Dans ce mode de réalisation, l'oxyde d'hafnium est passif et la couche mémoire (active) est réalisée dans un oxyde de titane. L'oxyde d'hafnium possède une rigidité diélectrique supérieure à

40

celle d'un oxyde de titane.

#### Etape a): troisième électrode

[0061] L'étape a) est avantageusement exécutée de sorte que la troisième électrode 6 est réalisée dans au moins un matériau choisi parmi Ti, TiN, Pt, Zr, Al, Hf, Ta, TaN, C, Cu, Ag, W. La troisième électrode 6 peut être un alliage de ces matériaux ou un empilement d'une partie de ces matériaux.

**[0062]** La troisième électrode 6 peut présenter une épaisseur supérieure ou égale à 10 nm.

**[0063]** La troisième électrode 6 comporte avantageusement une couche destinée à assurer une fonction de getter pour piéger des atomes d'oxygène. A titre d'exemple non limitatif, la troisième électrode 6 peut être un empilement Ti/TiN ou Ti/TaN, la couche de Ti étant proximale par rapport à la deuxième couche diélectrique 5. La couche de Ti assure une fonction de getter pour piéger les atomes d'oxygène.

# Etape b) de gravure

**[0064]** Comme illustré à la figure 3, l'empilement est recouvert d'un masque M avant l'étape b) de gravure. Le masque M peut être un masque dur ou une résine.

[0065] Comme illustré aux figures 4 et 5, les espèces électriquement chargées s'accumulent avantageusement lors de l'étape b) aux première et deuxième interfaces I<sub>1</sub>, I<sub>2</sub> de chaque cellule C mémoire résistive, selon une densité surfacique de charge adaptée pour générer le champ électrique qui est strictement inférieur à la première rigidité électrique et strictement supérieur à la deuxième rigidité diélectrique.

**[0066]** Lorsque l'étape a) est exécutée de sorte que la deuxième couche diélectrique 5 est réalisée dans un oxyde d'hafnium, le bombardement de l'étape b) est avantageusement adapté de sorte que des espèces électriquement chargées s'accumulent aux première et deuxième interfaces  $I_1$ ,  $I_2$  de chaque cellule C mémoire résistive, selon une densité surfacique de charge typiquement comprise entre  $10^{13}$  C par cm² et 5.  $10^{13}$  C par cm².

**[0067]** L'étape b) est avantageusement exécutée par une technique de gravure choisie parmi :

- une gravure ionique réactive ;

- une gravure au plasma.

[0068] A titre d'exemple non limitatif, lorsque la première électrode 2 est réalisée en TiN, la deuxième électrode 4 est réalisée en TiN, la troisième électrode 6 est réalisée en Ti/TiN, et la deuxième couche diélectrique 5 est réalisée en HfO<sub>2</sub>, l'étape b) peut utiliser une chimie à base chlorée.

### Mise en fonctionnement des cellules mémoires ré-

### sistives

[0069] Le procédé peut comporter une étape c) consistant à appliquer une première tension électrique, notée  $V_{Set}$ , entre les première et troisième électrodes 2, 6 de chaque cellule C mémoire résistive, adaptée pour former un chemin de conduction 7 électrique (visible à la figure 5) au sein de la deuxième couche diélectrique 5 reliant les deuxième et troisième électrodes 4, 6. A titre d'exemple,  $V_{set}$  peut être compris entre 1 V et 3 V.

[0070] Le procédé peut comporter une étape d) consistant à appliquer une deuxième tension électrique, notée V<sub>Reset</sub>, entre les première et troisième électrodes 2, 6 de chaque cellule C mémoire résistive, adaptée pour rompre le chemin de conduction 7 électrique formé lors de l'étape c). La deuxième couche diélectrique 5 de chaque cellule C mémoire résistive présente, à l'issue de l'étape d), une résistance électrique notée R<sub>off</sub>, de préférence comprise entre 10<sup>4</sup> et 2. 10<sup>5</sup> ohms. A titre d'exemple, V<sub>Reset</sub> peut être compris entre -1 V et -3 V.

**[0071]** La deuxième électrode 4 de chaque cellule C mémoire résistive est une électrode à potentiel flottant, c'est-à-dire que la deuxième électrode 4 n'est pas soumise à un potentiel électrique de référence au cours du fonctionnement de la cellule C mémoire résistive.

### **Empilement**

35

40

**[0072]** L'invention a également pour objet un empilement pour fabriquer des cellules C mémoires résistives, comportant successivement :

- un substrat 1, comprenant de préférence des transistors et une couche d'interconnexions;

- une première électrode 2 ;

- une première couche diélectrique 3, possédant une première rigidité électrique ;

- une deuxième électrode 4, métallique ;

- une deuxième couche diélectrique 5, possédant une deuxième rigidité diélectrique strictement inférieure à la première rigidité diélectrique;

- une troisième électrode 6.

[0073] Les caractéristiques techniques décrites ciavant pour le procédé (le substrat 1 ; les première, deuxième, et troisième électrodes 2, 4, 6 ; les première et deuxième couches diélectriques 3, 5) s'appliquent également pour cet objet de l'invention.

**[0074]** L'invention ne se limite pas aux modes de réalisation exposés. L'homme du métier est mis à même de considérer leurs combinaisons techniquement opérantes, et de leur substituer des équivalents.

### 55 Revendications

1. Procédé de fabrication de cellules (C) mémoires résistives, comportant les étapes :

20

25

35

40

45

50

- a) prévoir un empilement comportant successivement :

- un substrat (1), comprenant de préférence des transistors et une structure d'interconnexions;

- une première électrode (2);

- une première couche diélectrique (3), possédant une première rigidité électrique ;

- une deuxième électrode (4), métallique ;

- une deuxième couche diélectrique (5), possédant une deuxième rigidité diélectrique strictement inférieure à la première rigidité diélectrique :

- une troisième électrode (6);

la première couche diélectrique (3) et la deuxième électrode (4) présentant une première interface ( $I_1$ ), la deuxième couche diélectrique (5) et la deuxième électrode (4) présentant une deuxième interface ( $I_2$ );

b) graver l'empilement par un bombardement d'espèces électriquement chargées, de manière à délimiter des cellules (C) mémoires résistives;

le bombardement de l'étape b) étant adapté de sorte que des espèces électriquement chargées s'accumulent aux première et deuxième interfaces (I<sub>1</sub>, I<sub>2</sub>) de chaque cellule (C) mémoire résistive, de manière à générer un champ électrique qui est strictement inférieur à la première rigidité électrique et strictement supérieur à la deuxième rigidité diélectrique.

- 2. Procédé selon la revendication 1, dans lequel les espèces électriquement chargées s'accumulent lors de l'étape b) aux première et deuxième interfaces (I<sub>1</sub>, I<sub>2</sub>) de chaque cellule (C) mémoire résistive, selon une densité surfacique de charge adaptée pour générer le champ électrique qui est strictement inférieur à la première rigidité électrique et strictement supérieur à la deuxième rigidité diélectrique.

- 3. Procédé selon la revendication 1 ou 2, dans lequel la première couche diélectrique (3) de l'empilement prévu lors de l'étape a) présente une épaisseur choisie en fonction du champ électrique généré lors de l'étape b) de manière à autoriser un courant tunnel circulant entre les première et deuxième électrodes (2, 4).

- 4. Procédé selon l'une des revendications 1 à 3, comportant :

- une étape c) consistant à appliquer une première tension électrique, notée V<sub>Set</sub>, entre les première et troisième électrodes (2, 6) de chaque cellule (C) mémoire résistive, adaptée pour

former un chemin de conduction (7) électrique au sein de la deuxième couche diélectrique (5) reliant les deuxième et troisième électrodes (4, 6);

- une étape d) consistant à appliquer une deuxième tension électrique, notée  $V_{Reset}$ , entre les première et troisième électrodes (2, 6) de chaque cellule (C) mémoire résistive, adaptée pour rompre le chemin de conduction (7) électrique formé lors de l'étape c) ;

procédé dans lequel la deuxième couche diélectrique (5) de chaque cellule (C) mémoire résistive présente, à l'issue de l'étape d), une résistance électrique notée  $R_{\rm off}$ , de préférence comprise entre  $10^4$  et  $2.10^5$  ohms :

et dans lequel la première couche diélectrique (3) de l'empilement prévu lors de l'étape a) est adaptée pour présenter une résistance électrique strictement inférieure à  $R_{\rm off}$ , de préférence inférieure ou égale à  $R_{\rm off}$ /10.

- 5. Procédé selon l'une des revendications 1 à 4, dans lequel l'étape a) est exécutée de sorte que la deuxième couche diélectrique (5) est réalisée dans un oxyde d'hafnium; et le bombardement de l'étape b) est adapté de sorte que des espèces électriquement chargées s'accumulent aux première et deuxième interfaces (I<sub>1</sub>, I<sub>2</sub>) de chaque cellule (C) mémoire résistive, selon une densité surfacique de charge comprise entre 10<sup>13</sup> C par cm<sup>2</sup> et 5.10<sup>13</sup> C par cm<sup>2</sup>.

- **6.** Procédé selon l'une des revendications 1 à 5, dans lequel l'étape b) est exécutée par une technique de gravure choisie parmi :

- une gravure ionique réactive ;

- une gravure au plasma.

**DOCUMENTS CONSIDERES COMME PERTINENTS**

Citation du document avec indication, en cas de besoin,

US 2011/068312 A1 (SEKINE KATSUYUKI [JP]

US 2008/237693 A1 (LEE JANG-EUN [KR] ET

US 2011/210303 A1 (MURAOKA KOICHI [JP] ET

\* alinéas [0044] - [0078]; figures 5-11,

des parties pertinentes

ET AL) 24 mars 2011 (2011-03-24)

AL) 2 octobre 2008 (2008-10-02) \* alinéas [0023] - [0027], [0041], [0043] - [0047]; figures 1, 7-9 \*

AL) 1 septembre 2011 (2011-09-01)

[0096]; figures 3-8 \*

\* alinéas [0044] - [0067], [0087] -

Catégorie

A

A

A

### RAPPORT DE RECHERCHE EUROPEENNE

Numéro de la demande

EP 22 19 0897

CLASSEMENT DE LA DEMANDE (IPC)

DOMAINES TECHNIQUES RECHERCHES (IPC)

H01L G11C

Examinateur

Köpf, Christian

INV.

H10B63/00

H10N70/20

Revendication

1-6

1-6

| 1 | 0 |  |

|---|---|--|

|   |   |  |

15

20

25

30

35

40

45

50

1

(P04C02)

EPO FORM 1503 03.82

55

| Munich |  |

|--------|--|

|        |  |

I ieu de la recherche

- X : particulièrement pertinent à lui seul Y : particulièrement pertinent en combinaison avec un autre document de la même catégorie

CATEGORIE DES DOCUMENTS CITES

Le présent rapport a été établi pour toutes les revendications

- : arrière-plan technologique : divulgation non-écrite : document intercalaire

Date d'achèvement de la recherche

- T : théorie ou principe à la base de l'invention

- E : document de brevet antérieur, mais publié à la date de dépôt ou après cette date

D : cité dans la demande

L : cité pour d'autres raisons

- & : membre de la même famille, document correspondant

# EP 4 142 451 A1

# ANNEXE AU RAPPORT DE RECHERCHE EUROPEENNE RELATIF A LA DEMANDE DE BREVET EUROPEEN NO.

5

10

15

20

25

30

35

40

45

50

55

EP 22 19 0897

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités dans le rapport de recherche européenne visé ci-dessus.

Lesdits members sont contenus au fichier informatique de l'Office européen des brevets à la date du

Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets.

17-01-2023

| au | Occument brevet cité<br>rapport de recherche | e  | Date de publication |        | Membre(s) de la famille de brevet( |        | Date de<br>publication |

|----|----------------------------------------------|----|---------------------|--------|------------------------------------|--------|------------------------|

| US | s 2011068312                                 | A1 | 24-03-2011          | JP     | 2011066313                         |        | 31-03-2                |

|    |                                              |    |                     | KR     | 20110031091                        | A      | 24-03-2                |

|    |                                              |    |                     | US     | 2011068312                         | A1     | 24-03-2                |

| US | s 2008237693                                 | A1 | 02-10-2008          | JP     | 2008258616                         |        | 23-10-2                |

|    |                                              |    |                     | KR     | 20080088776                        |        | 06-10-2                |

|    |                                              |    |                     | TW     | 200849566                          |        | 16-12-2                |

|    |                                              |    |                     | US<br> | 2008237693                         | A1<br> | 02-10-2                |

| US | s 2011210303                                 | A1 | 01-09-2011          | JP     | 5531296                            |        | 25-06-2                |

|    |                                              |    |                     |        | WO2010026625                       |        | 26-01-2                |

|    |                                              |    |                     | TW     | 201021260                          |        | 01-06-2                |

|    |                                              |    |                     | US     | 2011210303                         |        | 01-09-2                |

|    |                                              |    |                     | WO     | 2010026625                         | A1     | 11-03-2                |

|    |                                              |    |                     |        |                                    |        |                        |

|    |                                              |    |                     |        |                                    |        |                        |

|    |                                              |    |                     |        |                                    |        |                        |

|    |                                              |    |                     |        |                                    |        |                        |

|    |                                              |    |                     |        |                                    |        |                        |

|    |                                              |    |                     |        |                                    |        |                        |

|    |                                              |    |                     |        |                                    |        |                        |

|    |                                              |    |                     |        |                                    |        |                        |

|    |                                              |    |                     |        |                                    |        |                        |

|    |                                              |    |                     |        |                                    |        |                        |

|    |                                              |    |                     |        |                                    |        |                        |

|    |                                              |    |                     |        |                                    |        |                        |

Pour tout renseignement concernant cette annexe : voir Journal Officiel de l'Office européen des brevets, No.12/82