Europäisches

Patentamt

European

Patent Office

Office européen

des brevets

(11)

EP 4 235 795 A1

(12)

## EUROPEAN PATENT APPLICATION

(43) Date of publication:

30.08.2023 Bulletin 2023/35

(21) Application number: 22199708.3

(22) Date of filing: 05.10.2022

(51) International Patent Classification (IPC):

**H01L 29/06** (2006.01)      **H01L 29/10** (2006.01)

**H01L 29/66** (2006.01)      **H01L 29/735** (2006.01)

**H01L 29/161** (2006.01)      **H01L 29/737** (2006.01)

(52) Cooperative Patent Classification (CPC):

**H01L 29/735; H01L 29/0657; H01L 29/1008;**

**H01L 29/161; H01L 29/6625; H01L 29/66242;**

**H01L 29/737**

(84) Designated Contracting States:

**AL AT BE BG CH CY CZ DE DK EE ES FI FR GB

GR HR HU IE IS IT LI LT LU LV MC ME MK MT NL

NO PL PT RO RS SE SI SK SM TR**

Designated Extension States:

**BA**

Designated Validation States:

**KH MA MD TN**

(30) Priority: 25.02.2022 US 202263313993 P

07.05.2022 US 202217739092

(71) Applicant: **GlobalFoundries U.S. Inc.**

**Malta, NY 12020 (US)**

(72) Inventors:

- **Malinowski, Arkadiusz**

**Malta, 12020 (US)**

- **Derrickson, Alexander**

**Malta, 12020 (US)**

- **Holt, Judson**

**Malta, 12020 (US)**

(74) Representative: **Grünecker Patent- und

Rechtsanwälte

PartG mbB**

**Leopoldstraße 4**

**80802 München (DE)**

### (54) LATERAL BIPOLAR JUNCTION TRANSISTORS INCLUDING A GRADED SILICON-GERMANIUM INTRINSIC BASE

(57) A structure for a lateral bipolar junction transistor, the structure comprising: a semiconductor substrate (10); a first terminal (16), for example a collector, including a first raised semiconductor layer (16) on the semiconductor substrate (10); a second terminal (18), for example an emitter, including a second raised semiconductor layer (18) on the semiconductor substrate (10); and an intrinsic base (12, 30, 28) on the semiconductor substrate, the intrinsic base positioned in a lateral direction between the first raised semiconductor layer (16) of the first terminal and the second raised semiconductor layer (18) of the second terminal. The intrinsic base includes a first portion (30) comprising silicon-germanium with a first germanium concentration that is graded in the lateral direction, a second region (12) with a substantially uniform low germanium concentration and a third region (28) with a substantially uniform high germanium content.

FIG. 7

## Description

### CROSS-REFERENCE TO RELATED APPLICATIONS

**[0001]** This application claims the benefit of U.S. Provisional Patent Application No. 63/313,993, filed February 25, 2022, which is hereby incorporated by reference herein in its entirety.

### BACKGROUND

**[0002]** This disclosure relates generally to semiconductor devices and integrated circuit fabrication and, in particular, to structures for a bipolar junction transistor and methods of forming a structure for a bipolar junction transistor.

**[0003]** A bipolar junction transistor is a multi-terminal electronic device that includes an emitter, a collector, and an intrinsic base arranged between the emitter and collector to define junctions. In a PNP bipolar junction transistor, the emitter and collector are comprised of p-type semiconductor material, and the intrinsic base is comprised of n-type semiconductor material. In an NPN bipolar junction transistor, the emitter and collector are comprised of n-type semiconductor material, and the intrinsic base is comprised of p-type semiconductor material. During operation, the base-emitter junction is forward biased, the base-collector junction is reverse biased, and the collector-emitter current may be controlled with the base-emitter voltage.

**[0004]** A heterojunction bipolar transistor is a variant of a bipolar junction transistor in which the semiconductor materials of the terminals have different energy band-gaps, which creates junctions that are heterojunctions. For example, the collector and emitter of a heterojunction bipolar transistor may be constituted by silicon, and the intrinsic base of a heterojunction bipolar transistor may be constituted by silicon-germanium, which is characterized by a narrower band gap than silicon.

**[0005]** Improved structures for a bipolar junction transistor and methods of forming a structure for a bipolar junction transistor are needed.

### SUMMARY

**[0006]** In an embodiment of the invention, a structure for a lateral bipolar junction transistor is provided. The structure comprises a first terminal including a first raised semiconductor layer on a semiconductor substrate, a second terminal including a second raised semiconductor layer on the semiconductor substrate, and an intrinsic base on the semiconductor substrate. The intrinsic base is positioned in a lateral direction between the first raised semiconductor layer of the first terminal and the second raised semiconductor layer of the second terminal. The intrinsic base includes a portion comprising silicon-germanium with a germanium concentration that is graded in the lateral direction.

**[0007]** In an embodiment of the invention, a method of forming a structure for a lateral bipolar junction transistor is provided. The method comprises forming a first terminal including a first raised semiconductor layer on a semiconductor substrate, forming a second terminal including a second raised semiconductor layer on the semiconductor substrate, and forming an intrinsic base on the semiconductor substrate that is positioned in a lateral direction between the first raised semiconductor layer of the first terminal and the second raised semiconductor layer of the second terminal. The intrinsic base includes a portion comprising silicon-germanium with a germanium concentration that is graded in the lateral direction.

### 15 BRIEF DESCRIPTION OF THE DRAWINGS

**[0008]** The accompanying drawings, which are incorporated in and constitute a part of this specification, illustrate various embodiments of the invention and, together with a general description of the invention given above and the detailed description of the embodiments given below, serve to explain the embodiments of the invention.

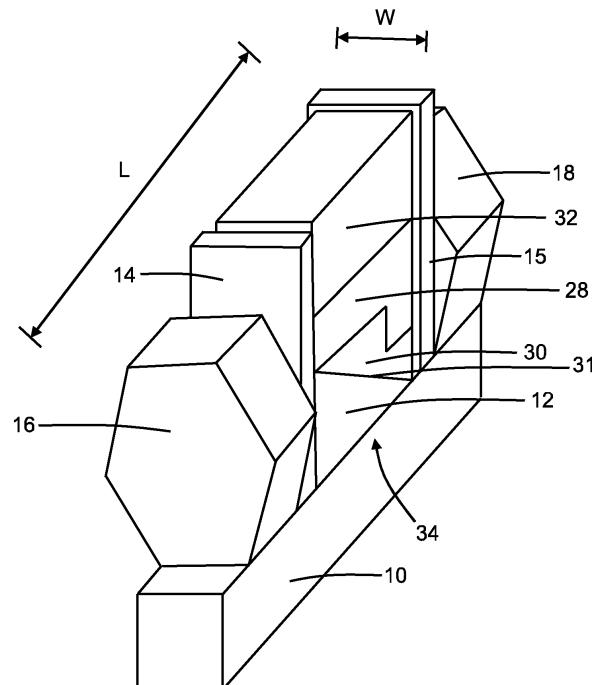

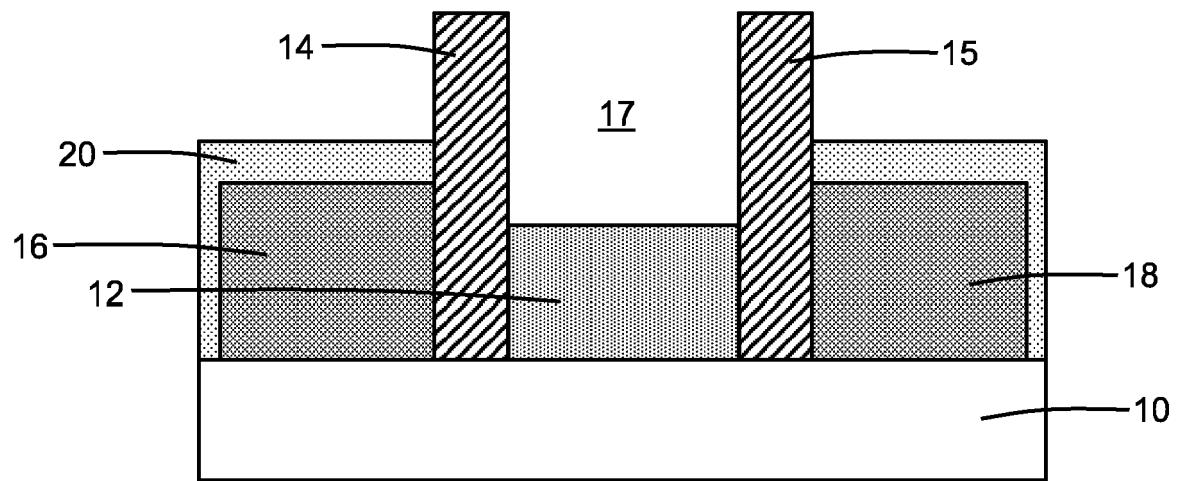

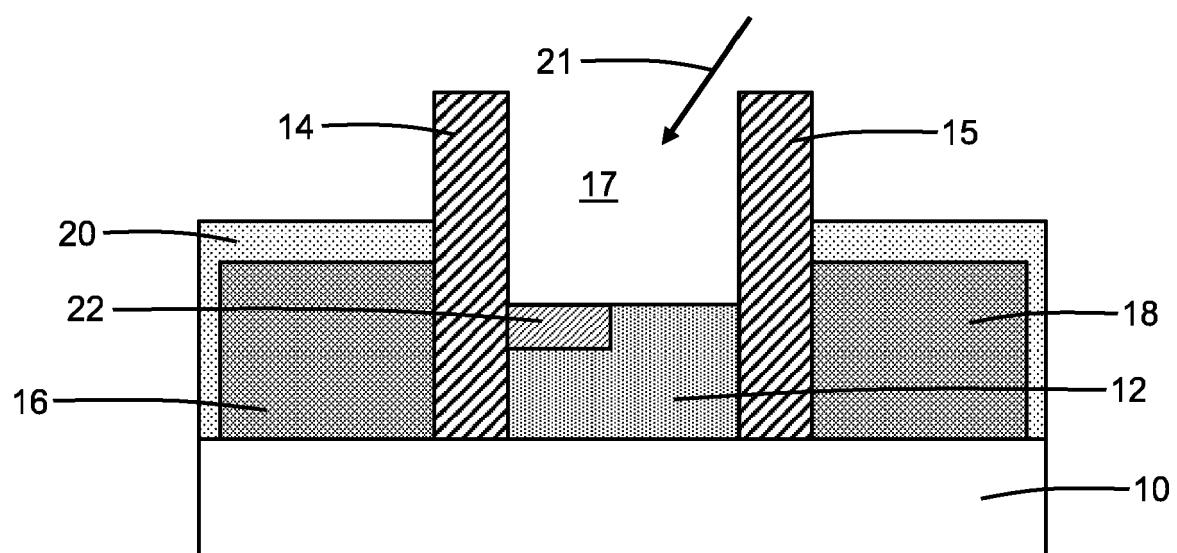

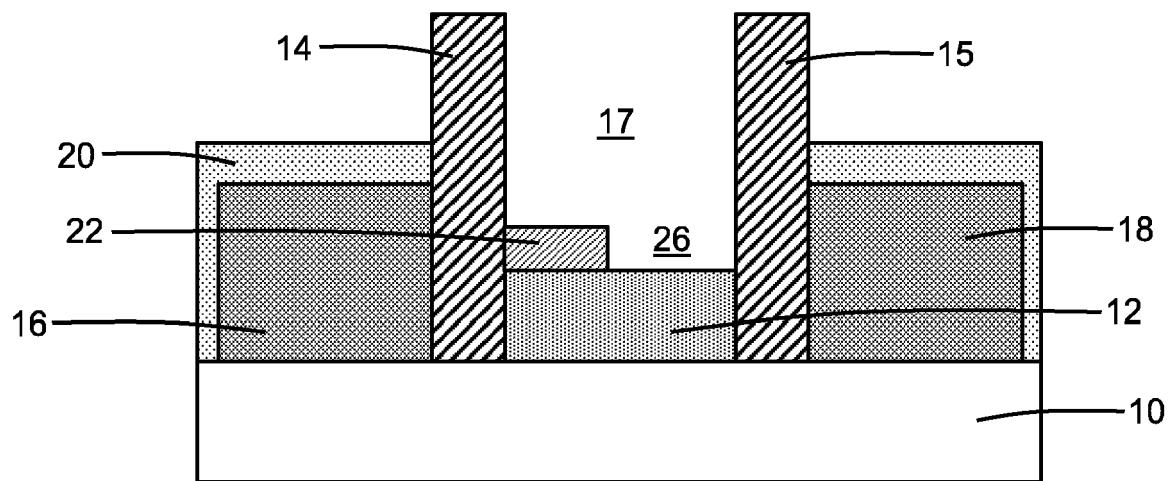

**25** FIGS. 1-6 are cross-sectional views of a structure at successive fabrication stages of a processing method in accordance with embodiments of the invention. FIG. 7 is a perspective view of a structure in accordance with alternative embodiments of the invention.

### 30 DETAILED DESCRIPTION

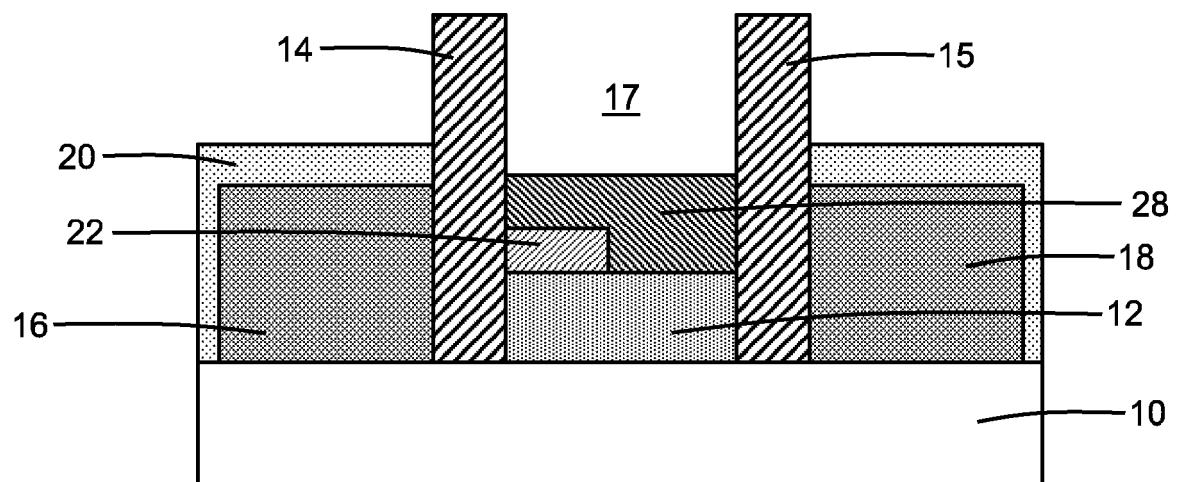

**[0009]** With reference to FIG. 1 and in accordance with embodiments of the invention, a semiconductor substrate 10 is comprised of a semiconductor material, such as single-crystal silicon. A semiconductor layer 12 may be formed by patterning the semiconductor substrate 10 with lithography and etching processes, or by patterning an epitaxially-grown layer. In an embodiment, the semiconductor layer 12 may be comprised of single-crystal silicon and lack germanium. In an embodiment, the semiconductor layer 12 may be comprised of single-crystal silicon-germanium that has a uniform germanium concentration. In an embodiment, the semiconductor layer 12 may be doped (e.g., lightly doped) with a concentration of a p-type dopant (e.g., boron) to provide p-type conductivity. The semiconductor layer 12 may provide a portion of an intrinsic base of the bipolar junction transistor.

**[0010]** Dielectric spacers 14, 15 may be formed at opposite sides of the semiconductor layer 12 by anisotropically etching a deposited conformal dielectric layer. The dielectric spacers 14, 15 may be comprised of a dielectric material, such as silicon nitride. The dielectric spacers 14, 15 project above a top surface of the semiconductor layer 12 as an artifact of the process used to form the semiconductor layer 12, and a cavity 17 exists above semiconductor layer 12 and laterally between the dielectric spacer 14 and the dielectric spacer 15.

**[0011]** Semiconductor layers 16, 18 are formed on the semiconductor substrate 10 adjacent to the opposite sides of the semiconductor layer 12. The semiconductor layers 16, 18 may provide terminals (i.e., an emitter and a collector) of the bipolar junction transistor. In an embodiment, the semiconductor layer 16 may provide an emitter, and the semiconductor layer 18 may provide a collector. In an alternative embodiment, the semiconductor layer 16 may provide a collector, and the semiconductor layer 18 may provide an emitter.

**[0012]** The semiconductor layers 16, 18 may be comprised of a semiconductor material, such as single-crystal silicon. The semiconductor layers 16, 18 may be doped (e.g., heavily doped) with a concentration of a dopant, such as an n-type dopant (e.g., phosphorus) to provide n-type conductivity. The semiconductor layers 16, 18 may be concurrently formed using an epitaxial growth process and may contain single-crystal semiconductor material (e.g., single-crystal silicon).

**[0013]** The dielectric spacer 14 is positioned in a lateral direction between the semiconductor layer 12 and the semiconductor layer 16. The dielectric spacer 15 is positioned in a lateral direction between the semiconductor layer 12 and the semiconductor layer 18. A dielectric layer 20 comprised of, for example, silicon nitride may be applied that coats the semiconductor layers 16, 18.

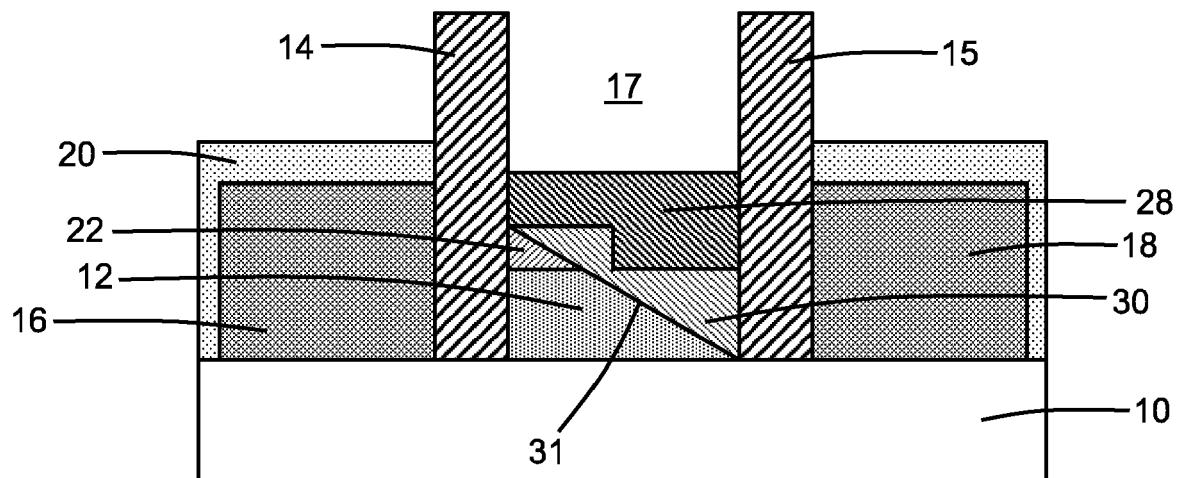

**[0014]** With reference to FIG. 2 in which like reference numerals refer to like features in FIG. 1 and at a subsequent fabrication stage, a tilted ion implantation is performed to implant ions, as diagrammatically shown by a single-headed arrow 21, into a section 22 of the semiconductor layer 12. The dielectric spacer 15 blocks the implantation of the ions 21 into another section of the semiconductor layer 12 (i.e., a non-implanted section that is adjacent to the section 22 and that is laterally between the section 22 and the dielectric spacer 15) due to shadowing of the surface area caused by the off-normal incidence of the ions 21 during ion implantation. The tilt angle relative to the surface normal is chosen to define the extent of the shadowing by the dielectric spacer 15 and the selectively-implanted volume forming the section 22. In an embodiment, the tilted ion implantation is performed with the semiconductor substrate 10 fixed in position.

**[0015]** An unimplanted section of the semiconductor layer 12 exists following the formation of the implanted section 22. In an embodiment, the implanted section 22 may extend from the top surface of the semiconductor layer 12 partially through the semiconductor layer 12. In an alternative embodiment, the implanted section 22 may extend from the top surface of the semiconductor layer 12 fully through the semiconductor layer 12. In an embodiment, the implanted section 22 may include a single atomic layer positioned proximate to the top surface of the semiconductor layer 12. In an embodiment, the implanted section 22 may be larger than the unimplanted section of the semiconductor layer 12. In an embodiment, the implanted section 22 may be smaller than the unimplanted section of the semiconductor layer 12. In an em-

bodiment, the implanted section 22 and the unimplanted section of the semiconductor layer 12 may have equal sizes.

**[0016]** The implanted section 22 of the semiconductor layer 12 is altered to facilitate a subsequent selective etching process in which the implanted section 22 of the semiconductor layer 12 has a significantly lower etch rate (i.e., a poisoned surface area). The implantation may change the crystalline structure of the implanted section 22 of the semiconductor layer 12 (e.g., amorphization) and/or change the material properties of the implanted section 22 of the semiconductor layer 12 from those of a semiconductor material to those of, or substantially similar to, a dielectric material. In the latter regard, the ions 21 implanted to form the implanted section 22 may be, or include, gallium, boron, or both elements, and may be performed using a single implantation or multiple implantations. In an embodiment, the concentration of implanted atoms in the implanted section 22 may be greater than or equal to  $1 \times 10^{19} \text{ cm}^{-3}$ .

**[0017]** With reference to FIG. 3 in which like reference numerals refer to like features in FIG. 2 and at a subsequent fabrication stage, a cavity 26 may be formed in the semiconductor layer 12 by a selective etching process that removes the semiconductor material of the unimplanted section of the semiconductor layer 12 selective to semiconductor material of the implanted section 22 of the semiconductor layer 12. As used herein, the terms "selective" and "selectivity" in reference to a material removal process (e.g., etching) denote that the material removal rate (i.e., etch rate) for the targeted material is higher than the material removal rate (i.e., etch rate) for at least another material exposed to the material removal process. In an embodiment, the cavity 26 may be formed using a wet chemical etching process that employs an etchant solution containing potassium hydroxide.

**[0018]** The etching process is controlled such that the cavity 26 only penetrates partially through the unimplanted section of the semiconductor layer 12 in a vertical direction. The cavity 26 is laterally offset from a vertical centerline of the semiconductor layer 12 and defines an open space in conjunction with the cavity 17. The implanted section 22 of the semiconductor layer 12, which is modified by the implanted ions 21, functions as an etch stop such that the cavity 26 is positioned in a lateral direction between the implanted section 22 and the dielectric spacer 15.

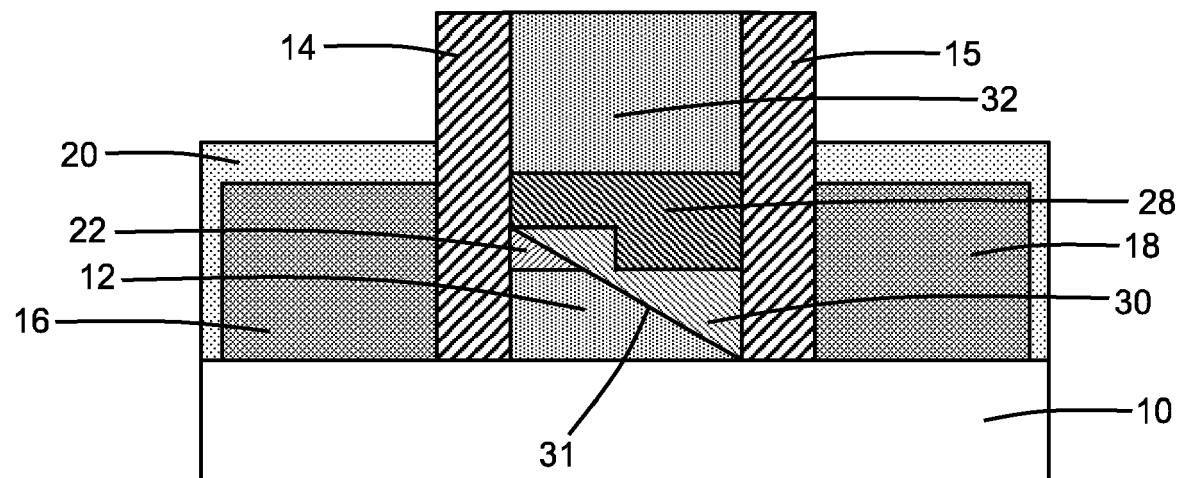

**[0019]** With reference to FIG. 4 in which like reference numerals refer to like features in FIG. 3 and at a subsequent fabrication stage, a semiconductor layer 28 is formed within the cavity 26 adjacent to the implanted section 22 of the semiconductor layer 12, as well within the cavity 17 over the semiconductor layer 12. The semiconductor layer 28 may be comprised of a single-crystal semiconductor material that is epitaxially grown from the exposed surfaces of the semiconductor layer 12. The semiconductor layer 28 includes a portion inside the cavity 17 and a portion inside the cavity 26. In an embodiment,

the semiconductor layer 28 may be comprised of silicon-germanium including silicon and germanium with the silicon content ranging from 95 atomic percent to 50 atomic percent and the germanium content ranging from 5 atomic percent to 50 atomic percent. In an embodiment, the germanium content of the semiconductor layer 28 may be uniform or substantially uniform over its volume. The semiconductor layer 28 may be in situ doped during epitaxial growth with a concentration of a dopant, such as a p-type dopant (e.g., boron) that provides p-type conductivity. In an embodiment, the semiconductor layer 28 may be uniformly doped during epitaxial growth. The semiconductor layer 28, which provides a contribution to the intrinsic base of the bipolar junction transistor, directly contacts the adjacent sections (including the implanted section 22) of the semiconductor layer 12.

**[0020]** With reference to FIG. 5 in which like reference numerals refer to like features in FIG. 4 and at a subsequent fabrication stage, a thermal process, such as a rapid thermal anneal, is used to cause germanium to diffuse outwardly from the semiconductor layer 28 into a portion 30 of the semiconductor layer 12. The portion 30 may include all or part of the implanted section 22. The diffusion of germanium into the portion 30 of the semiconductor layer 12 may occur in a lateral direction and in a vertical direction. The offset positioning of the portion of the semiconductor layer 28 inside the cavity 26 adjacent to the semiconductor layer 18 results in an asymmetrical profile for the germanium that is laterally and vertically diffused into the portion 30 of the semiconductor layer 12. The thermal process may be controlled such that germanium does not diffuse into a portion of the semiconductor layer 12 that is positioned between the portion 30 and the semiconductor substrate 10. The portion of the semiconductor layer 12 that lacks diffused germanium is positioned adjacent to the semiconductor substrate 10.

**[0021]** An interface 31 is defined between the portion 30 of the semiconductor layer 12 that includes diffused germanium and the portion of the semiconductor layer 12 that lacks diffused germanium. Although the interface 31 is diagrammatically shown as inclined in FIG. 5, the interface 31 may have a different shape, such as a shape with a degree of curvature or an irregular shape. At and along the interface 31, the germanium concentration in the portion 30 of the semiconductor layer 12 has a minimum value and transitions from the germanium concentration in the portion 30 to the germanium concentration, if any, in the portion of the semiconductor layer 12 that lacks diffused germanium. The portion 30 of the semiconductor layer 12 with the multi-directional germanium gradient may extend in a lateral direction from the dielectric spacer 14 to the dielectric spacer 15.

**[0022]** The germanium concentration in the portion 30 of the semiconductor layer 12 is graded in a lateral direction and is also graded in a vertical direction. In that regard, the germanium concentration in the portion 30 may decrease with increasing distance from the semi-

conductor layer 28 in a lateral direction, and the germanium concentration in the portion 30 may decrease with increasing distance from the semiconductor layer 28 in a vertical direction. In an embodiment, the germanium concentration in the portion 30 may exhibit a 50 percent decrease per 10 nanometers of distance in a direction from the semiconductor layer 28 toward the interface 31. In an embodiment in which the semiconductor layer 12 is initially comprised of silicon and lacks germanium, the graded germanium profile in the portion 30 of the semiconductor layer 12 may exhibit a maximum concentration adjacent to the semiconductor layer 18 (e.g., the collector) and a minimum concentration (e.g., 0 atomic percent) at the interface 31, which is adjacent to the semiconductor layer 16 (e.g., the emitter). In an embodiment in which the semiconductor layer 12 is initially comprised of silicon-germanium with a uniform or substantially uniform germanium concentration, the minimum germanium concentration at the interface 31 may be equal to the germanium concentration in the portion of semiconductor layer 12 that lacks diffused germanium. The germanium concentration in the semiconductor layer 28, following the thermal process, may be uniform or substantially uniform and greater than or equal to the maximum germanium concentration in the portion 30 of the semiconductor layer 12.

**[0023]** With reference to FIG. 6 in which like reference numerals refer to like features in FIG. 5 and at a subsequent fabrication stage, a semiconductor layer 32 is formed over the semiconductor layer 28. In an embodiment, the semiconductor layer 32 may be positioned fully above the semiconductor layer 28 of the intrinsic base such that the intrinsic base is positioned in a vertical direction between the semiconductor layer 32 and the semiconductor substrate 10. The semiconductor layer 32 may be comprised of a heavily-doped semiconductor material, such as polysilicon that is heavily doped with a concentration of a p-type dopant (e.g., boron) to provide p-type conductivity. The semiconductor layer 32 may provide an extrinsic base of the bipolar junction transistor.

**[0024]** The resultant structure is a lateral bipolar junction transistor that includes a laterallyarranged emitter, base, and collector. The semiconductor layers 16, 18 constitute the emitter and collector of the lateral bipolar junction transistor. The portion 30 of the semiconductor layer 12, the portion of the semiconductor layer 12 that lacks diffused germanium, and the semiconductor layer 28 may provide different portions of an intrinsic base of the lateral bipolar junction transistor. The germanium concentration in the portion 30 of the semiconductor layer 12 is graded in a lateral direction between the semiconductor layer 28 and the interface 31, and is also graded in a vertical direction between the semiconductor layer 28 and the interface 31. In the representative embodiment, the semiconductor layers 16, 18 may contain an n-type dopant, and the semiconductor layers 12, 28, 32 may contain a p-type dopant. In an alternative embodiment, the semiconductor layers 16, 18 may contain a p-

type dopant, and the semiconductor layers 12, 28, 32 may contain an n-type dopant.

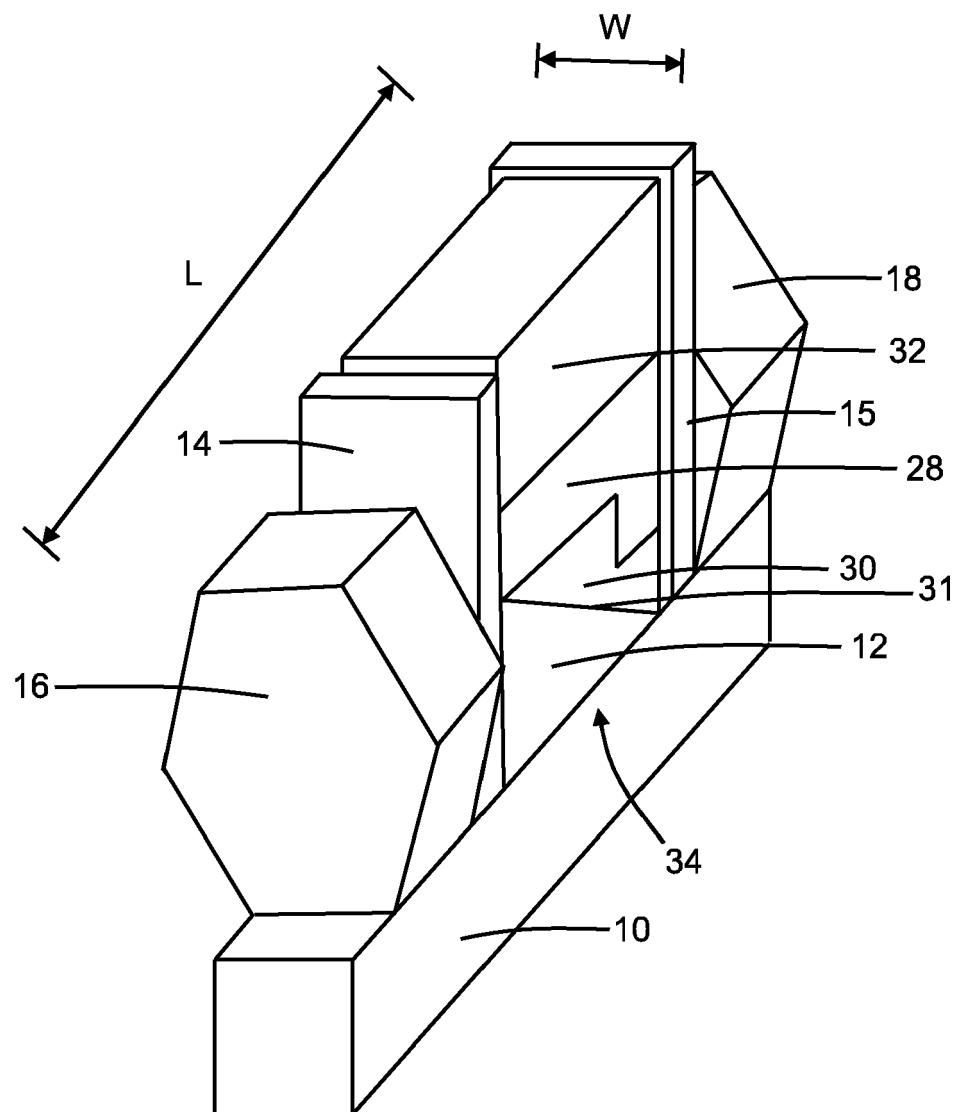

**[0025]** With reference to FIG. 7 in which like reference numerals refer to like features in FIG. 6 and in accordance with alternative embodiments, the semiconductor layer 12 and the semiconductor layer 28 may constitute a fin structure 34 projecting in a vertical direction from the semiconductor substrate 10. The fin structure 34 has a width W and a length L that is greater than the width. The lateral grading of the germanium concentration in portion 30 of the semiconductor layer 12 may extend in a direction along the length of the fin structure 34. In an embodiment, the semiconductor layers 16, 18 may have a faceted shape.

**[0026]** The methods as described above are used in the fabrication of integrated circuit chips. The resulting integrated circuit chips can be distributed by the fabricator in raw wafer form (e.g., as a single wafer that has multiple unpackaged chips), as a bare die, or in a packaged form. The chip may be integrated with other chips, discrete circuit elements, and/or other signal processing devices as part of either an intermediate product or an end product. The end product can be any product that includes integrated circuit chips, such as computer products having a central processor or smartphones.

**[0027]** References herein to terms modified by language of approximation, such as "about", "approximately", and "substantially", are not to be limited to the precise value specified. The language of approximation may correspond to the precision of an instrument used to measure the value and, unless otherwise dependent on the precision of the instrument, may indicate a range of +/- 10% of the stated value(s).

**[0028]** References herein to terms such as "vertical", "horizontal", etc. are made by way of example, and not by way of limitation, to establish a frame of reference. The term "horizontal" as used herein is defined as a plane parallel to a conventional plane of a semiconductor substrate, regardless of its actual three-dimensional spatial orientation. The terms "vertical" and "normal" refer to a direction perpendicular to the horizontal, as just defined. The term "lateral" refers to a direction within the horizontal plane.

**[0029]** A feature "connected" or "coupled" to or with another feature may be directly connected or coupled to or with the other feature or, instead, one or more intervening features may be present. A feature may be "directly connected" or "directly coupled" to or with another feature if intervening features are absent. A feature may be "indirectly connected" or "indirectly coupled" to or with another feature if at least one intervening feature is present. A feature "on" or "contacting" another feature may be directly on or in direct contact with the other feature or, instead, one or more intervening features may be present. A feature may be "directly on" or in "direct contact" with another feature if intervening features are absent. A feature may be "indirectly on" or in "indirect contact" with another feature if at least one intervening

feature is present. Different features may "overlap" if a feature extends over, and covers a part of, another feature with either direct contact or indirect contact.

**[0030]** The descriptions of the various embodiments of the present invention have been presented for purposes of illustration but are not intended to be exhaustive or limited to the embodiments disclosed. Many modifications and variations will be apparent to those of ordinary skill in the art without departing from the scope and spirit of the described embodiments. The terminology used herein was chosen to best explain the principles of the embodiments, the practical application or technical improvement over technologies found in the marketplace, or to enable others of ordinary skill in the art to understand the embodiments disclosed herein.

**[0031]** The following embodiments are explicitly disclosed:

Embodiment 1:

**[0032]** A structure for a lateral bipolar junction transistor, the structure comprising:

25 a semiconductor substrate;

a first terminal including a first raised semiconductor layer on the semiconductor substrate;

a second terminal including a second raised semiconductor layer on the semiconductor substrate; and an intrinsic base on the semiconductor substrate, the intrinsic base positioned in a lateral direction between the first raised semiconductor layer of the first terminal and the second raised semiconductor layer of the second terminal, and the intrinsic base including a first portion comprising silicon-germanium with a first germanium concentration that is graded in the lateral direction.

Embodiment 2:

**[0033]** The structure of embodiment 1 wherein the first germanium concentration in the first portion of the intrinsic base is graded in a vertical direction relative to the semiconductor substrate.

45 Embodiment 3:

**[0034]** The structure of embodiment 1 or 2 wherein the intrinsic base is a fin structure projecting in a vertical direction from the semiconductor substrate.

50 Embodiment 4:

**[0035]** The structure of embodiment 3 wherein the fin structure has a length and a width, and the grading of the first germanium concentration in the first portion of the intrinsic base extends along the length of the fin structure.

## Embodiment 5:

**[0036]** The structure of one of embodiments 1 to 4 further comprising:

5 a first dielectric spacer positioned in the lateral direction between the first raised semiconductor layer and the intrinsic base; and

a second dielectric spacer positioned in the lateral direction between the second raised semiconductor layer and the intrinsic base,

wherein the first portion of the intrinsic base extends from the first dielectric spacer to the second dielectric spacer.

## Embodiment 6:

**[0037]** The structure of one of embodiments 1 to 5 wherein the first germanium concentration in the first portion of the intrinsic base decreases in a direction from the first raised semiconductor layer to the second raised semiconductor layer.

## Embodiment 7:

**[0038]** The structure of embodiment 6 wherein the first terminal is an emitter of the lateral bipolar junction transistor, and the second terminal is a collector of the lateral bipolar junction transistor.

## Embodiment 8:

**[0039]** The structure of one of embodiments 1 to 7 wherein the intrinsic base includes a second portion positioned in a vertical direction adjacent to the semiconductor substrate.

## Embodiment 9:

**[0040]** The structure of embodiment 8 wherein the intrinsic base includes a third portion comprising silicon-germanium with a second germanium concentration that is greater than a maximum value of the first germanium concentration, and the first portion of the intrinsic base is positioned in the vertical direction between the third portion of the intrinsic base and the second portion of the intrinsic base.

## Embodiment 10:

**[0041]** The structure of embodiment 9 further comprising:

an extrinsic base on the third portion of the intrinsic base, the extrinsic base comprising a heavily-doped semiconductor material.

## Embodiment 11:

**[0042]** The structure of embodiment 8 or 9 wherein the second portion of the intrinsic base comprises silicon-germanium with a second germanium concentration that is substantially uniform and that is less than a minimum value of the first germanium concentration.

## Embodiment 12:

**[0043]** The structure of one of embodiments 8 to 11 to wherein the second portion of the intrinsic base comprises silicon and lacks a germanium concentration.

## 15 Embodiment 13:

**[0044]** The structure of one of embodiments 8 to 13 wherein the first portion of the intrinsic base and the second portion of the intrinsic base adjoin along an interface, and the first germanium concentration has a minimum value at the interface.

## Embodiment 14:

**[0045]** A method of forming a structure for a lateral bipolar junction transistor, the method comprising: forming a first terminal including a first raised semiconductor layer on a semiconductor substrate;

30 forming a second terminal including a second raised semiconductor layer on the semiconductor substrate; and

forming an intrinsic base on the semiconductor substrate that is positioned in a lateral direction between the first raised semiconductor layer of the first terminal and the second raised semiconductor layer of the second terminal,

wherein the intrinsic base includes a first portion comprising silicon-germanium with a first germanium concentration that is graded in the lateral direction.

## Embodiment 15:

**[0046]** The method of embodiment 14 wherein the first germanium concentration in the first portion of the intrinsic base is graded in a vertical direction relative to the semiconductor substrate.

## 50 Embodiment 16:

**[0047]** The method of embodiment 14 or 15 wherein forming the intrinsic base on the semiconductor substrate that is positioned in the lateral direction between the first raised semiconductor layer of the first terminal and the second raised semiconductor layer of the second terminal comprises:

depositing a first layer comprised of a first semiconductor material;

implanting a first section of the first layer; and

removing a second section of the first layer that is adjacent to the first section to define a cavity.

Embodiment 17:

**[0048]** The method of embodiment 16 wherein implanting the first section of the first layer comprises: performing a tilted implantation of boron or gallium into the first section of the first layer.

Embodiment 18:

**[0049]** The method of embodiment 17 wherein removing the second section of the first layer that is adjacent to the first section to define the cavity comprises: performing a wet chemical etching process using an etchant comprising potassium hydroxide.

Embodiment 19:

**[0050]** The method of one of embodiments 16 to 18 further comprising:

depositing a second layer comprised of a second semiconductor material containing a concentration of germanium, wherein the second layer includes a portion inside the cavity; and

performing a thermal process to cause the germanium to diffuse in the lateral direction from the second layer into the first layer.

Embodiment 20:

**[0051]** The method of embodiment 19 wherein the thermal process causes the germanium to diffuse in a vertical direction from the second layer into the first layer.

## Claims

1. A structure for a lateral bipolar junction transistor, the structure comprising:

a semiconductor substrate;

a first terminal including a first raised semiconductor layer on the semiconductor substrate;

a second terminal including a second raised semiconductor layer on the semiconductor substrate; and

an intrinsic base on the semiconductor substrate, the intrinsic base positioned in a lateral direction between the first raised semiconductor layer of the first terminal and the second raised semiconductor layer of the second terminal, and the intrinsic base including a first portion com-

prising silicon-germanium with a first germanium concentration that is graded in the lateral direction.

- 5     2. The structure of claim 1, wherein the first germanium concentration in the first portion of the intrinsic base is graded in a vertical direction relative to the semiconductor substrate.

- 10    3. The structure of claim 1 or 2, wherein the intrinsic base is a fin structure projecting in a vertical direction from the semiconductor substrate, wherein the fin structure preferably has a length and a width, and wherein the grading of the first germanium concentration in the first portion of the intrinsic base preferably extends along the length of the fin structure.

- 15    4. The structure of one of claims 1 to 3, further comprising:

20           a first dielectric spacer positioned in the lateral direction between the first raised semiconductor layer and the intrinsic base: and

a second dielectric spacer positioned in the lateral direction between the second raised semiconductor layer and the intrinsic base,

wherein the first portion of the intrinsic base extends from the first dielectric spacer to the second dielectric spacer.

- 25    5. The structure of one of claims 1 to 4, wherein the first germanium concentration in the first portion of the intrinsic base decreases in a direction from the first raised semiconductor layer to the second raised semiconductor layer.

- 30    6. The structure of one of claims 1 to 5, wherein the first terminal is an emitter of the lateral bipolar junction transistor, and the second terminal is a collector of the lateral bipolar junction transistor.

- 35    7. The structure of one of claims 1 to 6, wherein the intrinsic base includes a second portion positioned in a vertical direction adjacent to the semiconductor substrate.

- 40    8. The structure of claim 7, wherein the intrinsic base includes a third portion comprising silicon-germanium with a second germanium concentration that is greater than a maximum value of the first germanium concentration, and the first portion of the intrinsic base is positioned in the vertical direction between the third portion of the intrinsic base and the second portion of the intrinsic base.

- 45    9. The structure of claim 8 further comprising:

50           an extrinsic base on the third portion of the intrinsic base, the extrinsic base comprising a heavily-doped

semiconductor material.

10. The structure of one of claims 7 to 9, wherein the second portion of the intrinsic base comprises silicon-germanium with a second germanium concentration that is substantially uniform and that is less than a minimum value of the first germanium concentration, and/or wherein the second portion of the intrinsic base comprises silicon and lacks a germanium concentration, and/or wherein the first portion of the intrinsic base and the second portion of the intrinsic base adjoin along an interface, and the first germanium concentration has a minimum value at the interface.

11. A method of forming a structure for a lateral bipolar junction transistor, the method comprising:

forming a first terminal including a first raised semiconductor layer on a semiconductor substrate; 20

forming a second terminal including a second raised semiconductor layer on the semiconductor substrate; and

forming an intrinsic base on the semiconductor substrate that is positioned in a lateral direction between the first raised semiconductor layer of the first terminal and the second raised semiconductor layer of the second terminal, 25

wherein the intrinsic base includes a first portion comprising silicon-germanium with a first germanium concentration that is graded in the lateral direction.

12. The method of claim 11, wherein the first germanium concentration in the first portion of the intrinsic base is graded in a vertical direction relative to the semiconductor substrate. 35

13. The method of claim 11 or 12, wherein forming the intrinsic base on the semiconductor substrate that is positioned in the lateral direction between the first raised semiconductor layer of the first terminal and the second raised semiconductor layer of the second terminal comprises: 40

45

depositing a first layer comprised of a first semiconductor material;

implanting a first section of the first layer; and

removing a second section of the first layer that 50

is adjacent to the first section to define a cavity.

14. The method of claim 13, wherein implanting the first section of the first layer comprises:

performing a tilted implantation of boron or gallium 55

into the first section of the first layer, wherein removing the second section of the first layer that is adjacent to the first section to define the cavity preferably

comprises performing a wet chemical etching process using an etchant comprising potassium hydroxide.

- 5 15. The method of claim 13 or 14, further comprising:

10

15

depositing a second layer comprised of a second semiconductor material containing a concentration of germanium, wherein the second layer includes a portion inside the cavity; and

performing a thermal process to cause the germanium to diffuse in the lateral direction from the second layer into the first layer, wherein the thermal process preferably causes the germanium to diffuse in a vertical direction from the second layer into the first layer.

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

## EUROPEAN SEARCH REPORT

Application Number

EP 22 19 9708

5

| DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                          |                                                                                                                                                                                 |                                                  |                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------|

| Category                                                                                                                                                                                                                                                                     | Citation of document with indication, where appropriate, of relevant passages                                                                                                   | Relevant to claim                                | CLASSIFICATION OF THE APPLICATION (IPC)                   |

| 10                                                                                                                                                                                                                                                                           | X EP 1 094 523 A2 (MATSUSHITA ELECTRIC IND CO LTD [JP]) 25 April 2001 (2001-04-25)<br>* Figs. 1-6, 10, 11 and corresponding text passages. *<br>-----                           | 1, 3-7, 10, 11                                   | INV.<br>H01L29/06<br>H01L29/10<br>H01L29/66<br>H01L29/735 |

| 15                                                                                                                                                                                                                                                                           | X US 2015/263091 A1 (HASHEMI POUYA [US] ET AL) 17 September 2015 (2015-09-17)<br>* Figs. 1A, 1B, 4, 9 and corresponding text passages. *<br>-----                               | 1, 3-5, 11                                       | H01L29/161<br>ADD.<br>H01L29/737                          |

| 20                                                                                                                                                                                                                                                                           | X US 2021/091212 A1 (HOLT JUDSON [US] ET AL) 25 March 2021 (2021-03-25)<br>* Figs. 4, 7 and corresponding text passages. *<br>-----                                             | 1, 2, 4, 5, 11, 12                               |                                                           |

| 25                                                                                                                                                                                                                                                                           | A US 8 288 758 B2 (NING TAK H [US]; CHAN KEVIN K [US]; KHATER MARWAN H [US]; IBM [US]) 16 October 2012 (2012-10-16)<br>* Figs. 7-11 and corresponding text passages. *<br>----- | 7-10, 13-15                                      |                                                           |

| 30                                                                                                                                                                                                                                                                           | A US 9 647 099 B2 (IBM [US]) 9 May 2017 (2017-05-09)<br>* Figs. 1, 9 and corresponding text passages. *<br>-----                                                                | 7-10, 13-15                                      | TECHNICAL FIELDS<br>SEARCHED (IPC)<br>H01L                |

| 35                                                                                                                                                                                                                                                                           | A US 2018/277666 A1 (CHU CHUNG-HAO [TW] ET AL) 27 September 2018 (2018-09-27)<br>* Figs. 1-4 and corresponding text passages. *<br>-----                                        | 1-15                                             |                                                           |

| 40                                                                                                                                                                                                                                                                           |                                                                                                                                                                                 |                                                  |                                                           |

| 45                                                                                                                                                                                                                                                                           |                                                                                                                                                                                 |                                                  |                                                           |

| 50                                                                                                                                                                                                                                                                           | 3 The present search report has been drawn up for all claims                                                                                                                    |                                                  |                                                           |

| 55                                                                                                                                                                                                                                                                           | Place of search<br>Munich                                                                                                                                                       | Date of completion of the search<br>17 July 2023 | Examiner<br>Dauw, Xavier                                  |

| CATEGORY OF CITED DOCUMENTS                                                                                                                                                                                                                                                  |                                                                                                                                                                                 |                                                  |                                                           |

| X : particularly relevant if taken alone<br>Y : particularly relevant if combined with another document of the same category<br>A : technological background<br>O : non-written disclosure<br>P : intermediate document                                                      |                                                                                                                                                                                 |                                                  |                                                           |

| T : theory or principle underlying the invention<br>E : earlier patent document, but published on, or after the filing date<br>D : document cited in the application<br>L : document cited for other reasons<br>& : member of the same patent family, corresponding document |                                                                                                                                                                                 |                                                  |                                                           |

ANNEX TO THE EUROPEAN SEARCH REPORT

ON EUROPEAN PATENT APPLICATION NO.

EP 22 19 9708

5 This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

17-07-2023

| 10 | Patent document cited in search report | Publication date  |                                                                      | Patent family member(s)                                           | Publication date |

|----|----------------------------------------|-------------------|----------------------------------------------------------------------|-------------------------------------------------------------------|------------------|

| 15 | EP 1094523 A2 25-04-2001               | CN EP KR TW US US | 1294414 A 1094523 A2 20010051176 A 493278 B 6563146 B1 2003054601 A1 | 09-05-2001 25-04-2001 25-06-2001 01-07-2002 13-05-2003 20-03-2003 |                  |

| 20 | US 2015263091 A1 17-09-2015            |                   | NONE                                                                 |                                                                   |                  |

| 25 | US 2021091212 A1 25-03-2021            |                   | NONE                                                                 |                                                                   |                  |

| 30 | US 8288758 B2 16-10-2012               | US US             | 2012139009 A1 2012289018 A1                                          | 07-06-2012 15-11-2012                                             |                  |

| 35 | US 9647099 B2 09-05-2017               | US US             | 2016300934 A1 2016300935 A1                                          | 13-10-2016 13-10-2016                                             |                  |

| 40 | US 2018277666 A1 27-09-2018            |                   | NONE                                                                 |                                                                   |                  |

| 45 |                                        |                   |                                                                      |                                                                   |                  |

| 50 |                                        |                   |                                                                      |                                                                   |                  |

| 55 |                                        |                   |                                                                      |                                                                   |                  |

EPO FORM P0459

For more details about this annex : see Official Journal of the European Patent Office, No. 12/82

**REFERENCES CITED IN THE DESCRIPTION**

*This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.*

**Patent documents cited in the description**

- US 63313993 [0001]