#### (12)

# **EUROPEAN PATENT APPLICATION**

published in accordance with Art. 153(4) EPC

(43) Date of publication: 15.11.2023 Bulletin 2023/46

(21) Application number: 22912974.7

(22) Date of filing: 08.03.2022

- (51) International Patent Classification (IPC): G11C 7/06 (2006.01) G11C 7/08 (2006.01) G11C 11/4091 (2006.01)

- (52) Cooperative Patent Classification (CPC): G11C 7/065; G11C 7/02; G11C 7/06; G11C 7/08; G11C 11/4074; G11C 11/4091; G11C 11/4094; G11C 5/147; G11C 2207/2227; Y02D 30/70

- (86) International application number: **PCT/CN2022/079726**

- (87) International publication number: WO 2023/123668 (06.07.2023 Gazette 2023/27)

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

**Designated Extension States:**

**BA ME**

**Designated Validation States:**

KH MA MD TN

(30) Priority: 31.12.2021 CN 202111657770

- (71) Applicant: Changxin Memory Technologies, Inc. Hefei, Anhui 230601 (CN)

- (72) Inventor: SHANG, Weibing Hefei, Anhui 230601 (CN)

- (74) Representative: Klunker IP Patentanwälte PartG mbB Destouchesstraße 68 80796 München (DE)

# (54) CONTROL AMPLIFICATION CIRCUIT, SENSE AMPLIFIER AND SEMICONDUCTOR MEMORY

(57) Disclosed are a control amplifying circuit, a sense amplifier and a semiconductor memory. The control amplifying circuit includes a power supply output circuit, an isolation control circuit and an amplifying circuit. The power supply output circuit is configured to receive a power supply switching signal, and select one preset voltage value from at least two preset voltage values according to the power supply switching signal to output as

a preset power supply signal. The isolation control circuit is configured to receive a control command signal and the preset power supply signal, and generate an isolation control signal according to the control command signal. The amplifying circuit is configured to receive the isolation control signal and a signal to be processed, and amplify the signal to be processed based on the isolation control signal to obtain a target amplified signal.

FIG. 2

30

40

45

50

#### Description

#### CROSS-REFERENCE TO RELEVANT APPLICATION

1

[0001] The present disclosure is based on and claims priority to Chinese patent application No. 202111657770.X, filed on December 31, 2021 and entitled "CONTROL AMPLIFYING CIRCUIT, SENSE AMPLIFIER AND SEMICONDUCTOR MEMORY", the disclosures of which are hereby incorporated by reference in its entirety.

#### **TECHNICAL FIELD**

**[0002]** The present disclosure relates to the technical field of semiconductor memory, and more particularly, to a control amplifying circuit, a sense amplifier and a semiconductor memory.

#### **BACKGROUND**

**[0003]** Dynamic Random Access Memory (DRAM) is a semiconductor memory device commonly used in computers and consists of many repeating memory cells. In a process of data reading, a readout data signal of each memory cell is read out via a local data line, a global data line and a data bus in turn; and conversely, in a process of data writing, a write data signal is sequentially written into the memory cell via the data bus, the global data line, and the local data line.

**[0004]** At present, the DRAM includes a sense amplifier for signal amplification processing, but in the related art, the sense amplifier has a slow amplification speed and readily produce noise.

#### SUMMARY

[0005] The present disclosure provides a control amplifying circuit, a sense amplifier and a semiconductor memory, which can improve the problems that the signal amplification speed is slow and noise is easily generated.

[0006] According to a first aspect, the embodiments of the present disclosure provide a control amplifying circuit, which includes a power supply output circuit, an isolation control circuit and an amplifying circuit.

**[0007]** The power supply output circuit is configured to receive a power supply switching signal, and select one of at least two preset voltage values according to the power supply switching signal to output as a preset power supply signal.

**[0008]** The isolation control circuit is configured to receive a control command signal and the preset power supply signal, and generate an isolation control signal according to the control command signal.

**[0009]** The amplifying circuit is configured to receive the isolation control signal and a signal to be processed, and amplify the signal to be processed based on the isolation control signal to obtain a target amplified signal.

**[0010]** In some embodiments, the power supply switching signal includes a first power supply switching signal and/or a second power supply switching signal. The control amplifying circuit further includes a power supply switching circuit, configured to output the first power supply switching signal and/or the second power supply switching signal. The power supply output circuit is specifically configured to receive the first power supply switching signal and/or the second power supply switching signal, and select one of the at least two preset voltage values according to the first power supply switching signal and/or the second power supply switching signal and/or the second power supply switching signal to output as the preset power supply signal.

[0011] In some embodiments, the preset voltage values include a first voltage value and a second voltage value. The power supply output circuit is further configured to select the first voltage value to output as the preset power supply signal when the first power supply switching signal is in a first level state and the second power supply switching signal is in a second level state; or select the second voltage value to output as the preset power supply signal when the first power supply switching signal is in the second power supply switching signal is in the second power supply switching signal is in the first level state. The first voltage value and the second voltage value both belong to the second level state, and the first voltage value is greater than the second voltage value.

[0012] In some embodiments, a signal control circuit is configured to output the control command signal. The isolation control circuit is further configured to generate an isolation control signal with a third voltage value when the control command signal is in a first state, or, generate an isolation control signal with a same voltage value as the preset power supply signal when the control command signal is in a second state. The first state is a first level state or a second level state, the second state is the first level state or the second level state, level states of the first state and the second state are different, and the third voltage value belongs to the first level state and is less than the second voltage value.

[0013] In some embodiments, the power supply output circuit includes a first preset power supply, a second preset power supply, a first switching transistor and a second switching transistor. A first end of the first switching transistor is connected with the first power supply switching signal, and a first end of the second switching transistor is connected with the second power supply switching signal. A second end of the first switching transistor is connected with the first preset power supply, and a second end of the second switching transistor is connected with the second preset power supply. A third end of the first switching transistor is connected with a third end of the second switching transistor for outputting the preset power supply signal. The first preset power supply is configured to output the first voltage value, and the second preset power supply is configured to output the second

[0014] In some embodiments, the isolation control cir-

30

45

cuit includes a first inverter, a third switching transistor and a fourth switching transistor. An input end of the first inverter is connected with the control command signal, and an output end of the first inverter is respectively connected with a first end of the third switching transistor and a first end of the fourth switching transistor. A second end of the third switching transistor is connected with the preset power supply signal, and a third end of the fourth switching transistor is connected with a ground signal. A third end of the third switching transistor is connected with a second end of the fourth switching transistor for outputting the isolation control signal.

**[0015]** In some embodiments, the amplifying circuit includes a cross-coupled circuit and a control circuit. The amplifying circuit is further configured to receive the signal to be processed through the cross-coupled circuit, receive the isolation control signal through the control circuit, and amplify the signal to be processed according to the isolation control signal to obtain the target amplified signal.

[0016] In some embodiments, the cross-coupled circuit includes a fifth switching transistor, a sixth switching transistor, a seventh switching transistor and an eighth switching transistor, and the control circuit includes a ninth switching transistor and a tenth switching transistor. [0017] A first end of the fifth switching transistor is connected with a third end of the ninth switching transistor for receiving the signal to be processed, and a second end of the fifth switching transistor, a third end of the seventh switching transistor and a first end of the eighth switching transistor are connected with a second end of the tenth switching transistor.

**[0018]** A first end of the sixth switching transistor is connected with a third end of the tenth switching transistor for receiving a reference signal to be processed, and a second end of the sixth switching transistor, a third end of the eighth switching transistor and a first end of the seventh switching transistor are connected with a second end of a ninth switching transistor.

**[0019]** A third end of the fifth switching transistor and a third end of the sixth switching transistor are connected with a first reference signal, a second end of the seventh switching transistor and a second end of the eighth switching transistor are connected with a second reference signal, and a first end of the ninth switching transistor and a first end of the tenth switching transistor are connected with the isolation control signal.

**[0020]** In some embodiments, the amplifying circuit further includes a first reference circuit and a second reference circuit. The first reference circuit is configured to receive a first reference control signal and output the first reference signal according to the first reference control signal. The second reference circuit is configured to receive a second reference control signal and output the second reference signal according to the second reference control signal. A voltage value of the first reference signal is a fourth voltage value or a fifth voltage value, a voltage value of the second reference signal is the fourth

voltage value or a sixth voltage value, and the fourth voltage value is an intermediate value between the fifth voltage value and the sixth voltage value.

[0021] In some embodiments, the first reference circuit includes n eleventh switching transistors, and n is a positive integer. A first end of each eleventh switching transistor is connected with a respective one of first reference control signals, and a third end of each eleventh switching transistor is connected with a ground signal. A second end of each eleventh switching transistor is connected with an output end of the first reference circuit for outputting the first reference signal.

**[0022]** In some embodiments, the second reference circuit includes m twelfth switching transistors, and m is a positive integer. A first end of each twelfth switching transistor is connected with a respective one of second reference control signals, and a second end of each twelfth switching transistor is connected with a respective one of third preset power supplies. The second end of each twelfth switching transistor is connected with an output end of the second reference circuit for outputting the second reference signal.

**[0023]** In some embodiments, the amplifying circuit further includes a first signal establishing circuit and a second signal establishing circuit. The first signal establishing circuit is configured to receive a first control input signal and output the first reference control signal. The second signal establishing circuit is configured to receive a second control input signal and output the second reference control signal.

[0024] In some embodiments, the first signal establishing circuit includes n second inverters, and the second signal establishing circuit includes n third inverters. An input end of each second inverter is connected with a respective one of first control input signals, and an output end of each second inverter is configured to output the respective one of first reference control signals. A first reference control signal of each eleventh switching transistor is output through one of the n second inverters. An input end of each third inverter is connected with the respective one of the first control input signals, and an output end of each third inverter is configured to output the respective one of second reference control signals. A second reference control signal of each twelfth switching transistor is output through one of the m third inverters. [0025] In some embodiments, the amplifying circuit further includes a precharge circuit, and the precharge circuit includes a thirteenth switching transistor and a fourteenth switching transistor. A first end of the thirteenth switching transistor and a first end of the fourteenth switching transistor are connected with a precharge signal. A second end of the thirteenth switching transistor is connected with a fourth preset power supply. A third end of the thirteenth switching transistor is connected with the second end of the sixth switching transistor.

**[0026]** A third end of the fourteenth switching transistor is connected with the second end of the fifth switching transistor, and a second end of the fourteenth switching

transistor is connected with the second end of the sixth switching transistor.

[0027] In some embodiments, the amplifying circuit further includes a noise cancellation circuit, and the noise cancellation circuit includes a fifteenth switching transistor and a sixteenth switching transistor. A first end of the fifteenth switching transistor and a first end of the sixteenth switching transistor are connected with a noise cancellation signal. A second end of the fifteenth switching transistor is connected with the second end of the fifth switching transistor, and a third end of the fifth switching transistor. A second end of the sixteenth switching transistor is connected with the second end of the sixth switching transistor, and a third end of the sixteenth switching transistor is connected with the first end of the sixth switching transistor is connected with the first end of the sixth switching transistor is connected with the first end of the sixth switching transistor is connected with the first end

**[0028]** In some embodiments, the first switching transistor, the second switching transistor, the third switching transistor, the seventh switching transistor and the eighth switching transistor are P-type channel field effect transistors (FETs). The fourth switching transistor, the fifth switching transistor, the sixth switching transistor, the ninth switching transistor, the tenth switching transistor, the eleventh switching transistor, the twelfth switching transistor, the thirteenth switching transistor, the fourteenth switching transistor, the fifteenth switching transistor and the sixteenth switching transistor are N-type channel FETs.

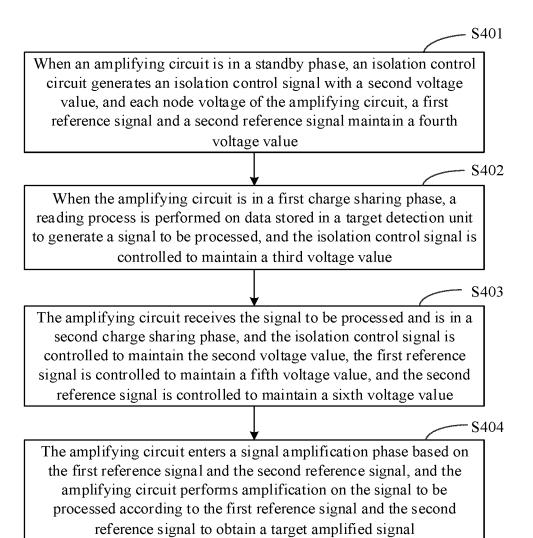

**[0029]** According to a second aspect, the embodiments of the present disclosure provide a control method for an amplifying circuit, which is applied to an amplifying circuit connected to a target detection unit and includes the following operations.

**[0030]** When the amplifying circuit is in a first amplification phase, a power supply output circuit selects a second voltage value to output as a preset power supply signal according to a power supply switching signal, an isolation control circuit generates an isolation control signal with the second voltage value according to a control command signal in a second state, and the amplifying circuit receives the isolation control signal and a signal to be processed and performs preliminary amplification on the signal to be processed.

**[0031]** When the amplifying circuit is in an evolution phase, the power supply output circuit selects a first voltage value to output as the preset power supply signal according to the power supply switching signal, the isolation control circuit generates an isolation control signal with the first voltage value according to the control command signal in the second state, and the amplifying circuit performs secondary amplification on the signal to be processed according to the isolation control signal.

[0032] In some embodiments, the amplifying circuit is further in a standby phase, a first charge sharing phase, a second charge sharing phase, and a precharge phase, and the method further includes the following operations.

[0033] When the amplifying circuit is in the standby

phase, the second charge sharing phase or the precharge phase, the power supply output circuit selects the second voltage value to output as the preset power supply signal according to the power supply switching signal, and the isolation control circuit generates the isolation control signal with the second voltage value according to the control command signal in the second state. When the amplifying circuit is in the first charge sharing phase, the power supply output circuit selects the second voltage value to output as the preset power supply signal according to the power supply switching signal, the isolation control circuit generates an isolation control signal with a third voltage value according to a control command signal in a first state, and the amplifying circuit receives the signal to be processed to perform first charge sharing. [0034] According to a third aspect, the embodiments of the present disclosure provide a sense amplifier including the control amplifying circuit according to any one of the first aspects.

**[0035]** According to a fourth aspect, the embodiments of the present disclosure provide a semiconductor memory including the sense amplifier according to any one of the third aspects.

[0036] The embodiment of the present disclosure provides a control amplifying circuit, a sense amplifier and a semiconductor memory. The control amplifying circuit includes a power supply output circuit, an isolation control circuit and an amplifying circuit. The power supply output circuit is configured to receive a power supply switching signal, and select one of at least two preset voltage values according to the power supply switching signal to output as a preset power supply signal. The isolation control circuit is configured to receive a control command signal and the preset power supply signal, and generate an isolation control signal according to the control command signal. The amplifying circuit is configured to receive the isolation control signal and a signal to be processed, and amplify the signal to be processed based on the isolation control signal to obtain a target amplified signal. In this way, a voltage value of the preset power supply signal can be adjusted by using the power supply switching signal, and then a voltage value of the isolation control circuit is adjusted, so as to optimize the signal amplification process and partially improve the problems that the signal amplification speed is slow and noise is easily generated.

#### BRIEF DESCRIPTION OF THE DRAWINGS

### [0037]

40

FIG. 1 is a schematic diagram of an application scenario of a sense amplifier.

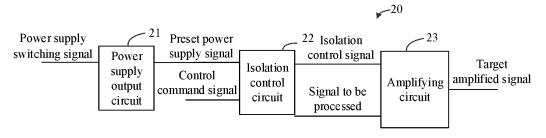

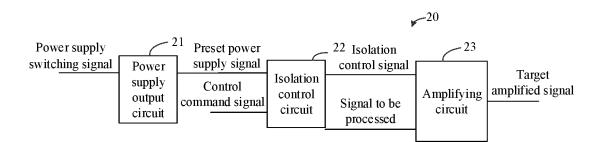

FIG. 2 is a schematic structural diagram of a control amplifying circuit according to an embodiment of the present disclosure.

FIG. 3 is a schematic structural diagram of another control amplifying circuit according to an embodi-

30

45

ment of the present disclosure.

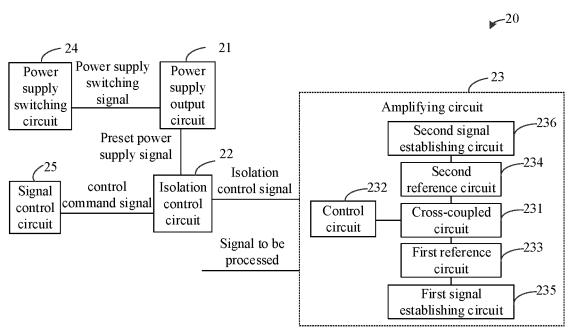

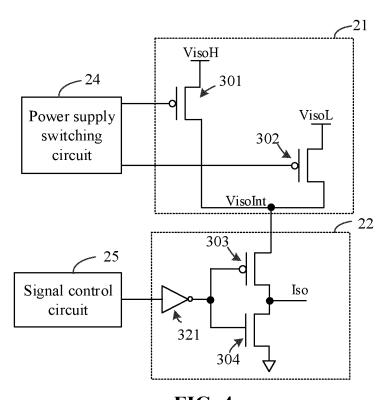

FIG. 4 is a partial detailed structural diagram of a control amplifying circuit according to an embodiment of the present disclosure.

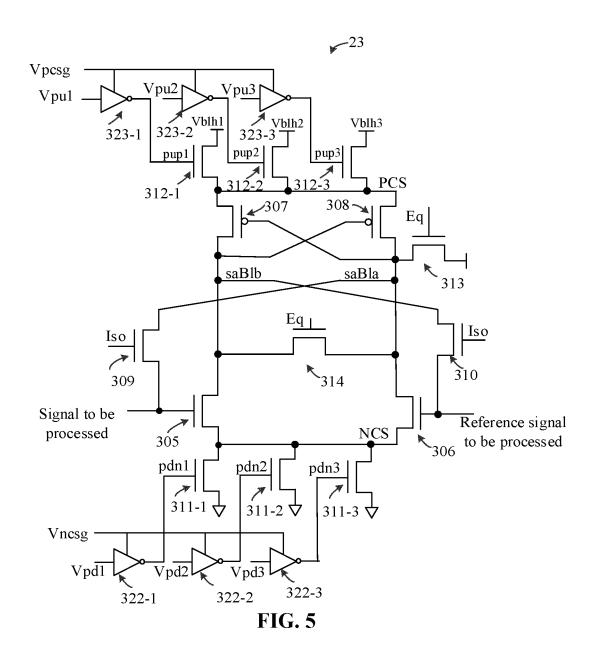

FIG. 5 is a partial detailed structural diagram of another control amplifying circuit according to an embodiment of the present disclosure.

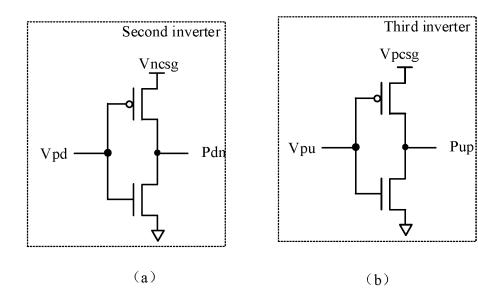

FIG. 6 is a schematic structural diagram of an inverter according to an embodiment of the present disclosure.

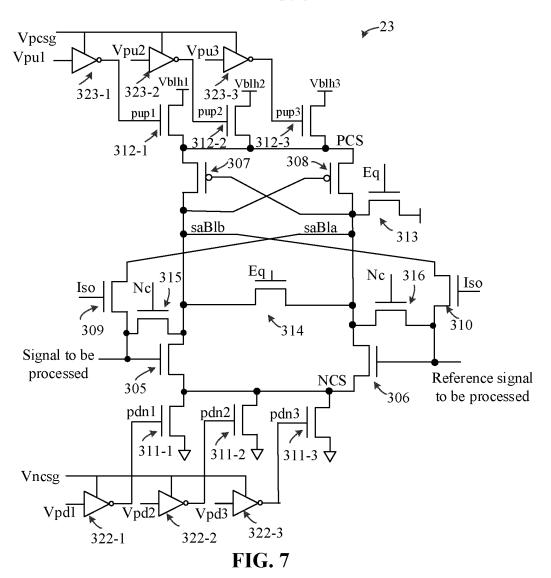

FIG. 7 is a partial detailed structural diagram of another control amplifying circuit according to an embodiment of the present disclosure.

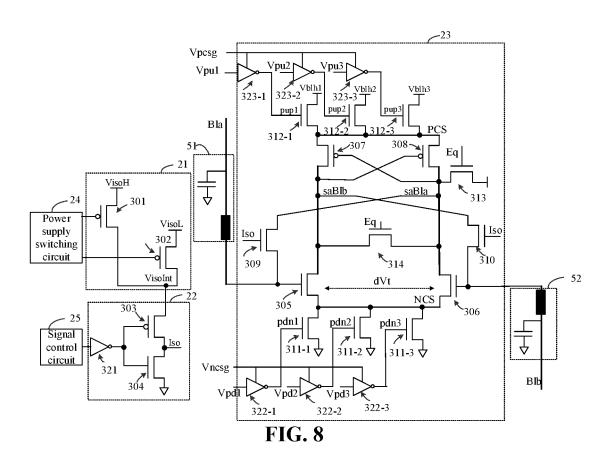

FIG. 8 is a schematic diagram of an application scenario of a control amplifying circuit according to an embodiment of the present disclosure.

FIG. 9 is a schematic flowchart of a control method for an amplifying circuit according to an embodiment of the present disclosure.

FIG. 10 is a schematic flowchart of another control method for an amplifying circuit according to an embodiment of the present disclosure.

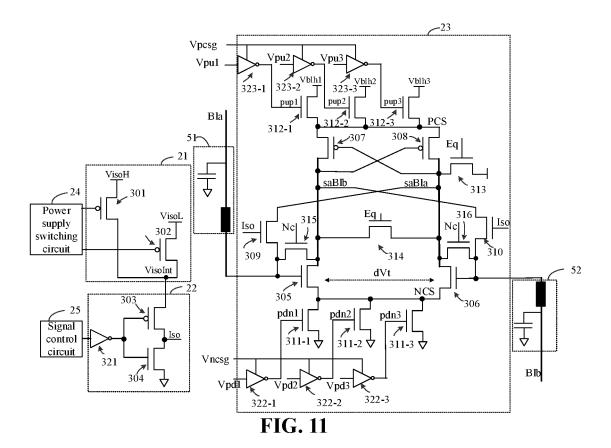

FIG. 11 is a schematic diagram of an application scenario of another control amplifying circuit according to an embodiment of the present disclosure.

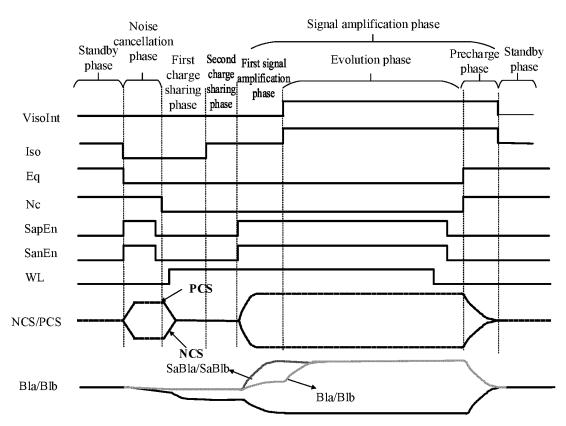

FIG. 12 is a signal timing diagram of an amplifying circuit according to an embodiment of the present disclosure.

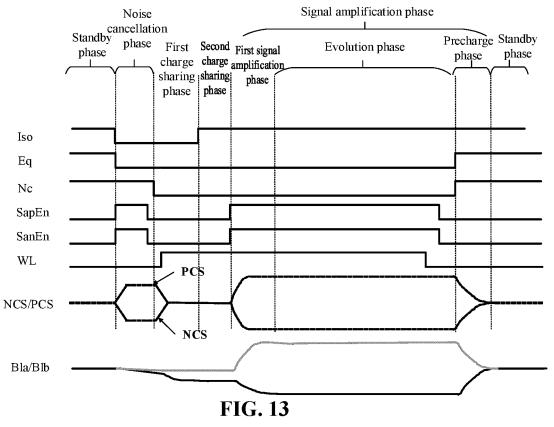

FIG. 13 is a timing diagram of signals according to the related art.

FIG. 14 is a schematic structural diagram of a sense amplifier according to an embodiment of the present disclosure.

FIG. 15 is a schematic structural diagram of a semiconductor memory according to an embodiment of the present disclosure.

#### **DETAILED DESCRIPTION**

**[0038]** The technical solutions in the embodiments of the present disclosure will be clearly and completely described below in conjunction with the accompanying drawings in the embodiments of the present disclosure. It is to be understood that the specific embodiments described herein are merely intended to explain the relevant application and not to limit the application. It should also be noted that, for ease of description, only portions related to the related application are shown in the accompanying drawings.

**[0039]** Unless otherwise defined, all technical and scientific terms used herein have the same meaning as those generally understood by those skilled in the art belonging to the present disclosure. The terms used herein are only adopted to describe the embodiments of the disclosure and not intended to limit the disclosure.

**[0040]** In the following description, "some embodiments" involved describes a subset of all possible embodiments, but it is to be understood that "some embod-

iments" may be a same subset or different subsets of all possible embodiments and may be combined with each other without conflict.

[0041] It should be noted that the term "first\second\third" involved in the embodiments of the present disclosure is merely used to distinguish similar objects without representing a specific order for the objects. It is to be understood that "first\ second\ third" may be interchanged to specific sequences or orders if allowed to implement the embodiments of the disclosure described herein in sequences except the illustrated or described ones.

**[0042]** The following is explanation of technical terms involved in the embodiments of the present disclosure and a correspondence of partial terms.

P-type FET: hole-type FET; N-type FET: electron type FET.

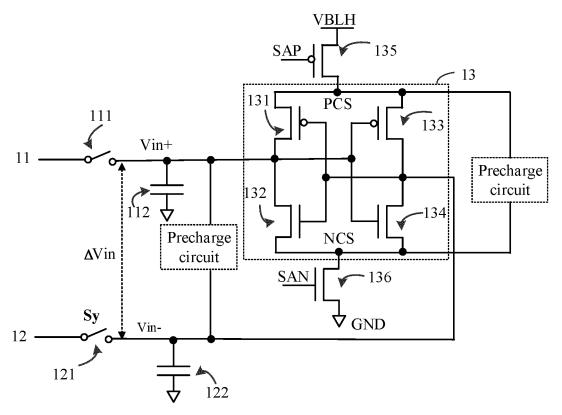

**[0043]** It is to be appreciated that in the working process of DRAM, it is necessary to use the sense amplifier to realize signal amplification in various operation processes. FIG. 1 illustrates a schematic diagram of an application scenario of a sense amplifier. The application scenario includes a first signal line 11, a second signal line 12 and a sense amplifier 113.

**[0044]** The first signal line 11 is provided with a first switch 111 and a first capacitor 112 for inputting a signal to be processed Vin+. The second signal line 12 is provided with a second switch 121 and a second capacitor 122 for inputting a reference signal to be processed Vin-, and the sense amplifier 113 is used for amplifying the signal to be processed Vin+ and the reference signal to be processed Vin-. A voltage difference between the signal to be processed Vin- is  $\Delta$ Vin. The first switch 111 and the first capacitor 112 may be regarded as one memory cell, and the second switch 121 and the second capacitor 122 may be regarded as another memory cell.

[0045] Specifically, the sense amplifier includes a first switching transistor 131, a second switching transistor 132, a third switching transistor 133 and a fourth switching transistor 134. A first end of the first switching transistor 131, a first end of the second switching transistor 132, a third end of the third switching transistor 133 and a second end of the fourth switching transistor 134 are all connected with the reference signal to be processed Vin-, and a third end of the first switching transistor 131, a second end of the second switching transistor 132, a first end of the third switching transistor 133 and a first end of the fourth switching transistor 134 are all connected with the signal to be processed Vin+. In this application scenario, there are also a fifth switching transistor 135 and a sixth switching transistor 136. A first end of the fifth switching transistor 135 is connected with a first control signal SAP, a second end of the fifth switching transistor 135 is connected with a power supply signal VBLH, and a third end of the fifth switching transistor 135 and a sec-

25

40

45

50

ond end of the first switching transistor 131 are connected with a second end of the third switching transistor 133 to form a first reference signal end. A first end of the sixth switching transistor 136 is connected with a second control signal SAN, a second end of the sixth switching transistor 136 is connected with a ground signal GND, and the second end of the sixth switching transistor 136 and the third end of the second switching transistor 132 are connected with a third end of the fourth switching transistor 134 to form a second reference signal end. The first switching transistor 131, the third switching transistor 132 and the fifth switching transistor 135 are P-type FETs, a first end of the P-type FET is a gate pin, a second end of the P-type FET is a source pin, and a third end of the P-type FET is a drain pin. The second switching transistor 132, the fourth switching transistor 134 and the sixth switching transistor 136 are N-type FETs, a first end of the N-type FET is a gate pin, a second end of the Ntype FET is a drain pin, and a third end of the N-type FET is a source pin.

**[0046]** In addition, there may be a precharge circuit between the first signal line 11 and the second signal line 12, and there may be a precharge circuit between the second end of the third switching transistor 133 and the third end of the fourth switching transistor for precharging the first reference signal end and the second reference signal end.

**[0047]** At present, the signal amplification speed of the sense amplifier is slow, the circuit is easy to generate noise, and the power consumption is high, which affect the performance of the semiconductor memory.

[0048] The embodiments of the present disclosure provide a control amplifying circuit, which includes a power supply output circuit, an isolation control circuit and an amplifying circuit. The power supply output circuit is configured to receive a power supply switching signal, and select one preset voltage value from at least two preset voltage values according to the power supply switching signal to output as a preset power supply signal. The isolation control circuit is configured to receive a control command signal and the preset power supply signal, and generate an isolation control signal according to the control command signal. The amplifying circuit is configured to receive the isolation control signal and a signal to be processed, and amplify the signal to be processed based on the isolation control signal to obtain a target amplified signal. In this way, a voltage value of the preset power supply signal can be adjusted by using the power supply switching signal, and then a voltage value of the isolation control signal is adjusted, so as to optimize the signal amplification process and improve the problems that the signal amplification speed is slow and noise is easily gen-

**[0049]** The embodiments of the present disclosure will be described in detail with reference to the accompanying drawings.

**[0050]** In an embodiment of the present disclosure, reference is made to FIG. 2, which shows a schematic struc-

tural diagram of a control amplifying circuit 20 according to the embodiment of the present disclosure. As shown in FIG. 2, the control amplifying circuit 20 may include a power supply output circuit 21, an isolation control circuit 22 and an amplifying circuit 23.

**[0051]** The power supply output circuit 21 is configured to receive a power supply switching signal, and select one preset voltage value from at least two preset voltage values according to the power supply switching signal to output as a preset power supply signal.

**[0052]** The isolation control circuit 22 is configured to receive a control command signal and the preset power supply signal, and generate an isolation control signal according to the control command signal.

**[0053]** The amplifying circuit 23 is configured to receive the isolation control signal and a signal to be processed, and amplify the signal to be processed based on the isolation control signal to obtain a target amplified signal.

[0054] It should be noted that the control amplifying circuit 20 provided in the embodiment of the present disclosure may be applied in a variety of signal amplification scenarios, for example, in a sense amplifier in a DRAM. [0055] The control amplifying circuit 20 provided in the embodiment of the present disclosure receives the power supply switching signal, the control command signal and the signal to be processed from the outside, completes the amplification process of the signal to be processed based on the power supply switching signal and the control command signal, and finally obtains the target amplified signal. Both the control command signal and the power supply switching signal need to be determined according to a specific operation stage of the amplifying circuit.

**[0056]** Specifically, for the control amplifying circuit 20, at least two preset voltage values are selected and outputted by the power supply output circuit 21 according to the power supply switching signal to obtain the preset power supply signal; the isolation control signal is outputted by the isolation control circuit 22 according to the control command signal and the preset power supply signal; and the signal to be processed is amplified by the amplifying circuit 23 according to the isolation control signal to output the target amplified signal.

**[0057]** In this way, a voltage value of the preset power supply signal can be adjusted by using the power supply switching signal, and then a voltage value of the isolation control signal output by the isolation control circuit 22 is adjusted, so as to optimize the signal amplification process and solve the problems that the signal amplification speed is slow and noise is easily generated.

**[0058]** In some embodiments, the power supply switching signal may include a first power supply switching signal and/or a second power supply switching signal. On the basis of FIG. 2, as shown in FIG. 3, the control amplifying circuit 20 may further include a power supply switching circuit 24.

**[0059]** The power supply switching circuit 24 is configured to output the first power supply switching signal

and/or the second power supply switching signal.

**[0060]** The power supply output circuit 21 is specifically configured to receive the first power supply switching signal and/or the second power supply switching signal, and select one preset voltage value from the at least two preset voltage values according to the first power supply switching signal and/or the second power supply switching signal to output as the preset power supply signal.

**[0061]** It should be noted that the power supply switching signal may include only one signal, for example, the first power supply switching signal or second power supply switching signal. Alternatively, the power supply switching signal may include a pair of signals having opposite level states, for example, including both the first power supply switching signal and a second power supply switching signal.

[0062] In one specific embodiment, two preset voltage values are set as a first voltage value and a second voltage value. The power supply switching signal includes both of the first power supply switching signal and the second power supply switching signal. In such case, the power supply output circuit 21 is further configured to generate a preset power supply signal having the first voltage value when the first power supply switching signal is in a first level state and the second power supply switching signal is in a second level state; or generate a preset power signal having the second voltage value when the first power supply switching signal is in the second level state and the second power supply switching signal is in the first level state.

[0063] The first voltage value and the second voltage value both belong to the second level state, and the first voltage value is greater than the second voltage value.

[0064] It should be noted that, for the P-type FET, the

**[0064]** It should be noted that, for the P-type FET, the first level state may enable the P-type FET to be in an on-state, and the second level state may enable the P-type FET to be in an off-state. For the N-type FET, the first level state may enable the N-type FET to be in an off-state and the second level state may enable the N-type FET to be in an on-state. The first level states of different switching transistors may be different voltage ranges since different switching transistors have different specifications.

[0065] In another specific embodiment, the power supply switching signal includes only the first power supply switching signal. In such case, the power supply output circuit 21 is further configured to generate a preset power supply signal having the first voltage value when the first power supply switching signal is in the first level state; or generate a preset power supply signal having the second voltage value when the first power supply switching signal is in the second level state.

**[0066]** In this way, the power supply output circuit 21 may output two preset power supply signals with different voltage values, rather than one power supply signal with a fixed voltage value. In this way, in different operation stages of the amplifying circuit 23, more control means can be provided by adjusting the voltage values of the

preset power supply signals, so as to partially solve the problems that the signal amplifying speed is slow and the circuit has a high noise.

**[0067]** In some embodiments, as shown in FIG. 3, the control amplifying circuit 20 may further include a signal control circuit 25.

**[0068]** The signal control circuit 25 is configured to output the control command signal.

**[0069]** The isolation control circuit 22 is further configured to generate an isolation control signal with a third voltage value when the control command signal is in a first state; or generate an isolation control signal with a same voltage value as the preset power supply signal when the control command signal is in a second state.

**[0070]** The first state is the first level state and the second state is the second level state. Alternatively, the first state is the second level state and the second state is the first level state.

[0071] It should be noted that, for the isolation control circuit 22, if the control command signal is in the first level state and the preset power supply signal has the first voltage value, the isolation control signal has the first voltage value. If the control command signal is in the first level state and the preset power supply signal has the second voltage value, the isolation control signal has the second voltage value. If the control command signal is in the first state, the isolation control signal has the third voltage value.

**[0072]** Alternatively, if the control command signal is in the second level state and the preset power supply signal has the first voltage value, the isolation control signal has the first voltage value. If the control command signal is in the second level state and the preset power supply signal has the second voltage value, the isolation control signal has the second voltage value. If the control command signal is in the first state, the isolation control signal has the third voltage value.

[0073] The third voltage value belongs to the first level state, the first voltage value and the second voltage value both belong to the second level state, the third voltage value is lower than the second voltage value, and the second voltage value is lower than the first voltage value. [0074] Exemplarily, in a customary representation, the first level state may be represented by a logic "0", the second level state may be represented by a logic "1", the third voltage value may be represented by a logic "0", and both the first voltage value and the second voltage value may be represented by logic "1". the above is merely illustrative and does not have actual limitations.

[0075] In this way, the isolation control signal has three different voltage values, which can provide more control means to optimize the signal amplification process and partially solve the problems that the signal amplification speed is slow and the circuit noise is high.

**[0076]** Taking the power supply switching signal including both the first power supply switching signal and the second power supply switching signal as an example, a feasible structure of the power supply output circuit 21

is provided.

**[0077]** On the basis of FIG. 3, as shown in FIG. 4, the power supply output circuit 21 includes a first preset power supply VisoH, a second preset power supply VisoL, a first switching transistor 301 and a second switching transistor 302.

**[0078]** A first end of the first switching transistor 301 is connected with the first power supply switching signal, and a first end of the second switching transistor 302 is connected with the second power supply switching signal

[0079] A second end of the first switching transistor 301 is connected with the first preset power supply VisoH, and a second end of the second switching transistor 302 is connected with the second preset power supply VisoL. [0080] A third end of the first switching transistor 301 is connected with a third end of the second switching transistor 302 for outputting the preset power supply signal V'isoInt.

**[0081]** The first preset power supply VisoH is configured to output the first voltage value, and the second preset power supply VisoL is configured to output the second voltage value.

**[0082]** It should be noted that, as shown in FIG. 4, the first switching transistor 301 and the second switching transistor 302 both are P-type FETs. In the following description, a first end of the P-type FET is a gate pin, a second end of the P-type FET is a source pin, and a third end of the P-type FET is a drain pin.

[0083] It should be noted that when the first power supply switching signal is in the first level state and the second power supply switching signal is in the second level state, the first switching transistor 301 is turned on and the second switching transistor 302 is turned off, so the voltage values of the preset power supply signal V'isoInt and the first preset power supply VisoH are the same, that is, the preset power supply signal VisoInt has the first voltage value. When the first power supply switching signal is in the second level state and the second power supply switching signal is in the first level state, the first switching transistor 301 is turned off and the second switching transistor 302 is turned on, so the voltage values of the preset power supply signal V'isoInt and the second preset power supply VisoL are the same, that is, the preset power supply signal VisoInt has the second voltage value.

[0084] In this way, in the embodiments of the present disclosure, on the premise that the isolation control signal Iso is in the second level state, the isolation control signal Iso may be controlled to be a higher voltage (the first voltage value) or a lower voltage (the second voltage value) to suit the voltage requirements and the signal transmission speed at different amplification stages, thereby optimizing the signal amplification process, improving the signal amplification speed and reducing the circuit noise.

[0085] Taking the first state being the first level state and the second state being the second level state as an

example, a feasible structure of the isolation control circuit 22 is provided. In some embodiments, as illustrated in FIG. 4, the isolation control circuit 22 includes a first inverter 321, a third switching transistor 303 and a fourth switching transistor 304.

[0086] An input end of the first inverter 321 is connected with an output end of the signal control circuit 25 for receiving the control command signal output by the signal control circuit 25. An output end of the first inverter 321 is respectively connected with a first end of the third switching transistor 303 and a first end of the fourth switching transistor 304.

**[0087]** A second end of the third switching transistor 303 is connected with the preset power supply signal VisoInt, and a third end of the fourth switching transistor 304 is connected with a ground signal.

**[0088]** A third end of the third switching transistor 303 is connected with a second end of the fourth switching transistor 304 for outputting the isolation control signal Iso.

**[0089]** It should be noted that the third switching transistor 303 is a P-type FET, and the fourth switching transistor 304 is an N-type FET. In the following description, a first end of the N-type FET is a gate pin, a second end of the N-type FET is a drain pin, and a third end of the N-type FET' is a source pin.

[0090] In this way, when the control command signal is in the first level state, the third switching transistor 303 is in the off-state and the fourth switching transistor 304 is in the on-state, so that the isolation control signal Iso has the third voltage value corresponding to the ground potential. When the control command signal is in the second level state, the third switching transistor 303 is in the on-state and the fourth switching transistor 304 is in the off-state, so that the voltage value of the isolation control signal Iso is the same as the voltage value of the preset power supply signal Visolnt, i.e., the voltage value or the isolation control signal is the first voltage value or the second voltage value.

**[0091]** In addition, when the first state is the second level state and the second state is the first level state, the isolation control circuit 22 may include only the third switching transistor 303 and the fourth switching transistor 304. The output end of the signal control circuit 25 is connected with the first end of the third switch transistor 303 and the first end of the fourth switch transistor 304, and the other connections remain unchanged.

[0092] In such case, when the control command signal is in the second level state, the third switching transistor 303 is in the off-state and the fourth switching transistor 304 is in the on-state, so that the isolation control signal Iso has the third voltage value corresponding to the ground potential. When the control command signal is in the first level state, the third switching transistor 303 is in the on-state and the fourth switching transistor 304 is in the off-state, so that the voltage value of the isolation control signal Iso is the same as the voltage value of the preset power supply signal VisoInt, i.e., the voltage value

30

40

45

of the isolation control signal is the first voltage value or the second voltage value.

**[0093]** In some embodiments, as shown in FIG. 3, the amplifying circuit 23 includes a cross-coupled circuit 231 and a control circuit 232.

**[0094]** The amplifying circuit 23 is further configured to receive the signal to be processed through the cross-coupled circuit 231, receive the isolation control signal through the control circuit 232, and amplify the signal to be processed according to the isolation control signal to obtain the target amplified signal.

[0095] It should be note that, taking DRAM as an example, the cross-coupled circuit 231 is connected with a target detection unit through a bit line and connected with a complementary memory cell through a complementary bit line. In the initial state, the potentials on the bit line and the complementary bit line are the same. After the memory cell on the bit line (i.e., the target detection unit) is turned on, the memory cell performs charge sharing with the bit line, so that the potential on the bit line rises or drops. The memory cells on the complementary bit line are always turned off, and therefore the potential on the complementary bit line remains unchanged. Since the potential on the bit line rises and drops, the voltage difference between the bit line and the complementary bit line changes, so that a part of devices in the crosscoupled circuit 231 are turned on, and the signal amplification process is performed. In such case, the signal received by the cross-coupled circuit 231 from the bit line may be regarded as the signal to be processed, and the signal received by the cross-coupled circuit 231 from the complementary bit line may be regarded as the reference signal to be processed.

[0096] It should also be noted that the cross-coupled circuit 231 further includes a readout bit line connected with one set of switching transistors and a complementary readout bit line connected with another set of switching transistors. When the control circuit 22 controls the isolation control signal to be in the first level state, the bit line and the readout bit line are not connected, and the complementary bit line and the complementary readout bit line are not connected. When the isolation control signal is in the first level state, the control circuit 22 can control the bit line and the readout bit line to be connected, and the complementary bit line and the complementary readout bit line to be connected. Then, the cross-coupled circuit 231 may complete the signal amplification process by means of the readout bit line/complementary readout bit line, as described below.

**[0097]** In one specific embodiment, on the basis of FIG. 3, as shown in FIG. 5, the cross-coupled circuit 231 may include a fifth switching transistor 305, a sixth switching transistor 306, a seventh switching transistor 307 and an eighth switching transistor 308, and the control circuit 232 includes a ninth switching transistor 309 and a tenth switching transistor 310.

**[0098]** A first end of the fifth switching transistor 305 is connected with a third end of the ninth switching transistor

309 for receiving the signal to be processed, and a second end of the fifth switching transistor 305, a third end of the seventh switching transistor 307 and a first end of the eighth switching transistor 308 are connected with a second end of the tenth switching transistor 310. The second end of the fifth switching transistor 305, the third end of the seventh switching transistor 307, the first end of the eighth switching transistor 308 and the second end of the tenth switching transistor 310 are both connected to the complementary readout bit line.

**[0099]** A first end of the sixth switching transistor 306 is connected with a third end of the tenth switching transistor 310 for receiving a reference signal to be processed, and a second end of the sixth switching transistor 306, a third end of the eighth switching transistor 308 and a first end of the seventh switching transistor 307 are connected with a second end of the ninth switching transistor 309. The second end of the sixth switching transistor 306, the third end of the eighth switching transistor 308, the first end of the seventh switching transistor 307 and the second end of the ninth switching transistor 309 are both connected to the readout bit line.

**[0100]** A third end of the fifth switching transistor 305 and a third end of the sixth switching transistor 306 are connected with a first reference signal NCS, a second end of the seventh switching transistor 307 and a second end of the eighth switching transistor 308 are connected with a second reference signal PCS, and a first end of the ninth switching transistor 309 and a first end of the tenth switching transistor 310 are connected with the isolation control signal Iso.

**[0101]** It should be noted that the fifth switching transistor 305, the sixth switching transistor 306, the ninth switching transistor 309 and the tenth switching transistor 310 are N-type FETs, and the seventh switching transistor 307 and the eighth switching transistor 308 are P-type FETs.

**[0102]** Thus, when the isolation control signal Iso is in the second level state (having the first voltage value or the second voltage value), the ninth switching transistor 309 and the tenth switching transistor 310 in the control circuit 232 are turned on, and the cross-coupled circuit 231 receives the signal to be processed. When the isolation control signal Iso is in the first level state (having the third voltage value), the ninth switching transistor 309 and the tenth switching transistor 310 in the control circuit 232 are turned off, and the cross-coupled circuit 231 is not connected to the external signal.

**[0103]** It should be noted that, during signal amplification, the first reference signal NCS may be used to provide a low reference potential for the cross-coupled circuit 231, and the second reference signal PCS may be used to provide a high reference potential for the cross-coupled circuit 231. Based on this, the amplification principle of the cross-coupled circuit 231 is briefly described as follows.

**[0104]** Assuming that the stored data of the target detection unit is "0", the voltage of the signal to be processed

is lower than the voltage of the reference signal to be processed. The amplification phase of the cross-coupled circuit 231 includes a first amplification phase and an evolution phase.

**[0105]** In the first amplification phase, the isolation control signal Iso is in the second voltage value of the second level state, the ninth switching transistor 309 and the tenth switching transistor 310 are turned on, the bit line is connected with the readout bit line, and the complementary bit line is connected to the complementary readout bit line. In such case, the reference signal to be processed is transmitted to the readout bit line, so that the sixth switching transistor 306 is turned on, the potential on the readout bit line is pulled low based on the low reference potential, then the seventh switching transistor 307 is turned on, and the potential on the complementary readout bit line is pulled high based on the high reference potential.

**[0106]** In the evolution phase, the isolation control signal Iso is in the first voltage value of the second level state, the conduction degrees of the ninth switching transistor 309 and the tenth switching transistor 310 are increased, the potential on the readout bit line after being pulled low is transmitted to the bit line through the ninth switching transistor 309, the reference signal to be processed on the bit line is quickly pulled low, and the reference signal to be processed on the complementary bit line is quickly pulled high through the tenth switching transistor 310, so that the voltage difference between the signal to be processed and the reference signal to be processed is increased to obtain the target amplified signal.

**[0107]** Assuming that the stored data of the target detection unit is "1", the voltage of the signal to be processed is higher than the voltage of the reference signal to be processed. In the first amplification phase, the fifth switching transistor 305 is in the on-state, potential pull-down processing is performed on the complementary readout bit line based on the low reference potential, the eighth switching transistor 308 is in the on-state, and potential pull-up processing is performed on the readout bit line based on the high reference potential.

**[0108]** In the evolution phase, the isolation control signal Iso is in the first voltage value of the second level state, the conduction degrees of the ninth switching transistor 309 and the tenth switching transistor 310 are increased, the potential on the readout bit line after being pulled high is transmitted to the bit line, the reference signal to be processed on the bit line is quickly pulled high, and the reference signal to be processed on the complementary bit line is quickly pulled low through the tenth switching transistor 310, so that the voltage difference between the signal to be processed and the reference signal to be processed to obtain the target amplified signal subsequently.

**[0109]** It should also be noted that, during signal amplification, when the amplifying circuit 23 starts to amplify, since the isolation control signal Iso is at the second volt-

age value, the gate voltages of the ninth switching transistor 309 and the tenth switching transistor 310 are low, the voltage of the bit line or the complementary bit line is raised slowly without generating a high noise, so that the stored data of the adjacent memory cells is not affected. Therefore, the sensing amplitude of the amplifying circuit 23 can be improved, while the internal nodes of the amplifying circuit 23 can quickly reach a low reference potential or a high reference potential. In the evolution phase, when the isolation control signal Iso is at the first voltage value, the gate voltages of the ninth switching transistors 309 and the tenth switching transistor 310 are raised, and the voltage flowing through the bit line or the complementary bit line is raised. Since the internal node voltage of the amplifying circuit 23 has changed, the bit line or the complementary bit line is quickly pulled high or low, so that the signal amplification speed is improved, and noise generated when the potential of the bit line or the complementary bit line is raised is suppressed.

**[0110]** In some embodiments, as shown in FIG. 3, the amplifying circuit 23 further includes a first reference circuit 233 and a second reference circuit 234.

**[0111]** The first reference circuit 233 is configured to receive a first reference control signal and output the first reference signal according to the first reference control signal.

**[0112]** The second reference circuit 234 is configured to receive a second reference control signal and output the second reference signal according to the second reference control signal.

**[0113]** A voltage value of the first reference signal is a fourth voltage value or a fifth voltage value, a voltage value of the second reference signal is the fourth voltage value or a sixth voltage value, and the fourth voltage value is an intermediate value between the fifth voltage value and the sixth voltage value.

**[0114]** It should be noted that the first reference signal may provide a low reference potential to the cross-coupled circuit 231, and the second reference signal may provide a high reference potential to the cross-coupled circuit, so that the cross-coupled circuit 231 may perform amplification processing on the signal to be processed and the reference signal to be processed according to the high reference potential (i.e., the fifth voltage value) and the low reference potential (i.e., the sixth voltage value)

**[0115]** Exemplarily, as shown in FIG. 5, the first reference circuit 233 includes n eleventh switching transistors (e.g., an eleventh switching transistor 311-1, an eleventh switching transistor 311-2 and an eleventh switching transistor 311-3). n is a positive integer.

**[0116]** A first end of each eleventh switching transistor is connected with a respective one of first reference control signals (e.g., pdn1, pdn2, pdn3 in FIG. 5), and a third end of each eleventh switching transistor 311 is connected with a ground signal.

[0117] A second end of each eleventh switching tran-

sistor is connected with an output end of the first reference circuit 233 for outputting the first reference signal NCS.

**[0118]** It should be noted that three eleventh switching transistors are shown in FIG. 5, but the number of the eleventh switching transistors may be more or less in a practical application scenario. In addition, the number of the first reference control signals is also more than one, and one first reference control signal corresponds to one eleventh switching transistor. The level states of the multiple first reference control signals may be different, i.e., the level states of the respective pdn1, pdn2, and pdn3 are individually varied. That is, one eleventh switching transistor is individually controlled by one first reference control signal.

**[0119]** As shown in FIG. 5, all eleventh switching transistors may be N-type FETs. Taking the eleventh switching transistor 311-1 as an example, when the first reference control signal pdn1 is in the first level state, the eleventh switching transistor 311-1 is turned off. When the first reference control signal pdn1 is in the second level state, the eleventh switching transistor 311-1 is turned on.

[0120] Thus, the potential of the first reference signal NCS can be adjusted by the eleventh switching transistor in the on-state through the first reference circuit 233, thereby providing a low reference potential for the crosscoupled circuit 231. In addition, each of different eleventh switching transistors is connected with a separate ground potential, and the specific voltage values of these ground potentials may be different to provide different voltage drop speeds of the first reference signal NCS. In addition, the voltage drop speed of the first reference signal NCS may be controlled by controlling the number of the eleventh switching transistors in the on-state. In this way, by controlling the voltage adjustment speed to be different, it is able to reduce the noise generated when the voltage of the signal to be processed is rapidly reduced during the signal amplification.

**[0121]** In some embodiments, as shown in FIG. 5, the second reference circuit 234 includes m twelfth switching transistors (e.g., a twelfth switching transistor 312-1, a twelfth switching transistor 312-3 in FIG. 5), and m is a positive integer. A first end of each twelfth switching transistors is connected with a respective one of second reference control signals (e.g., pup1, pup2, pup3 in FIG. 5), and a second end of each twelfth switching transistors is connected with a respective one of third preset power supplies (e.g., Vblhl, Vblh2, Vblh3 in FIG. 5).

**[0122]** The second end of each twelfth switching transistor is connected with an output end of the second reference circuit 234 for outputting the second reference signal PCS.

**[0123]** It should be noted that three twelfth switching transistors are shown in FIG. 5, but the number of the twelfth switching transistors 312 may be more or less in a practical application scenario. In addition, the number

of the second reference control signals is also more than one, and one second reference control signal corresponds to one twelfth switch transistor. The level states of the multiple second reference control signals may be different, i.e., the level states of the respective pup1, pup2, and pup3 are individually varied. That is, one twelfth switching transistor is individually controlled by one second reference control signal.

[0124] As shown in FIG. 5, the twelfth switching transistors may be N-type FETs. Therefore, taking the twelfth switching transistor 312-1 as an example, when the second reference control signal pup1 is in the first level state, the twelfth switching transistor 312-1 is turned off. When the first reference control signal pup1 is in the second level state, the eleventh switching transistor 312-1 is turned on.

**[0125]** Thus, the twelfth switching transistor in the onstate charges the second reference signal PCS to the second level state (a high reference potential), to provide a high reference potential for the cross-coupled circuit 231. Each of different twelfth switching transistors is connected with a separate third preset power supply, the voltage values of these third preset power supplies may be different to provide different voltage rise speeds of the second reference signal PCS. In addition, the voltage rise speeds may be controlled by controlling the number of the twelfth switching transistors in the on-state. In this way, by controlling the voltage rise speed to be different, it is able to reduce the noise generated when the voltage of the second reference signal is rapidly raised during the signal amplification.

**[0126]** In some embodiments, as shown in FIG. 3, the amplifying circuit 23 further includes a first signal establishing circuit 235 and a second signal establishing circuit 236.

**[0127]** The first signal establishing circuit 235 is configured to receive a first control input signal and output the first reference control signal.

**[0128]** The second signal establishing circuit 236 is configured to receive a second control input signal and output the second reference control signal.

**[0129]** In one specific embodiment, as shown in FIG. 5, the first signal establishing circuit 235 includes n second inverters (e.g., a second inverter 322-1, a second inverter 322-2, a second inverter 322-3 in FIG. 5), and the second signal establishing circuit 236 includes m third inverters (e.g., a third inverter 323-1, a third inverter 323-2, a third inverter 323-3 in FIG. 5).

**[0130]** An input end of each second inverter is connected with a respective one of first control input signals (e.g., Vpd1, Vpd2, Vpd3 in FIG. 5), and an output end of each second inverter is configured to output the respective one of first reference control signals (e.g., pdn1, pdn2, pdn3 in FIG. 5). A first reference control signal of each eleventh switching transistor is output through one of the second inverters.

**[0131]** An input end of each third inverter is connected with a respective one of second control input signals (e.g.,

Vpu1, Vpu2, Vpu3 in FIG. 5), and an output end of each third inverter is configured to output the respective one of second reference control signals (e.g., pup1, pup2, pup3 in FIG. 5). A second reference control signal of each twelfth switching transistor is output through one of the third inverters.

**[0132]** It should be noted that, as shown in FIG. 5, the input end of each second inverter is also connected with a power supply signal Vncsg. When the first control input signal is in the first level state, the second inverter outputs the first reference control signal in the second level state according to the power supply signal Vncsg. When the first control input signal is in the second level state, the second inverter outputs the first reference control signal in the first level state.

**[0133]** Similarly, the input end of each third inverter is also connected with a power supply signal Vpcsg. When the second control input signal is in the first level state, the third inverter outputs the second reference control signal in the second level state according to the power supply signal. When the second control input signal is in the second level state, the third inverter outputs the second reference control signal in the first level state.

**[0134]** The second inverter and the third inverter may adopt the same circuit structure, for example, implemented by one N-type FET and one P-type FET. FIG. 6 illustrates a schematic structural diagram of an inverter according to an embodiment of the present disclosure. The specific structure of the second inverter is shown in (a) of FIG. 6, and the specific structure of the third inverter is shown in (b) of FIG. 6.

[0135] It should also be noted that the number of first control input signals is also more than one, one second inverter is used to receive one first control input signal, and the level states of these first control input signals may be different. Taking the first control input signal Vpd1 in FIG. 5 as an example, when the first control input signal Vpd1 is in the first level state, the second inverter 322-1 outputs the first reference control signal pdn1 in the second level state, and in such case, the eleventh switching transistor 311-1 is in the on-state. Conversely, when the first control input signal Vpd1 is in the second level state, the second inverter 322-1 outputs the first reference control signal pdn1 in the first level state, and in such case, the eleventh switching transistor 311-1 is in the off-state. [0136] Similarly, the number of second control input signals is also more than one, one third inverter is used to receive one second control input signal, and the level states of these second control input signals may be different. Taking the second control input signal Vpd1 in FIG. 5 as an example, when the second control input signal Vpu1 is in the first level state, the third inverter 323-1 outputs the second reference control signal pup1 in the second level state, and in such case, the twelfth switching transistor 312-1 is in the on-state. Conversely, when the second control input signal Vpu1 is in the second level state, the third inverter 323-1 outputs the second reference control signal pup1 in the first level state,

and in such case, twelfth switching transistor 312-1 is in the off-state.

**[0137]** Thus, by the first signal establishing circuit, the second signal establishing circuit, the first reference circuit, and the second reference circuit, the first reference signal and the second reference signal with different voltage adjustment speeds can be provided for the crosscoupled circuit, thereby implementing the amplification process of the signal to be processed.

[0138] In some embodiments, as illustrated in FIG. 5, the amplifying circuit 23 further includes a precharge circuit, and the precharge circuit includes a thirteenth switching transistor 313 and a fourteenth switching transistor 314.

**[0139]** A first end of the thirteenth switching transistor 313 and a first end of the fourteenth switching transistor 314 are connected with a precharge signal Eq.

**[0140]** A second end of the thirteenth switching transistor 313 is connected with a fourth preset power supply. A third end of the thirteenth switching transistor 313 is connected with the second end of the sixth switching transistor 306.

**[0141]** A third end of the fourteenth switching transistor 314 is connected with the second end of the fifth switching transistor 305, and a second end of the fourteenth switching transistor 314 is connected with the second end of the sixth switching transistor 306.

[0142] The thirteenth switching transistor 313 and the fourteenth switching transistor 314 are both N-type FETs. [0143] In this way, in response to the precharge signal Eq, the precharge circuit performs a precharge process for the amplifying circuit 23, and enables the respective circuit nodes of the amplifying circuit 23 are set to have the same voltage value after completion of the precharge process.

**[0144]** In some embodiments, on the basis of FIG. 5, as shown in FIG. 7, the amplifying circuit 23 further includes a noise cancellation circuit, and the noise cancellation circuit includes a fifteenth switching transistor 315 and a sixteenth switching transistor 316.

**[0145]** A first end of the fifteenth switching transistor 315 and a first end of the sixteenth switching transistor 316 are connected with a noise cancellation signal Nc.

**[0146]** A second end of the fifteenth switching transistor 315 is connected with the second end of the fifth switching transistor 305, and a third end of the fifteenth switching transistor 315 is connected with the first end of the fifth switching transistor 305.

**[0147]** A second end of the sixteenth switching transistor 316 is connected with the second end of the sixth switching transistor 306, and a third end of the sixteenth switching transistor 316 is connected with the first end of the sixth switching transistor 306.

**[0148]** The fifteenth switching transistor 315 and the sixteenth switching transistor 316 are both n-type FETs. Therefore, when the noise cancellation signal is in the second level state, the fifteenth switching transistor 315 and the sixteenth switching transistor 316 are in the on-

45

state, so that the first and third ends of the fifth switching transistor 305 are connected, and the first and third ends of the sixth switching transistor 306 are connected, thereby performing an offset cancellation operation on the fifth switching transistor 305 and the sixth switching transistor 306. In this way, a threshold value difference of the switching transistors in the signal amplification process can be further eliminated, and accuracy of sensing on the signal to be processed in the amplification process can be improved.

[0149] In particular, FIG. 4, FIG. 5 and FIG. 7 are only one alternative circuit structure for the control amplifying circuit. The first switching transistor 301, the second switching transistor 302, the third switching transistor 303, the seventh switching transistor 307 and the eighth switching transistor 308 are P-type channel FETs. The fourth switching transistor 304, the fifth switching transistor 305, the sixth switching transistor 306, the ninth switching transistor 309, the tenth switching transistor 310, the eleventh switching transistor 311, the twelfth switching transistor 312, the thirteenth switching transistor 313, the fourteenth switching transistor 314, the fifteenth switching transistor 315 and the sixteenth switching transistor 316 are N-type channel FETs. Of course, the types of the above switching transistors do not constitute a limitation to the embodiments of the present disclosure. In a practical application scenario, the foregoing circuit control logic may be realized by various types of circuit devices, and may be specifically selected according to the practical application scenario.

[0150] To sum up, in the embodiments of the present disclosure, by adding the power supply switching circuit, the preset power supply signal having two voltage values (the first voltage value or the second voltage value) is provided, and the isolation control circuit may output an isolation control signal having three different voltage values (the first voltage value, the second voltage value, or the third voltage value) according to the preset power supply signal. When the amplifying circuit is in the nonoperating state, the voltage of the preset power supply signal can be dropped to the second voltage value to reduce the leakage phenomenon of the switching transistors in the isolation control circuit, avoid the failure of the switching transistors, and prolong the service life of the isolation control circuit. In addition, in different operation phases of the amplifying circuit, the voltage value of the isolation control signal is adjusted to be the first voltage value or the second voltage value, the noise generated when the potential of the signal to be processed rises is eliminated, the voltage change speed of the signal to be processed is increased, and the signal amplification process is optimized, thereby solving the problems that the signal amplification speed is slow and the circuit noise is high.

**[0151]** In another embodiment of the present disclosure, reference is made to FIG. 8, which illustrates an application scenario diagram of a control amplifying circuit 20 according to an embodiment of the present dis-

closure. As shown in FIG. 8, in this application scenario, there are a bit line Bla, a complementary bit line Blb, a readout bit line saBla, a complementary readout bit line saBlb and a control amplifing circuit 20. A first memory cell 51 is provided on the bit line Bla, and a second memory cell 52 is provided on the complementary bit line Blb. The first memory cell 51 and the second memory cell 52 may both serve as the target detection unit mentioned above.

The control amplifying circuit 20 includes a pow-[0152] er supply output circuit 21, an isolation control circuit 22, a power supply switching circuit 214, an isolation control circuit 22 and an amplifying circuit 23. The power supply output circuit 21 includes a first switching transistor 301 and a second switching transistor 302, and the isolation control circuit 22 includes a third switching transistor 303, a fourth switching transistor 304 and a first inverter 321. The amplifying circuit 23 may include a fifth switching transistor 305, a sixth switching transistor 306, a seventh switching transistor 307, an eighth switching transistor 308, a ninth switching transistor 309, a tenth switching transistor 310, three eleventh switching transistors (an eleventh switching transistor 311-1, an eleventh switching transistor 311-2 and an eleventh switching transistor 311-3 in FIG. 9), three twelfth switching transistors (a twelfth switching transistor 312-1, a twelfth switching transistor 312-2 and a twelfth switching transistor 312-3 in FIG. 9), a thirteenth switching transistor 313, a fourteenth switching transistor 314, three second inverters (a second inverter 322-1, a second inverter 322-2 and a second inverter 322-3 in FIG. 9) and three third inverters (a third inverter 323-1, a third inverter 323-2 and a third inverter 323-3 in FIG. 9). The connection relationship and type of each device are shown in FIG. 9, and the operating principle of its circuit can refer to the above description, which will not be elaborated here.

**[0153]** Based on the above circuit structure, a control method for an amplifying circuit 23 is briefly described. **[0154]** FIG. 9 illustrates a schematic flowchart of a control method for an amplifying circuit according to an embodiment of the present disclosure. As shown in FIG. 9, the method may include the following operations.

**[0155]** In S401, when the amplifying circuit is in a standby phase, an isolation control circuit generates an isolation control signal with a second voltage value, and each node voltage of the amplifying circuit, a first reference signal and a second reference signal maintain a fourth voltage value.

[0156] In such case, the precharge signal is in the second level state, the thirteenth switching transistor 313 and the fourteenth switching transistor 314 are turned on, the first reference control signal and the second reference control signal are connected with the fourth power supply, and each node voltage of the amplifying circuit, the first reference signal and the second reference signal maintain the fourth voltage value. That is, the bit line Bla, the complementary bit line Blb, the readout bit line saBla and the complementary readout bit line saBlb are all at

40

45

the fourth voltage value. Then, the precharge signal is in the first level state, and the thirteenth switching transistor 313 and the fourteenth switching transistor 314 are both turned off.

**[0157]** In S402, when the amplifying circuit is in a first charge sharing phase, a reading process is performed on data stored in a target detection unit to generate a signal to be processed, and the isolation control signal is controlled to maintain a third voltage value.

**[0158]** It should be noted that the target detection unit is turned on according to the operation instruction, and transmits the stored potential to the connected bit line Bla to form the signal to be processed. The amplifying circuit is in the first charge sharing phase.

**[0159]** The power supply output circuit selects the second voltage value to output as a preset power supply signal according to the power supply switching signal, and the isolation control circuit generates the isolation control signal Iso with the third voltage value according to the control command signal in the first state. In such case, since the ninth switching transistor 309 and the tenth switching transistor 310 are in the off-state, the bit line Bla and the target detection unit perform charge sharing, and the potential of the bit line Bla is lower or higher than the fourth voltage value.

**[0160]** In S403, the amplifying circuit receives the signal to be processed and is in a second charge sharing phase, the isolation control signal is controlled to maintain the second voltage value, the first reference signal is controlled to maintain a fifth voltage value, and the second reference signal is controlled to maintain a sixth voltage value.

**[0161]** It should be noted that, after the first charge sharing phase, the potential of the bit line Bla is stabilized, the power supply output circuit selects the second voltage value to output as the preset power supply signal according to the power supply switching signal, the isolation control circuit generates the isolation control signal Iso having the second voltage value according to the control command signal in the second state, and the ninth switching transistor 309 and the tenth switching transistor 310 are turned on.