# (11) EP 4 297 010 A2

(12)

# **EUROPEAN PATENT APPLICATION**

(43) Date of publication: 27.12.2023 Bulletin 2023/52

(21) Application number: 23207965.7

(22) Date of filing: 28.07.2020

(51) International Patent Classification (IPC): G09G 5/12 (2006.01)

(52) Cooperative Patent Classification (CPC): **G09G 3/32; G09G 3/3233; G09G 3/3291;**G09G 3/2022; G09G 2300/0857; G09G 2320/0673;

G09G 2330/12; G09G 2370/08

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

(30) Priority: 15.10.2019 KR 20190127865

(62) Document number(s) of the earlier application(s) in accordance with Art. 76 EPC: 20877953.8 / 3 971 881

(71) Applicant: Sapien Semiconductors Inc.

Ulju-gun

Ulsan 44919 (KR)

(72) Inventors:

- LEE, Jae Hoon 46230 Busan (KR)

- JANG, Jin Woong 16679 Gyeonggi-do (KR)

- (74) Representative: Vossius & Partner Patentanwälte Rechtsanwälte mbB Siebertstrasse 3 81675 München (DE)

### Remarks:

This application was filed on 06.11.2023 as a divisional application to the application mentioned under INID code 62.

# (54) MICRO DISPLAY DEVICE, DATA DRIVING CIRCUIT, AND METHOD FOR INSPECTING SAME

A display device comprising a pixel unit including a plurality of pixels, each including a luminous element and a pixel circuit connected to the luminous element; a clock generator configured to generate a plurality of clock signals each corresponding to each of a plurality of subframes constituting a frame; and a parallel to serial converter configured to convert the plurality of clock signals to a serial clock signal and transfer the serial clock signal to the pixel unit; and wherein the pixel circuit of each pixel includes a first pixel circuit configured to control light-emission and non-emission of the luminous element in response to a control signal applied to each of the plurality of subframes; and a second pixel circuit configured to store bit values of image data in the frame and generate the control signal based on the stored bit values and the serial clock signal such that each subframe included in the frame is controlled according to each bit value.

FIG. 1

EP 4 297 010 A2

#### **CROSS-REFERENCE TO RELATED APPLICATIONS**

1

**[0001]** This application is a 371 National Stage of International Application No. PCT/KR2020/009942, filed July 28, 2020, which claims priority to Korean Patent Application No. 10-2019-0127865, filed October 15, 2019, the disclosures of which are herein incorporated by reference in their entirety.

#### **FIELD OF THE INVENTION**

**[0002]** Aspect(s) of the present invention relates to a data drive circuit and a display device including the data drive circuit. In addition, aspects of the present disclosure related to a micro-display device and its checking method thereof. In addition, aspect(s) of the present invention related to a device having a Memory Inside Pixel (MIP) display.

#### **BACKGROUND OF THE INVENTION**

**[0003]** As an information society develops, the demand for display devices to display images is increasing, and various types of display devices such as liquid crystal display devices, plasma display devices, organic light illumination display devices, etc. are being utilized. In recent years, interest in display devices using micro light emitting diodes ( $\mu$ LED) (hereinafter referred to as "microdisplays") has also increased.

**[0004]** With the need for excellent display characteristics for Virtual Reality (VR), Augmented Reality (AR), and Mixed Reality (MR) technologies, the development of micro LED on Silicon or AMOLED on Silicon is increasing, especially for high-resolution implementations, and the demand for minimizing pixel sizes is increasing.

**[0005]** In addition, with the rapid growth of the AR and MR markets in recent years, the growth of the microdisplay (or micro display) market with Cu-Cu bonding and micro-LEDs is expected due to its low power consumption characteristics and excellent luminance characteristics.

**[0006]** For pulse width modulation PWM drive of pixel circuits with built-in memory, a large number of wirings are required in the display activation area because a connection is required to the pixel circuit for a large number of gray scale representation signals. Therefore, in order to test the defective bonding conventionally, in particular, a large display panel with a separate pixel drive circuit (IC) and scan/data driver drive circuit (Scan / Data Driver IC) requires a number of input PADs in the pixel drive circuit

**[0007]** As such, when a number of micro light emitting devices (LEDs) are joined and attached to one display device as the display resolution increases, it is necessary to take measures against this because a defective bonding inevitably occurs. In order to determine existence of

a pixel containing a defective bonding of a micro light emitting device, information about the pixel containing the defective bonding is required.

**[0008]** Conventionally, there is a method of placing daisy chains in the micro-display adjacent area and indirectly checking the joining characteristics, but there is a disadvantage that it is impossible to determine the exact bad bonding position. In addition, the Mobile Industry Processor Interface (MIPI) is a Preferred Display Standard for Portable Electronic Devices, Supporting Two Display Standards: Video Mode and Command Mode.

**[0009]** In addition, the mobile industry processor interface (MIPI<sup>®</sup>) is a recent display standard for portable electronic devices, supporting two display standards: video mode and command mode.

**[0010]** In video mode, frame data is transmitted from the host to the display driver IC in real time. In the video mode, even if the image to be transmitted to the display driver IC is a still image, the host continues to transmit the same still image to the display driver IC. Thus, the power consumption of the host increases.

**[0011]** In a command mode, a start of the transmission of frame data is controlled by a tearing effect TE signal. When displaying a still image on the display, the display driving integrated circuit (IC) may periodically read the still image stored in the frame buffer embedded in the display driving IC and transmit the read still image to the display. This operation is called a panel self-refresh. However, the command mode may have the disadvantage that the size and price of IC development are affected because there must be additional frame memory.

**[0012]** On the other hand, the conventional display, as described above, must be continuously refreshed to maintain the output of the still image, while the memory inside pixel (MIP) display has memory in each pixel, so that the image can be displayed once and then displayed without a screen refresh.

**[0013]** When driving video mode in a MIP environment, the host may continue to transmit data to the display driving IC, which adds to the burden on the host and increases the host's power consumption. In addition, when driving in the command mode in the MIP environment, the transmission amount cannot be predicted, so there may be a disadvantage that additional memory is required to implement it.

# DETAILED DESCRIPTIONS OF THE EMBODIMENT

# **TECHNICAL PROBLEMS TO BE SOLVED**

**[0014]** Aspect(s) of the present invention is to provide a data driver and a display device including the data driving circuit, which accurately implement gamma characteristics even in process changes by implementing a gamma circuit matched with a pixel circuit.

**[0015]** In addition, Aspect(s) the present invention is provided to the above-described necessity, for the purpose of providing a micro LED display and a method of

35

40

45

checking thereof to determine whether the pixel is defective for the result of performing the bonding of the micro LED display device substrate and the CMOS driver substrate.

**[0016]** In addition, aspect(s) of the present invention provides an electronic device and the method thereof for improving power consumption in a memory inside pixel (MIP) display.

**[0017]** However, this problem is exemplary, and the scope of the present invention is not limited thereto.

**[0018]** A data driver according to one embodiment of the present invention may include a reference current generation circuit that generates a reference current corresponding to a predetermined brightness; a gamma current generator including a plurality of transistors of different sizes operated by the reference current and a current mirror, configured to convert the reference current into a first to M gamma current and output; a reference gamma voltage generation circuit configured to convert the first to the first M gamma current into the first to the M<sup>th</sup> reference gamma voltages;

a gamma voltage generation circuit configured to convert the first to the Mth reference gamma voltages into a first to a Mth gamma voltages; and a divider configured to generate the first to M gamma voltages by dividing the first to N gamma buffer voltage

**[0019]** The gamma current generation circuit may include the first to the Mth transistors outputting the first to the Mth gamma currents, respectively. Each of the first to the Mth transistors may be composed of one or more transistors of the same or different sizes connected in series and/or parallel.

**[0020]** The reference gamma voltage generation circuit may include the first to the Mth transistors, and the first to the Mth transistors may have the same size as the drive transistors of the pixels. Each gate voltage of each of the first to the Mth transistors may be the first to the Mth reference gamma voltages, respectively.

[0021] A micro display device according to an embodiment of the present invention may include: a plurality of pixels arranged in a display area; and a power supply provided around the display area and outputting a power voltage to a power line connected to the plurality of pixels; wherein each of the plurality of pixels includes a first electrode and a second electrode, at least one light emitting device having a first electrode connected to the power line; and an AND gate connected to an input terminal of the second electrode of the at least one light emitting device, an input terminal of a first AND gate included in a first pixel among the plurality of pixels receives a node voltage and a test pulse signal applied to a second electrode of at least one emitting device included in the first pixel; an output terminal of the first AND gate outputs an operation result obtained by performing an AND operation based on the node voltage and the test pulse signal,

the operation result may be transmitted by being connected to an input terminal of a second AND gate included in a second pixel arranged adjacent to the same row as the first pixel among the plurality of pixels.

[0022] In addition, the micro display device may include: a measuring unit for measuring current to test whether bonding is defective; a first switch for connecting the plurality of pixels arranged in the display area in a row unit; and a second switch for sequentially connecting the plurality of pixels arranged in the display area in units of columns, wherein the measurement unit may measure a current corresponding to an AND gate operation result by sequentially connecting a plurality of pixels included in a row to which the first switch is connected through the second switch.

**[0023]** In addition, the display area is separated into a predetermined number of sub-regions of the column nit, the second switch is provided for each of the sub-regions, and the first switch may be connected sequentially to each of the sub-regions for a plurality of pixels contained in the connected row.

[0024] In addition, the micro-display may include: a checking unit configured to test for defects in the pixel circuit; and a third switch; connected to the checking unit, the first switch includes a first pole and a second pole, the first pole is connected to the second electrode of the plurality of light emitting devices, the second switch connects the measuring unit and the second pole of the first switch, the third switch configured to connect the second pole of the first switch with the checking unit, the measuring unit may test whether the bonding is defective based on the current flowing through the first switch and the second switch by turning on the first switch and the second switch in the first checking mode; and the checking unit may test the defect of the pixel circuit based on the current flowing through the first switch and the third switch by turning on the first switch and the third switch in the second checking mode.

[0025] The electronic device according to an embodiment of the present invention may include: a controller configured to receive a first video data including at least one or more bit values, generate clock signals having different assigned periods corresponding to each of the at least one or more bit values in the order of least significant bit (LSB) to most significant bit (MSB), and determine control data by reading each of the at least one or more bit values from a first memory in response to each of the generated clock signals; a first memory configured to store at least one bit value of the first video data; and a circuit including a pixel circuit configured to control light emission of a pixel (PX) based on the control data.

**[0026]** Other aspects, features and advantages other than those described above will become apparent from the following detailed description, claims and drawings for carrying out the invention.

20

25

# **[0027]** According to one embodiment of the present invention, a data driving circuit and a display device, which includes the data driving circuit may provide accu-

5

which includes the data driving circuit may provide accurately gamma characteristics even in process changes by implementing gamma circuits matched with pixel circuits

**[0028]** According to an embodiment of the present invention, it is possible to easily detect the defective bonding of micro-LEDs, thereby improving other productivity. In addition, it may be possible to determine the exact defect bonding position when performing repair operation, thereby improving yield.

**[0029]** In addition, according to an embodiment of the present invention, by adjusting a position of the most significant bit (MSB) and the least significant bit (LSB) of the bit string in the data displayed by pulse width module (PWM) drive, and adding a separate storage device for the MSB to which a relatively long time is assigned to the bit string reading, thereby it is possible to reduce the power consumption at a system level of the device.

**[0030]** In addition, according to an embodiment of the present invention, in the mobile industry processor interface (MIPI) command mode (MIPI) where the writing rate is fast in memory, a memory inside pixel (MIP) may avoid problems that can be caused by differences between bit string reading time and data writing time stored in memory in memory circuitry (e.g., screen tearing).

**[0031]** It will be appreciated by persons skilled in the art that that the effects that could be achieved with the present invention are not limited to what has been particularly described hereinabove and other advantages of the present invention will be more clearly understood from the following detailed description taken in conjunction with the accompanying drawings.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

**[0032]** The above and other aspects, features, and advantages of certain embodiments of the disclosure will be more apparent from the following description taken in conjunction with the accompanying drawings, in which:

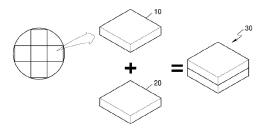

FIG. 1 is a schematic view shows the manufacturing process of the display device according to some embodiments.

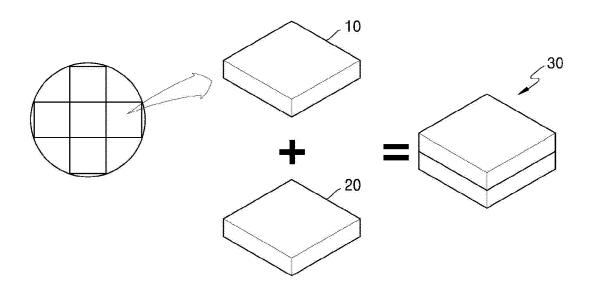

FIG. 2 is a view schematic view shows a display device according to some embodiments.

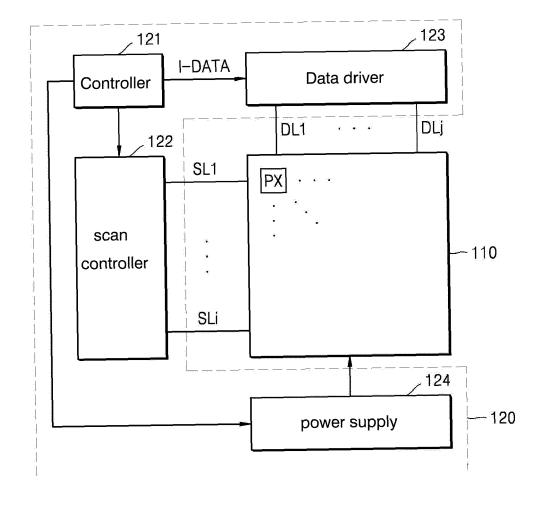

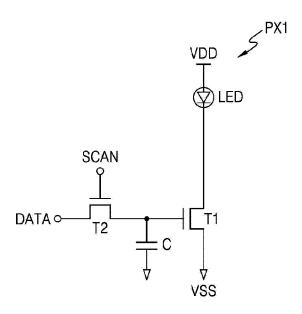

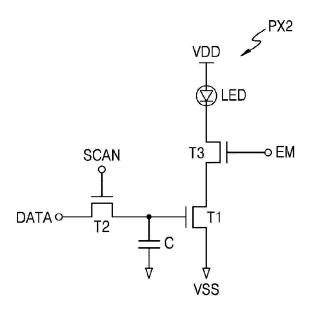

FIGS. 3 and 4 are examples of pixels of display devices shown in FIG. 2.

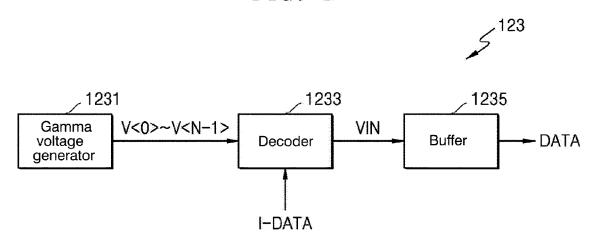

FIG. 5 is a schematic view shows a data driver according to some embodiments.

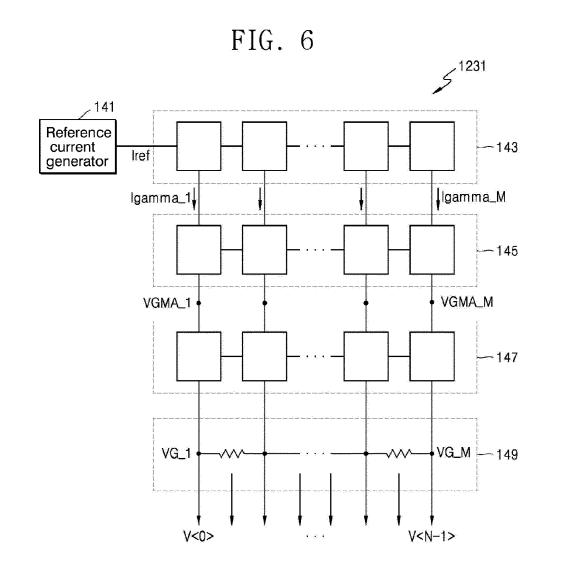

FIG. 6 is a schematic view shows a gamma voltage generator according to some embodiments.

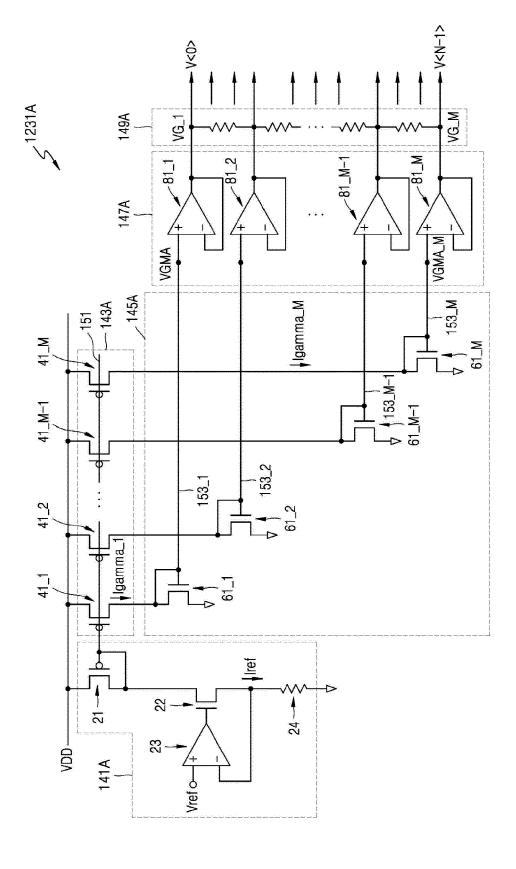

FIG. 7 is a schematic view shows the gamma voltage generator according to some embodiments.

FIGS. 8 and 9 are shows a schematic view of the

gamma voltage generator according to some embodiments.

FIG. 10 is a schematic view shows a display device according to some embodiments.

FIG. 11 is a block degree for explaining how to check whether a row (line) unit defect according to some embodiments.

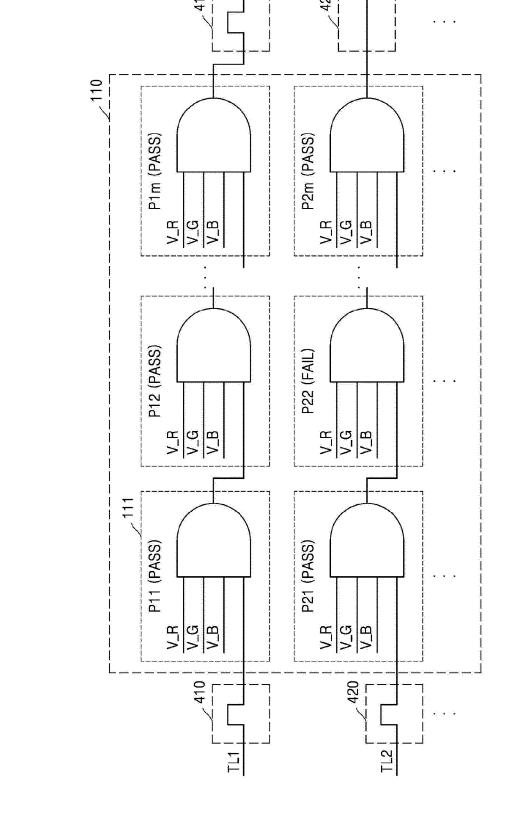

FIG. 12 is a drawing for describing a gate chain of the pixel unit according to some embodiments.

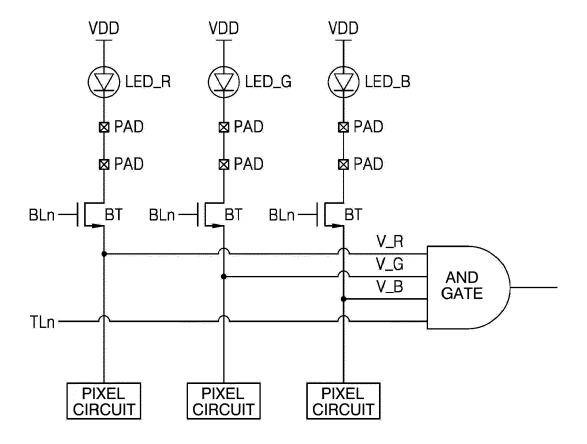

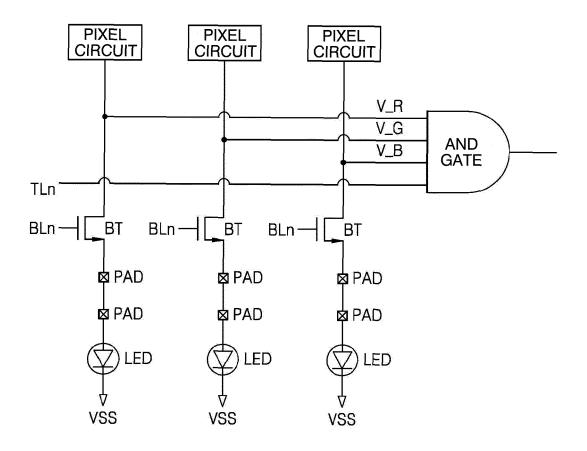

FIG. 13a and FIG. 13b is figures for describing the structure of the gate of the pixel circuit according to some embodiments.

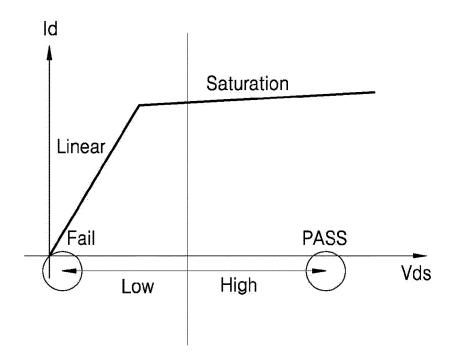

FIG. 14 shows a voltage-current graph in a common anode type to illustrate the operation of the gate of the pixel circuit according to some embodiments.

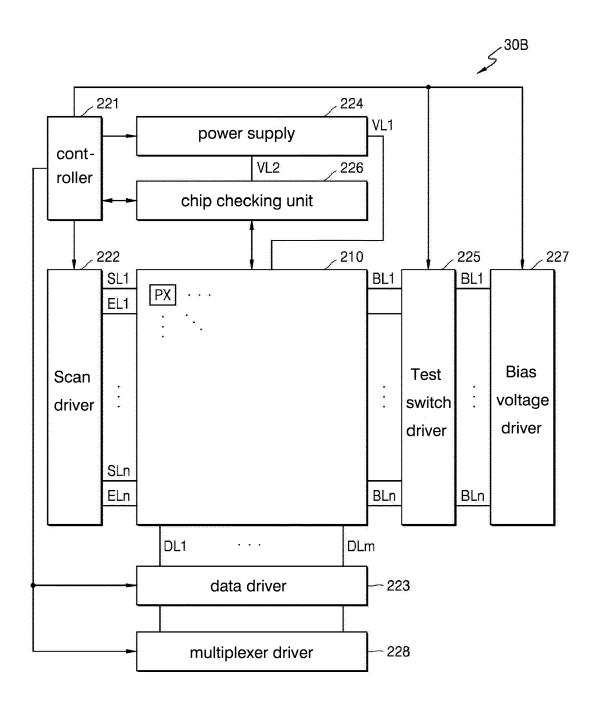

FIG. 15 is a schematic view showing a display device 30B inspecting a defective pixel based on the current according to some embodiments.

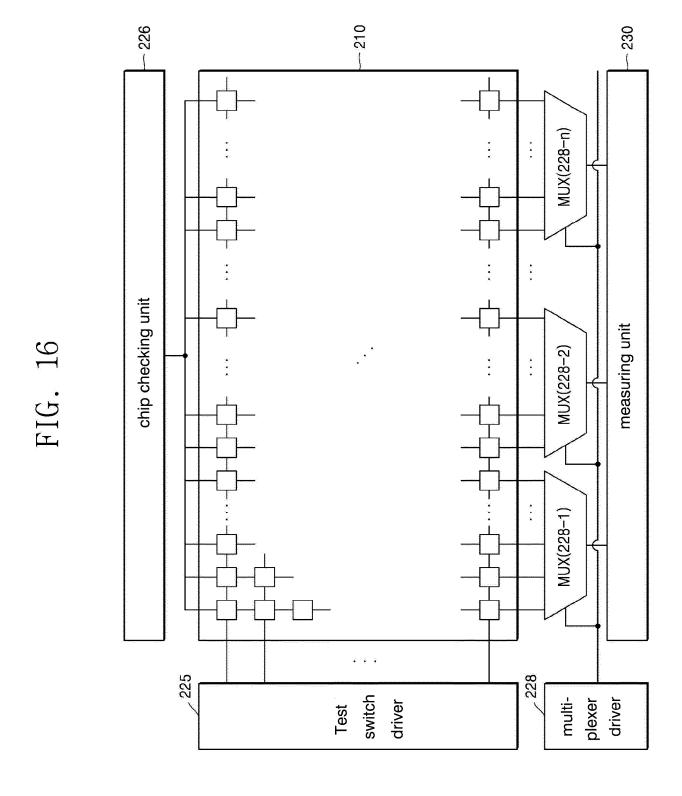

FIG. 16 is a diagram describing a configuration for driving the checking mode according to some embodiments.

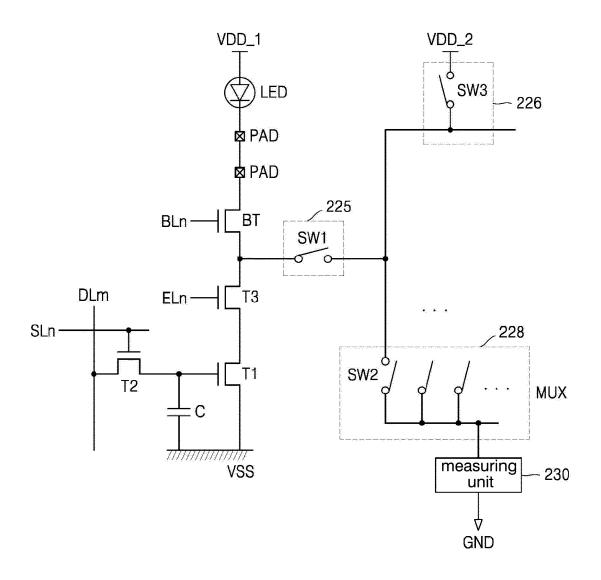

FIG. 17 is an example of a pixel of a display device 30B according to some embodiments.

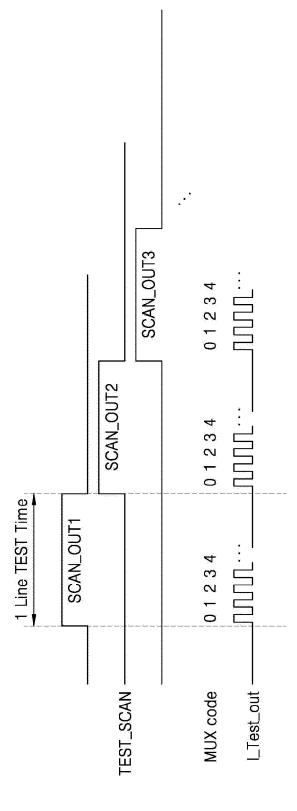

FIG. 18 is a timing degree for explaining the timing in the first checking mode according to some embodiments.

FIG. 19 is an example of an electronic device according to some embodiments.

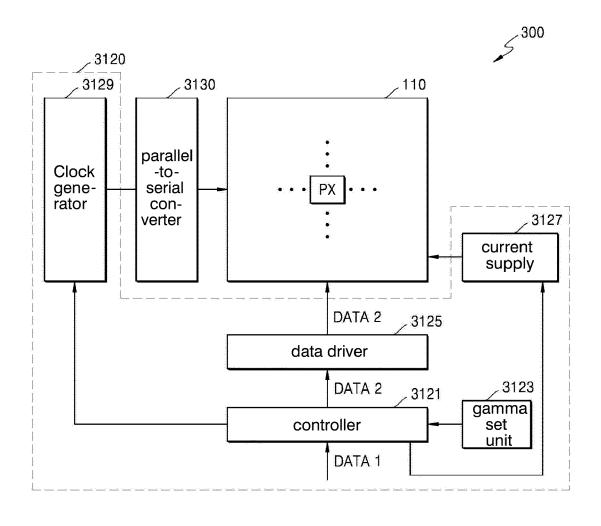

FIG. 20 is another example of an electronic device according to some embodiments.

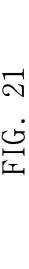

FIG. 21 illustrates a schematic for driving a current supply, pixel (PX) of an electronic device according to some embodiments.

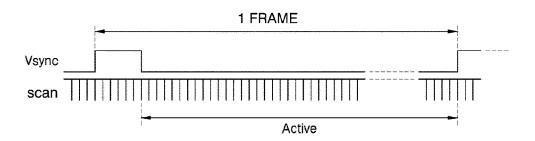

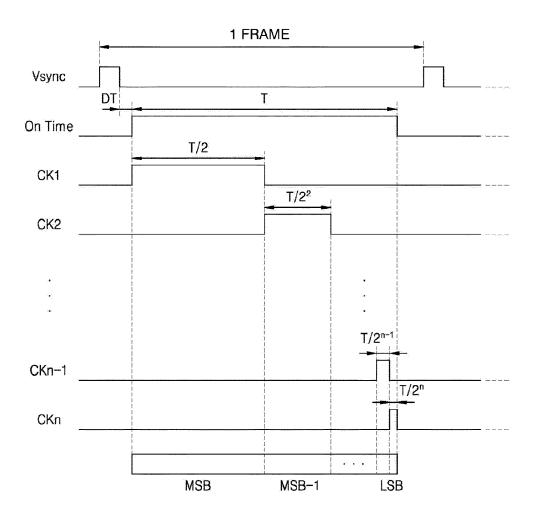

FIG. 22 is an example showing the driving timing of a general clock signal according to some embodiments

FIG. 23 is another example showing the driving timing of a general clock signal according to some embodiments.

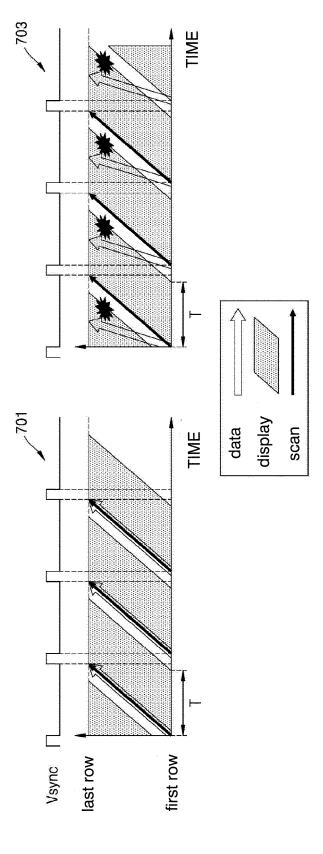

FIG. 24 is an example of a display operation in a mobile industry processor interface (MPIP) video mode (video mode) and a command mode according to clock signal drive according to some embodiments.

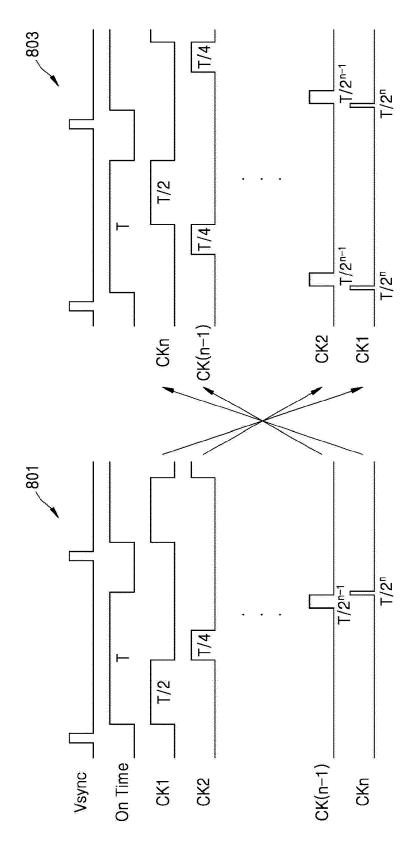

FIG. 25 is an example of an operation according to the clock signal drive timing change according to some embodiments.

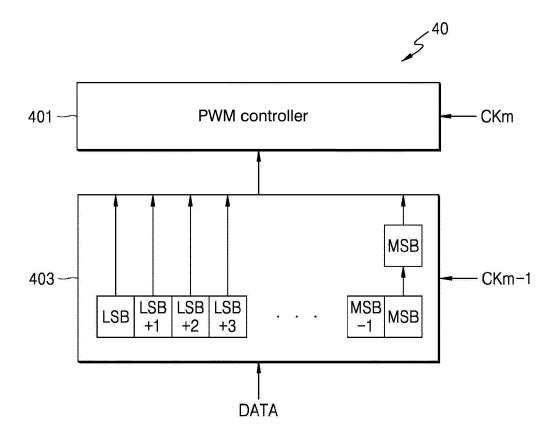

FIG. 26 is an example of an electronic device including additional memory in a memory inside pixel (MIP) circuit according to some embodiments.

# Best Mode for Carrying out the Invention

**[0033]** The electronic device according to an embodiment of the present invention may include: a controller configured to receive a first video data including at least one or more bit values, generate clock signals having different assigned periods corresponding to each of the

45

at least one or more bit values in the order of least significant bit (LSB) to most significant bit (MSB), and determine control data by reading each of the at least one or more bit values from a first memory in response to each of the generated clock signals; a first memory configured to store at least one bit value of the first video data; and a circuit including a pixel circuit configured to control light emission of a pixel (PX) based on the control data

#### Modes for carrying out the invention

**[0034]** Since the present invention can apply various transformations and can have various embodiments, specific embodiments are illustrated in the drawings and described in detail in the detailed description. Effects and features of the present invention, and a method of achieving them, will become apparent with reference to the embodiments described below in detail in conjunction with the drawings. However, the present invention is not limited to the embodiments disclosed below and may be implemented in various forms.

**[0035]** Hereinafter, embodiments of the present invention will be described in detail with reference to the accompanying drawings, and when described with reference to the drawings, the same or corresponding components are given the same reference numerals, and the overlapping description thereof will be omitted.

**[0036]** In the following description, terms such as first, second, and the like are used for the purpose of distinguishing one component from another, not in a limiting sense. Also, in the following description, the singular expression may include the plural expression unless the context clearly dictates otherwise.

[0037] In the following description, when X and Y are connected, X and Y are electrically connected, X and Y are functionally connected, and X and Y are directly connected. have. Here, X and Y may be objects (eg, devices, elements, circuits, wirings, electrodes, terminals, conductive films, layers, etc.). Therefore, it is not limited to a predetermined connection relationship, for example, the connection relationship shown in the drawings or detailed description, and may include other than the connection relationship shown in the drawings or detailed description.

**[0038]** When X and Y are electrically connected, for example, an element (for example, a switch, a transistor, a capacitor, an inductor, a resistance element, a diode, etc.) that enables the electric connection of X and Y, it may include a case where one or more connections are made between X and Y.

**[0039]** When X and Y are functionally connected, a circuit that enables the functional connection of X and Y (for example, a logic circuit (OR gate, inverter, etc.), signal conversion circuits (AD conversion circuits, gamma correction circuits, etc.), potential level conversion circuits (level shifter circuits, etc.), current supply circuits, amplifier circuits (circuits that can increase signal ampli-

tude or current amount, etc.), signal generation circuits, a case in which one or more memory circuits (memory, etc.) are connected between X and Y may be included. **[0040]** In the following description, "ON" used in connection with a device state may refer to an activated state of a device, and "OFF" may refer to an inactive state of a device. As used in connection with a signal received by a device, "on" may refer to a signal that activates a device, and "off" refers to a signal that deactivates a device. The device can be activated by a high voltage or a low voltage. For example, a P-type transistor is activated by a low voltage, and an N-type transistor is activated by a high voltage. Accordingly, it should be understood that the "on" voltages for a P-type and N-type transistor are opposite (low vs. high) voltage levels.

**[0041]** A term that refers to a variable (e.g., a parameter) related to the display of data used in the following description, and an object (e.g., an electronic device, a display device, a display device, etc.) used to perform the operation of the invention. Terms referring to components of the device (e.g., circuit, pixel circuit, pixel, driving circuit, controller, processor, controller, etc.) are exemplified for convenience of description. Accordingly, the present disclosure is not limited to the terms described below, and other terms having equivalent technical meanings may be used. In the following description, terms such as include or have means that a feature or element described in the specification is present, and the possibility that one or more other features or elements may be added is not excluded in advance.

**[0042]** FIG. 1 is a schematic view showing the manufacturing process of the display device according to some embodiments.

**[0043]** Referring to FIG. 1, the display device 30 may include a light emitting device array 10 and a drive circuit board 20. The light emitting device array 10 may be combined with the drive circuit substrate 20. The display device 30 may be a micro display device.

[0044] The light emitting device array 10 may include a plurality of light emitting devices. The emitting device may be a light emitting diode (LED). The light emitting device may be a light emitting diode (LED) of a micro to a nano-unit size. At least one light emitting device array 10 may be prepared by growing a plurality of light emitting diodes on the semiconductor wafer (SW). Thus, the display device 30 may be prepared by combining the light emitting device array 10 with the drive circuit substrate 20 without having to transfer the light emitting diode individually to the drive circuit substrate 20.

**[0045]** The driving circuit board 20 may be a Si-CMOS substrate in which pixel circuits corresponding to each of the light emitting diodes on the light emitting device array 10 and independently controlling the light emitting diodes are arranged. A pixel circuit may include at least one transistor and at least one capacitor.

**[0046]** Micro LEDs may require a high processing temperature of 1000 °C or more and cannot be directly grown and patterned on top of the transistor of the drive circuit

board 20. A pixel may be formed by connecting light emitting device array 10 and the pixel circuit of the drive circuit substrate 20 electrically by combining after respectively forming a pixel circuit array on the light emitting device array 10 and the drive circuit substrate 20 according to an embodiment of the present invention. At this time, the exact arrangement of the pixel circuit array and the light emitting diode array is important.

[0047] The pixel circuit on the light emitting diode and the drive circuit board 20 on the light emitting device array 10 may be electrically connected to configure the pixel (PX). FIG. 2 is a view that outlines the display device according to some embodiments. Referring to FIG. 2, the display device 30 may include a pixel unit 110 and a driver 120.

**[0048]** The pixel unit 110 may display the image using a m-bit digital image signal that can display a one to 2<sup>m</sup> gradation levels. The pixel unit 110 may be placed in the display area displaying the image. The pixel unit 110 may include a predetermined pattern, for example, a matrix type, a plurality of pixels PX arranged in various patterns such as zigzag type. Pixels PX may emit one color, for example, emit the color of one of red, blue, green, or white. Pixels (PX) may emit other colors other than red, blue, green, and white.

**[0049]** Pixels (PX) may include light emitting devices. The light emitting device may be a self-illuminating device. For example, the light emitting device may be an inorganic light emitting diode (LED). The light emitting device may be a micro light emitting diode (LED). The light emitting device may emit a single peak wavelength or a plurality of peak wavelengths.

**[0050]** Pixel (PX) may further include a pixel circuit connected to a light emitting device. The pixel circuit may include at least one transistor and at least one capacitor. Transistors may be CMOS transistors.

**[0051]** The pixel unit 110 may include scan lines SL1 -SLi applying the scan signal to the pixel PX and a data line DL1-DLj applying the data signal to the pixels PX. The pixel unit 110 may further include a light emitting control line applying a light emitting control signal (see EM, FIG. 4) to the pixel PX.

**[0052]** Scan lines SL1-SLi are connected to pixels PX arranged in the same row, and the data lines DL1-DLj each may be connected to the pixels PX arranged in the same column. Light emitting control lines may be connected to pixels PX arranged in the same row.

**[0053]** The driver 120 is provided in the undisplay area around the pixel unit 110, and the pixel unit 110 may be driven and controlled. The driver 120 may include a controller 121, a scan driver 122, a data driver 123 and a power supply 124.

**[0054]** Under the control of the controller 121, the scan driver 122 may sequentially apply a scan signal to the scan lines SL1-SLi, and the data driver 123 may apply the data signal to each pixel PX. According to the control of the controller 121, the scan driver 122 may sequentially apply the light emitting control signal to the light emitting

control lines. The pixels PX may emit light with a brightness corresponding to the voltage level or current level of the data signal received through the data lines DL1-DLj in response to the scan signal received through the scan lines SL1-SLi.

**[0055]** The power supply 124 may receive an external power source and/or an internal power supply apply and converts it to a voltage of various levels necessary for the operation of each component, and the voltage may be supplied to the pixel unit 110 according to the power control signal input from the controller 121.

**[0056]** The power supply 124 may apply the first power voltage (VDD) to the pixel unit 110. The power supply 124 may generate a drive voltage and apply it to the scan driver 122 and the data driver 123.

[0057] The controller 121, the scan driver 122, the data driver 123, and the power supply 124 are each formed in the form of a separate integrated circuit chip or one integrated circuit chip and are mounted directly on the substrate where the pixel unit 110 is formed. Or The controller 121, the scan driver 122, the data driver 123, and the power supply 124 may be mounted on a flexible printed circuit film or attached to a substrate in the form of a tape carrier package (TCP).

[0058] FIG. 3 and FIG. 4 are examples of the pixel of the display device shown in FIG. 2.

[0059] Referring to FIG. 3, the pixel PX1 may be connected to a scan line SL, a data line DL, and a power line. [0060] The scan line may transmit a scan signal. The data line intersecting with the scan line may transmit a data signal. The power line may transmit the first power voltage (VDD).

**[0061]** The pixel (PX1) may include the light emitting diode (LED) and a pixel circuit connected to the light emitting diode (LED). The pixel circuit may include the first transistor T1 and the second transistors T2, and capacitors C.

[0062] The first transistor T1 may include a gate electrode connected to the first electrode of the capacitor C, a first electrode connected to the light emitting diode LED, and a second electrode connected to the second power voltage VSS. The second power voltage VSS may be a ground voltage GND. The first transistor T1 may serve as a driving transistor, and may receive a data signal according to a switching operation of the second transistor T2 to supply current to the light emitting diode LED. [0063] The second transistor T2 may include a gate electrode connected to the scan line SL, a first electrode connected to the data line DL, and a second electrode connected to the gate electrode of the first transistor T1. The second transistor T2 may be turned on according to the scan signal SCAN transmitted through the scan line SL, transmit the data signal DATA transmitted through the data line DL to the gate of the first transistor T1, and act as a switching transistor.

**[0064]** The capacitor C may include a first electrode connected to the gate electrode of the first transistor T1, and a second electrode connected to the second power

40

45

voltage VSS.

**[0065]** The first electrode of the light emitting diode LED may receive the first power voltage VDD from the power line. The second electrode of the light emitting diode LED may be connected to the first electrode of the first transistor T1. The light emitting diode LED may display an image by emitting light with a luminance corresponding to the data signal.

[0066] Referring to FIG. 4, a pixel PX2 may include a third transistor T3 between the first transistor T1 and the light emitting diode LED in the pixel PX1 shown in FIG. 3. [0067] The third transistor T3 may include a gate electrode connected to the light emitting control line, a first electrode connected to the second electrode of the light emitting diode LED, and a second electrode connected to the first electrode of the first transistor T1.

[0068] The third transistor T3 may be turned on according to a light emitting control signal EM received through the light emitting control line to allow the driving current of the first transistor T1 to flow through the light emitting diode LED. In FIG. 2, the light emitting control line is connected to the scan driver 122. The light emitting control line may receive the light emitting control signal EM from the scan driver 122.

**[0069]** The light emitting control line may be connected to a light emitting control driver (not shown) separate from the scan driver 122 to receive the light emitting control signal EM according to an embodiment.

**[0070]** FIG. 5 is a schematic diagram illustrating a data driver according to some exemplary embodiments.

**[0071]** Referring to FIG. 5, the data driver 123 may include a gamma voltage generator 1231, a decoder 1233, and a buffer 1235.

[0072] The gamma voltage generator 1231 may generate a plurality of gamma voltages V<0> to V<N-1> (N is a natural number). According to an embodiment, the gamma voltage generator 1231 may generate an arbitrary number of gamma voltages. For example, the gamma voltage generator 1231 may generate gamma voltages V<0> to V<255> having 256 gray levels. In another embodiment, the gamma voltage generator 1231 may generate gamma voltages V<0> to V<1023> having 1024 grayscale levels.

[0073] The decoder 1233 may receive input data I\_DATA from the controller 121 and gamma voltages V<0> to V<N-1> from the gamma voltage generator 1231. The decoder 1233 may select one of the plurality of gamma voltages V<0> to V<N-1> based on the input data I\_DATA and output it as the input voltage VIN. The decoder 1233 may be configured for each channel corresponding to each of the data lines DL1 to DLj. The buffer 1235 may generate a data signal DATA corresponding to the input voltage VIN and output the data signal DATA to the data lines DL1 to DLj. The buffer 1235 may be configured for each channel corresponding to each of the data lines DL1 to DLj. The buffer 1235 may output the data signal DATA to a corresponding data line among the plurality of data lines DL1 to DLj.

**[0074]** FIG. 6 shows a schematic diagram illustrating a gamma voltage generator according to some exemplary embodiments.

**[0075]** Referring to FIG. 6, the gamma voltage generator 1231 may include a reference current generator circuit 141, a gamma current generator circuit 143, a reference gamma voltage generator circuit 145, and a gamma voltage generator circuit 147, and a divider 149 according to an embodiment of the present invention.

[0076] The reference current generation circuit 141 may generate a reference current lref. The reference current generation circuit 141 may generate a reference current lref corresponding to the brightness set in the display device.

[0077] The gamma current generating circuit 143 may generate first to Mth gamma currents lgamma\_1 to lgamma\_M (M is a natural number, M≤N) based on the reference current lref. For example, M may be 13 and N may be 256. The first to Mth gamma currents lgamma\_1 to lgamma\_M may be currents corresponding to M gamma voltages among the gamma voltages V<0> to V<N-1>, respectively.

**[0078]** The reference gamma voltage generation circuit 145 may output the first to Mth reference gamma voltages VGMA\_1 to VGMA\_M corresponding to the first to Mth gamma currents lgamma\_1 to lgamma\_M output from the gamma current generation circuit 143.

**[0079]** The gamma voltage generating circuit 147 may buffer the first to Mth reference gamma voltages VGMA\_1 to VGMA\_M to output the first to Mth gamma buffer voltages VG\_1 to VG\_M. The gamma voltage generation circuit 147 may include a plurality of voltage followers for providing a stabilized voltage.

[0080] The divider 149 may be formed of a resistor string. The divider 149 may generate and output the first to the Nth gamma voltages V<0>,..., V<N-1>) by dividing the voltages between the first to Mth gamma buffer voltages VG\_1 to VG\_M output from the gamma voltage generating circuit 147. For example, when outputting 256 gamma voltages, the divider 149 may generate a first gamma voltage V<0> to a 255th gamma voltage V<255>.

[0081] FIG. 7 is a schematic diagram illustrating a gamma voltage generator according to some exemplary embodiments.

[0082] Referring to FIG. 7, the gamma voltage generator 1231A may include a reference current generator circuit 141A, a gamma current generator circuit 143A, a reference gamma voltage generator circuit 145A, a gamma voltage generator circuit 147A, and a divider 149A.

[0083] The reference current generation circuit 141A

may include a first transistor 21, a second transistor 22, an operational amplifier 23, and a resistor 24. The first transistor 21 may include a gate connected to the first control line 151, a first terminal connected to a source of the first power voltage VDD, and a second terminal connected to a gate and a first terminal of the second transistor 22

[0084] The second transistor 22 has a gate connected

to the output terminal of the operational amplifier 23, a first terminal connected to a second terminal of the first transistor 21, and a second terminal connected to the second terminal (-) of the operational amplifier 23.

[0085] The first input terminal (+) of the operational amplifier 23 is connected to a source of the reference voltage Vref, and the second input terminal (-) is connected to the resistor 24. The output terminal of the operational amplifier 23 is connected to a gate of the second transistor 22. When the reference voltage Vref is applied to the first input terminal (+), the second transistor 22 may be turned on or off according to a voltage of the output terminal due to a voltage difference between the second input terminal (-) and the output terminal. The reference voltage Vref may have a value corresponding to a predetermined brightness (luminance).

**[0086]** In the operational amplifier 23 may determine the output terminal voltage is determined according to the reference voltage Vref and the resistance value of the resistor 24, and determine may determine the reference current Iref flowing through the first transistor 21 and the second transistor 22 turned on from the first power voltage VDD.

**[0087]** The reference current generation circuit 141A may supply the reference current lref to the gamma current generation circuit 143A by forming a current mirror with the gamma current generation circuit 143A.

[0088] Although the above-described embodiment shows an example in which the reference current generation circuit 141A includes the first transistor 21 implemented as a P-type transistor and the second transistor 22 implemented as an N-type transistor, an embodiment of the present invention is not limited an example thereto, and the reference current generation circuit 141A may be configured by implementing the first transistor 21 and the second transistor 22 as different types of transistors, and configuring an operational amplifier corresponding thereto.

**[0089]** The gamma current generation circuit 143A may generate the first to the Mth gamma currents Igamma\_1 to Igamma\_M based on the reference current Iref. The gamma current generation circuit 143A may include the first to the Mth transistors 41\_1 to 41\_M. The first to the Mth transistors 41\_1 to 41\_M may be implemented as P-type transistors.

**[0090]** Each of the first to the Mth transistors 41\_1 to 41\_M may include a gate connected to the first control line 151, a first terminal connected to a source of the first power voltage VDD, and a second terminal connected to a reference gamma voltage generating circuit 145A. The first to the Mth transistors 41\_1 to 41\_M may have different sizes. Here, the size may be a channel length (W/L) for a channel width.

**[0091]** The first to the Mth transistors 41\_1 to 41\_M have a size that can create the first to the Mth gamma currents Igamma\_1 to Igamma\_M corresponding to M gamma voltages among the gamma voltages V<0> to V<N-1>, respectively.

**[0092]** As shown in FIG. 7, each of the first to the Mth transistors 41\_1 to 41\_M is illustrated as one transistor. In another example, each of the first to the Mth transistors 41\_1 to 41\_M may be implemented as one or more transistors under the condition that a predetermined transistor size is satisfied.

[0093] The first to the Mth transistors 41\_1 to 41\_M may constitute the reference current generation circuit 141A and the current mirror circuit, respectively. Accordingly, based on the reference current lref formed in the reference current generation circuit 141A while the first transistor 21 of the reference current generation circuit 141A is turned on, the first to the Mth transistors 41\_1 to 41\_M are the first to the Mth gamma currents lgamma\_1 to lgamma M may be generated, respectively.

[0094] The reference gamma voltage generation circuit 145A is configured to generate the first to the Mth reference gamma voltages VGMA\_1 to VGMA\_M based on the first to the Mth gamma currents Igamma\_1 to Igamma\_M output from the gamma current generation circuit 143A. The reference gamma voltage generation circuit 145A may include the first to the Mth transistors 61\_1 to 61\_M. The first to the Mth transistors 61\_1 to 61\_M may be implemented as N-type transistors.

**[0095]** Each of the first to the Mth transistors 61\_1 to 61\_M may include a gate connected to a corresponding control line of the 2-1 to 2-M control lines 153\_1 to 153\_M, a gamma current generating circuit 143A, a first terminal, and a second terminal connected to the gate.

[0096] The second terminals of the first to the Mth transistors 61\_1 to 61\_M are connected to a power supply that supplies a power voltage (e.g., the second power voltage VSS, a ground voltage, etc.) different from the first power voltage VDD.

[0097] The first to the Mth transistors 61\_1 to 61\_M may have the same size. The first to the Mth transistors 61\_1 to 61\_M may have the same size as the driving transistor T1 of the pixel PX in FIG. 3. The gate voltages of the first to Mth transistors 61\_1 to 61\_M may be the first to the Mth reference gamma voltages VGMA\_1 to VGMA M.

**[0098]** The gamma voltage generating circuit 147A may generate the first to the M<sup>th</sup> gamma buffer voltages VG\_1 to VG\_M based on the first to the M<sup>th</sup> reference gamma voltages VGMA\_1 to VGMA\_M. The gamma voltage generating circuit 147A may include the first to the Mth buffers 81\_1 to 81\_M.

[0099] The first to the Mth buffers 81\_1 to 81\_M may include a first input terminal (+) receiving one of the first to the Mth reference gamma voltages VGMA\_1 to VGMA\_M, an output terminal, a second input terminal (-) connected to the output terminal. The first to Mth buffers 81\_1 to 81\_M may output the first to Mth gamma buffer voltages VG\_1 to VG\_M to respective output terminals. [0100] The divider 149A may be formed of a resistor string. The divider 149A may generate the first to Nth gamma voltages V<0>, ..., V<N-1> through divide volt-

ages between the first to the Mth gamma buffer voltages

VG\_1 to VG\_M output from the gamma voltage generating circuit 147A.

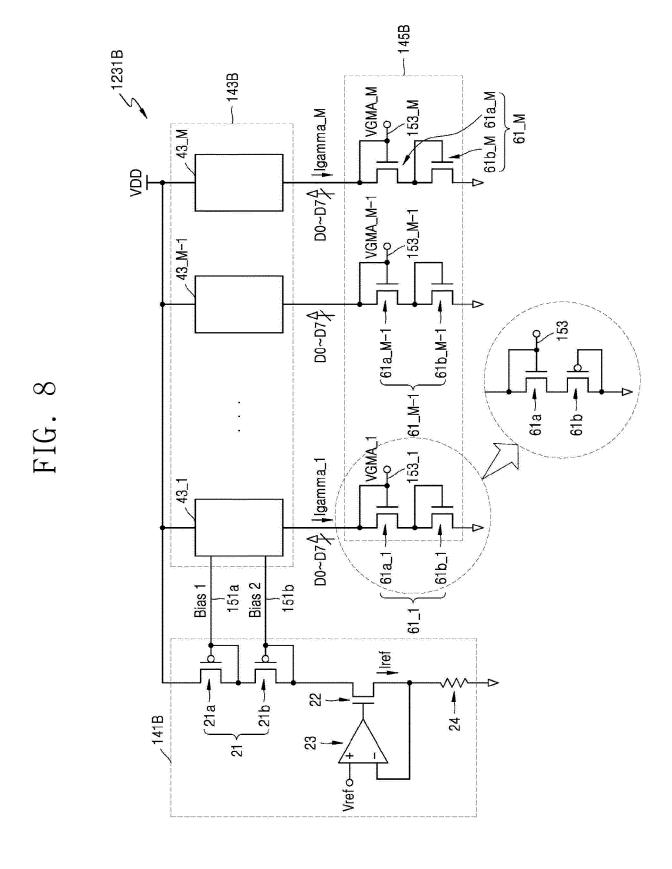

**[0101]** FIGS. 8-9 are schematic diagrams illustrating a gamma voltage generator according to some exemplary embodiments.

[0102] Referring to FIG. 8, the gamma voltage generator 1231B may include a reference current generation circuit 141B, a gamma current generation circuit 143B, and a reference gamma voltage generation circuit 145B. [0103] For convenience of explanation, in FIG. 8, the gamma voltage generation circuit and the divider are omitted. The gamma voltage generation circuit and the divider omitted in FIG. 8 are the same as those of the gamma voltage generating circuit 147A and the divider 149A shown in FIG. 7.

**[0104]** The reference current generation circuit 141B may include a first transistor 21, a second transistor 22, an operational amplifier 23, and a resistor 24.

**[0105]** The first transistor 21 may include a pair of 1-1 transistors 21a and 1-2 transistors 21b connected in series. The 1-1 transistor 21a may include a gate connected to the 1-1 control line 151a, a first terminal connected to a source of the first power voltage VDD, and a second terminal connected to the gate and the first- 2 and the first terminal of the transistor 21b.

**[0106]** The 1-1 transistor 21a may be turned on and off by the gate voltage Bias1. The 1-2 transistor 21b may include a gate connected to the 1-2th control line 151b, a first terminal connected to the second terminal of the 1-1 transistor 21a, and a second terminal connected to the gate and the first terminal of the second transistor 22. The 1-2 transistor 21b may be turned on and off by the gate voltage Bias2.

**[0107]** The second transistor 22 may include a gate connected to the output terminal of the operational amplifier 23, a first terminal connected to the second terminal of the 1-2 transistor 21b, and a second terminal connected to the second input terminal " - " of the operational amplifier 23.

**[0108]** The first input terminal (+) of the operational amplifier 23 may be connected to the source of the reference voltage Vref, and the second input terminal (-) may be connected to the resistor 24. The output terminal of the operational amplifier 23 is connected to the gate of the second transistor 22. When the reference voltage Vref is applied to the first input terminal (+), the second transistor 22 may be turned on or off according to the voltage of the output terminal due to the voltage difference between the second input terminal (-) and the output terminal. The reference voltage Vref may have a value corresponding to brightness (luminance).

**[0109]** An output terminal voltage of the operational amplifier 23 is determined according to the reference voltage Vref and the resistance value of the resistor 24. A reference current Iref of the operational amplifier 23 may be determined by the first transistor 21 and the second transistor 22 turned on from the first power supply voltage VDD.

**[0110]** Although the above-described embodiment shows an example in which the reference current generation circuit 141B includes the first transistor 21 implemented as a P-type transistor and the second transistor 22 implemented as an N-type transistor according to an embodiment of the present invention, the example is not limited thereto, and the reference current generation circuit 141B may be configured by implementing the first transistor 21 and the second transistor 22 as different types of transistors, and configuring an operational amplifier corresponding thereto.

**[0111]** The gamma current generating circuit 143B may operate as a reference current generating circuit 141B and a current mirror. The gamma current generation circuit 143B may generate the first to the M<sup>th</sup> gamma currents Igamma\_1 to Igamma\_M corresponding to mbit gamma data from a register (not shown) based on the reference current Iref. The gamma current generation circuit 143B may include the first to the Mth current conversion circuits 43\_1 to 43\_M. Each of the first to the Mth current conversion circuits 43\_1 to 43\_M may include one or more transistors connected in series and/or in parallel. The first to the M<sup>th</sup> current conversion circuits 43\_1 to 43\_M may constitute a reference current generating circuit 141B and a current mirror circuit, respectively.

**[0112]** The gamma data may be a digital value of m bits (e.g., 8 bits of D0 to D7) corresponding to one of the first to Nth gamma voltages (V<0>, ..., V<N-1>). For example, the first current conversion circuit 43\_1 may receive gamma data corresponding to the first gamma voltage V<0>, and the second current conversion circuit 43\_2 may receive the fourth gamma voltage V<3)., and the third current conversion circuit 43\_3 may receive gamma data corresponding to the twelfth gamma voltage V<11>.

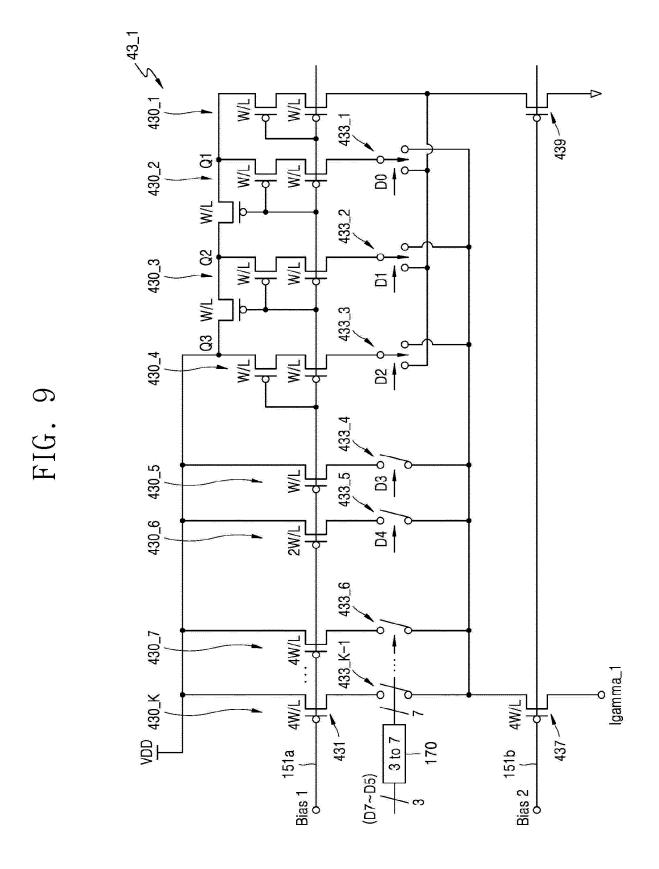

**[0113]** FIG. 9 shows a first current conversion circuit 43\_1, the second to the Mth current conversion circuits 43\_2 to 43\_M may be similarly applied.

**[0114]** The first current conversion circuit 43\_1 may include a plurality of first transistors 431 whose gates are connected to the 1-1 control line 151a, a plurality of switches 433\_1 to 433\_K-1 that are turned on and off according to a gamma data, a second transistor 437, and a third transistor 439 having gates connected to the 1-2<sup>th</sup> control line 151b. The first current conversion circuit 43\_1 may include the first to the K<sup>th</sup> circuit 430\_1 to 430\_K. Each of the first transistor 431, the second transistor 437, and, the third transistor 439 may be implemented as a P-type transistor.

**[0115]** The first circuit 430\_1 may include a gate connected to the 1-1 control line 151a, and a pair of first transistors 431 connected in series and provided between the first node Q1 and the third transistor 439. The pair of first transistors 431 of the first circuit 430\_1 may have the same size. Each of the pair of first transistors 431 of the first circuit 430\_1 may have the same size as the driving transistor of the pixel PX.

**[0116]** The second circuit 430\_2 may include three the first transistors 431 and a first switch 433\_1. The second circuit 430\_2 may include a gate connected to the first-first control line 151a, a pair of first transistors 431 connected in series between the first node Q1 and the first switch 433\_1, and a first transistor 431 provided between the first node Q1 and the second node Q2.

[0117] The three first transistors 431 of the second circuit 430\_2 may have the same size. Each of the three first transistors 431 of the second circuit 430\_2 may have the same size as the driving transistor of the pixel PX. The first switch 433\_1 optionally connect the output terminal, the second terminal, of the first transistor 431 to the second transistor 437 or the third transistor 439 according to the bit value of a first bit D0 of the gamma data. [0118] The third circuit 430\_3 may include three first transistors 431 and a second switch 433\_2. The third circuit 430\_3 may include the gate connected to the 1-1 control line 151a, a pair of first transistors 431 connected in series between the second node Q2 and the second switch 433\_2, and the first transistor 431 provided between the second node Q2 and the third node Q3.

**[0119]** The three first transistors 431 of the third circuit 430\_3 may have the same size. Each of the three first transistors 431 of the third circuit 430\_3 may have the same size as the driving transistor of the pixel PX. The second switch 433\_2 may optionally connect the output terminal, a second terminal, of the first transistor 431 to the second transistor 437 or the third transistor 439 according to a bit value of a second bit D1 of the gamma data.

**[0120]** The fourth circuit 430\_4 may include three first transistors 431 and a third switch 433\_3. The fourth circuit 430\_4 may include a gate connected to the first-first control line 151a and a pair of first transistors 431 connected in series between a third node Q3 and the third switch 433\_3. The pair of first transistors 431 of the fourth circuit 430\_4 may have the same size.

**[0121]** Each of the pair of first transistors 431 of the fourth circuit 430\_4 may have the same size as the driving transistor of the pixel PX. The third switch 433\_3 may optionally connect the output terminal (second terminal) of the first transistor 431 to the second transistor 437 or the third transistor 439 according to the bit value of the third bit D2 of the gamma data.

[0122] The fifth circuit 430\_5 may include a first transistor 431 and a fourth switch 433\_4. The gate of the first transistor 431 of the fifth circuit 430\_5 is connected to the first-first control line 151a and may be provided between the third node Q3 and the fourth switch 433\_4. The first transistor 431 of the fifth circuit 430\_5 may have the same size as the driving transistor of the pixel PX. The fourth switch 433\_4 may selectively connect the output terminal (the second terminal) of the first transistor 431 to the second transistor 437 according to the bit value of the fourth bit D3 of the gamma data.

**[0123]** The sixth circuit 430\_6 may include one first transistor 431 and a fifth switch 433\_5. The first transistor

431 may include a gate connected to the first-first control line 151a and may be provided between the third node Q3 and the fifth switch 433\_5. The size of the first transistor 431 of the sixth circuit 430\_6 may be twice the size of the driving transistor of the pixel PX. The fifth switch 433\_5 may selectively connect an output terminal (second terminal) of the first transistor 431 to the second transistor 437 according to the bit value of the fifth bit D4 of the gamma data.

[0124] The seventh circuit 430\_7 may include one first transistor 431 and a sixth switch 433\_6. the seventh circuit may include a gate of the first transistor 431 of the seventh circuit is connected to the first control line 151a and may be provided between the third node Q3 and the sixth switch 433\_6. The size of the first transistor 431 of the seventh circuit may be four times that of the driving transistor of the pixel PX. The sixth switch 433\_6 may selectively connect an output terminal (second terminal) of the first transistor 431 to the second transistor 437 according to the bit value of the bit selected by the selector 170 among the sixth to eighth bits D5 to D7 of the gamma data.

[0125] The selector 170 may select one of the sixth to eighth bits D5 to D7 and output the sixth to K-1th switches 433\_6 to 433\_K-1 of the seventh to Kth circuit 430\_7 to 430\_K. As shown in FIG. 9, for example, the selector 170 may select one of the sixth to eighth bits D5 to D7 and output the selected one to seven circuit according to aspect(s) of the present invention.

[0126] Since each of the eighth to Kth circuit 430\_8 to 430\_K is the same as the seventh circuit, a detailed description thereof will be omitted. The first to K-1th switches 433\_1 to 433\_K-1 may be implemented as transistors. [0127] The second transistor 437 may include a gate connected to the 1-2-th control line 151b, a first terminal, and a second terminal electrically connected to the first transistor 431 through the first to K-1th switches 433\_1 to 433\_K-1. The first gamma current Igamma\_1 may be output through a second terminal of the second transistor 437.

**[0128]** A third transistor 439 may include a gate connected to the 1-2th control line 151b, a first terminal and a second terminal electrically connected to the first transistor 431 through the first to third switches 433\_1 to 433\_3.

**[0129]** The second terminal of the third transistor 439 may be connected to a power supply that supplies a voltage different from the first power voltage VDD (e.g., the second power voltage VSS, a ground voltage, etc.).

[0130] Referring back to FIG. 8, the reference gamma voltage generation circuit 145B may generate the first to Mth reference gamma voltages VGMA\_1, VGMA\_M based on the first to the MTh gamma currents Igamma\_1, Igamma\_M output from the gamma current generation circuit 143B. The reference gamma voltage generating circuit 145B may include the first to Mth transistor pairs 61 1.61 M.

[0131] The first to the Mth transistor pairs 61\_1 to 61\_M

40

may be implemented as a pair of series-connected transistors 61a\_1/61b\_1, ..., 61a\_M-1/61b\_M-1, 61a\_M/61b\_M, respectively.

**[0132]** The transistors 61a\_1 to 61a\_M may include each gate connected to a corresponding control line among the 2-1 to 2-M control lines 153\_1 to 153\_M, a first termina connected to the gate and the gamma current generating circuit 143B, and a second terminal.

**[0133]** The transistors 61b\_1 to 61b\_M may include a gate, a first terminal, and a second terminal connected to the gate. A first terminal of the transistors 61b\_1 to 61b\_M may be connected to a second terminal of a corresponding one of the transistors 61a\_1 to 61a\_M.

**[0134]** The second terminal of the transistors (61b\_1 to 61b\_M) may be connected to a power source supplying a different power voltage(e.g., a second power voltage (VSS), ground voltage, etc.) from the first power voltage (VDD).

[0135] Each of transistors 61a\_1/61b\_1, 61a\_2/61b\_2, ..., 61a\_M-1/61b\_M-1, 61a\_M/61b\_M may have the same size. Transistors 61a\_1/61b\_1, 61a\_2/61b\_2, ..., 61a\_M-1 / 61b\_M-1, 61a\_M/61b\_M may have the same size as the drive transistors of pixels (PX).

**[0136]** Each gate voltage of the transistors 61a\_1 to 61a\_M may be a first to M reference gamma voltage VGMA\_1 to VGMA\_M. Each gate of transistors 61a\_1 to 61a\_M may be connected to the gamma voltage generation circuit.

**[0137]** As shown in FIG. 8, a pair of transistors 61a\_1/61b\_1, ..., 61a\_M-1/61b\_M-1, 61a\_M/61b\_M are examples implemented as N-type transistors. In another embodiment, the transistors (61a\_1 to 61a\_M) are each implemented as N-type transistors, and transistors 61b\_1 to 61b\_M may be implemented as P-type transistors, respectively.

[0138] Here, the transistors 61b\_1 to 61b\_M may each include a gate, a first terminal, and a second terminal connected to the gate. A first terminal of the transistors 61b\_1 to 61b\_M may be connected to a second terminal of a corresponding one of the transistors 61a\_1 to 61a\_M. Second terminals of the transistors 61b\_1 to 61b\_M may be connected to a power supply that supplies a power voltage different from the first power voltage VDD (e.g., a second power voltage VSS, a ground voltage, etc.).

**[0139]** Conventional gamma circuits measure gamma properties to generate a gamma voltage by a predetermined voltage setting, and a gamma adjustment is required by display device characteristic changes due to process variation. Embodiments of the present invention can implement gamma circuit using a transistor matched with the drive transistor by producing transistors of gamma circuits in the same process on the same substrate as the drive transistor of the pixel. Accordingly, the gamma characteristics required by the display device can be accurately implemented regardless of the changes that occur in the process, and the gamma voltage can be set without measuring the gamma characteristics.

**[0140]** In addition, embodiments of the present invention may simply generate and adjust the gamma current Igamma inherently containing gamma information by adjusting the brightness using the reference current generation circuit.

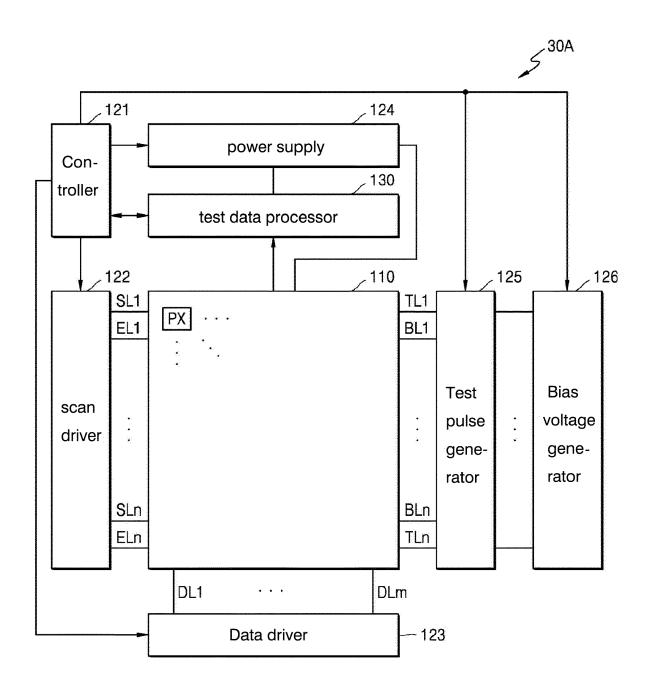

**[0141]** FIG. 10 is a schematic diagram shows a display device according to some embodiments.

**[0142]** Referring to FIG. 10, the display device 30A may include a pixel unit 110 and a driving unit.

**[0143]** The pixel unit 110 may be placed in the display area displaying the image. The pixel unit 110 may include a predetermined pattern, for example, it may include a plurality of pixels (PX) arranged in various patterns, such as matrix type, zigzag type, etc. Pixels (PX) may emit one color, for example, it can emit the color of one of red, blue, green, or white. Pixels (PX) may emit other colors other than red, blue, green, and white.

**[0144]** Pixels (PX) may include lighting devices. Lighting device can be a self-emitting device. For example, a light emitting device may be a light emitting diode (LED). Light emitting device can emit a single peak wavelength or multiple peak wavelengths.

**[0145]** The pixel (PX) may further include a pixel circuit connected to the pixel circuit. The pixel circuit may include at least one thin film transistor and at least one capacitor. The pixel circuit can be implemented by a semiconductor lamination structure on the substrate.

[0146] The pixel unit 110 may include scan lines SL1-SLn supplying scan signals to pixels PX, light emitting control lines EL1-ELn and pixels PX applying data signals to the pixels DL1-DLm to apply the light emitting control signal to the pixels PX. In addition, the pixel unit 110 may include a test pulse line TL1-TLn applying a test pulse signal to the pixels PX and a bias line BL1-BLn applying the bias voltage. Scan lines SL1-SLn, light emitting control lines EL1-ELn, test pulse lines TL1-TLn and bias lines BL1-BLn may be each connected to pixels PX in the same row, and each of the data lines DL1-DLm may be connected to the pixels PX arranged in the same column.

[0147] The driver and the generator are provided in a non-display area around the pixel unit 110, and drive and control the pixel unit 110. The driver and the generator may include the controller 121, the scan driver 122, the data driver 123, the power supply 124, the test pulse generation unit 125, and the bias voltage driver 126. The driver may be operated according to a drive mode and a checking mode.

[0148] In the driving mode, according to the control of the controller 121, the scan driver 122 may apply a scanning signal to scan lines SL1-SLn, and the data driver 123 may apply data signal to each pixel (PX). According to the control of the controller 121, the scan driver 122 may apply in turn a light emitting control signal to the light emitting control line EL1-ELn. Pixels (PX) may emit at a predetermined brightness corresponding to the voltage level or current level of the data signal received through the data line DL1-DLm in response to the scan signal received through scan lines SL1-SLn.

**[0149]** In a checking mode, according to the control of the controller 121, the scan driver 122 may apply the scan signal in turn with to scan lines (SL1-SLn), and the data driver 123 may apply a checking signal to each pixel (PX). According to the control of the controller 121, the scan driver 122 may apply the light emitting control signal in turn to the light emitting control line (EL1-ELn). According to the control of the controller 121, the test pulse generator 125 may apply the test pulse signal to each pixel (PX).

**[0150]** The power supply 124 may receive an external power source and/or an internal power supply apply and converts it to a voltage of various levels necessary for the operation of each component, and the voltage may be supplied to the pixel unit 110 according to the power control signal input from the controller 121.

**[0151]** The power supply 124 may generate a power voltage and apply the power voltage to the pixel unit 110. The power supply 124 may generate a driving voltage and supply a driving voltage to the scan driver 122, the data driver 123, and the bias voltage driver 126.

**[0152]** The test pulse generator 125 may generate a test pulse in the checking mode and apply it to the pixel unit 110. The test data processor 130 may measure the output test pulse in units of each row (line) of the pixel unit 110 and determine the pixel circuit is defective based on the measured value.

**[0153]** The controller 121, scan driver 122, the data driver 123, the power supply 124, the test pulse generator 125, and the bias voltage driver 126 may be each formed in the form of a separate integrated circuit chip or one integrated circuit chip, or mounted directly on the substrate where the pixel unit 110 is formed, mounted on flexible printed circuit film or attached to a substrate in the form of tape carrier package (TCP), or formed directly on the substrate.

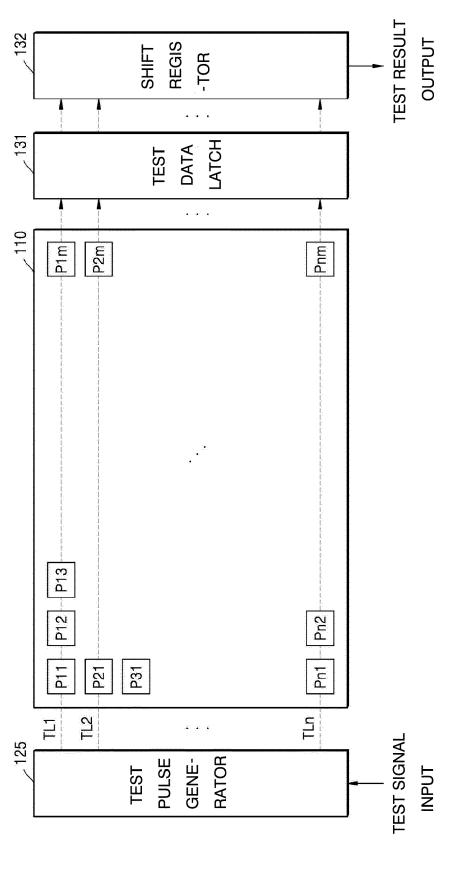

**[0154]** FIG. 11 is a block diagram for explaining how to check whether a row (line) unit defect according to some embodiments.

**[0155]** Referring to FIG. 11, the test data processor 130 may include the test data latch 131 and the shift register 132.

**[0156]** When a test signal is input from the control unit 121, the test pulse generator 125 may generate a test pulse signal and transmit the test pulse signal in rows (lines) of the pixel unit 110 through the test pulse line TL1 to TLn.

[0157] A test data latch 131 may store a test pulse signal passed a gate chain of the pixel unit 110 contained in one row of pixels e.g., P11 to P1m. A shift registers 132 may be confirmed sequentially in rows (lines) through the test pulse signal stored in the test data latch 131 according to an aspect of the present invention.

**[0158]** For example, the test pulse generator 125 may apply the test pulse to the pixel unit 110 through the first test pulse line TL1 by generating a test pulse when a test signal is input from the controler 121. At this time, the test pulse applied to the first row of the pixel unit 110 may

be output through P11, P12, P13, to P1m. The test data latch 131 may store the output test pulse and can be sequentially delivered to the shift register 132.

**[0159]** Each pixel (e.g., P11 to P1m) may include a logical device such as an AND gate inside thereof, and each logical device may form a gate chain to pass the test pulse. The detailed structure for the gate chain is FIG. 4.

[0160] FIG. 12 is a drawing for describing the gate chain of the pixel unit according to some embodiments. [0161] Each pixel included in each row (line) of the pixel unit 110 may include an AND gate, respectively. The respective AND gate included in each pixel may include terminals corresponding to R, G, and B node voltages as input terminals.

**[0162]** Referring to FIG. 12, the test pulse 410 input through the first test pulse line TL1 may be input through one of the input terminals of the AND gate included in the first pixel P11. Also, an output terminal of an AND gate included in the first pixel P11 may be connected to an input terminal of an AND gate included in the second pixel P12.

**[0163]** Specifically, the first test pulse 410 through the first test pulse line TL1 may be input to the first row of the pixel unit 110. At this time, a state in which the output voltage is high is called 1, that is, true, and a state where the output voltage is low is called 0, that is, false. That is, when there is no defect in the bonding and the voltage states of R, G, and B nodes are all true 1, as a result of performing an AND operation between the voltage of each node and the test pulse signal, the test pulse signal may pass through the pixel P11. In other words, when the test pulse signal is true 1, the operation result output from the AND gate may also be true 1.

[0164] The operation result output from the first pixel P11 may be input to an input terminal of an AND gate included in the second pixel P12 arrayed adjacent to the same row as the first pixel P11. The AND gate included in the second pixel P12 may perform AND operation based on a voltage of the node corresponding to the subpixels (e.g., R, G, and B) included in the second pixel P12 and the operation result received from the AND gate of the first pixel P11.

**[0165]** Similarly, an operation result output from the second pixel P12 may be transmitted to the AND gate in the third pixel P13. The AND operation may be performed based on a voltage of the node corresponding to the subpixels (e.g., R, G, and B) in the third pixel P13 and the operation result output from the second pixel P12.

[0166] That is, when the bonding of all pixels (e.g., P11 to P1m) included in the first row is not defective and the test pulse 410 input to the first pixel P11 is true, the pulse 411 output from the mth pixel P1m may also be true 1. Conversely, if any one of the pixels included in the line has a bad bonding, the output pulse may be false 0.

**[0167]** For example, when any one of the pixels P21 to P2m included in the second row (e.g., P22) has a bad bonding FAIL, the test pulse 420 input through the second

test pulse line TL2 may be true 1 while the output pulse 421 may be false 0. Through this, it may be determined that at least one pixel among the pixels included in the second row is in a defective bonding, i.e., fail state.

**[0168]** FIG. 13A and FIG. 13B are diagrams for explaining a structure of a gate of a pixel circuit according to some embodiments. In particular, FIG.13A illustrates a common anode type pixel circuit and FIG. 13B illustrates a common cathode type pixel circuit according to aspect(s) of the present invention.

**[0169]** Referring to FIG. 13A and FIG. 13B, the bias voltage driver 126 may apply the bias voltage through the bias voltage line BLn to test whether the sub-pixels (eg, LED\_R, LED\_G, LED\_B) have poor bonding. That is, when the transistor is turned on according to the bias voltage, V\_R, V\_G, and V\_B node values corresponding to R, G, and B may be input to the AND gate.

**[0170]** The AND gate may determine whether to pass the test pulse signal input through the test pulse line TLn based on the V\_R, V\_G, and V\_B node values.

**[0171]** Specifically, in a normal circuit without bad bonding, when the transistor is turned on by applying a bias voltage for testing, V\_R, V\_G, and V\_B node values that are true 1 can be input to the AND gate, so that the test pulse signal with a true 1 value can be passed.

**[0172]** On the other hand, when bonding of any one of the PADs of the LEDs corresponding to R, G, and B is bad, the corresponding node value may be false 0. For example, when the PAD bonding corresponding to B is bad, the V\_B node value becomes false 0, and the output of the AND gate also becomes false 0.

**[0173]** FIG. 14 illustrates a voltage-current graph in a common anode type to describe an operation of a gate of a pixel circuit according to some embodiments.

**[0174]** Referring to FIG. 14, the current Id flowing through the LED corresponding to each of V\_R, V\_G, and V\_B may change according to the voltage values Vds of the V\_R, V\_G, and V\_B nodes input to the AND gate. For example, a current graph represents a linear region up to a specific voltage value, and a saturation region from a voltage value thereafter.

**[0175]** In other words, the voltage values Vds of the V\_R, V\_G, and V\_B nodes are variable according to the current Id, and in the pixel according to an embodiment of the present invention, the voltage values Vds of each of the V\_R, V\_G, and V\_B nodes are A bias and a pixel circuit may be set to have an appropriate logic value according to the current Id.

**[0176]** When the respective voltage values Vds of the V\_R, V\_G, and V\_B nodes enter a saturation region, the AND gate may determine that the corresponding node is true 1, high. That is, if bonding of the light emitting diode (LED) pad (PAD) corresponding to the V\_R, V\_G, and V\_B nodes is all normal, when all nodes enter the saturation region, it is determined that the logic values of all nodes are true 1, High, and the test pulse signal can pass PASS.

[0177] On the other hand, when bonding of any one of

the light emitting diode LED pads corresponding to the V\_R, V\_G, and V\_B nodes is defective, the value of the node corresponding to the defective pad does not enter the saturation region. That is, since the value of one of the input terminals of the AND gate is false 0, low, the output of the AND gate is also false 0, low and may not pass the test pulse signal Fail.

**[0178]** FIG. 15 is a diagram schematically illustrating a display device 30B for checking a bad pixel based on a current according to some embodiments.

**[0179]** The pixel unit 210 may be disposed in a display area for displaying an image. The pixel unit 210 may include a plurality of pixels PXs arranged in various patterns such as a predetermined pattern, for example, a matrix type or a zigzag type. The pixel PX emits one color, for example, one color among red, blue, green, and white. The pixel PX may emit colors other than red, blue, green, and white.

**[0180]** The pixel PX may include a light emitting device. The light emitting device may be a secondary light emitting device. For example, the light emitting device may be a light emitting diode (LED). The light emitting device may emit a single peak wavelength or emit a plurality of peak wavelengths.

[0181] The pixel PX may further include a pixel circuit connected to the light emitting device. The pixel circuit may include at least one thin film transistor and at least one capacitor. The pixel circuit may be implemented by a semiconductor stacked structure on a substrate.

[0182] In the pixel unit 210, scan lines SL1-SLn applying a scan signal to the pixels PX, emission control lines EL1-ELn applying an emission control signal to the pixels PX, and pixels PX) may include data lines DL1-DLm to which the data signal is applied. Also, the pixel unit 110 may include bias apply lines BL1-BLn for applying a bias voltage to the pixels PX.

**[0183]** The scan lines SL1-SLn, light emitting control lines EL1-ELn, and the bias apply lines BL1-BLn are respectively connected to the pixels PX arranged in the same row, and the respective data lines DL1-DLm, may be connected to the pixels PXs arranged in the same column.

[0184] The driver is provided in the un-displaying area around a pixel unit 210, and the pixel unit 210 can be driven and controlled. The driver may include a controller 221, a scan driver 222, a data driver 223, a power supply 224, a test switch driver 225 and a bias voltage driver 227. The driver may operate according to a driving mode and a checking mode.

[0185] In the driving mode, under the control of the controller 221, the scan driver 222 sequentially applies a scan signal to the scan lines SL1-SLn, and the data driver 223 applies a data signal to each pixel PX.

**[0186]** According to the control of the controller 221, the scan driver 222 may sequentially apply the light emitting control signal to the light emitting control lines EL1-ELn. The pixels PX may emit light with a brightness corresponding to a voltage level or a current level of a data

signal received through the data lines DL1 to DLm in response to a scan signal received through the scan lines SL1 to SLn.

[0187] In the checking mode, under the control of the controller 221, the scan driver 222 may sequentially applly a scan signal to the scan lines SL1-SLn, and the data driver 223 may apply a checking signal to each pixel PX. According to the control of the controller 221, the scan driver 222 may sequentially apply the light emitting control signal to the light emitting control lines EL1-ELn. Under the control of the controller 221, the test switch driver 225 may apply a signal for turning on the checking switch to each pixel.

**[0188]** Meanwhile, the checking mode may be classified into a first checking mode for checking whether pad bonding is defective, and a second checking mode for checking the chip itself.

**[0189]** In the first checking mode, under the control of the controller 221, a multiplexer driver 228 may sequentially control a connection of the multiplexers to check whether the pad bonding is defective in line units. The multiplexer driver 228 may measure the current flowing through the pixel unit 110 in line units of the pixel unit 110 and may be determine a defect at least one pixel PX among the pixels PX of the corresponding line based on the measured current value.

**[0190]** In a second checking mode, under the control of the controller 221, the chip checking unit 226 may apply a signal for turning on a switch for chip checking. In the second checking mode, the circuit of the chip itself may be checked based on the second power voltage VDD\_2 flowing through the second power line VL2.

**[0191]** The power supply 224 may receive external power and/or internal power and convert it into voltages of various levels necessary for the operation of each component, and supply the voltage to the pixel unit 210 according to the power control signal input from the controller 221.

**[0192]** The power supply 224 may generate a first power voltage VDD\_1 and apply it to the pixel unit 210 through the first power line VL1. The power supply 224 may generate a driving voltage and supply y it to the scan driver 222, the data driver 223, and the bias voltage driver 227. The power supply 224 may generate the second power voltage VDD\_2 and supply it to the chip checking unit 226.

**[0193]** The controller 221, the scan driver 222, the data driver 223, the power supply 224, the test switch driver 225, the chip checking unit 226, and the bias voltage driver 227 are separated or integrated formed on a circuit chip(s), respectively.

**[0194]** Alternatively, the controller 221, the scan driver 222, the data driver 223, the power supply 224, the test switch driver 225, the chip checking unit 226, and the bias voltage driver 227 formed in the form of one integrated circuit chip or mounted directly on the substrate on which the pixel unit 210 is formed.

[0195] The controlle 221, the scan driver 222, the data

driver 223, the power supply 224, the test switch driver 225, the chip checking unit 226, and the bias voltage driver 227 are separated or integrated formed on a circuit chip(s) may be mounted on a flexible printed circuit film, attached to a substrate in the form of a tape carrier package (TCP), or directly formed on the substrate.

**[0196]** FIG. 16 is a diagram for explaining a configuration for driving a checking mode according to some embodiments

**[0197]** The multiplexer may divide the entire pixel unit 210 into at least one section and may include at least one multiplexer 228-1, 228-2 to 228-n connected to an output terminal of each section. The multiplexer driver 228 may control the connection to the pixel unit 210 of the at least one multiplexer 228-1, 228-2 to 228-n, respectively, to sequentially measure the current for each line of the output terminal.

**[0198]** When a measuring unit 230 receives a current flowing through the pixel unit 210 from the at least one multiplexer 228-1, 228-2 to 228-n, the at least one multiplexer 228-1, 228-2 to 228-n can directly measure the current value of the selected pixel, and test whether bonding is defective and based on this.

**[0199]** The measuring unit 230 may further include a current-voltage converter (not shown), through which the current may be converted into a voltage and then measured. As another example, the measuring unit 230 may further include a signal amplifier (not shown), through which the signal may be amplified and measured.