#

## (11) **EP 4 383 332 A1**

(12)

### **EUROPEAN PATENT APPLICATION**

published in accordance with Art. 153(4) EPC

(43) Date of publication: 12.06.2024 Bulletin 2024/24

(21) Application number: 22852832.9

(22) Date of filing: 19.07.2022

- (51) International Patent Classification (IPC):

H01L 27/146 (2006.01) H04N 25/70 (2023.01)

G02B 5/18 (2006.01)

- (52) Cooperative Patent Classification (CPC): G02B 5/18; H01L 27/146

- (86) International application number: **PCT/JP2022/028108**

- (87) International publication number: WO 2023/013408 (09.02.2023 Gazette 2023/06)

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

Designated Extension States:

**BA ME**

**Designated Validation States:**

KH MA MD TN

- (30) Priority: 06.08.2021 JP 2021130073

- (71) Applicant: Sony Semiconductor Solutions Corporation Atsugi-shi, Kanagawa 243-0014 (JP)

- (72) Inventors:

- NOUDO, Shinichiro

Atsuqi-shi, Kanaqawa 243-0014 (JP)

- IWASE, Toshihito Atsugi-shi, Kanagawa 243-0014 (JP)

- YOKOCHI, Kaito Atsugi-shi, Kanagawa 243-0014 (JP)

- SUZUKI, Masayuki

Atsugi-shi, Kanagawa 243-0014 (JP)

- TODA, Atsushi Atsugi-shi, Kanagawa 243-0014 (JP)

- EBIKO, Yoshiki Atsugi-shi, Kanagawa 243-0014 (JP)

- YAMAMOTO, Atsushi Atsugi-shi, Kanagawa 243-0014 (JP)

- NATORI, Taichi

Atsugi-shi, Kanagawa 243-0014 (JP)

- TAKEUCHI, Koichi Atsugi-shi, Kanagawa 243-0014 (JP)

- (74) Representative: MFG Patentanwälte Meyer-Wildhagen Meggle-Freund Gerhard PartG mbB Amalienstraße 62 80799 München (DE)

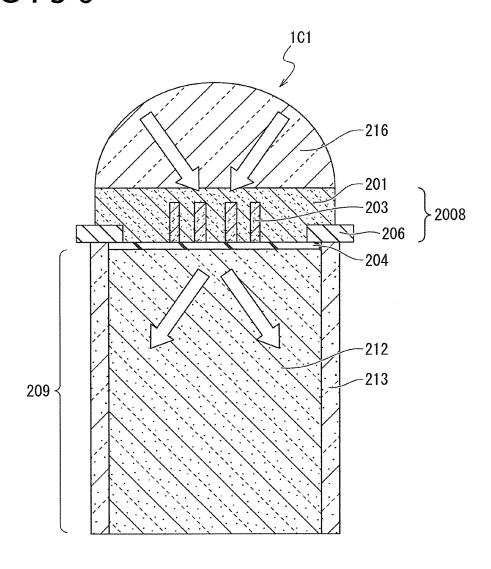

F I G . 3

# (54) PHOTODETECTOR, MANUFACTURING METHOD FOR PHOTODETECTOR, AND ELECTRONIC DEVICE

(57) A photodetector that makes it possible to attempt to improve optical characteristics in terms of oblique incidence of light at angle-of-view ends is provided. A photodetector includes multiple pixels arranged in a matrix on a semiconductor substrate. Each of the multiple pixels includes a photoelectric converting section that photo-electrically converts incident light, and a deflecting section that is arranged on a light-incidence-surface side of the photoelectric converting section, and has multiple pillars with different thicknesses, pitches, or shapes in the pixel. The pillars guide an incident principal ray that is incident at a different angle for each image height to the photoelectric converting section at a prism angle at which light is bent relative to the principal ray differently for each pixel.

EP 4 383 332 A

#### Description

[Technical Field]

<sup>5</sup> **[0001]** The technology according to the present disclosure (the present technology) relates to a photodetector, a photodetector manufacturing method, and electronic equipment including the photodetector.

[Background Art]

15

25

35

40

55

[0002] Photodetectors use a photoelectric converting element such as a photodiode included in each pixel to convert, into an electric signal, an electric charge amount according to intensity of light whose image is formed on the pixel by an on-chip lens. From a viewpoint of high use efficiency of incident light, a backside illumination photodetector in which incident light directly arrives at pixels through on-chip lenses has been attracting attention.

**[0003]** Meanwhile, since on-chip lenses effectively use light at an angle-of-view periphery (angle-of-view ends) of a photodetector, they are arranged according to generally-called pupil correction. That is, while an on-chip lens corresponding to a pixel positioned at the angle-of-view middle (the image height is zero) is arranged such that its optical axis substantially coincides with a center of the pixel, the shift amounts of the positions of on-chip lenses from the centers of the pixels increase as their distances to angle-of-view ends decrease (as image heights increase). Stated differently, as distances to angle-of-view ends decrease, the shift amounts of the positions of on-chip lenses in the exit direction of a principal ray increase. However, due to oblique incidence at angle-of-view ends, optical characteristics in terms of crosstalk, non-uniform sensitivity, or the like deteriorate undesirably.

**[0004]** In view of this, there has been a proposed technology that prevents deterioration of optical characteristics in terms of crosstalk, non-uniform sensitivity, or the like. PTL 1 described below discloses a technology of changing shapes of on-chip lenses for controlling deflection of light at pixels.

[Citation List]

[Patent Literature]

30 **[0005]** [PTL 1] JP 2006-156515A

[Summary]

[Technical Problem]

**[0006]** According to the technology disclosed in PTL 1 described above, responsiveness of resist solubility to an exposure amount is high, and additionally its behavior is not linear. Accordingly, processing difficulty is high, shapes also are not stabilized, and feasibility is low.

**[0007]** The present disclosure has been made in view of such a circumstance, and an object thereof is to provide a photodetector, a photodetector manufacturing method and electronic equipment that make it possible to attempt to improve optical characteristics regarding oblique incidence of light at angle-of-view ends.

[Solution to Problem]

[0008] One aspect of the present disclosure is a photodetector including multiple pixels arranged in a matrix on a semiconductor substrate, in which each of the multiple pixels includes a photoelectric converting section that photoelectrically converts incident light, and a deflecting section that is arranged on a light-incidence-surface side of the semiconductor substrate, and has multiple pillars with different thicknesses, pitches, or shapes in the pixel, and the pillars guide a principal ray that is incident at a different angle for each image height to the photoelectric converting section at a prism angle at which light is bent relative to the principal ray differently for each pixel.

**[0009]** Another aspect of the present disclosure is a photodetector manufacturing method including a step of forming multiple pixels in a matrix on a semiconductor substrate, and forming, in each of the multiple pixels, a photoelectric converting section that photo-electrically converts incident light, and a deflecting section arranged on a light-incidence-surface side of the semiconductor substrate, and a step of forming, in the deflecting section, multiple pillars with different thicknesses, pitches, or shapes in each pixel in the multiple pixels such that a prism angle of the pixel is attained.

**[0010]** In addition, another aspect of the present disclosure is electronic equipment including a photodetector including multiple pixels arranged in a matrix on a semiconductor substrate, in which each of the multiple pixels includes a photoelectric converting section that photo-electrically converts incident light, and a deflecting section that is arranged

on a light-incidence-surface side of the semiconductor substrate, and has multiple pillars with different thicknesses, pitches, or shapes in the pixel, and the pillars guide a principal ray that is incident at a different angle for each image height to the photoelectric converting section at a prism angle at which light is bent relative to the principal ray differently for each pixel.

5

15

20

35

40

50

[Brief Description of Drawings]

#### [0011]

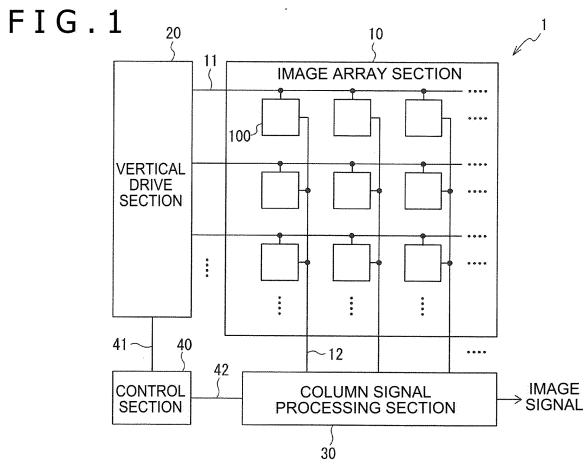

10 [FIG. 1]

FIG. 1 is a figure depicting a configuration example of a photodetector according to a first embodiment of the present technology.

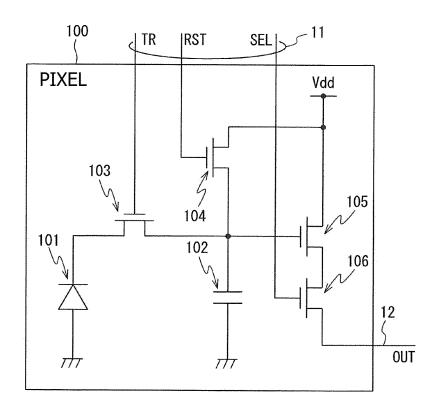

[FIG. 2]

FIG. 2 is a circuit diagram representing a configuration example of pixels according to the first embodiment of the present technology.

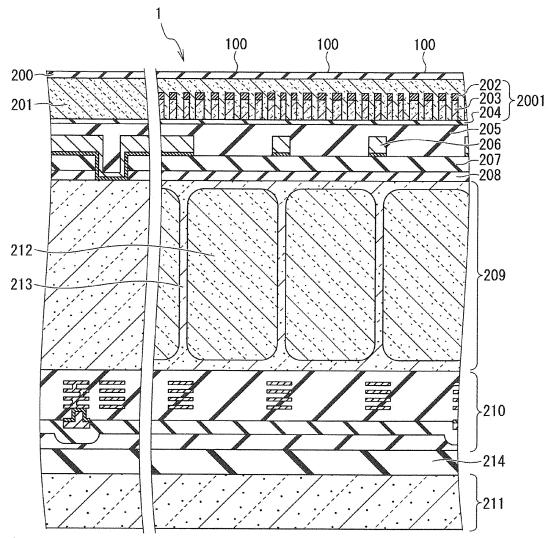

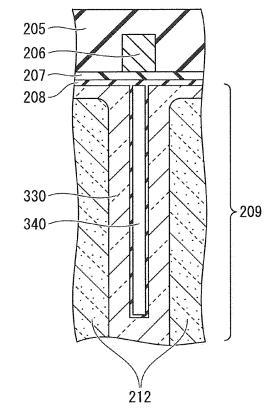

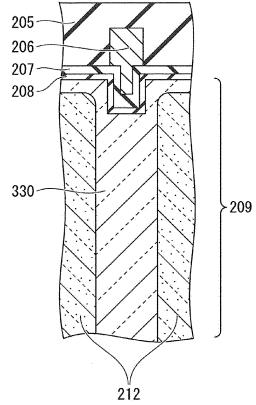

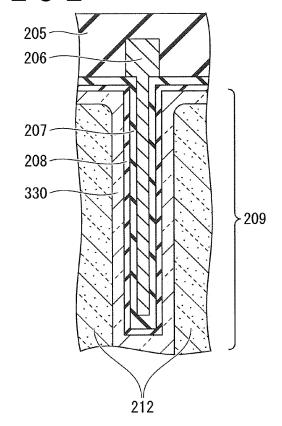

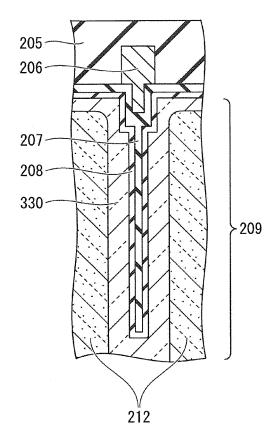

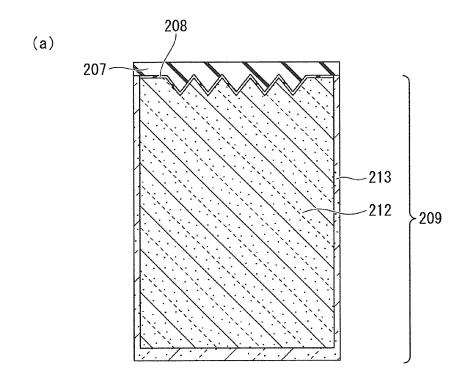

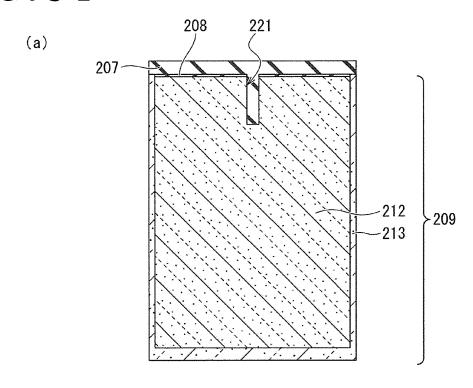

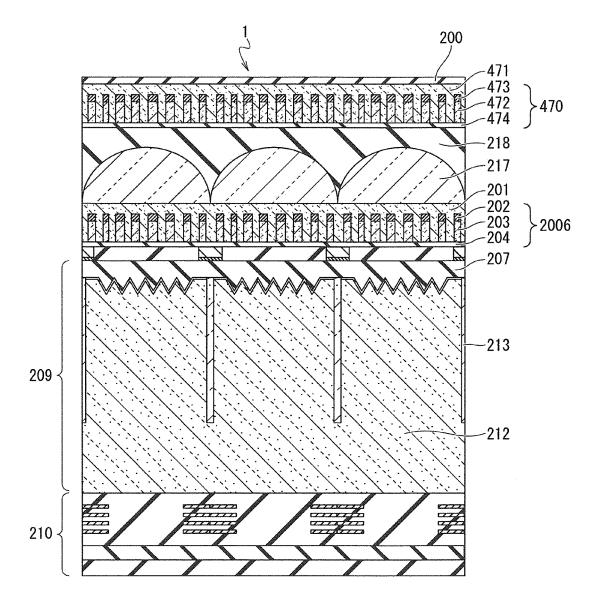

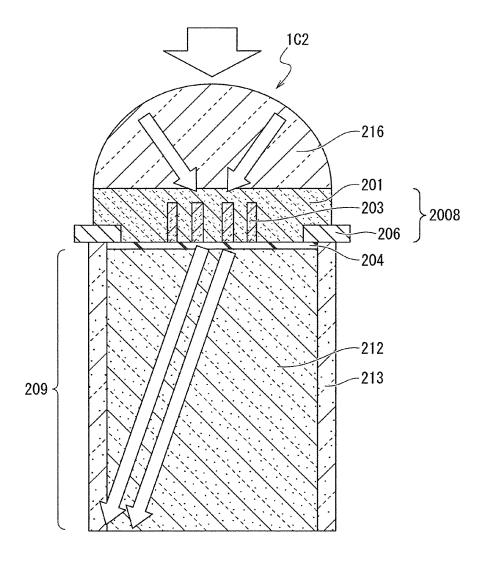

[FIG. 3]

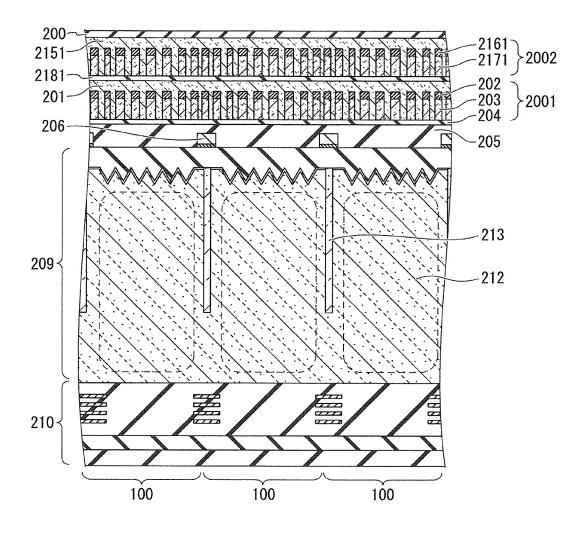

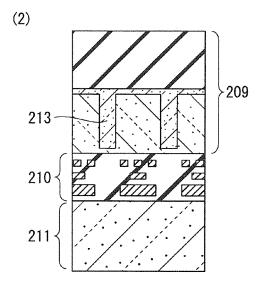

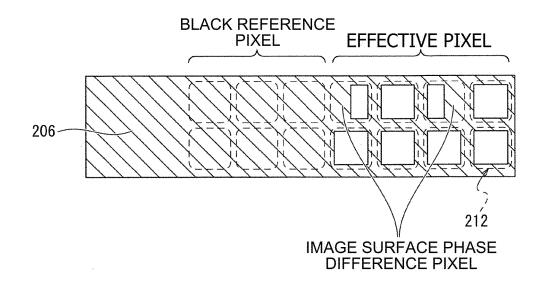

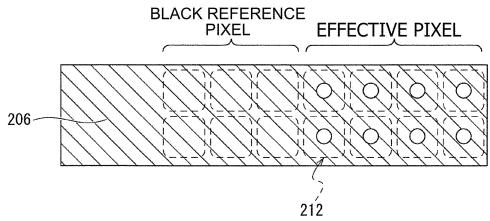

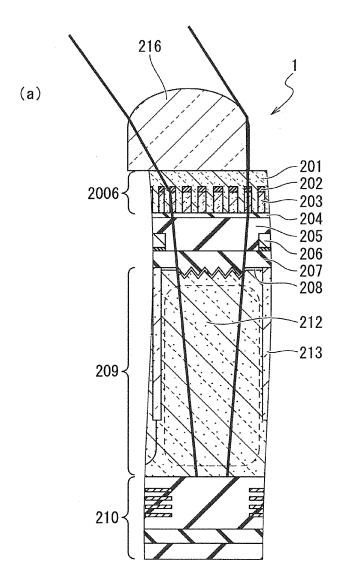

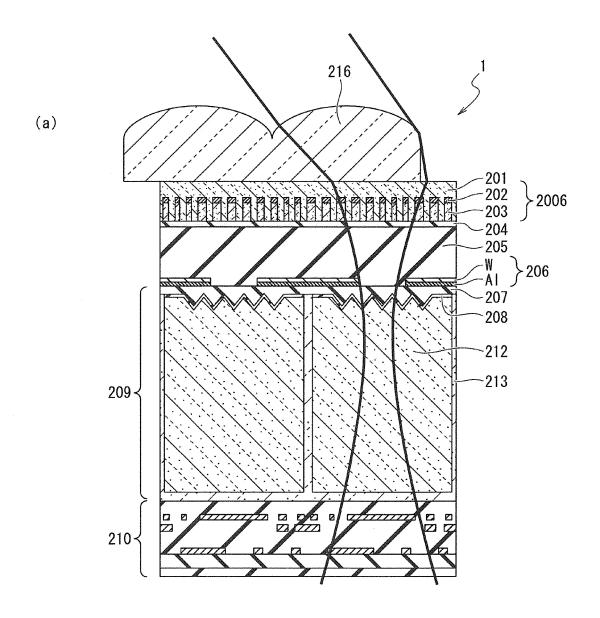

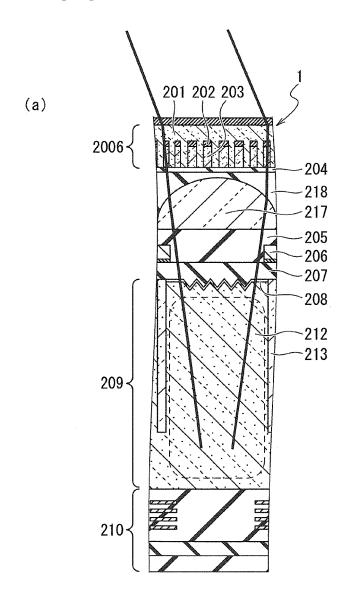

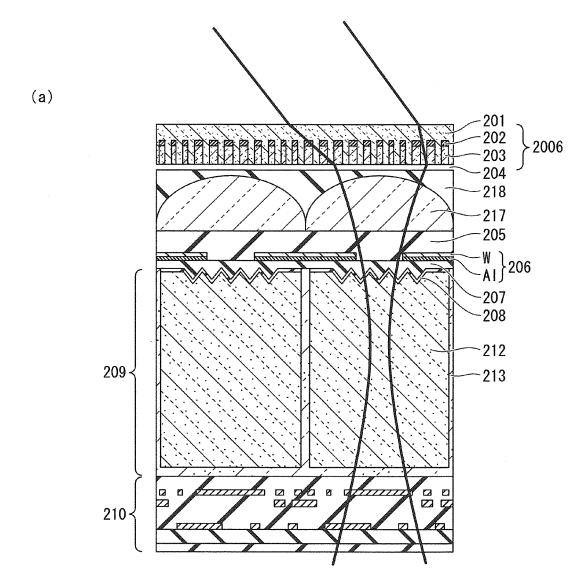

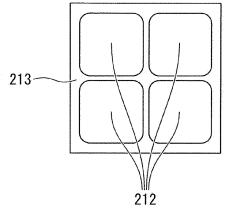

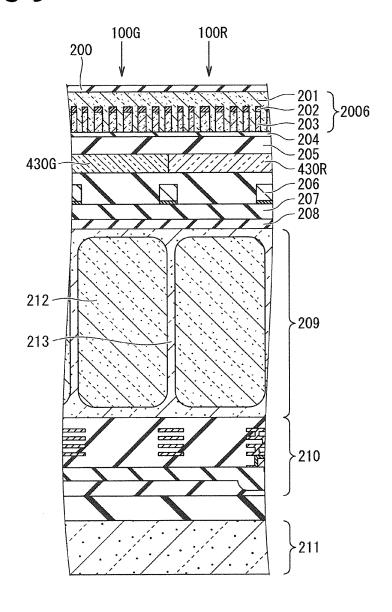

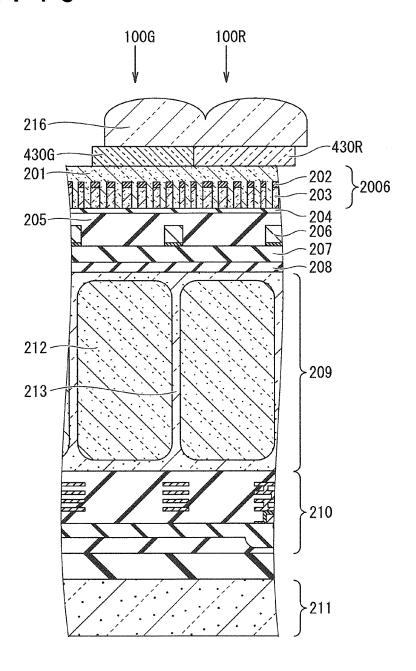

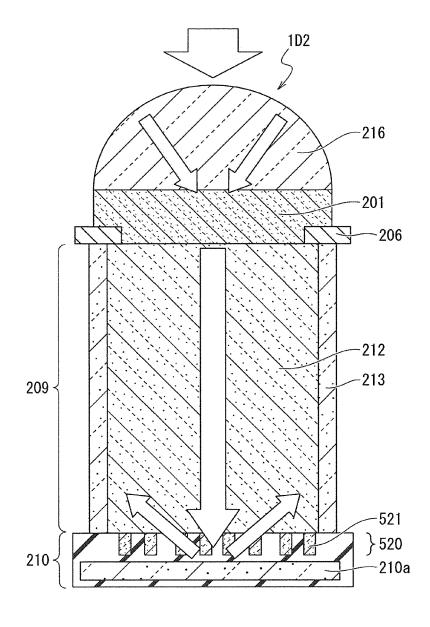

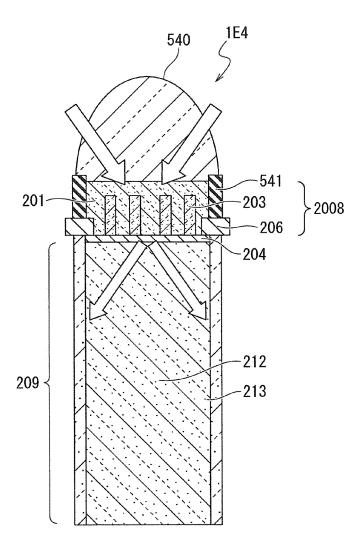

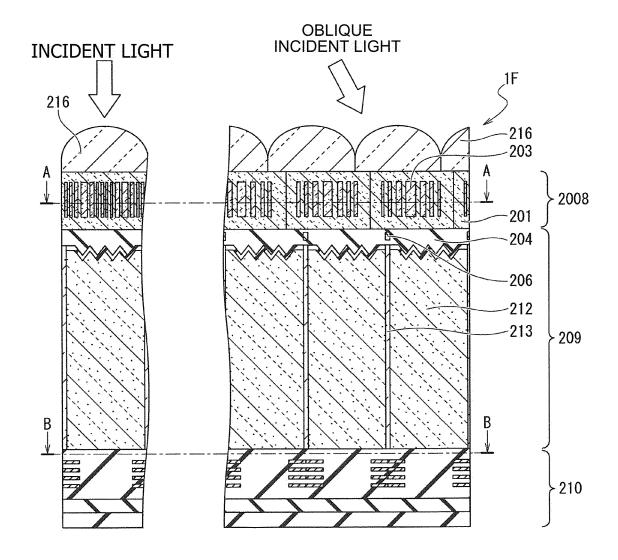

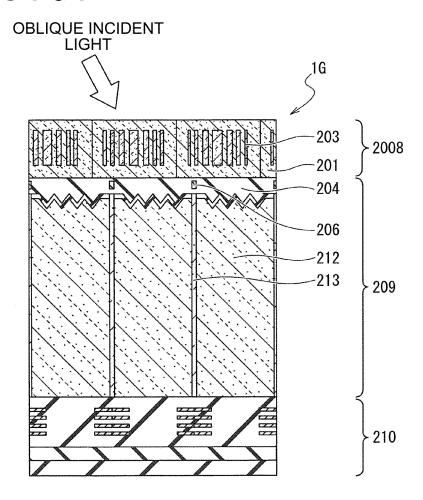

FIG. 3 includes a schematic cross-sectional view depicting a configuration example of the pixels according to the first embodiment of the present technology, and representing the pixels arranged in a pixel array section.

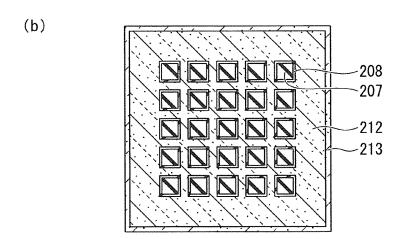

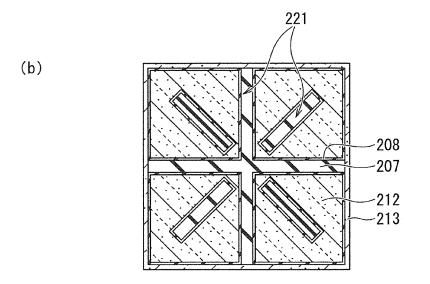

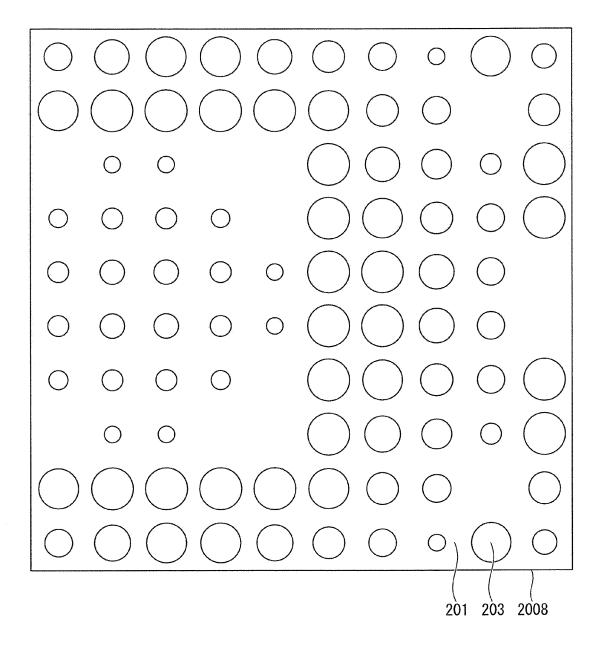

[FIG. 4]

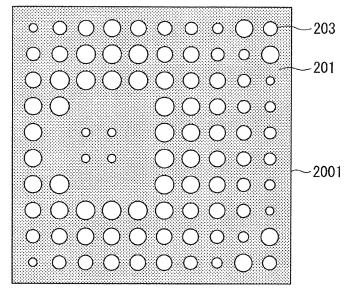

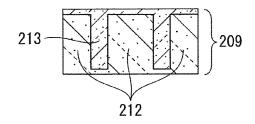

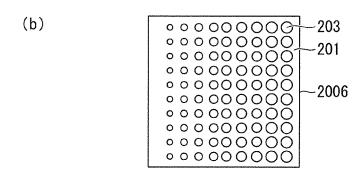

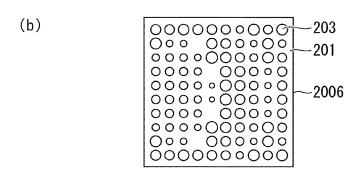

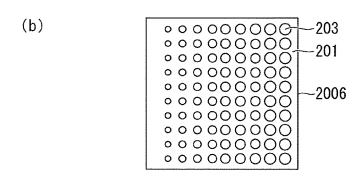

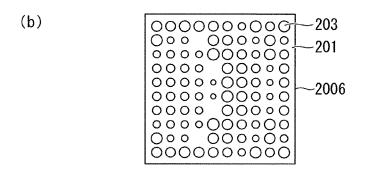

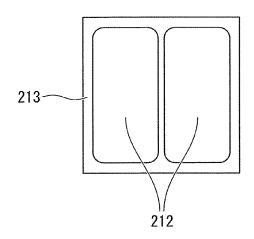

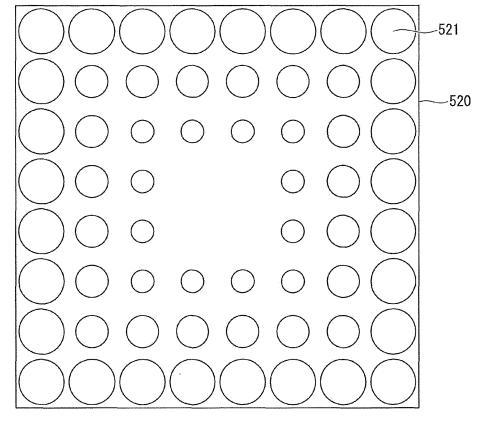

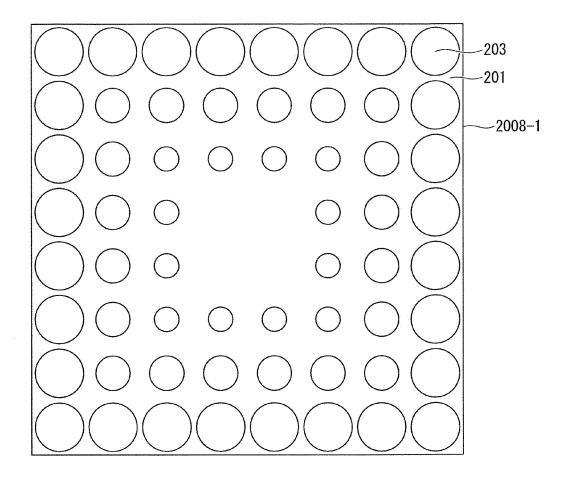

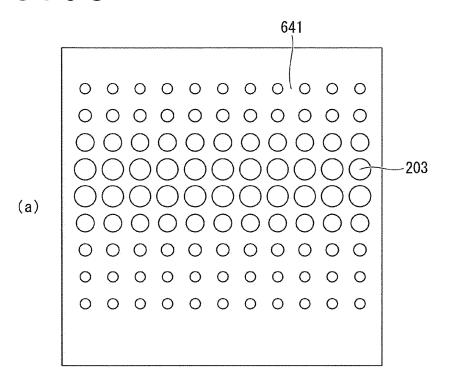

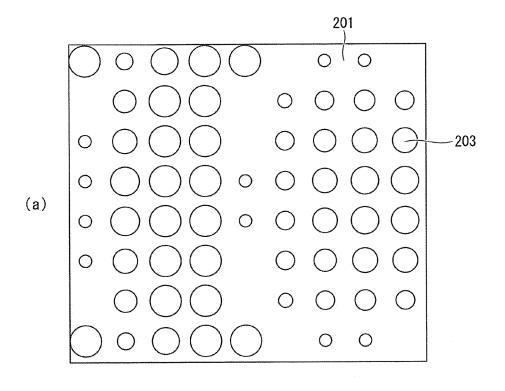

FIG. 4 is a plan view depicting multiple pillars arranged in a pixel.

[FIG. 5]

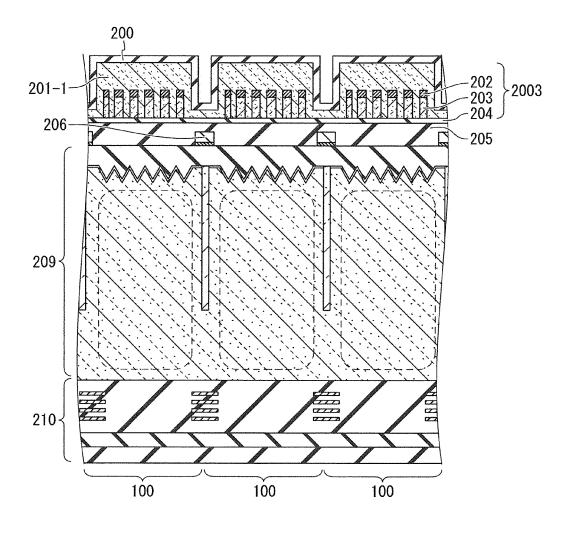

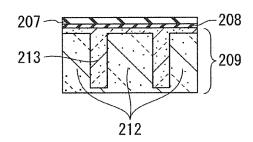

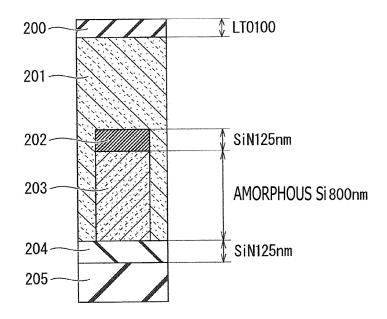

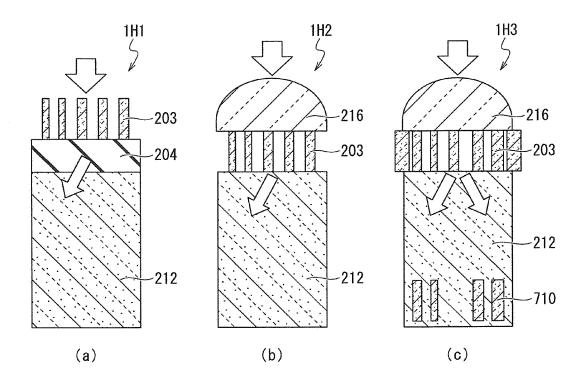

FIG. 5 is a partial vertical cross-sectional view depicting an example of the semiconductor structure of the photodetector according to a first modification example of the first embodiment.

[FIG. 6]

FIG. 6 is a partial vertical cross-sectional view depicting an example of the semiconductor structure of the photodetector according to a second modification example of the first embodiment.

[FIG. 7A]

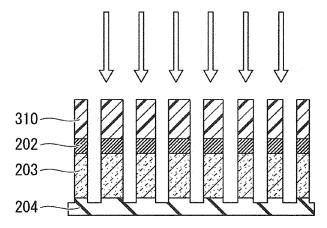

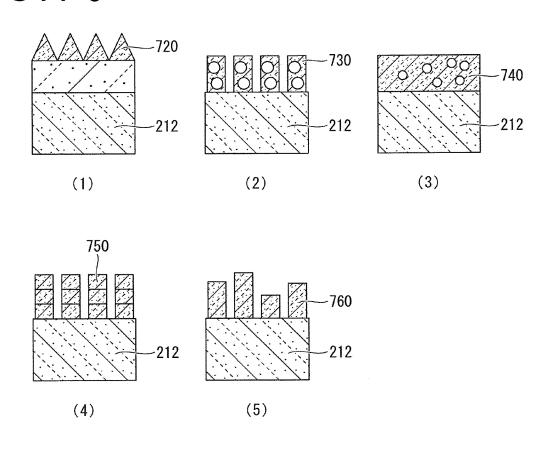

FIG. 7A is a figure (No. 1) depicting an example of a photodetector manufacturing method in the present first embodiment.

30 [FIG. 7B]

FIG. 7B is a figure (No. 2) depicting the example of the photodetector manufacturing method in the present first embodiment.

[FIG. 7C]

FIG. 7C is a figure (No. 3) depicting the example of the photodetector manufacturing method in the present first embodiment.

[FIG. 7D]

FIG. 7D is a figure (No. 4) depicting the example of the photodetector manufacturing method in the present first embodiment.

[FIG. 7E]

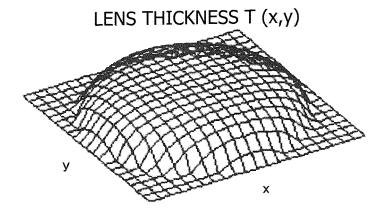

FIG. 7E is a figure (No. 5) depicting the example of the photodetector manufacturing method in the present first embodiment.

[FIG. 8]

FIG. 8 is a partial vertical cross-sectional view depicting an example of the semiconductor structure of the photodetector according to a third modification example of the first embodiment.

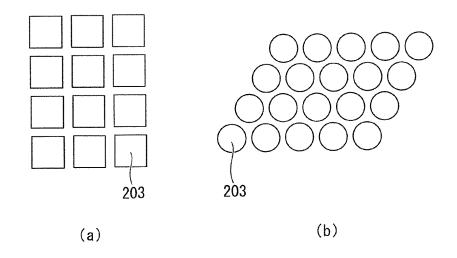

45 [FIG. 9]

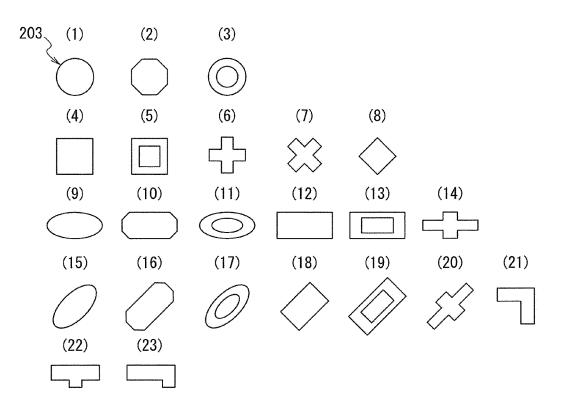

FIG. 9 is a plan view depicted for explaining the angle of view of the photodetector according to the third modification example of the first embodiment.

[FIG. 10]

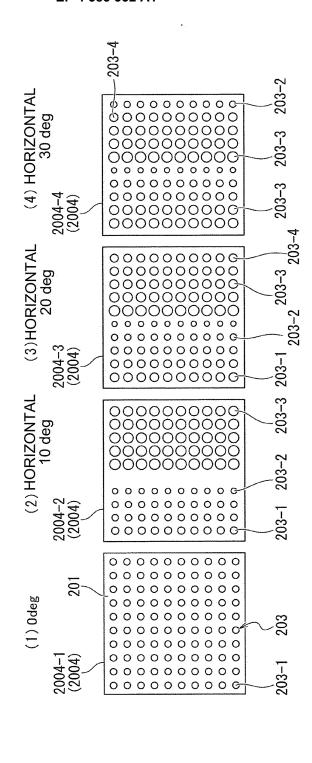

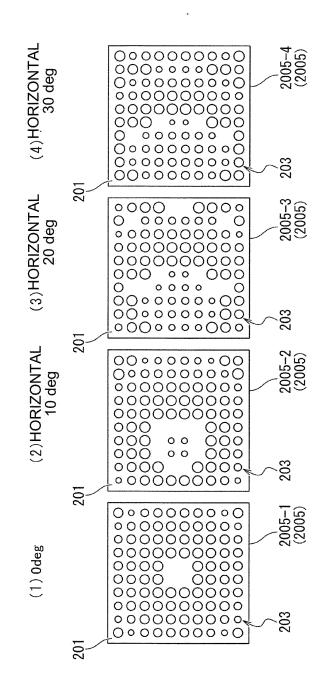

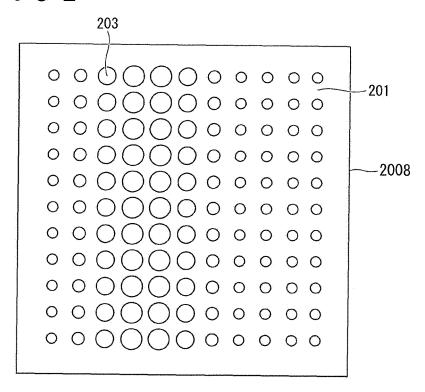

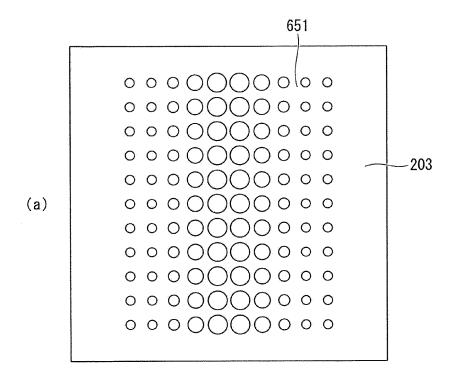

FIG. 10 is a plan view depicting an arrangement example of pillars for each image height in the third modification example of the first embodiment.

[FIG. 11]

FIG. 11 is a figure depicting a phase difference necessary for causing oblique incident light to be transmitted vertically. [FIG. 12]

FIG. 12 is a figure depicting a phase difference map corresponding to a prism angle in a certain direction.

<sup>55</sup> [FIG. 13]

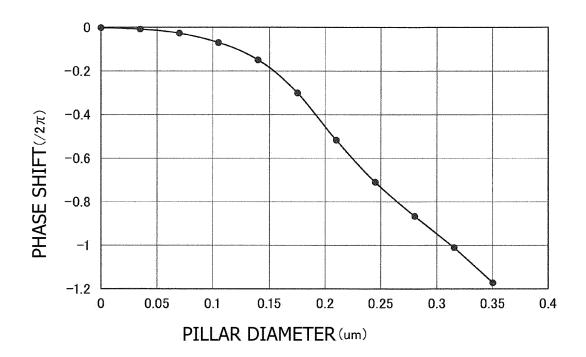

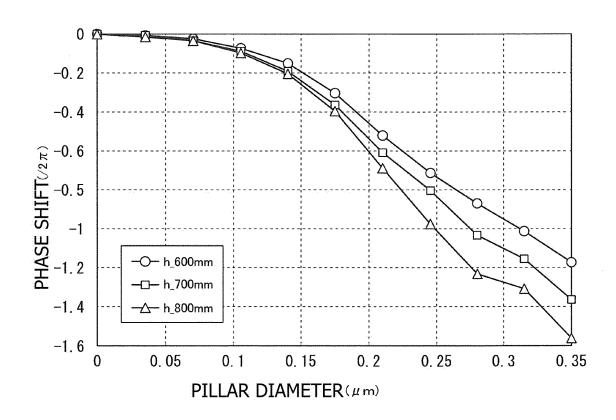

FIG. 13 is a characteristics diagram depicting a phase difference library associating phase difference and pillar diameters.

[FIG. 14]

FIG. 14 is a figure depicted for explaining a process of replacing the phase difference of each pillar with a pillar diameter.

[FIG. 15]

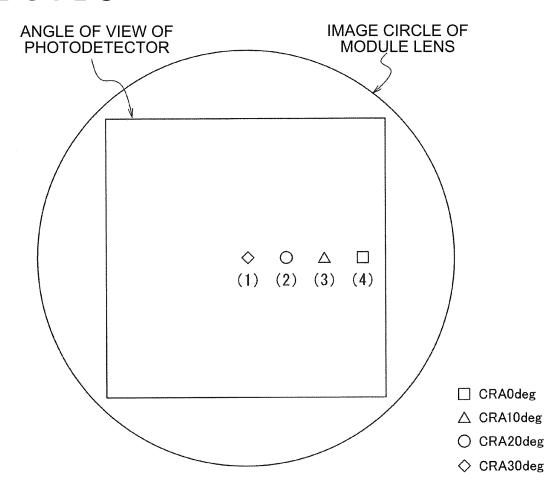

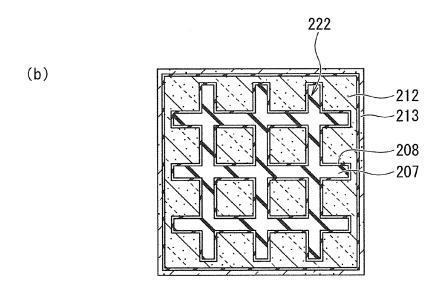

FIG. 15 is a plan view depicting the angle of view of the photodetector according to a fourth modification example of the first embodiment.

[FIG. 16]

5

FIG. 16 is a plan view depicting an arrangement example of pillars for each image height in the fourth modification example of the first embodiment.

[FIG. 17]

FIG. 17 is a figure depicting a phase difference map combining a lens functionality and a prism functionality.

[FIG. 18]

FIG. 18 is a figure depicted for explaining a lens phase difference map.

[FIG. 19]

FIG. 19 is a plan view depicting pillar array patterns.

15 [FIG. 20]

FIG. 20 is a plan view depicting cross-sectional shapes of pillars taken along a direction vertical to a height direction.

[FIG. 21]

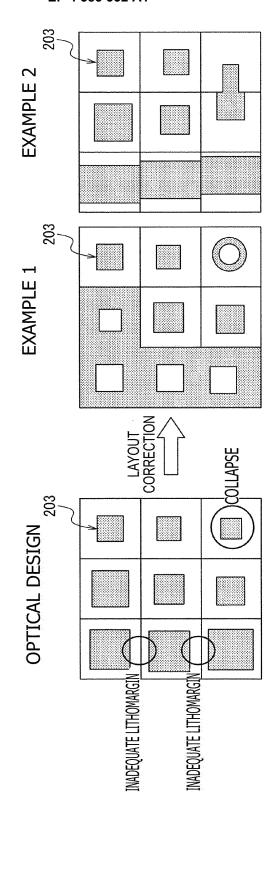

FIG. 21 is a plan view depicted for explaining layout correction and an effective refractive index distribution.

[FIG. 22]

FIG. 22 is a characteristics diagram depicting an example of a phase difference library of circular amorphous Si pillars at pitches of 350 nm.

[FIG. 23]

FIG. 23 is a figure depicted for explaining a turn of phases.

[FIG. 24]

FIG. 24 is a partial vertical cross-sectional view depicting reflection preventing films formed on a pillar.

[FIG. 25A]

$FIG.\ 25 A is a figure\ depicting\ a\ structure\ including\ a\ reflection\ preventing\ film\ that\ doubles\ as\ an\ etching\ stopper\ layer.$

[FIG. 25B]

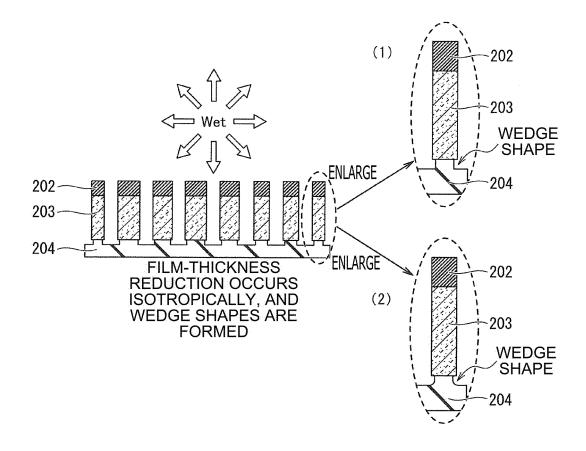

FIG. 25B is a figure depicting a filler material peeling prevention structure formed by wedge processing of pillar bottoms.

[FIG. 26]

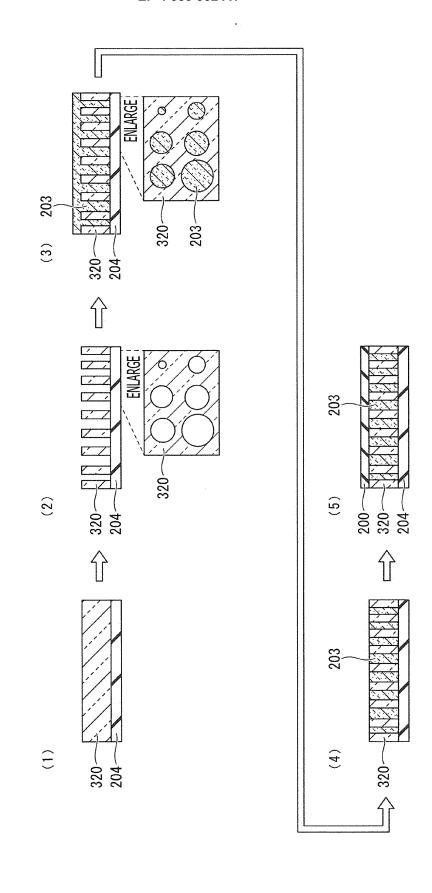

FIG. 26 is a figure depicting a filler material manufacturing process.

[FIG. 27A]

FIG. 27A is a plan view (No. 1) depicting a modification example of a light blocking metal.

35 [FIG. 27B]

30

50

FIG. 27B is a plan view (No. 2) depicting a modification example of the light blocking metal.

[FIG. 27C]

FIG. 27C is a plan view (No. 3) depicting a modification example of the light blocking metal.

[FIG. 27D]

40 FIG. 27D is a plan view (No. 4) depicting a modification example of the light blocking metal.

[FIG. 28A] FIG. 28A is a partial vertical cross-sectional view (No. 1) depicting a modification example of an element separating section.

[FIG. 28B] FIG. 28B is a partial vertical cross-sectional view (No. 2) depicting a modification example of the element separating section.

[FIG. 28C] FIG. 28C is a partial vertical cross-sectional view (No. 3) depicting a modification example of the element separating section.

[FIG. 28D] FIG. 28D is a partial vertical cross-sectional view (No. 4) depicting a modification example of the element separating section.

[FIG. 28E] FIG. 28E is a partial vertical cross-sectional view (No. 5) depicting a modification example of the element separating section.

[FIG. 28F]

FIG. 28F is a partial vertical cross-sectional view (No. 6) depicting a modification example of the element separating section.

[FIG. 29]

FIG. 29 is a partial vertical cross-section depicting a diffraction/scattering element provided with regular recesses and projections at an interface of a semiconductor substrate on the light-reception-surface side.

[FIG. 30]

FIG. 30 is a partial vertical cross-section (No. 1) depicting a light splitting section provided on the interface of the

semiconductor substrate on the light-reception-surface side.

[FIG. 31]

FIG. 31 is a partial vertical cross-section (No. 2) depicting the light splitting section provided on the interface of the semiconductor substrate on the light-reception-surface side.

<sup>5</sup> [FIG. 32]

10

15

30

FIG. 32 is a partial vertical cross-section (No. 3) depicting the light splitting section provided on the interface of the semiconductor substrate on the light-reception-surface side.

[FIG. 33]

FIG. 33 is a partial vertical cross-sectional view depicting a combination of a deflecting section with the prism functionality and an on-chip lens.

[FIG. 34]

FIG. 34 is a partial vertical cross-sectional view depicting a combination of a deflecting section that combines the prism functionality and the lens functionality and an on-chip lens.

[FIG. 35]

FIG. 35 is a partial vertical cross-sectional view depicting a combination of the deflecting section with the prism functionality and an inner lens.

[FIG. 36]

FIG. 36 is a partial vertical cross-sectional view depicting a combination of a deflecting section that combines the prism functionality and the lens functionality and an inner lens.

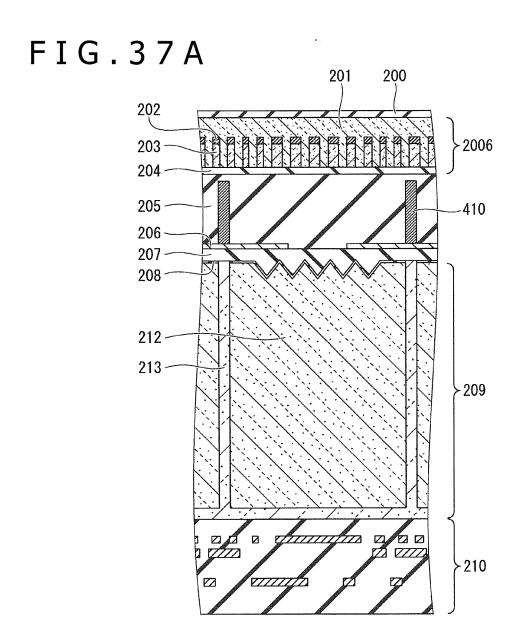

<sup>20</sup> [FIG. 37A]

FIG. 37A is a partial vertical cross-sectional view (No. 1) depicting the configuration of light blocking walls.

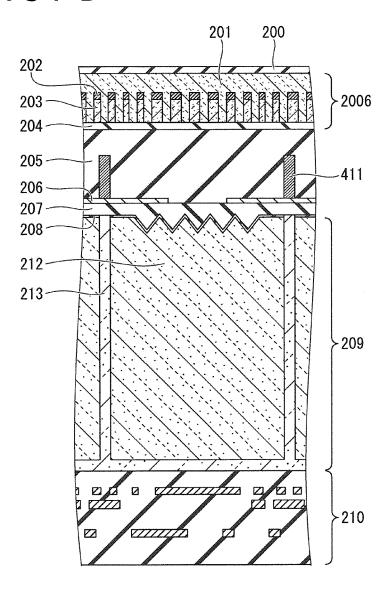

[FIG. 37B]

FIG. 37B is a partial vertical cross-sectional view (No. 2) depicting the configuration of light blocking walls.

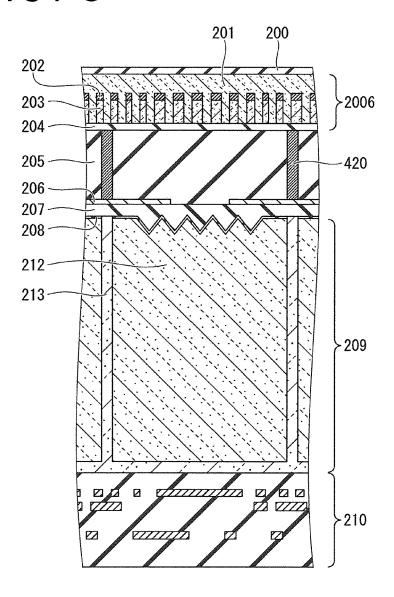

[FIG. 37C]

<sup>25</sup> FIG. 37C is a partial vertical cross-sectional view (No. 3) depicting the configuration of light blocking walls.

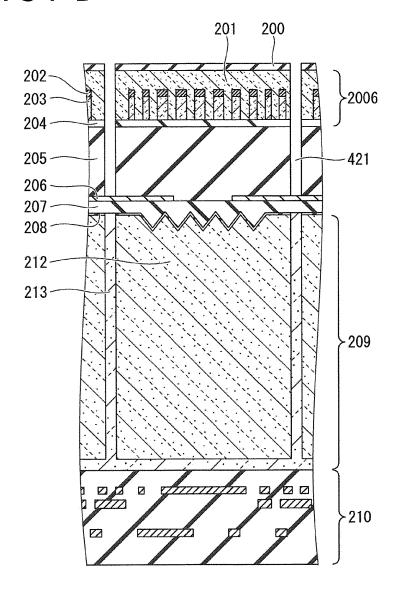

[FIG. 37D] FIG. 37D is a partial vertical cross-sectional view (No. 4) depicting the configuration of light blocking walls.

[FIG. 38A] FIG. 38A is a plan view (No. 1) depicting the configuration of division of a photoelectric converting section.

[FIG. 38B] FIG. 38B is a plan view (No. 2) depicting the configuration of division of the photoelectric converting section.

[FIG. 39] FIG. 39 is a partial vertical cross-sectional view depicting a configuration example including color filters including a generally used pigment or a dye under deflecting elements.

[FIG. 40]

FIG. 40 is a partial vertical cross-sectional view depicting a configuration example including color filters on deflecting sections.

[FIG. 41]

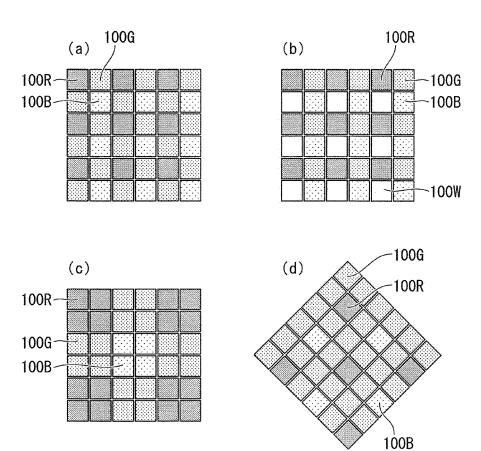

FIG. 41 is a plan view depicting an array example of color filters.

[FIG. 42]

FIG. 42 is a partial vertical cross-sectional view depicting a combination with a surface plasmon resonance filter.

[FIG. 43]

FIG. 43 is a partial vertical cross-sectional view depicting a combination with a GMR filter.

40 [FIG. 44]

FIG. 44 is a partial vertical cross-sectional view depicting a combination with a stacked filter having different refractive indices.

[FIG. 45]

FIG. 45 is a partial vertical cross-sectional view of the photodetector including deflecting sections at multiple stages.

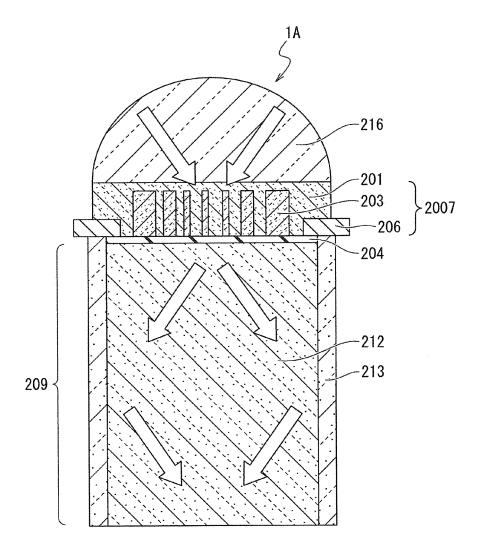

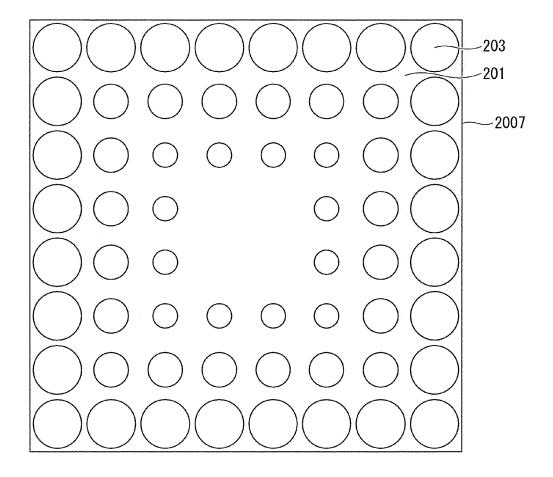

<sup>45</sup> [FIG. 46A]

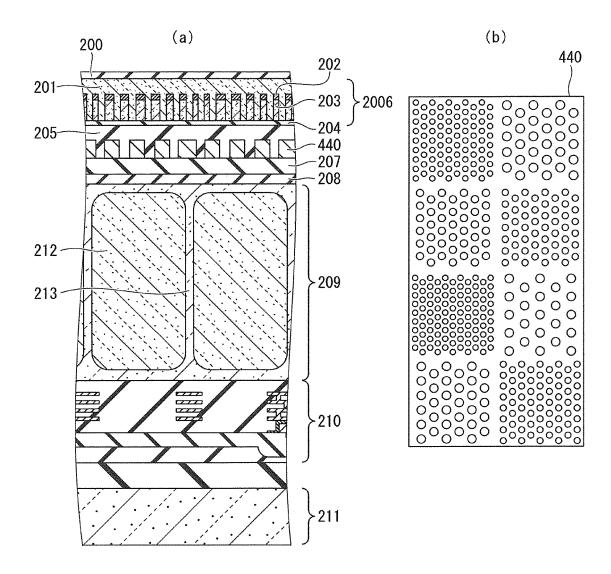

FIG. 46A is a partial vertical cross-sectional view depicting a configuration example of a photodetector according to a second embodiment of the present technology.

[FIG. 46B]

FIG. 46B is a figure depicting an example of a phase distribution in the second embodiment.

50 [FIG. 46C]

FIG. 46C is a figure depicting an example of the arrangement layout of pillars in the second embodiment.

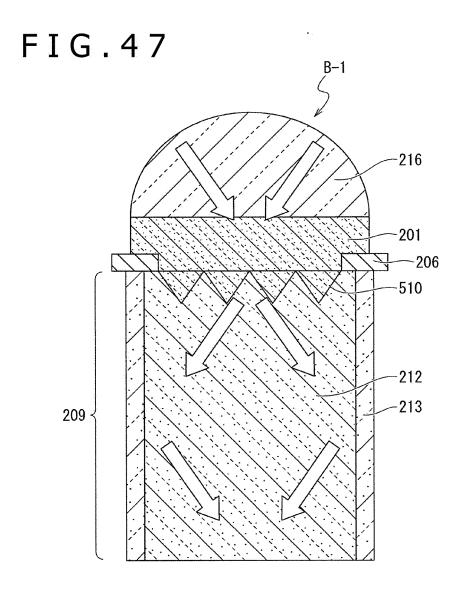

[FIG. 47]

FIG. 47 is a partial vertical cross-sectional view depicting a configuration example of a photodetector as an example to be compared with the second embodiment.

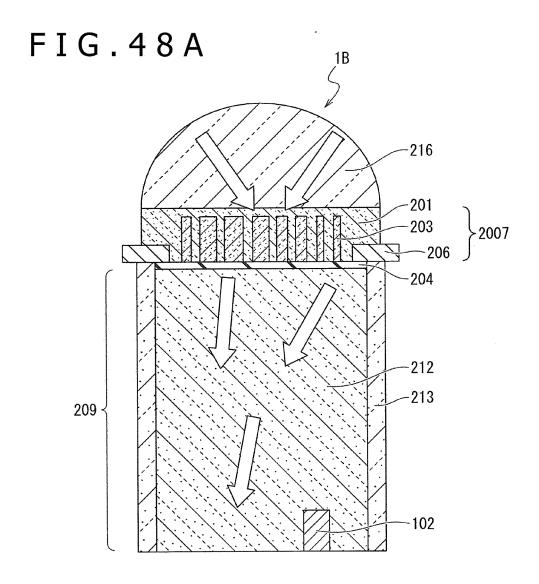

55 [FIG. 48A]

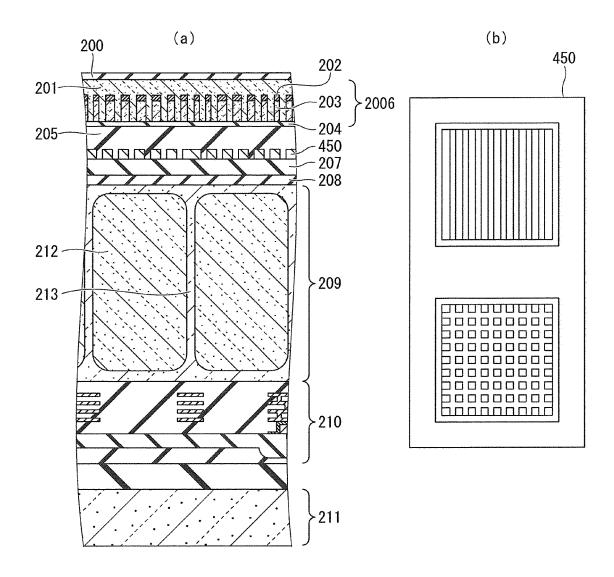

FIG. 48A is a partial vertical cross-sectional view depicting a configuration example of a photodetector according to a third embodiment of the present technology.

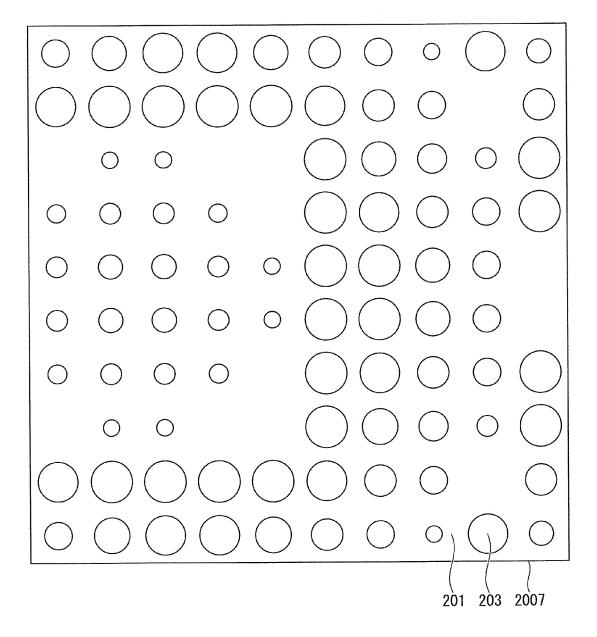

[FIG. 48B]

FIG. 48B is a figure depicting an example of a phase distribution in the third embodiment.

[FIG. 48C]

FIG. 48C is a figure depicting an example of the arrangement layout of pillars in the third embodiment.

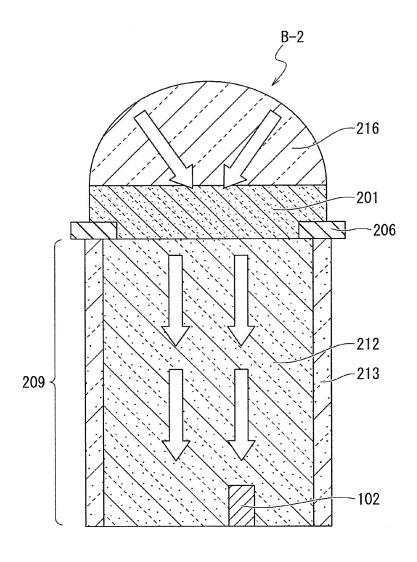

[FIG. 49]

FIG. 49 is a partial vertical cross-sectional view depicting a configuration example of a photodetector as an example to be compared with the third embodiment.

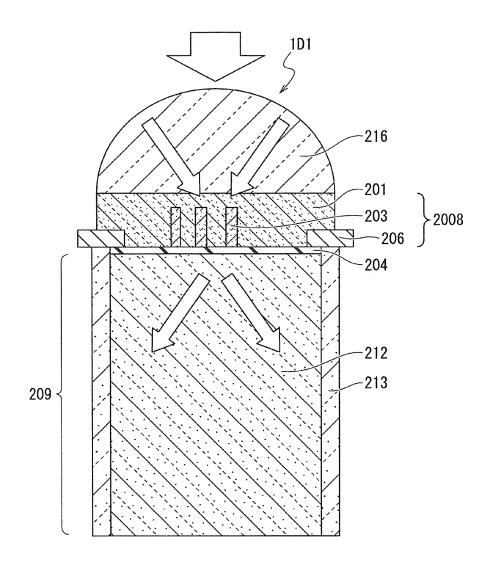

[FIG. 50]

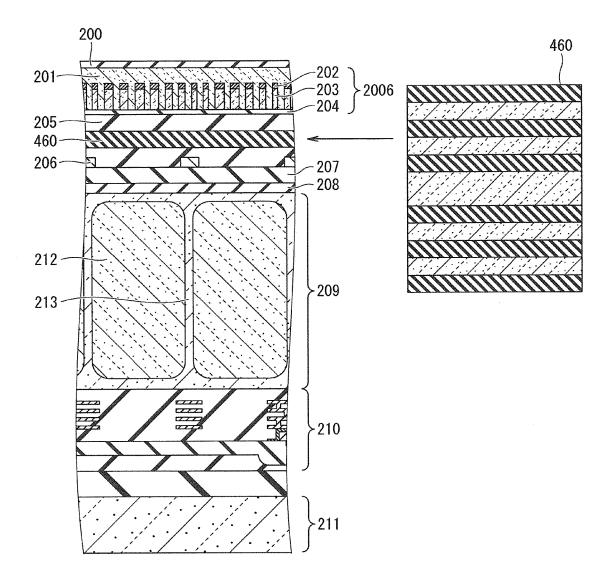

FIG. 50 is a partial vertical cross-sectional view depicting a configuration example of a photodetector according to a fourth embodiment of the present technology.

10 [FIG. 51A]

15

30

35

45

FIG. 51A is a partial vertical cross-sectional view depicting a configuration example of a photodetector according to a first modification example of the fourth embodiment of the present technology.

[FIG. 51B]

FIG. 51B is a figure depicting an example of a phase distribution in the first modification example of the fourth embodiment.

[FIG. 51C]

FIG. 51C is a figure depicting an example of the arrangement layout of pillars in the first modification example of the fourth embodiment.

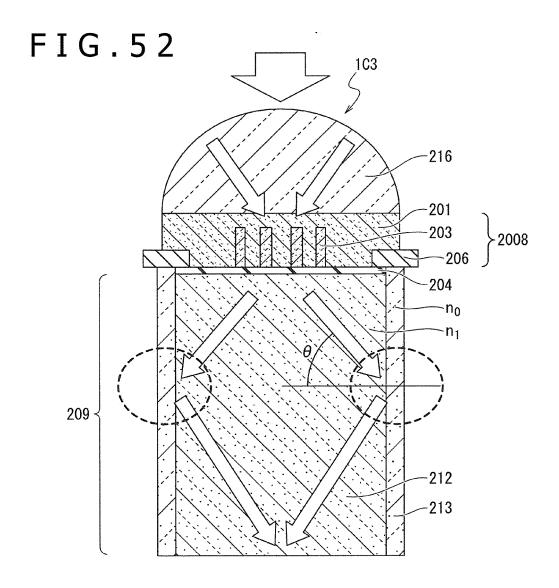

[FIG. 52]

FIG. 52 is a partial vertical cross-sectional view depicting a configuration example of a photodetector according to a second modification example of the fourth embodiment of the present technology.

[FIG. 53]

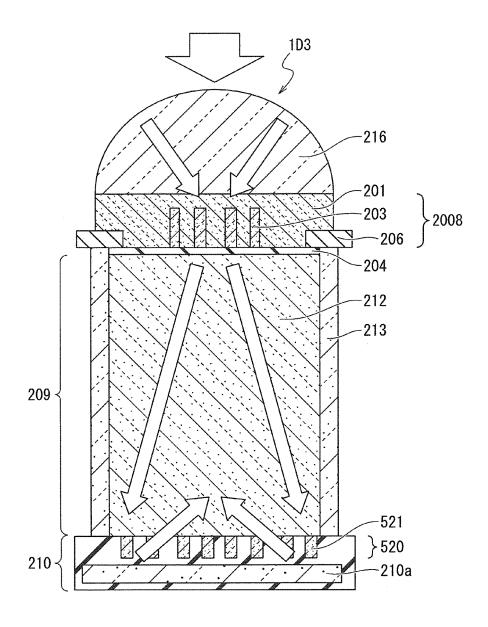

FIG. 53 is a partial vertical cross-sectional view depicting a configuration example of a photodetector according to a fifth embodiment of the present technology.

25 [FIG. 54A]

FIG. 54A is a partial vertical cross-sectional view depicting a configuration example of a photodetector according to a first modification example of the fifth embodiment of the present technology.

[FIG. 54B]

FIG. 54B is a figure depicting an example of a phase distribution in the first modification example of the fifth embodiment.

[FIG. 54C]

FIG. 54C is a figure depicting an example of the arrangement layout of pillars in the first modification example of the fifth embodiment.

[FIG. 55]

FIG. 55 is a partial vertical cross-sectional view depicting a configuration example of a photodetector according to a second modification example of the fifth embodiment of the present technology.

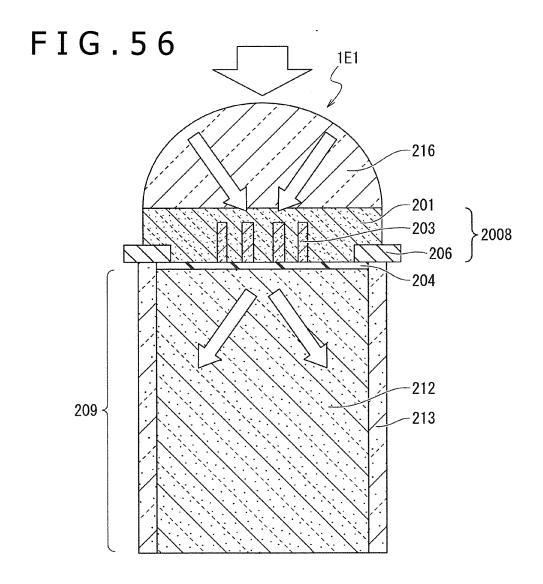

[FIG. 56]

FIG. 56 is a partial vertical cross-sectional view depicting a configuration example of a photodetector according to a sixth embodiment of the present technology.

40 [FIG. 57A]

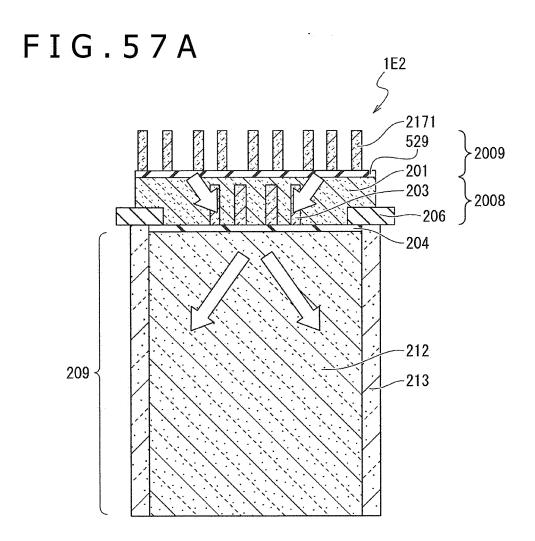

FIG. 57A is a partial vertical cross-sectional view depicting a configuration example of a photodetector according to a first modification example of the sixth embodiment of the present technology.

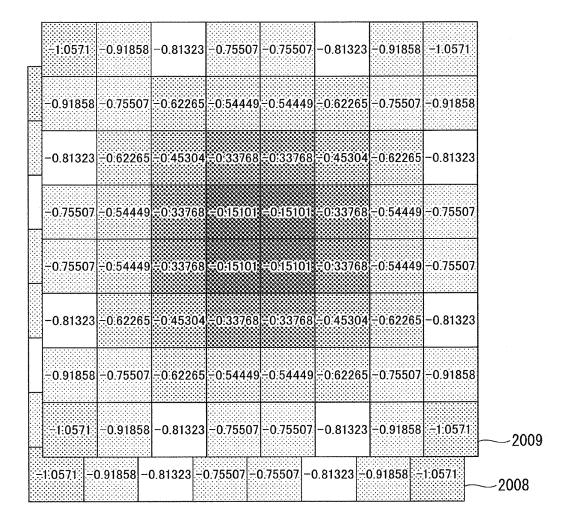

[FIG. 57B]

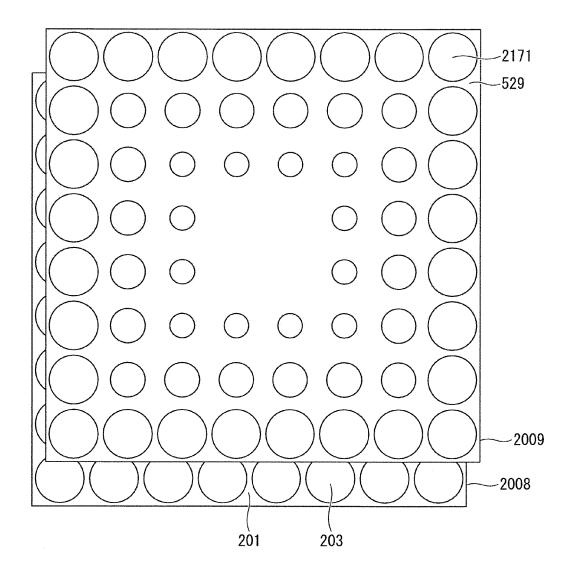

FIG. 57B is a figure depicting an example of a phase distribution in the first modification example of the sixth embodiment.

[FIG. 57C]

FIG. 57C is a figure depicting an example of the arrangement layout of pillars in the first modification example of the sixth embodiment.

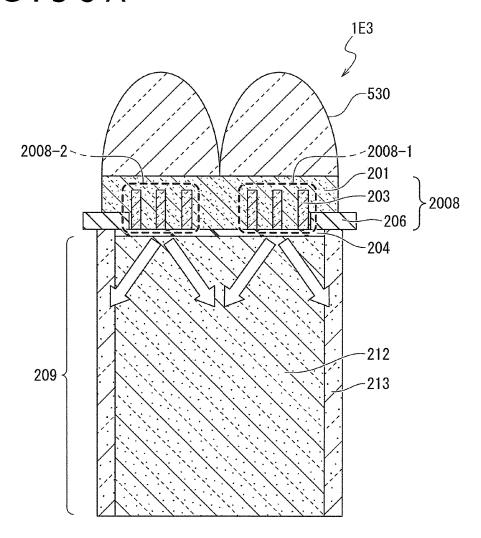

[FIG. 58A]

FIG. 58A is a partial vertical cross-sectional view depicting a configuration example of a photodetector according to a second modification example of the sixth embodiment of the present technology.

IFIG. 58B1

FIG. 58B is a figure depicting an example of a phase distribution in the second modification example of the sixth embodiment.

55 [FIG. 58C]

FIG. 58C is a figure depicting an example of the arrangement layout of pillars in the second modification example of the sixth embodiment.

[FIG. 59]

FIG. 59 is a partial vertical cross-sectional view depicting a configuration example of a photodetector according to a third modification example of the sixth embodiment of the present technology.

[FIG. 60]

FIG. 60 is a partial vertical cross-sectional view depicting a configuration example of a photodetector according to a seventh embodiment of the present technology.

[FIG. 61]

5

10

15

25

35

50

55

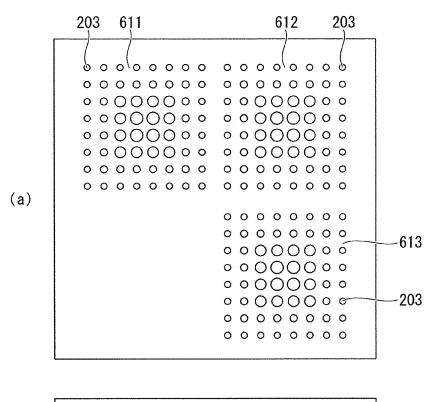

FIG. 61 is a plan view depicting an example of an array of multiple pillars in the seventh embodiment.

[FIG. 62]

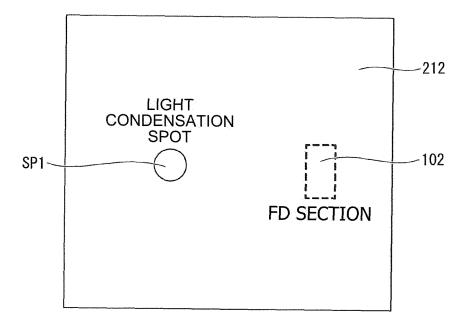

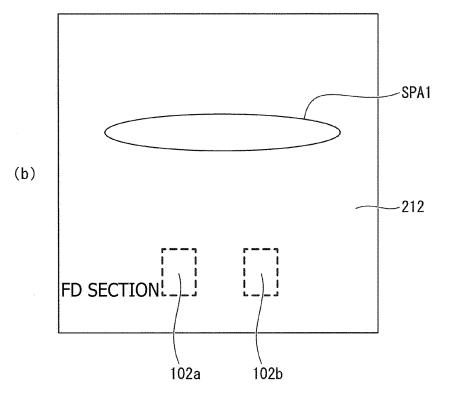

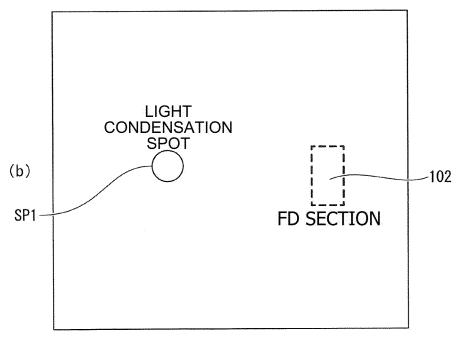

FIG. 62 is a figure depicted for explaining how it looks when a light condensation spot is kept away from an FD section in the seventh embodiment.

[FIG. 63]

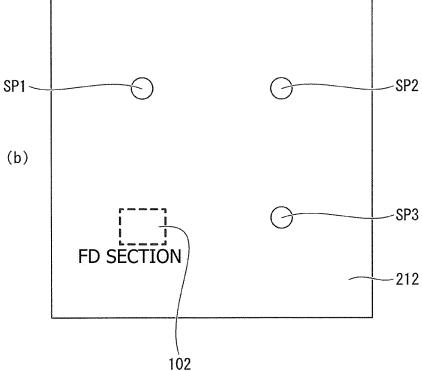

FIG. 63 is a plan view depicting an arrangement example of deflecting sections relative to pixels according to an eighth embodiment of the present technology.

[FIG. 64]

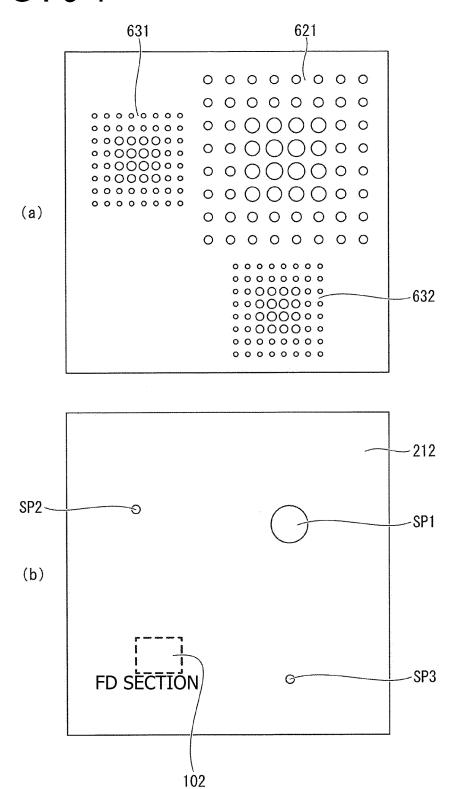

FIG. 64 is a plan view depicting an arrangement example of deflecting sections relative to pixels according to a ninth embodiment of the present technology.

[FIG. 65]

FIG. 65 is a plan view depicting an arrangement example of a deflecting section relative to pixels according to a tenth embodiment of the present technology.

<sup>20</sup> [FIG. 66]

FIG. 66 is a plan view depicting another arrangement example of a deflecting section relative to pixels according to a tenth embodiment of the present technology.

**IFIG. 67**

FIG. 67 is a partial vertical cross-sectional view depicting a configuration example of a photodetector according to an eleventh embodiment of the present technology.

[FIG. 68]

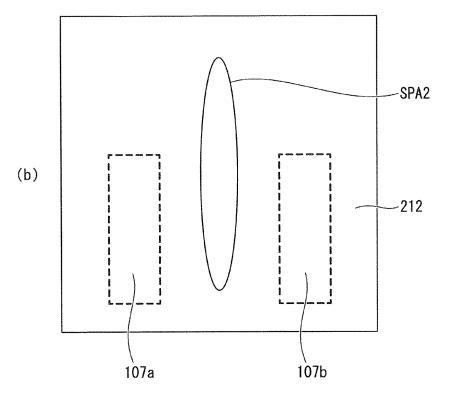

FIG. 68 is a figure depicted for explaining how it looks when a light condensation spot is kept away from an FD section in the eleventh embodiment.

[FIG. 69]

FIG. 69 is a partial vertical cross-sectional view depicting a configuration example of a photodetector according to a twelfth embodiment of the present technology.

[FIG. 70]

FIG. 70 is a figure depicting constituent elements of pillars in the twelfth embodiment.

[FIG. 71]

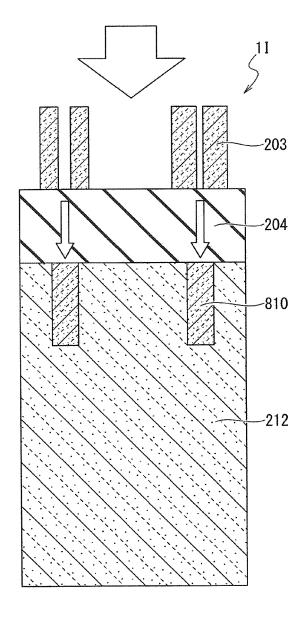

FIG. 71 is a partial vertical cross-sectional view depicting a configuration example of a photodetector according to a thirteenth embodiment of the present technology.

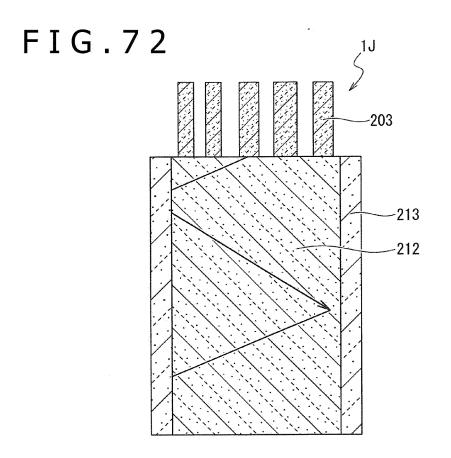

[FIG. 72]

FIG. 72 is a partial vertical cross-sectional view depicting a configuration example of a photodetector according to a fourteenth embodiment of the present technology.

40 [FIG. 73]

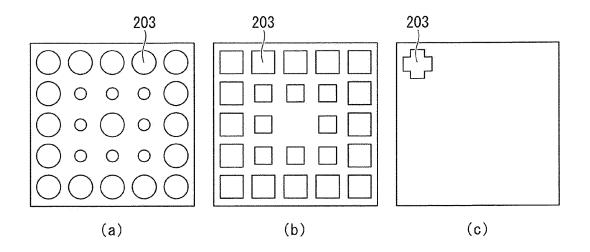

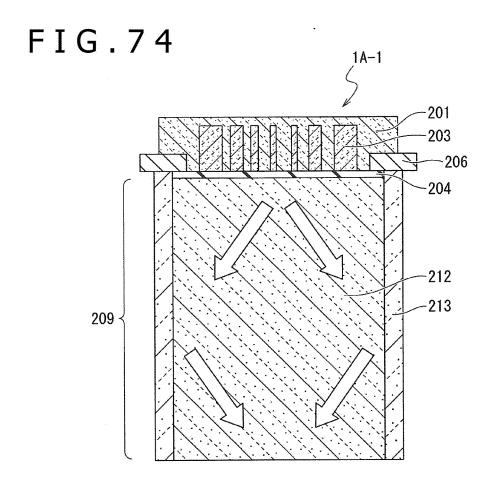

FIG. 73 is a plan view depicting the shapes of pillars according to a fifteenth embodiment of the present technology. [FIG. 74]

FIG. 74 is a partial vertical cross-sectional view depicting a configuration example of a photodetector according to a modification example of the second embodiment of the present technology.

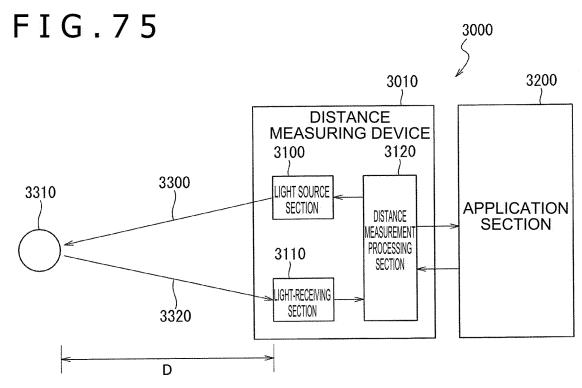

<sup>45</sup> [FIG. 75]

FIG. 75 is a block diagram depicting the configuration of an example of electronic equipment using a distance measuring device that can be applied to the present embodiments.

[Description of Embodiments]

**[0012]** Hereinbelow, embodiments of the present disclosure are explained with reference to the figures. In the descriptions of the figures that are referred to in the following explanation, identical or similar portions are given identical or similar reference signs, and overlapping explanations are omitted. It should be noted that the figures are schematic figures, and the relations between thicknesses and plane dimensions, the ratios between the thicknesses of respective devices or respective members, and the like are different from actual ones. Accordingly, specific thicknesses and dimensions should be determined by taking the following explanation into consideration. In addition, certainly, portions depicted in different figures include portions with dimensions having different relations or ratios.

[0013] In addition, definitions of directions such as the up-down direction in the following explanation are definitions

that are used simply for convenience of explanation, and do not limit the technical idea of the present disclosure. For example, certainly, if a subject object is observed after being rotated 90°, the up-down direction mentioned in an explanation of the subject object is interpreted as meaning the left-right direction, and if the subject object is observed after being rotated 180°, the up-down direction mentioned in an explanation of the subject object is interpreted as meaning an inverted direction.

**[0014]** In addition, it is assumed that the state of being transparent in the present specification is defined as meaning a state where the transmittance of a subject member for a wavelength region of light that is expected to be received by a photodetector is close to 100%. For example, even if a material itself absorbs light in an expected wavelength region, the material is transparent if the material is processed to be very thin, and the transmittance is close to 100%. For example, in a case of a photodetector used for the near-infrared region, even if a member absorbs a large portion of light in the visible region, the member can be said to be transparent if its transmittance for the near-infrared region is close to 100%. Alternatively, it is assumed that even if there are some absorbed components or reflected components, a member can be regarded as being transparent if the influence of the absorption or the reflection is only to the extent that can be tolerated in view of sensitivity specifications of a photodetector.

**[0015]** Note that advantages described in the present specification are merely for listing, but not limiting, examples, and there may be other advantages.

<First Embodiment>

10

30

35

50

55

<sup>20</sup> (Configuration of Photodetector)

**[0016]** FIG. 1 is a figure depicting a configuration example of a photodetector according to a first embodiment of the present technology. A photodetector 1 in the figure includes a pixel array section 10, a vertical drive section 20, a column signal processing section 30, and a control section 40. The pixel array section 10 includes pixels 100 that are arranged in an array (in a matrix). The region of the multiple arrayed pixels 100 forms a generally-called "angle of view" (image heights) corresponding to an image-capturing target space. Here, the pixels 100 generate image signals according to received light.

**[0017]** Each pixel 100 has a photoelectric converting element that generates charge according to received light. In addition, the pixel 100 further has a pixel circuit. The pixel circuit generates an image signal based on the charge generated by the photoelectric converting element. The generation of the image signal is controlled by a control signal generated by the vertical drive section 20 mentioned later.

[0018] Signal lines 11 and 12 are arranged in an XY matrix in the pixel array section 10. The signal lines 11 are signal lines that transmit control signals of the pixel circuits in the pixels 100. Each signal line 11 is arranged for one row of the pixel array section 10. The signal lines 11 are placed such that pixels 100 arranged in each row share a signal line 11.

[0019] The signal lines 12 are signal lines that transmit image signals generated by the pixel circuits of the pixels 100.

Each signal line 12 is arranged for each column of the pixel array section 10. The signal lines 12 are placed such that pixels 100 arranged in each column share a signal line 12. These photoelectric converting elements and pixel circuits are formed on a semiconductor substrate. The vertical drive section 20 generates control signals for the pixel circuits of the pixels 100.

40 [0020] The vertical drive section 20 transmits the generated control signals to the pixels 100 through the signal lines 11 in the figure. The column signal processing section 30 processes image signals generated by the pixels 100. The column signal processing section 30 performs processes on the image signals transmitted from the pixels 100 through the signal lines 12 in the figure.

**[0021]** One of the processes in the column signal processing section 30 is analog-digital conversion in which analog image signals generated at the pixels 100 are converted into digital image signals, for example. The image signals processed by the column signal processing section 30 are output as image signals of the photodetector 1.

**[0022]** The control section 40 performs the overall control of the photodetector 1. The control section 40 controls the photodetector 1 by generating and outputting control signals for controlling the vertical drive section 20 and the column signal processing section 30. The control signals generated by the control section 40 are transmitted to the vertical drive section 20 and the column signal processing section 30 by signal lines 41 and 42, respectively.

(Configuration of Pixels)

**[0023]** FIG. 2 is a circuit diagram representing a configuration example of the pixels according to the first embodiment of the present technology. A pixel 100 in the figure includes a photoelectric converting element 101, a charge retaining section 102, and MOS transistors 103 to 106. The anode of the photoelectric converting element 101 is grounded, and the cathode of the photoelectric converting element 101 is connected to the source of the MOS transistor 103.

[0024] The drain of the MOS transistor 103 is connected to the source of the MOS transistor 104, the gate of the MOS

transistor 105, and one end of the charge retaining section 102. The other end of the charge retaining section 102 is grounded.

**[0025]** The drains of the MOS transistors 105 and 106 share and are connected to a power line Vdd, and the source of the MOS transistor 105 is connected to the drain of the MOS transistor 106. The source of the MOS transistor 106 is connected to an output signal line OUT.

**[0026]** The gates of the MOS transistors 103, 104, and 106 are connected to a transfer signal line TR, a reset signal line RST, and a selection signal line SEL, respectively. Note that the transfer signal line TR, the reset signal line RST, and the selection signal line SEL are included in the signal line 11.

**[0027]** In addition, the output signal line OUT is included in the signal line 12. The photoelectric converting element 101 generates charge according to received light as mentioned before. A photodiode can be used as the photoelectric converting element 101. In addition, the charge retaining section 102 and the MOS transistors 103 to 106 are included in a pixel circuit.

**[0028]** The MOS transistor 103 is a transistor that transfers the charge generated by the photo-electric conversion by the photoelectric converting element 101 to the charge retaining section 102. The transfer of the charge by the MOS transistor 103 is controlled by a signal transmitted by the transfer signal line TR.

**[0029]** The charge retaining section 102 is a capacitor that retains the charge transferred by the MOS transistor 103. The MOS transistor 105 is a transistor that generates a signal based on the charge retained in the charge retaining section 102.

**[0030]** The MOS transistor 106 is a transistor that outputs the signal generated by the MOS transistor 105 as an image signal to the output signal line OUT. The MOS transistor 106 is controlled by a signal transmitted by the selection signal line SEL. The MOS transistor 104 is a transistor that resets the charge retaining section 102 by discharging the charge retained in the charge retaining section 102 to the power line Vdd.

**[0031]** The resetting by the MOS transistor 104 is controlled by a signal transmitted by the reset signal line RST, and is executed before the transfer of the charge by the MOS transistor 103. Note that, by making the MOS transistor 103 conductive at the time of the resetting, the photoelectric converting element 101 also can be reset. In such a manner, the pixel circuit converts the charge generated by the photoelectric converting element 101 into the image signal.

(Configuration of Pixels)

10

35

50

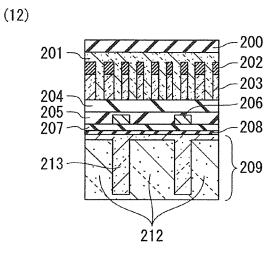

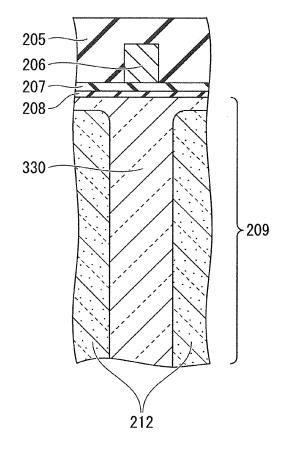

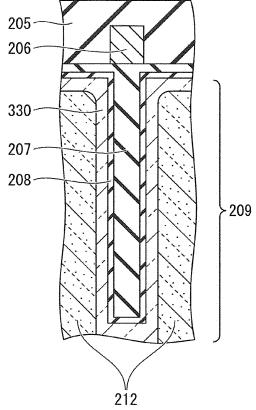

[0032] FIG. 3 includes a schematic cross-sectional view depicting a configuration example of the pixels according to the first embodiment of the present technology, and representing the pixels 100 arranged in the pixel array section 10. The figure depicts an example of the backside illumination photodetector 1. The back-surface side of a semiconductor substrate 209 is an upward-facing side, which is an irradiated-surface side, and the front-surface side of the semiconductor substrate 209 where a wiring layer 210 is formed is a downward-facing side.

**[0033]** The pixel 100 includes an inorganic protective film 200, a filler material 201, a reflection preventing film 202, pillars 203, a reflection preventing film 204, an insulating film 205, a light blocking metal 206, an insulating film 207, a fixed electric charge film 208, the semiconductor substrate 209, the wiring layer 210, a support substrate 211, and an insulating film 214. The semiconductor substrate 209 and the support substrate 211 are joined by plasma joining or the like. In addition, the filler material 201, the reflection preventing film 202, the pillars 203, and the reflection preventing film 204 are included in a deflecting section 2001.

**[0034]** For example, possible examples of the semiconductor substrate 209 include a Si substrate, a SiGe substrate, an InGaAs substrate and the like. It is assumed here that the semiconductor substrate 209 is a Si substrate, and includes, for each pixel 100, a photoelectric converting section 212 and multiple pixel transistors which are not depicted. The photoelectric converting sections 212 are formed such that they extend in the entire region in the thickness direction of the semiconductor substrate 209. The photoelectric converting sections 212 are formed as pn-junction photodiodes including first conductivity regions, n-type semiconductor regions for convenience in the present example, and second conductivity regions, p-type semiconductor regions in the present example, facing both the front and back surfaces of the semiconductor substrate 209.

[0035] The p-type semiconductor regions facing both the front and back surfaces of the semiconductor substrate 209 double as hole charge accumulating regions for suppressing dark current. The pixels 100 each including a photodiode PD and a pixel transistor Tr are separated by element separating sections 213. The element separating sections 213 are formed as p-type semiconductor regions, and are grounded, for example. The pixel transistor Tr is formed by forming an n-type source region and drain region in a p-type semiconductor well region formed on the front-surface side of the semiconductor substrate 209, and forming a gate electrode on a substrate surface between the n-type source region and drain region via a gate insulating film.

**[0036]** The wiring layer 210 transmits image signals generated by the pixels 100. In addition, the wiring layer 210 further transmits signals to be applied to the pixel circuits. Specifically, the wiring layer 210 is included in the signal lines explained with reference to FIG. 2 (the output signal line OUT, the transfer signal line TR, the reset signal line RST, and

the selection signal line SEL) and the power line Vdd. The wiring layer 210 and the pixel circuits are connected by via plugs. **[0037]** In addition, the wiring layer 210 is a multilayer, and wiring layers in the wiring layer 210 also are connected by via plugs. For example, the wiring layer 210 can be formed by using a metal such as Al or Cu. For example, the via plugs can be formed by using a metal such as W or Cu. For example, a silicon oxide film or the like can be used for insulation of the wiring layer 210.

**[0038]** The fixed electric charge film 208 has negative fixed electric charge attained by an oxygen dipole, and plays a role of ensuring pinning. For example, the fixed electric charge film 208 can be formed by using an oxide or a nitride including at least one of Hf, Al, zirconium, Ta, and Ti. In addition, the fixed electric charge film 208 can also be formed by using an oxide or a nitride including at least one of lanthanum, cerium, neodymium, promethium, samarium, europium, gadolinium, terbium, dysprosium, holmium, thulium, ytterbium, lutetium, and yttrium.

**[0039]** In addition, the fixed electric charge film 208 can also be formed by using hafnium oxynitride or aluminum oxynitride. In addition, the fixed electric charge film 208 can also be doped with silicon or nitrogen in an amount that does not impair the insulation property. Thereby, the heat-resistant property or the like can be improved. By controlling the film thickness or stacking multiple layers, desirably, the fixed electric charge film 208 doubles as a reflection preventing film for the Si substrate having a high refractive index.

**[0040]** The insulating film 207 is a film that is formed adjacent to the back surface of the semiconductor substrate 209, and insulates the semiconductor substrate 209. For example, the insulating film 207 is formed by using SiO2, and insulates and also protects the back-surface side of the semiconductor substrate 209.

#### 20 (Configuration of Pixels)

10

30

35

50

**[0041]** The light blocking metal 206 is arranged in the boundary regions of the pixels 100 on the semiconductor-substrate side relative to the pillars 203, and block stray light leaking from adjacent pixels 100. The light blocking metal 206 only has to be a material that blocks light, but preferably is formed by using a metal film of Al, W, copper, or the like, for example, as a material that has a high light blocking property, and additionally can be processed precisely by microprocessing, for example, etching. Other than these, the light blocking metal 206 can be formed by using silver, gold, platinum, Mo, Cr, Ti, nickel, iron, tellurium, or the like or an alloy including these metals. In addition, the light blocking metal 206 can also be formed by stacking multiple these materials.

**[0042]** In order to enhance the adhesion with the underlying insulating film 207, a barrier metal, for example, Ti, Ta, W, Co, or Mo or an alloy, nitride, oxide, or carbide of any of these may be provided under the light blocking metal 206. In addition, the light blocking metal 206 may double as light blocking barriers of pixels that determine the optical black level, and may double as light blocking barriers for preventing noise to peripheral circuit regions.

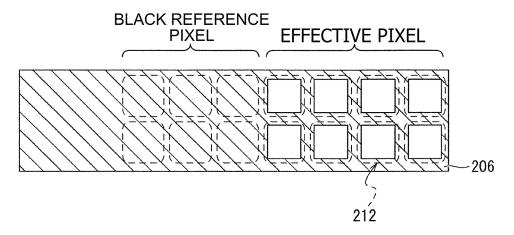

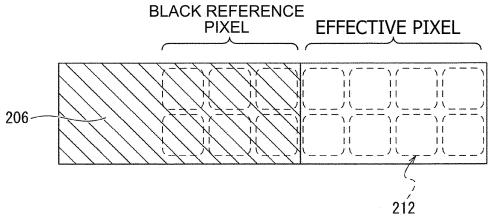

**[0043]** Desirably, the light blocking metal 206 is grounded such that it is not destroyed by plasma damage due to accumulated charge during processing. The grounding structure may be formed in pixel arrays, but the grounding structure may be provided in a region outside the effective region depicted in FIG. 3 after all conductors are connected electrically.

**[0044]** The insulating film 205 is a film arranged adjacent to the insulating film 207 and the light blocking metal 206. The insulating film insulates and also flattens the back-surface side of the semiconductor substrate 209.

**[0045]** The support substrate 211 is a substrate that reinforces and supports the semiconductor substrate 209 and the like in manufacturing steps of the photodetector 1, and is formed by using a silicon substrate or the like, for example. The support substrate 211 is bonded together with the semiconductor substrate 209 by plasma joining or by using an adhesive material, and supports the semiconductor substrate 209 and the like. The support substrate 211 may include a logic circuit, and it becomes possible to reduce the chip size by forming connection vias between the substrates and by vertically stacking various peripheral circuit functionalities.

[0046] In order to suppress reflection at a refractive index interface at the bottoms of the pillars 203, the reflection preventing film 204 may have a film thickness taking into consideration a generally-called X/4n rule where the expected wavelength of the photodetector is  $\lambda$ , and the refractive index of the reflection preventing film 204 is n. Furthermore, in order to enhance the reflection preventing effect, a film having a different refractive index may be stacked. Note that, in addition to reflection prevention, it is also possible to cause the reflection preventing film 204 to serve as an etching stopper layer at the time of processing by dry etching by selecting a material having a high etching selectivity relative to the pillars 203. For example, when the pillars 203 include amorphous silicon, the reflection preventing film 204 can serve as a film combining a reflection preventing functionality and an etching stopper layer simultaneously by including 125 nm silicon nitride.

**[0047]** As depicted in FIG. 4, the deflecting section 2001 may include the pillars 203 that are processed into columnar forms in each pixel 100 such that the multiple pillars 203 are arrayed differently or have different thicknesses, pitches or shapes. By providing the pillars 203 in such a manner, phase differences of light change locally, and it becomes possible to control the direction of light according to the layout of the pillars 203.

[0048] In order to suppress reflection at a refractive index interface at the tops of the pillars 203, the reflection preventing

film 202 may have a film thickness taking into consideration the generally-called X/4n rule. Furthermore, in order to enhance the reflection preventing effect, a film having a different refractive index may be stacked. The film may be provided only at pillar sections having high refractive indices by forming the film before processing the pillars 203.

**[0049]** The filler material 201 is provided in spaces between the pillars 203, and can prevent the pillars 203 from collapsing, and can prevent tapes from being left after assembly steps. The filler material 201 may be provided not only in the spaces between the pillars 203, but provided to cover the pillars 203 on the light-incidence-surface side of the pillars 203.

**[0050]** The inorganic protective film 200 is included above the filler material 201, and it becomes possible to avoid damage to the filler material 201 at the time of peeling of a PAD resist of PAD openings at a latter step. The film thickness of the filler material 201 from the upper ends of the pillars 203, and the film thickness of the inorganic protective film 200 may be determined taking into consideration a target wavelength and refractive indices such that the multilayer films as a whole cancel out reflected waves, by using the Fresnel coefficient method or the like, for example.

**[0051]** Note that whereas the configuration example of the pixels disclosed here depicts a backside illumination photodetector, this is not the sole example, and the present technology can be applied to a frontside illumination photodetector, and furthermore to a photodetector using an organic photoelectric conversion film or the like.

<First Modification Example of First Embodiment>

(Metasurface Elements at Multiple Stages)

10

15

20

30

35

50

55

**[0052]** FIG. 5 is a partial vertical cross-sectional view depicting an example of the semiconductor structure of the photodetector 1 according to a first modification example of the first embodiment. In FIG. 5, portions identical to their counterparts in FIG. 3 described above are given identical reference signs, and detailed explanations thereof are omitted. **[0053]** FIG. 5 depicts multi-stage configuration in which a deflecting section 2002 is stacked on the light-incidence side of the deflecting section 2001. The deflecting section 2002 includes a filler material 2151, a reflection preventing film 2161, pillars 2171, and a reflection preventing film 2181. The inorganic protective film 200 is stacked on the light-incidence side of the deflecting section 2002.

**[0054]** As mentioned above, according to the first modification example of the first embodiment, it becomes possible to reduce the aspect ratio of pillars per stage by forming a multi-stage structure, and it is possible to avoid the problem of pattern collapses in a case where it is difficult to increase the heights of the pillars 203 and 2171 due to pattern collapses or the like that occur at the time of chemical drying in Wet cleaning. Furthermore, a pillar structure with a single layer is principally designed on the premise that there is a single wavelength, but, by providing the pillars 203 and 2171 at the multiple stages, it become possible to cope with a wide band of wavelengths and multi-spectrums by combining stages with different designs. Furthermore, it becomes possible also to realize deflection control.

<Second Modification Example of First Embodiment>

(Metasurface Elements Including Filler Material in Box Lens Shapes)

[0055] FIG. 6 is a partial vertical cross-sectional view depicting an example of the semiconductor structure of the photodetector 1 according to a second modification example of the first embodiment. In FIG. 6, portions identical to their counterparts in FIG. 3 described above are given identical reference signs, and detailed explanations thereof are omitted. [0056] In FIG. 6, a filler material 201-1 of a deflecting section 2003 has openings in trench shapes at the boundaries between the pixels 100. Whereas the figure depicts an instance of the trenches that stop at middle portions, the trenches can also penetrate the filler material 201-1, thereby enhancing the lens power of box lenses. Desirably, the inorganic protective film 200 is stacked on the top surface (incidence-surface side) of the filler material 201-1 in the box lens shapes, from the viewpoint of assembly. Furthermore, the inorganic protective film 200 may be stacked on the side walls of the box lens shapes, thereby allowing an improvement of reliability such as control of moisture absorption of the filler material 201-1.

**[0057]** As mentioned above, according to the second modification example of the first embodiment, in addition to control of the pillars 203, it becomes possible to guide light near the boundary of a subject pixel 100 to the pixel 100 by using a refractive index difference between the filler material 201-1 and the atmospheric air. This gives a lens effect and a waveguide effect to the filler material 201-1, thereby making it possible to enjoy advantages in terms of color mixing suppression and higher sensitivity. Desirably, the material and film thickness of the inorganic protective film 200 is selected according to the X/4n rule to prevent reflection. Regarding the manufacturing method, it is sufficient if, after the pillars 203 and the filler material 201-1 are formed, processing is performed by anisotropic etching using a resist mask, and, after cleaning is performed as necessary, an inorganic surface protective film is formed by CVD, sputtering, or the like.

(Pixel Manufacturing Method)

10

30

35

40

50

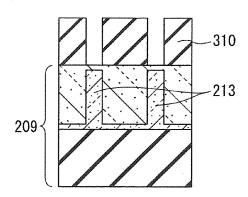

[0058] An example of a method of manufacturing the photodetector 1 in the present first embodiment is depicted in FIG. 7A to FIG. 7E.

**[0059]** In a region of the semiconductor substrate 209, for example, a silicon substrate, in the photodetector 1 of the present first embodiment where a pixel region should be formed, photoelectric converting sections separated by the element separating sections 213 as p-type semiconductor regions are formed. The photoelectric converting sections are formed as regions having pn junctions including n-type semiconductor regions formed to extend in the entire region in the substrate thickness direction, and p-type semiconductor regions that are in contact with the n-type semiconductor regions, and face both the front and back surfaces of the substrate.

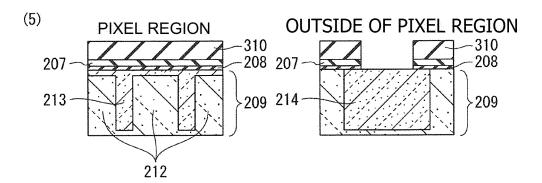

**[0060]** For example, as depicted in (1) of FIG. 7A, impurity regions are formed by ion-implanting desired impurities from the front-surface side of the semiconductor substrate 209 by using a resist 310 as a mask. The p-type semiconductor well regions, each of which is in contact with an element separating section 213, are formed in regions on the surface of the semiconductor substrate 209 that correspond to the respective pixels, and each plurality of pixel transistors are formed in each p-type semiconductor well region. Each pixel transistor includes a source region and a drain region, a gate insulating film, and a gate electrode.

**[0061]** Furthermore, the wiring layer 210 including aluminum, copper, or the like is formed on the top of the surface of the semiconductor substrate 209 with interlayer dielectric films such as SiO2 films interposed therebetween. Throughvias are formed between the pixel transistors formed on the substrate surface and the wiring layer, and are electrically connected for driving the photodetector 1. Interlayer dielectric films such as SiO2 films are stacked on the wires. Each interlayer dielectric film is flattened by chemical mechanical polishing (CMP) to make the surface of the wiring layer a substantially flat surface, and while connection is established with underlying-layer wires by through-vias, wires are formed thereon. This is repeated to sequentially form wires of each layer.

[0062] Next, as depicted in (2) of FIG. 7A, the semiconductor substrate 209 is turned upside down, and is pasted onto the support substrate 211 by plasma joining or the like. For example, after the semiconductor substrate 209 is made thinner by wet etching or dry etching from its back-surface side, for example, the semiconductor substrate 209 is made thinner to a desired thickness by CMP as depicted in (3) of FIG. 7B. The thickness of the semiconductor substrate 209 depends on an expected wavelength region. The thickness of the semiconductor substrate 209 is desirably in the range from 2 to 6  $\mu$ m, for example, if the expected wavelength region includes only the visible light region, and is desirably in the range from 3 to 15  $\mu$ m, for example, if the expected wavelength region to be sensed includes also the near-infrared region, but these are not the sole examples.

**[0063]** As depicted in (4) of FIG. 7B, the fixed electric charge film 208 can be formed by CVD, sputtering, or atomic layer deposition (ALD: Atomic Layer Deposition). In a case where ALD is adopted, this is suitable since favorable coverage can be attained at the atomic layer level, and it becomes possible to simultaneously form a silicon oxide film that reduces the interface state during the film formation of the fixed electric charge film 208. By controlling the film thickness or stacking multiple layers, desirably, the fixed electric charge film 208 doubles as a reflection preventing film for the Si substrate having a high refractive index. It is better if the insulating film 207, for example, SiO2 formed as a film by ALD, has a thickness which is at least equal to or greater than 20 nm, desirably equal to or greater than 50 nm, since film peeling due to the blistering phenomenon becomes likely to occur if the thickness is small.

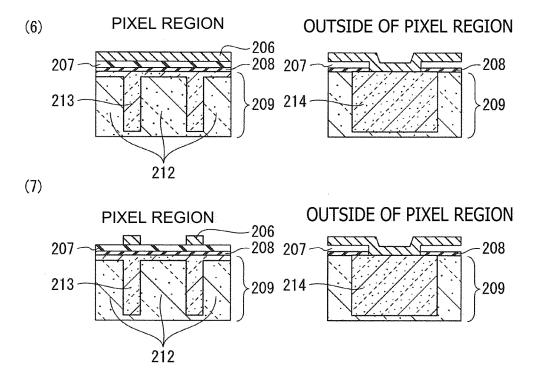

[0064] As the light blocking metal 206, a material mentioned before is formed as a film by using CVD, sputtering, or the like. Note that since there is a risk that plasma damage occurs if a metal is processed in an electrically floating state, desirably, as depicted in (5) of FIG. 7B, etching patterns of a resist with a width of, for example, several micrometers are transcribed in an outer region (the right side in (5) of FIG. 7B) of the photodetector 1, the surface of the semiconductor substrate 209 is exposed by forming grooves by anisotropic etching or wet etching, and then, as depicted in (6) of FIG. 7C, the light blocking metal 206 is formed as a film in a state where it is grounded to the semiconductor substrate 209. [0065] Desirably, a semiconductor substrate region to which the light blocking metal 206 is grounded is given in advance a ground potential as a p-type semiconductor region, for example. The light blocking metal 206 may be formed by stacking multiple layers, and, for example, formed as layers of titanium, titanium nitride, or stacked films of them that closely contact the insulating film 207. Alternatively, only titanium, titanium nitride or stacked films of them can also be used as the light blocking metal 206.

[0066] In addition, the light blocking metal 206 can also double as a light blocking film of a black-level calculation pixel (not depicted) which is a pixel 100 for calculating the black level of an image signal or a light blocking film for preventing operation errors of peripheral circuits. Next, as depicted in (7) of FIG. 7C, for example, etching patterns of openings for guiding light to the photoelectric converting sections 212 and furthermore pad sections, scribe line sections, or the like are formed in a resist on the light blocking metal 206, the light blocking metal 206 is partially removed by anisotropic etching or the like, and remnants are removed by chemical cleaning as necessary.

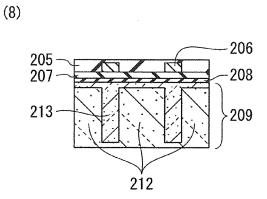

**[0067]** Next, as depicted in (8) of FIG. 7C, the insulating film 205, for example, SiO2, is formed by using CVD, sputtering, or the like on the light blocking metal 206, and is flattened by CMP.

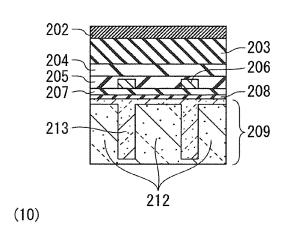

[0068] Furthermore, as depicted in (9) of FIG. 7D, for example, SiN is formed as a film having a thickness of 125 nm as the reflection preventing film 204 by using CVD, for example. For example, the amorphous silicon is formed as a film having a thickness of 800 nm as a material of the pillars 203, and, for example, SiN is formed as a film having a thickness of 125 nm as the reflection preventing film 202. Note that, in a case where degassing of hydrogen or the like occurs from the pillar material in thermal treatment at a latter step, if a highly-sealable dense film such as a SiN film is provided in contact with the pillar material, gas is confined at the interface, and circular floating portions of the film called blisters are formed undesirably. As a measure to avoid this, as vents for the gas, holes may be formed to penetrate parts of an outer region of the pixel array section 10 or parts of the boundary sections of the pixels 100. By providing the holes in such a manner, it is possible to avoid blisters, and specifically Ta2O5 or the like is suitable. Note that the film thickness needs to be set to a thickness which is optimum for a reflection preventing film, depending on individual selection of a material.

**[0069]** Next, as depicted in (10) of FIG. 7D, the reflection preventing film 204 and the pillars 203 are processed into columnar forms by using a resist as a mask. In a case where the selectivity of the resist is insufficient, hard mask processing in which the resist pattern is transcribed once onto a hard mask, for example, a SiO2 mask, and etching is performed through the hard mask may be performed. Note that the reflection preventing film 204 under the pillars 203 are provided for the purpose of optical reflection prevention, and, in addition to the functionality, may serve as an etching stopper layer at the time of the etching.

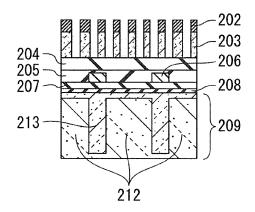

**[0070]** Next, Wet chemical cleaning is performed in order to remove resist residues and process remnants. After the chemical cleaning, typical spin drying undesirably increases the risk of pattern collapses due to imbalanced surface tension at the time of the chemical drying. As a measure against this, drying may be performed after replacement with IPA having low surface tension or furthermore supercritical cleaning may be used.

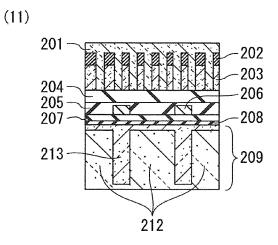

**[0071]** Next, as depicted in (11) of FIG. 7E, the filler material 201 is formed between the pillars 203. Desirably, the filler material 201 is transparent to a target wavelength, and a material having a large refractive index difference relative to the pillars 203 is used therefor. For example, the filler material 201 may be formed by spin-coating of a fluorine-containing siloxane-based resin. By providing the filler material 201 in such a manner, it becomes possible to avoid damage to the pillars 203 or defects related to adhesive residues when a protection tape is peeled at the time of assembly, and to avoid malfunction modes due to drop impacts when on the market.

**[0072]** Next, as depicted in (12) of FIG. 7E, in a case where the filler material 201 is an organic material, the inorganic protective film 200, for example, SiO2, may be provided at the uppermost section of the filler material 201. By providing the inorganic protective film 200 in such a manner, it becomes possible to avoid damage to the filler material 201 due to peeling of a resist at the time of PAD processing.

<Third Modification Example of First Embodiment>

35 (Configuration Example of Pillars) Prism Functionality

10

20

30

40

50

55

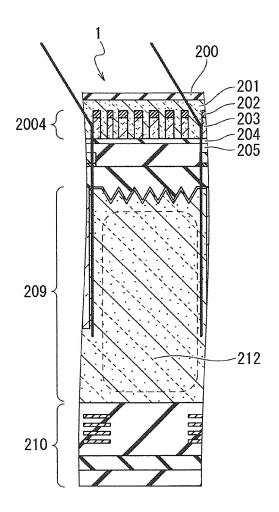

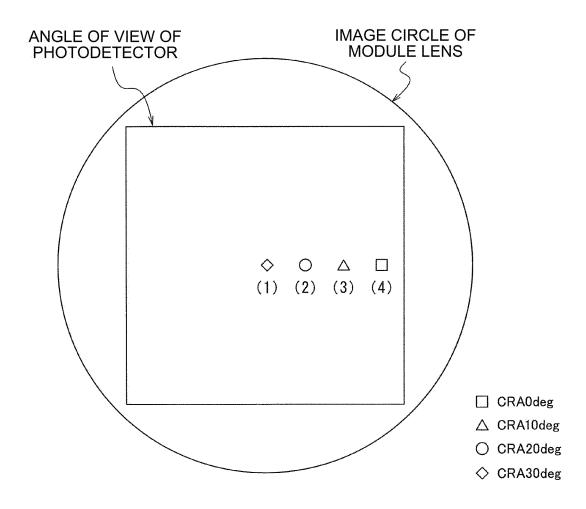

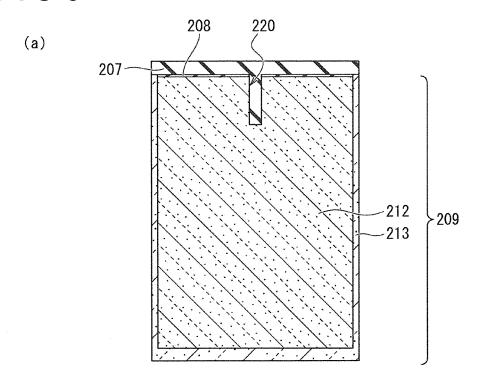

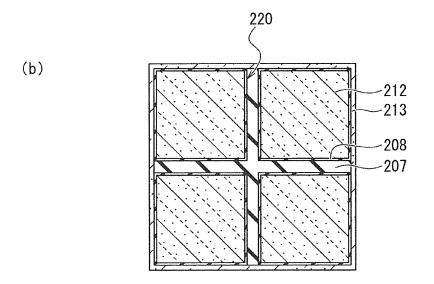

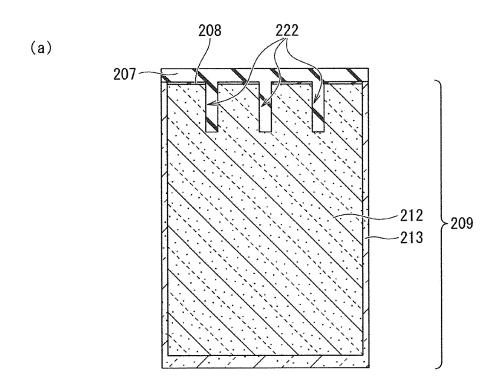

[0073] FIG. 8 is a partial vertical cross-sectional view depicting an example of the semiconductor structure of the photodetector 1 according to a third modification example of the first embodiment. In FIG. 8, portions identical to their counterparts in FIG. 3 described above are given identical reference signs, and detailed explanations thereof are omitted. [0074] In a deflecting section 2004 in FIG. 8, pillars 203 of each pixel are designed to have a deflection design according to a prism angle necessary for the image height, according to image heights in order to use light at angle-of-view ends of the photodetector 1 effectively. For example, a deflecting section 2004-1 corresponding to a pixel 100 positioned at the angle-of-view middle (the image height is zero) depicted in (1) of FIG. 9 has  $10 \times 10$  pillars 203-1 arranged therein with the same pillar diameter as depicted in (1) of FIG. 10. Arranging the pillars 203-1 in such a manner prevents occurrence of a phase difference change in the pixel 100, and light that is incident on the deflecting section 2004-1 vertically is transmitted vertically toward the photoelectric converting section 212.

[0075] In a case of an image height (2) depicted in FIG. 9, a principal ray is incident at an inclination of 10 deg in the horizontal direction, and a deflecting section 2004-2 is provided to a pixel 100 corresponding to the image height (2). As depicted in (2) in FIG. 10, in the deflecting section 2004-2, in view of a prism angle necessary for the image height (horizontal 10 deg), for example, pillars 203 may not be arranged in the fifth column, the pillars 203-1 may be arranged in the first column and the second column, pillars 203-2 with a diameter smaller than the pillars 203-1 may be arranged in the third column and the fourth column, and pillars 203-3 with a diameter larger than the pillars 203-1 may be arranged in the sixth column to the tenth column. By arranging the pillars 203 in such a manner, a gradient of continuous phase differences is generated at the pillar section, and light that is incident on the deflecting section 2004-2 at 10 deg is transmitted vertically toward the photoelectric converting section 212.

**[0076]** In a case of an image height (3) depicted in FIG. 9, a principal ray is incident at an inclination of 20 deg in the horizontal direction, and a deflecting section 2004-3 is provided to a pixel 100 corresponding to the image height (3). For example, as depicted in (3) of FIG. 10, in the deflecting section 2004-3, in view of a prism angle necessary for the

image height (horizontal 20 deg), the pillars 203-1 may be arranged in the first column to the fourth column, the pillars 203-2 may be arranged in the fifth column, the pillars 203-3 may be arranged in the sixth column and the eighth column, and pillars 203-4 with a diameter smaller than the pillars 203-3 and larger than the pillars 203-1 may be arranged in the ninth column and the tenth column. The linear inclination of phase differences at this time is set to an inclination which is approximately twice as large as that at the time of 10 deg. By arranging the pillars 203 in such a manner, a gradient of continuous phase differences is generated at the pillar section, and light that is incident on the deflecting section 2004-3 at 20 deg is transmitted vertically toward the photoelectric converting section 212.

**[0077]** In a case of an image height (4) depicted in FIG. 9, a principal ray is incident at an inclination of 30 deg in the horizontal direction, and a deflecting section 2004-4 is provided to a pixel 100 corresponding to the image height (4). As depicted in (4) of FIG. 10, in the deflecting section 2004-4, pillars 203 may be arranged in view of a prism angle necessary for the image height (horizontal 30 deg). The linear inclination of phase differences at this time is set to an inclination which is approximately three times as large as that at the time of 10 deg. By arranging the pillars 203 in such a manner, a gradient of continuous phase differences is generated at the pillar section, and light that is incident on the deflecting section 2004-4 at 30 deg is transmitted vertically toward the photoelectric converting section 212. Note that (1) to (4) of FIG. 9 are examples, and it becomes possible also to adopt a layout which is different in terms of 211 turns of phase differences or offset processes mentioned later. What is important is relative phase differences between the pillars 203.

(Derivation of Metasurface Design)

10

20

30

40

50

(Step 1) Derivation of Phase Difference Map for Each Pixel

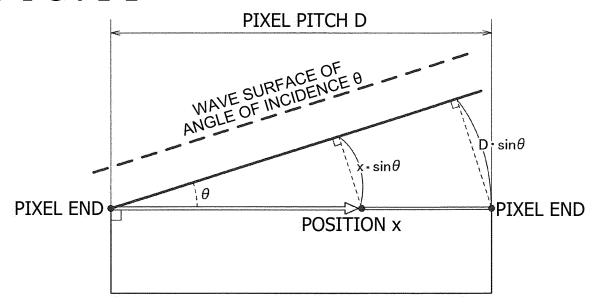

**[0078]** As depicted in FIG. 11, when it is assumed that the angle of incidence of light of a certain pixel 100 is  $\theta$ , its pixel size is D, an expected wavelength is X, and a pillar position in the pixel is x, a phase difference necessary for vertical incidence can be determined according to Formula (1). [Math. 1]

$$\Delta \varphi_{pri}(x) = \frac{x \cdot \sin\theta - D \cdot \sin\theta}{\lambda}$$

... Formula (1)

<sup>35</sup> **[0079]** Whereas a prism angle in the x direction is depicted for simplification here, a phase difference map corresponding to prism angles of any directions can be created by two-dimensional extension as depicted in FIG. 12.

**[0080]** Note that since it is sufficient if relative phase differences are set between pillars 203 in a prism design, the variability of constants is tolerated.

(Step 2) Derivation of Phase Difference library

**[0081]** For the structure to be mounted on the photodetector 1, taking into consideration the pitches, heights, refractive indices, extinction coefficients, and shapes of pillars, the film composition near the pillars and the like, a phase difference library associating phase differences and pillar diameters is created as depicted in FIG. 13.

**[0082]** The phase difference library may be calculated by performing optical simulation such as FDTD or RCWA or can also be determined experimentally. Note that light with a phase difference a is equivalent to  $\alpha$  +  $2\Pi$  × N (N is an integer). That is, even in a case where the phase difference of  $2\Pi$  +  $\phi$  is necessary, it is sufficient if only the phase difference of  $\phi$  is set. Such replacement with an equivalent phase is called a " $2\Pi$  turn."

(Step 3) Derivation of Pillar Layout

**[0083]** On the basis of the phase difference map, a phase difference of each pillar 203 can be replaced with a pillar diameter by using the phase difference library, but since there are constraints in terms of process limitations due to various causes such as the resolution of lithography or pattern collapses of high-aspect-ratio pillars, these are specified as design rules, and control is performed such that pillars 203 to be generated satisfy the design rules.

**[0084]** Specifically, after adjustment (uniform offset process) of constant terms depicted in (a) in FIG. 14 for phase differences, a process of a  $2\Pi$  turn depicted in (b) in FIG. 14 is performed, and then a process of replacing the phase difference of each pillar 203 with a pillar diameter depicted in (c) in FIG. 14 can be performed by using the phase

difference library. In a case where the design rules cannot be satisfied with these processes, the following measures are taken

[0085] The first measure is forcibly making a non-2 II turn. In a case where this process is performed, there is concern that scattering occurs at a turn portion, and stray light is generated.

**[0086]** The second measure is to forcibly perform a rounding process such that pillar diameters of patterns not satisfying the design rules approximate to the pillar diameters of their closest phases satisfying the design rules. The amounts of rounding can be errors, but this can be tolerated if the influence on pixel characteristics is only to the extent that does not cause a problem.

10 <Fourth Modification Example of First Embodiment>

(Configuration Example of Pillars) Prism Functionality + Lens Functionality

**[0087]** FIG. 15 is a plan view depicting the angle of view of the photodetector 1 according to a fourth modification example of the first embodiment.

**[0088]** In a deflecting section 2005 in FIG. 15, pillars 203 of each pixel 100 are designed to have a combination of a lens design to condense light onto the center of the pixel according to image heights, and a deflection design according to a prism angle necessary for the image height in order to use light at angle-of-view ends of the photodetector 1 effectively.

20 (Derivation of Metasurface Design)

15

25

30

35

40

50

55

(Step 1) Derivation of Phase Difference Map for Each Pixel

[0089] If a phase difference map for attaining a lens functionality and a phase difference map for attaining a prism functionality can be determined, these are simply added for each pillar, and thereby it is possible to synthesize a phase difference map ((c) of FIG. 17) combining the lens functionality and the prism functionality. An explanation of the procedure of deriving a prism phase difference map depicted in (a) in FIG. 17 is omitted since it is mentioned before. Phase differences in a lens phase difference map depicted in (b) in FIG. 17 can be calculated from lens thicknesses corresponding to respective pillar positions and an expected wavelength if expected lens shapes and refractive indices are known, as mentioned later. Alternatively, the phase differences may be calculated by performing optical simulation such as FDTD or RCWA or can also be determined experimentally. Note that, for a telecentric optical system or the like, it is also possible to give only the lens functionality without adopting a prism design for each pixel 100.

**[0090]** Thereafter, (Step 2) the derivation of phase difference library and (Step 3) the derivation of pillar layout are performed, but since details of these are mentioned before, explanations thereof are omitted.

[0091] As a specific example, FIG. 16 discloses an array of pillar diameters designed to combine the lens functionality and the prism functionality for each image height depicted in FIG. 15 in a case where a principal ray from a module lens is incident at (1) 0 deg, (2) horizontal 10 deg, (3) horizontal 20 deg, and (4) horizontal 30 deg. These are instances of amorphous silicon in a case where pillar pitches are 0.35  $\mu$ m, the pixel size is 3.5  $\mu$ m, the height of pillars 203 is 600 nm, and the refractive index of the filler material between pillars is approximately 1.5. By adopting designs in such a manner, deflecting elements that combine the lens functionality and the prism functionality simultaneously can be provided.

**[0092]** In a more generalized expression, if a refractive index and a geometric shape of a material at the time when it is attempted to mount, on each pixel, an optical element which is given a certain functionality can be given, it is possible to make the shape reflected in a phase difference map, and the functionality can be realized by specifying the diameter of each pillar by conversion based on a phase difference library, and creating pillar elements. Furthermore, by synthesizing multiple phase difference maps designed in such a manner, it becomes possible also to realize multiple functionalities simultaneously.

**[0093]** As an example of optical elements, as depicted in FIG. 18, if a function of a lens thickness T(x,y) is given for the position (x,y) of a pillar, a lens phase difference map is determined according to Formula (2) when the refractive index of a lens is n1, and the refractive index above the lens (e.g., atmospheric air) is n2. [Math. 2]

$$\Delta \varphi_{lens}(x,y) = \frac{T(x,y)}{(n_1 - n_2)\lambda}$$

... Formula (2)

(Material of Pillars)

[0094] The material of pillars 203 is desirably  $\alpha$ -Si, Poly-Si, or germanium in a case where they are used for near-infrared light, and is desirably any material selected from titanium oxide, niobium oxide, tantalum oxide, aluminum oxide, hafnium oxide, silicon oxynitride, silicon oxynitride, silicon oxycarbide, silicon oxycarbide, silicon carbonitride, and zirconium oxide or a stacked structure body of these in a case where they are used for visible light. Note that silicon oxynitride, silicon oxycarbide, and silicon carbonitride are included in polycrystalline silicon, for example.

(Pillar Arrays)

10

30

40

45

50

[0095] Spaces between pillars 203 are equal to or shorter than the target wavelength of light.

**[0096]** A square array may be adopted as depicted in (a) of FIG. 19 or a hexagonal close-packed array may be adopted as depicted in (b) of FIG. 19.

15 (Cross-Sectional Shapes of Pillars)

**[0097]** The shapes of metasurface elements, pillars 203, are determined from the viewpoint of anisotropic control of deflected components, reflected components dependent on area rates, processability, and pattern collapse resistance, in addition to control of effective refractive indices. Varied patterns of their top views are depicted in FIG. 20.

[0098] (1) to (3) of FIG. 20 excel in isotropy of deflection control. Alternatively, from the viewpoint of deflection, (4) to (8) of FIG. 20 have 4-fold symmetry or mirror symmetry about a horizontal axis, a vertical axis or an axis in the direction of 45 degrees or 135 degrees. Alternatively, from the viewpoint of deflection, (9) to (21) of FIG. 20 exhibit uniaxial characteristics.

**[0099]** Furthermore, in a case where a pattern collapse occurs when control is performed by making the shorter sides in (12) of FIG. 20 shorter, desirably, an auxiliary pattern for collapse prevention like (22) or (23) of FIG. 20 is arranged. If comparisons are made assuming that the cross-sectional areas are the same, (3), (5), (11), (13), (17), and (19) of FIG. 20 can avoid the risk of pattern collapses, and additionally allow small effective refractive index differences to be set, since they have doughnut shapes. Furthermore, if comparisons are made assuming that pitches are identical, (4) and (5) of FIG. 20 enhance pillar filling rates in cases of square arrays, (1) to (3) of FIG. 20 enhance pillar filling rates in cases of hexagonal close-packed arrays, and these are advantageous in a case where phase differences are set.

**[0100]** In addition, simulation can be performed to predict pattern collapses and un-resolvability as depicted in FIG. 21, and in a case where patterns are likely to fall under those cases, the layout or pattern shape can be corrected by using rules or simulation, to an extent that changes of an effective refractive index distribution can be tolerated.

35 (Height of Pillars)

**[0101]** Desirably, the heights are set such that phases of  $2\Pi$  or more can be attained within the range of pillar diameters that can be attained with processing, for a phase difference library specified by a wavelength, the refractive indexes of the pillars 203 and the filler material 201, pillar shapes and heights, and the like.

**[0102]** FIG. 22 depicts an example of a phase difference library of circular amorphous Si pillars at pitches of 350 nm. In a case where processing limits specify that the pillar diameter be 250 nm, desirably, the pillar height is set to approximately 800 nm.

(About Turn of Phases)

----

**[0103]** As depicted in FIG. 23, if phases become discontinuous, scattering occurs, and stray light is generated undesirably. Alternatively, if neighboring pixels have different area rates, variation of output power occurs undesirably since reflected components (sensitivity losses) differ between pixels. Accordingly, preferably, phases have a turn according to the rules (a) and (b) described below.

(a) There are turns in units of pixels.

- (b) A turn in a pixel is near the pixel center.

- [0104] According to the rule (a), the area rates of pixels positioned nearby are made identical to each other, and it becomes possible to suppress reflectance variation. According to the rule (b), if stray light from a turn portion crosses a pixel boundary, crosstalk occurs, leading to characteristics deterioration undesirably. Accordingly, desirably, a sufficient distance is ensured between a turn and each pixel boundary. That is, suitably, in terms of symmetry, an intra-pixel turn is set such that it passes near the pixel center.

16

(Reflection Preventing Film)

[0105] FIG. 24 is a partial vertical cross-sectional view depicting reflection preventing films formed on a pillar 203. [0106] Reflection preventing films 202 and 204 having different refractive indices and having such film thicknesses that the phases of reflected waves cancel out each other are provided to the top of the pillar 203, the bottom of the pillar 203 or both. Specifically, desirably, the thicknesses of the reflection preventing films are  $\lambda/(4\cdot n)$  assuming that the refractive index is n and the wavelength is  $\lambda$ . For example, for an expected wavelength of 940 nm, the thicknesses are estimated to be approximately 125 nm in a case of SiN (n  $\approx$  1.9). Actually, it is necessary to take into consideration multilayer-film interference effects and oblique incidence characteristics, and desirably the thicknesses are optimized by optical simulation or actual measurement.

(Processing Shapes of Pillars)

**[0107]** FIG. 25A depicts a structure including a reflection preventing film that doubles as an etching stopper layer. In FIG. 25A, the reflection preventing film 202 and pillars 203 are etched by anisotropic dry etching. In order to cause the reflection preventing film 204 to double as an etching stopper layer, the reflection preventing film 204 needs to be a material having a high etching selectivity relative to the material of the pillars 203, not only from the viewpoint of refractive indices. After dry etching, the reflection preventing film 204 has smaller film thicknesses between the pillars, while the film thicknesses of portions directly below the pillars are kept at the initial film thicknesses.

20 [0108]

10

15

25

30

40

50

55

(1) of FIG. 25B depicts a peeling prevention structure of the filler material 201 by using wedge shapes at the pillar bottoms. By adopting such shapes, the filler material 201 bites into and is caught by the wedge sections of the pillar bottoms like hooks, and the film peeling resistance can be improved. (2) of FIG. 25B depicts a structure in which, in addition to what is depicted in (1), the wedge sections are processed into rounded shapes with flaring ends. Due to these rounded shapes, stress concentration at steps of the reflection preventing film 204 can be reduced, and pattern collapses can be suppressed.

**[0109]** A method of processing for these pillar shapes is mentioned. Due to over-etching at the time of anisotropic dry etching of the pillars, portions between the pillars have vertically-shallow groove shapes. Next, by implementing Wet chemical processing, isotropic film-thickness reduction occurs, and the reflection preventing film 204 can be processed to have rounded wedge shapes at portions that are directly below the pillars and where the etching rate is higher than the pillar material.

35 (Configuration Example of Filler Material (Filler))

**[0110]** For the filler material 201, a siloxane-based resin, a styrene-based resin, an acrylic resin, a styrene-acrylic copolymer resin, a F-containing material of the resin, a F-containing material of the resin, or a material including the resin internally filled with beads having a refractive index which is lower than the refractive index of resin is used as an organic material.

**[0111]** In addition, for the filler material 201, silicon oxide, niobium oxide, tantalum oxide, aluminum oxide, hafnium oxide, silicon nitride, silicon oxynitride, silicon carbide, silicon oxycarbide, silicon carbonitride, zirconium oxide, and a stacked structure body of these inorganic materials can also be used.

45 (Another Method of Manufacturing Filler Structure)