(19)

(11) **EP 4 550 332 A2**

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication: **07.05.2025 Bulletin 2025/19**

(21) Application number: 25163028.1

(22) Date of filing: 18.07.2018

(51) International Patent Classification (IPC): G11C 11/4093 (2006.01)

(52) Cooperative Patent Classification (CPC):

G11C 11/4074; G11C 5/066; G11C 7/1057;

G11C 7/1084; G11C 7/1096; G11C 8/06;

G11C 11/4093; G11C 11/4096; Y02D 10/00

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

(30) Priority: 19.07.2017 US 201762534436 P

(62) Document number(s) of the earlier application(s) in accordance with Art. 76 EPC: 18835212.4 / 3 655 952

(71) Applicant: Micron Technology, Inc. Boise, ID 83716-9632 (US)

(72) Inventors:

HOLLIS, Timothy M. Meridian, 83642 (US)

• DIMITRIU, Dragos Boise, 83716 (US)

(74) Representative: Carpmaels & Ransford LLP One Southampton Row London WC1B 5HA (GB)

#### Remarks:

This application was filed on 11.03.2025 as a divisional application to the application mentioned under INID code 62.

# (54) APPARATUSES AND METHODS FOR PROVIDING ADDITIONAL DRIVE TO MULTILEVEL SIGNALS REPRESENTING DATA

(57) Apparatuses and methods for providing additional drive to multilevel signals representing data are described. An example apparatus includes a first driver section, a second driver section, and a third driver section. The first driver section is configured to drive an output terminal toward a first selected one of a first voltage and a second voltage. The second driver section configured to drive the output terminal toward a second

selected one of the first voltage and the second voltage. The third driver section configured to drive the output terminal toward the first voltage when each of the first selected one and the second selected one is the first voltage. The third driver circuit is further configured to be in a high impedance state when the first selected one and the second selected one are different from each other.

#### **BACKGROUND**

**[0001]** The pursuit of making computing systems more faster and more power efficient has led to advancement in interface communications to improve throughput without increasing. and ideally reducing, energy consumption. Often, as clock speeds increase, a desire to increase data transition times on interface busses to match the faster clock speeds exists. Future double data rate (DDR) dynamic random-access memory (DRAM) performance targets will soon exceed DRAM transistor switching capabilities. Some systems have implemented multi-level (e.g., more than two levels) signaling architectures to increase throughput over an interface bus.

1

[0002] A challenge with multilevel signaling in high speed, high bandwidth, low power memory systems is non-idealities that negatively affect system performance, for example, with regards to signal voltage levels, signal voltage margins. An example is the inability for signal drivers to fully drive the voltage levels of the multilevel signals to a high supply voltage or to a low supply voltage within a data period due to non-ideal performance of the circuits (e.g., pull-up and pull-down transistors) of the signal drivers. Variations in power, temperature, and fabrication process may further degrade system performance. As a result, the voltage range for the multilevel signals is reduced, which decreases the voltage margins for the different voltage levels. More generally, the signal drivers may be unable to adequately drive the multilevel signals to the correct voltage levels, which may result in data errors.

# SUMMARY

disclosed herein. An example apparatus according to an embodiment of the disclosure may include: a first driver section that may drive an output terminal toward a first selected one of a first voltage and a second voltage; a second driver section that may drive the output terminal toward a second selected one of the first voltage and the second voltage; and a third driver section that may drive the output terminal toward the first voltage when each of the first selected one and the second selected one is the first voltage, the third driver circuit further configured to be in a high impedance state when the first selected one and the second selected one are different from each other. [0004] Another example apparatus according to an embodiment of the disclosure may include: a driver circuit that may provide an output signal at a node responsive to a plurality of input signals, a boost circuit including a transistor coupled to the node and a supply voltage, when activated the boost circuit may provide additional drive to change the voltage of the node; and a boost control circuit that may provide a signal to activate the boost circuit

[0003] Apparatuses and methods for providing addi-

tional drive to multilevel signals representing data are

based on the logic levels of the plurality of input signals. Each of the plurality of input signals may have a respective logic level, and the output signal may have a voltage representing the logic levels of the plurality of input signals.

[0005] Another example apparatus according to an embodiment of the disclosure may include: a driver circuit that may provide at a node an output signal having a voltage indicative of a value of the data represented by a plurality of input bitstreams; a boost circuit that may be coupled to the node and may couple a supply voltage to the node when activated by an active boost signal; and a boost control circuit that may provide the boost signal to activate the boost circuit responsive to the data represented by the plurality of input bitstreams changing from a first value to a second value different from the first value. [0006] An example method according to an embodiment of the disclosure may include steps of: driving at a node of a driver circuit a multilevel output signal having a voltage indicative of data represented by logic levels of bits of a plurality of bitstreams: and additionally driving the node with a boost circuit responsive to the logic levels of the bits of the plurality of bitstreams.

#### 5 BRIEF DESCRIPTION OF THE DRAWINGS

#### [0007]

20

35

40

45

Figure 1 is a block diagram of an apparatus according to an embodiment of the present disclosure.

Figure 2A is a block diagram of an apparatus for a multilevel communication architecture according to an embodiment of the disclosure. Figure 2B is a block diagram of an apparatus for a multilevel communication architecture according to an embodiment of the disclosure.

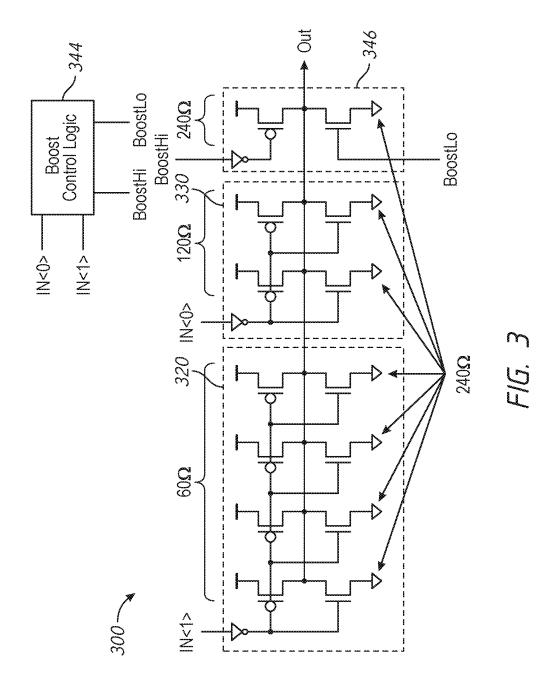

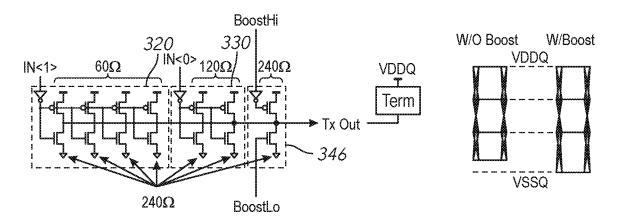

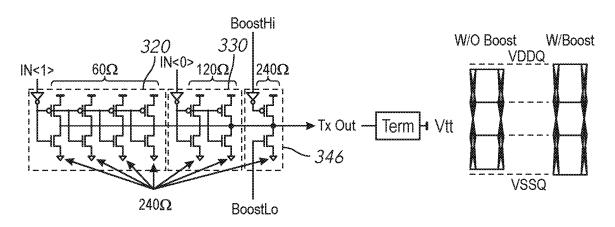

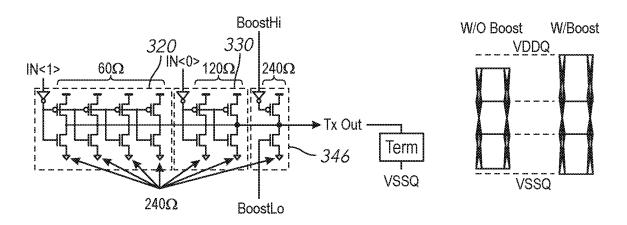

Figure 3 is a schematic drawing of a signal driver according to an embodiment of the disclosure.

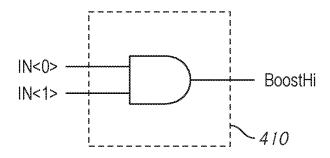

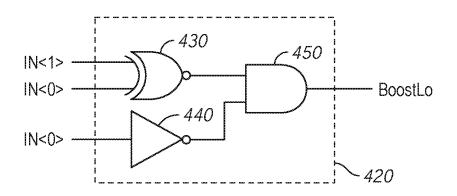

Figure 4A is a schematic diagram of a boost control circuit according to an embodiment of the disclosure. Figure 4B is a schematic diagram of a boost control circuit according to an embodiment of the disclosure. Figures 5A-5C are diagrams showing operation of a signal driver according to various embodiments of the disclosure.

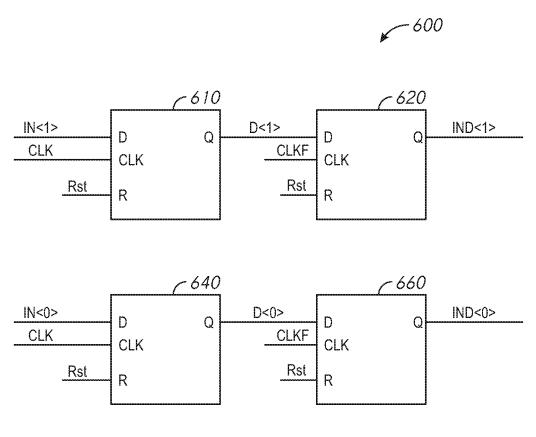

Figure 6 is a schematic diagram of an input circuit for a boost control circuit according to an embodiment of the disclosure.

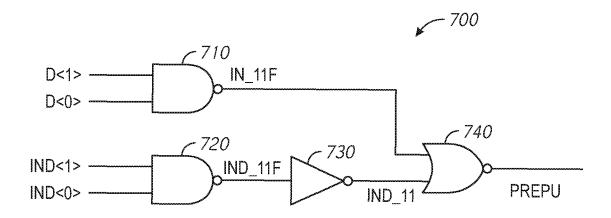

Figure 7A is a schematic diagram of a pull-up logic circuit for a boost control circuit according to an embodiment of the disclosure. Figure 7B is a schematic diagram of a pull-down logic circuit for a boost control circuit according to an embodiment of the disclosure.

Figure 8 is a timing diagram showing various signals during operation of a signal driver according to an embodiment of the disclosure.

Figure 9A is a schematic diagram of a pull-up logic

20

circuit for a boost control circuit according to an embodiment of the disclosure. Figure 9B is a schematic diagram of a pull-down logic circuit for a boost control circuit according to an embodiment of the disclosure.

Figure 10 is a timing diagram showing various signals during operation of signal driver according to an embodiment of the disclosure.

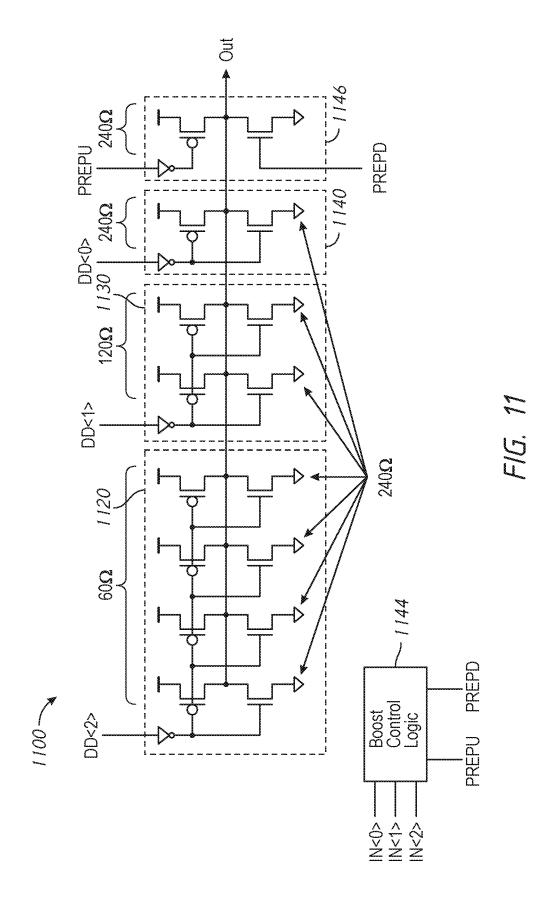

Figure 11 is a schematic diagram of a signal driver according to an embodiment of the disclosure.

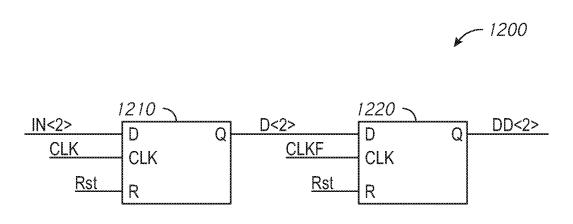

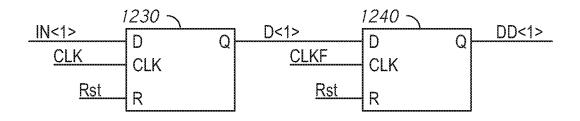

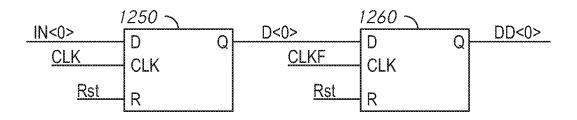

Figure 12 is a schematic diagram of an input circuit for a boost control circuit according to an embodiment of the disclosure.

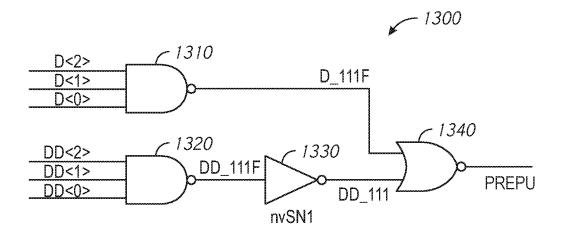

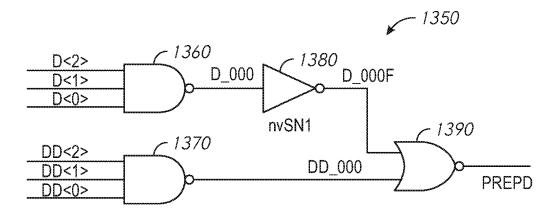

Figure 13A is a schematic diagram of a pull-up logic circuit for a boost control circuit according to an embodiment of the disclosure. Figure 13B is a schematic diagram of a pull-down logic circuit for a boost control circuit according to an embodiment of the disclosure.

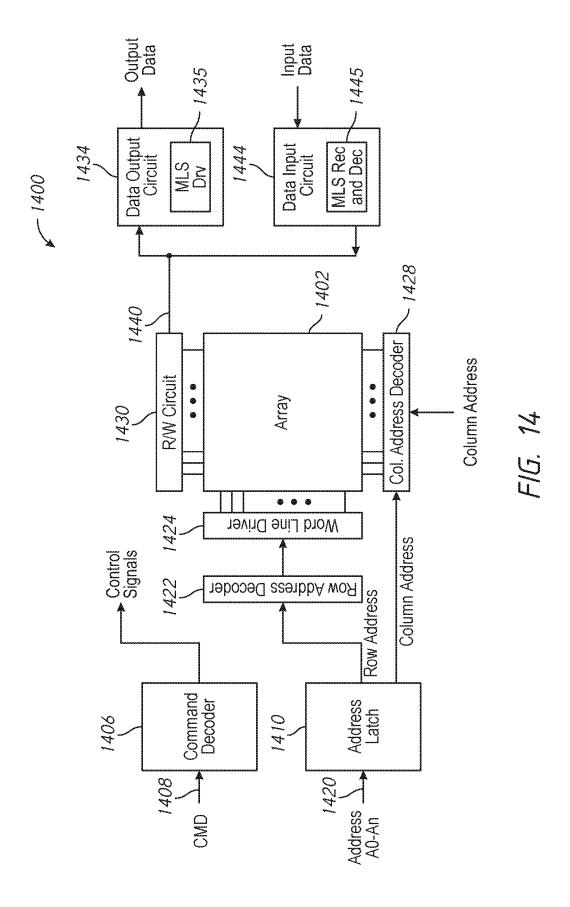

Figure 14 illustrates a portion of a memory according to an embodiment of the disclosure.

#### **DETAILED DESCRIPTION**

[0008] Certain details are set forth below to provide a sufficient understanding of examples of the disclosure. However, it will be clear to one having skill in the art that examples of the disclosure may be practiced without these particular details. Moreover, the particular examples of the present disclosure described herein should not be construed to limit the scope of the disclosure to these particular examples. In other instances, wellknown circuits, control signals, timing protocols, and software operations have not been shown in detail in order to avoid unnecessarily obscuring the disclosure. Additionally, terms such as "couples" and "coupled" mean that two components may be directly or indirectly electrically coupled. Indirectly coupled may imply that two components are coupled through one or more intermediate components.

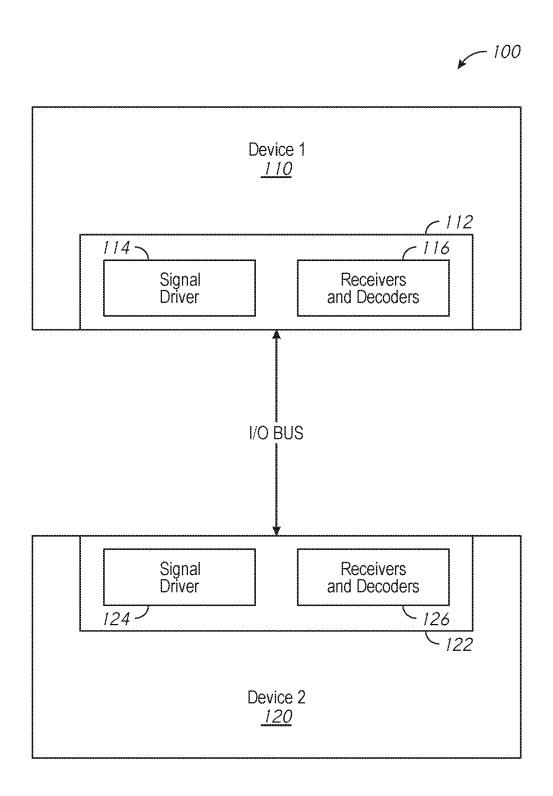

[0009] Figure 1 is a block diagram of an apparatus 100 according to an embodiment of the present disclosure. The apparatus 100 may include a first device 110 that communicates with a second device 120 over an input/output (I/O) bus. The first device 110 may include an I/O interface circuit 112 that includes signal driver 114 and receiver and decoder circuit 116 for communication over the I/O bus. The second device 120 may include an I/O interface circuit 122 that includes signal driver 124 and receiver and decoder circuit 126 for communication over the I/O bus. The I/O bus may support a multilevel communication architecture that includes a plurality of channels. In some embodiments, each channel may be single-ended and may include a single signal line. In other embodiments, each channel may include more than one signal line. In one embodiment, the first device 110, the second device 120, and the I/O bus may support a channel that includes conversion of M bitstreams to N

multilevel signals, where M is greater than N.

[0010] A bitstream includes a plurality of bits provided serially, wherein each bit of the bitstream is provided over a period of time, that may be referred to as a data period. For example, a first bit is provided for a first period, and a second bit is provided for a second period following the first period, and a third bit is provided for a third period following the second period, and so on. The successive bits provided in this serial manner represent a stream of bits. The corresponding bits of each bitstream for a data period represents data M bits wide. The N multilevel signals may be transmitted over the I/O bus. Each multilevel signal is provided over a data period having a voltage corresponding to one of multiple voltage levels (e.g., 2 different voltage levels, 4 different voltage levels, 8 different voltage levels, etc.), where each of the multiple voltage levels represents different data. In one example, 3 bit streams may be converted to 2 tri-level signals. In another example, pulse-amplitude modulation (PAM) may be used to convert 2, 3, or 4 bitstreams into a single multilevel signal having 4, 8, 16, etc., levels.

[0011] In some examples, the first device 110 may include a memory controller or processing system and/or the second device 120 may include a memory, including volatile memory and/or non-volatile memory. In some examples, the second device 120 may include a dynamic random access memory (DRAM), such as a double-datarate (DDR) DRAM or a low power DDR DRAM. It should be noted, however, that a memory is not a necessary component of the disclosure. Rather, the disclosure may be applied to any two or more devices, on or off-chip, that communicate with one another using multilevel signaling. **[0012]** The signal driver 114 may include circuitry that applies a bitstream conversion to a set of M bitstreams to generate N multilevel signals and drives the N multilevel signals as channels on the I/O bus. Similarly, the signal driver 124 may include circuitry that applies a bitstream conversion to a set of M bitstreams to generate N multilevel signals and drives the N multilevel signals as channels on the I/O bus. In some examples, the signal driver 114 may include modifications to existing DDR drivers to drive the multilevel signals onto the channels of the I/O bus.

[0013] For each channel, the receiver and decoder circuit 116 may include decoders configured to recover the set of M bitstreams by decoding the N multilevel signals received via the channels of the I/O bus as provided by the signal driver 124. Further, the receiver and decoder circuit 126 may include decoders configured to recover the set of M bitstreams by decoding the N multilevel signals received via the channels of the I/O bus as provided by the signal driver 114. In some embodiments, the receiver and decoder circuit 116 and the receiver and decoder circuit 126 may include comparators and decoding logic to recover the set of M bitstreams.

[0014] In operation, the first device 110 and the second device 120 may communicate over the I/O bus to transfer information, such as data, addresses, commands, etc.

55

While the I/O bus is shown to be bidirectional, the I/O bus may also be a unidirectional bus. The I/O interface circuit 112 and I/O interface circuit 122 may implement a multilevel communication architecture. In a multilevel communication architecture, data is sent over a channel during a data period. Data may include a single value on a signal line of a channel, or may be a combination of values provided on a plurality of signal lines of a channel. The data may represent a channel state. A receiver may determine an output signal value based on the value transmitted on the signal line(s) of a channel. In a single-ended architecture, the signal line value may be compared against one or more reference values to determine the output signal value. A receiver has a time period to determine and latch the output signal value from the time the output signal transitions to the current value to the time the output signal transitions to the next value. The transition time may be determined based on a clock signal, as well as a setup and hold time based on a transition from one value to another. In a multilevel communication architecture with a fixed slew rate or fixed rise/fall times, inherent jitter may occur due to differing magnitude shifts (e.g., from VH to VL vs. from VMID to VH or VL. The amount of jitter may be based on the slew rate, the rise/fall times, the multilevel magnitudes values, or combinations thereof. In some examples, the transition times may also be affected by process, voltage, and temperature variations.

[0015] In an example, the signal driver 114 may generate data for a channel by converting a bit from each of the M bitstreams during a data period into N multilevel signals. The data may be transmitted to the receiver and decoder circuit 126 via N signal lines of the I/O bus. The receiver and decoder circuit 126 may detect levels on the N signal lines and decode the levels to retrieve the bit from each of the M streams. By using multilevel signal lines, more data can be transmitted during a data period as compared with using binary signal line levels. In an example, M is 3 and N is 2, and the signal lines of the I/O bus are capable of being driven to three independent voltage levels. In another example. M is 2 and N is 1, and the signal lines of the I/O bus are capable of being driven to four independent voltage levels (e.g., in a PAM implementation). Communication protocol between the signal driver 124 and the receiver and decoder circuit 116 may be similar to the communication protocol between the encoder and signal driver 114 and the receiver and decoder circuit 126. The signal driver 114 may include a DRAM driver that has been segmented to drive multiple (e.g., more than 2) voltage levels on a signal line.

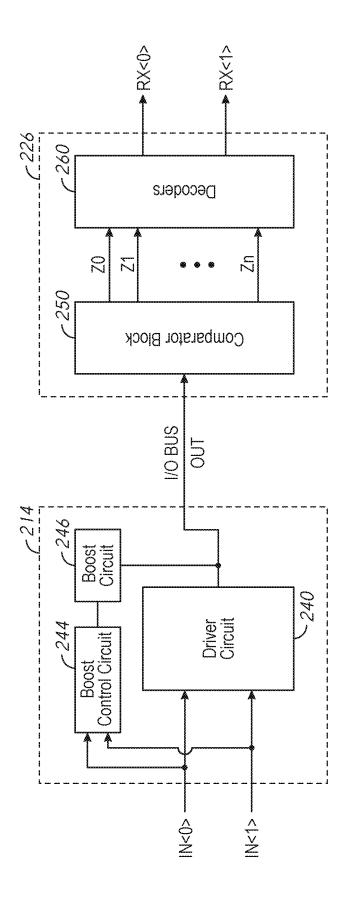

**[0016]** Figure 2A is a block diagram of an apparatus for a multilevel communication architecture according to an embodiment of the disclosure. The apparatus may include a signal driver 214 coupled to a receiver 226 via an I/O bus. The signal driver 214 may be implemented in the signal driver 114 and/or the signal driver 124 of Figure 1 and the receiver 226 may be implemented in the receiver and decoder circuit 116 and/or the receiver and decoder

circuit 126 of Figure 1.

[0017] The signal driver 214 may include a driver circuit 240. The driver circuit 240 may receive bitstreams IN<1> and IN<0> and drive an output signal OUT in response. The IN<1> and IN<0> bitstreams may represent a stream of two-bit data. The output signal OUT driven by the driver circuit 240 is based on the IN<1> and IN<0> bitstreams. For example, the signal may be a multilevel signal representing data of the IN<0> and IN<1> bitstreams. In some embodiments of the disclosure, the driver circuit 240 may include one or more signal line drivers having a pull-up (e.g., p-type) transistor coupled in series with a pull-down (e.g., n-type) transistor. A source of the pull-up transistor is coupled to a high supply voltage and the source of the pull-down transistor is coupled to a low supply voltage. In some embodiments, the high supply voltage is 1.2 V and the low supply voltage is ground. The output signal OUT is provided at a common node to which the pull-up and pull-down transistors are coupled. Gates of the pull-up and pull-down transistors of the driver circuit 240 are provided with the IN<1> and IN<0> bitstreams. In other embodiments of the disclosure, the driver circuit 240 may be implemented using other configurations.

[0018] The signal driver 214 further includes a boost control circuit 244 and a boost circuit 246. The boost control circuit 244 provides control signals to control the boost circuit 246 according to the IN<0> and IN<1> bitstreams. The boost circuit 244 may be controlled to provide increased pull-down capability and/or increased pull-down capability for the driver circuit 240 based on current data of the IN<0> and IN<1> bitstreams.

[0019] The receiver 226 may include comparator block 250 coupled to a decoder 260. The comparator 250 may be configured to receive the signal from the I/O bus and provide Z0-Zn signals (n is a whole number) to the decoder 260. The comparator block 250 may include circuits (not shown in Figure 2A) configured to compare the signal from the I/O bus against reference signals to provide the Z0-Zn signals. For example, the comparator block 250 may include comparators that compare the OUT signal from the I/O bus against various reference signals to provide the Z0-Zn signals. The decoder 260 may include logic to generate the bitstreams RX<0> and RX<1> based on the Z0-Zn signals from the comparator block 250. The RX<0> and RX<1> bitstreams may be logical equivalents of data transmitted by the IN<0> and IN<1> bitstreams. The RX<0> and RX<1> bitstreams may represent a stream of two-bit received data.

[0020] In operation, the IN<0> and IN<1> may be bit-streams to be transmitted over the I/O bus. Rather than send each bitstream on a separate signal line, the signal driver 214 may provide a signal based on the IN<0> and IN<1> bitstreams to be transmitted over a signal line using a multilevel signal. For example, the signal driver 214 may receive the IN<0> and IN<1> bitstreams, and during each data period, the driver circuit 240 may drive the signal line of the I/O bus with a voltage that will be used by the receiver 226 to provide the RX<0> and

45

50

20

RX<1> bitstreams. The multilevel signal may be used to represent data of the IN<0> and IN<1> bitstreams using fewer signal lines than one signal line per bitstream. For example, as in the embodiment of Figure 2A, data of the IN<0> and TN<1> bitstreams are provided to the receiver 226 on fewer than two signal lines (e.g., one signal on the I/O bus rather than one signal line for the IN<0> bitstream and another signal line for the IN<1> bitstream). Although Figure 2A illustrates operation with bitstreams IN<0> and IN<1> for providing bitstreams RX<0> and RX<1>, the number of bitstreams may be different in other embodiments of the disclosure. For example, in some embodiments of the disclosure, a third bitstream IN<2> may also be provided to the signal driver 214 in addition to the IN<0> and IN<1> bitstreams and a multilevel signal may be provided over the I/O bus representing the data from the IN<0>, IN<1>, and IN<2> bitstreams. Such embodiments are within the scope of the present disclosure.

**[0021]** Figure 3 is a schematic drawing of a signal driver 300 according to an embodiment of the disclosure. The signal driver 300 may be used for a multilevel signal architecture implementing pulse-amplitude modulation (PAM). The signal driver 300 may be used as the signal driver 214 in embodiments of the disclosure.

[0022] The signal driver 300 includes a driver circuit including six signal line drivers coupled to a common node that is an output. The output may represent an output terminal. Each of the signal line drivers are coupled to a high supply voltage (e.g., VDDQ) and to a low supply voltage (e.g., VSSQ). The driver circuit may be a driver in a DRAM, such as a double data rate (DDR) DRAM driver. In some embodiments of the disclosure, each of the signal line drivers has an impedance of 240 ohms. The driver circuit may include a first driver section 320 and a second driver section 330 configured to drive an output signal OUT to a common node to which the first and second driver sections 320 and 330 are coupled. A signal line may be coupled to the common node. The output signal OUT driven by the first and second driver sections 320 and 330 may be based on IN<1> and IN<0> bitstreams, which may be provided to the signal line drivers of the driver circuit. The output signal OUT may be a multilevel signal representing data of the IN<1> and IN<0> bitstreams that drives the I/O bus. In some embodiments of the disclosure, "1" data is represented by the IN<1> signal or IN<0> signal having a voltage of 1.2 V, and "0" data is represented by the IN<1> signal or IN<0> signal having a voltage of 0 V. However, other voltage levels may be used to represent the "1" and "0" data in other embodiments of the disclosure.

[0023] The first driver section 320 may include four signal line drivers coupled to the common node, each controlled responsive to the IN<1> bitstream. Each signal line driver may include a pull-up (e.g., p-type) transistor and a pull-down (e.g., n-type) transistor. The complement of the IN<1> bitstream is provided to the gates of the pull-up and pull-down transistors by an inverter circuit that receives the IN<1> bitstream. The second driver section

330 may include two signal line drivers coupled to the common node, each controlled responsive to the IN<0> bitstream, and each signal line driver may include a pullup (e.g., p-type) transistor and a pull-down (e.g., n-type) transistor. The complement of the IN<0> bitstream is provided to the gates of the pull-up and pull-down transistors by an inverter circuit that receives the IN<0> bitstream. In an embodiment of the disclosure where each signal line driver has an impedance of 240 ohms, the first driver section 320 has an effective impedance of 60 ohms, the second driver section 330 has an effective impedance of 120 ohms. With each of the signal line drivers having the same impedance, the signal line drivers have the same drive strength.

[0024] The signal driver 300 further includes a boost circuit 346 that receives control signals BoostHi and BoostLo from boost control circuit 344. The boost control circuit 344 includes logic circuits and provides control signals BoostHi and BoostLo to the boost circuit 346 based on the IN<0> and IN<1> bitstreams. In some embodiments of the disclosure, a BoostHi signal or BoostLo signal having the high logic level is represented by a signal of 1.2 V. and a BoostHi signal or BoostLo signal having the low logic level is represented by a signal of 0 V. However, other voltage levels may be used to represent the "1" and "0" data in other embodiments of the disclosure.

[0025] The boost circuit 346 is coupled to the common node and includes a pull-up (e.g., p-type) transistor and a pull-down (e.g., n-type) transistor, which are controlled by the BoostHi and BoostLo signals, respectively. The boost circuit 346 may also be referred to as another driver section of the driver circuit. The complement of the BoostHi signal is provided to the gate of the pull-up transistor by an inverter circuit that receives the BoostHi signal. In the embodiment of Figure 3, the BoostHi signal provided by the boost control circuit 344 is active when at a high logic level to activate the pull-up transistor and the BoostLo signal is active when at a high logic level to activate the pull-down transistor. When activated by an active BoostHi signal from the boost control circuit 344, the pull-up transistor provides additional drive to pull up the level of the signal line. Similarly, when activated by an active BoostLo signal from the boost control circuit 344, the pull-down transistor provides additional drive to pull down the level of the signal line. As previously discussed, in an embodiment of the disclosure where each signal line driver has an impedance of 240 ohms, the first driver section 320 has an effective impedance of 60 ohms, the second driver section 330 has an effective impedance of 120 ohms. The boost circuit 346 would have an impedance of 240 ohms. As a result, the first driver section 320, second driver section 330, and boost circuit (e.g., third driver section) have different drive strengths from one another.

**[0026]** As will be described in more detail below, the pull-up transistor of the boost circuit 346 may be activated when the IN<1> and IN<0> bitstreams represent data

45

corresponding to a voltage level of a high supply voltage (e.g., representing data "11"), and the pull-down transistor may be activated when the IN<1> and IN<0> bit-streams represent data corresponding to a voltage level of a low supply voltage (e.g., representing data "00"). While Figure 3 shows the boost circuit 346 as including one pull-up transistor and one pull-down transistor, in other embodiments of the disclosure, the boost circuit 346 may include a greater number of pull-up and/or pull-down transistors. Thus, the embodiment of Figure 3 is not intended to limit boost circuits, or more generally, driver circuits, to embodiments having the specific configuration shown in Figure 3.

[0027] In operation, the signal driver 300 may drive the OUT signal responsive to the IN<1> and IN<0> bitstreams. The IN<1> and IN<0> bitstreams are provided to the signal line drivers of the driver sections 320 and 330 to provide an output signal OUT having an appropriate voltage for the multilevel signal, for example, using PAM to convert a plurality of bitstreams into a multilevel signal. [0028] In some embodiments of the disclosure, PAM4 is used to convert two bitstreams (e.g., the IN<1> and IN<0> bitstreams) into an OUT signal having one of four different voltage levels. The IN<1> bitstream may be provided to the signal line drivers of the first driver section 320 and the IN<0> bitstream may be provided to the signal line drivers of the second driver section 330. The resulting output signal will have one of four different voltages corresponding to the data of the IN<1> and IN<0> bitstreams. For example, where a current data of the IN<1> and IN<0> bitstreams is a "00", the pull-down transistors of both the driver sections 320 and 330 are activated to drive (e.g., pull down) the common node to the low supply voltage to provide an output signal OUT having the voltage of the low supply voltage. Additionally, as previously described, a current data of "00" also causes the pull-down transistor of the boost circuit 346 to provide additional drive to pull down the common node to the low supply voltage. Where a current data of the IN<1> and IN<0> bitstream is a "11", the pull-up transistors of both the driver sections 320 and 330 are activated to drive (e.g., pull up) the common node to the high supply voltage to provide an output signal OUT having the voltage of the high supply voltage. Additionally, as previously described, a current data of "11" also causes the pull-up transistor of the boost circuit 346 to provide additional drive to pull up the common node to the high supply voltage. As illustrated by the example, the pull-up transistor of the boost circuit 346 is activated to drive the common node to the high supply voltage when the first and second driver sections 320 and 330 drive the common node to the high supply voltage. Similarly, the pulldown transistor of the boost circuit 346 is activated to drive the common node to the low supply voltage when the first and second driver sections 320 and 330 drive the common node to the low supply voltage.

[0029] For current data of the IN<1> and IN<0> bitstream is a "01", the pull-down transistors of the driver

section 320 are activated and the pull-down transistors of the driver section 330 are activated to provide a voltage to the common node that results in an output signal OUT having an intermediate-low voltage. Lastly, for current data of the IN<1> and IN<0> bitstream is a "10", the pullup transistors of the driver section 320 are activated and the pull-down transistors of the driver section 330 are activated to provide a voltage to the common node that results in an output signal OUT having an intermediatehigh voltage. For a current data of "01" or "10", that is, where the first and second driver sections 320 and 330 are driving the common node to different supply voltages, neither the pull-up nor pull-down transistors of the boost circuit 346 are activated to provide any additional drive to change the voltage of the common node. With both the pull-up and pull-down transistors of the boost circuit 346 deactivated, the boost circuit 346 is in a high-impedance state.

[0030] While the first driver section 320, the second driver section 330, and the boost circuit 346 are shown in Figure 3 as including p-type pull-up transistors and n-type pull-down transistors. That is, the pull-up and pull-down transistors have different conductivity types. In other embodiments of the disclosure, the first driver section 320, the second driver section 330, and the boost circuit 346 may include n-type pull-up transistors, or a combination of p-type and n-type pull-up transistors. In embodiments of the disclosure using n-type pull-up transistors, which are activated by a high logic level signal (e.g., having the high supply voltage), the logic level of the signals provided to gates of the n-type pull-up transistors will have a complementary logic level to signals provided to the gates of p-type pull-up transistors. A signal having a complementary logic level may be provided by using an inverter circuit.

[0031] Figure 4A is a schematic diagram of a boost control circuit 410 according to an embodiment of the disclosure. The boost control circuit 410 may be included in the boost control circuit 344 of the signal driver 300 of Figure 3 in some embodiments of the disclosure. The boost control circuit 410 may control the boost circuit 346 to provide additional drive capability to the driver sections 320 and 330 drive the common node to provide a voltage level of the high supply voltage (e.g., when the IN<1> and IN<0> bitstreams represent "11" data). The boost control circuit 410 includes an AND logic circuit that receives the IN<1> and IN<0> bitstreams and provides the BoostHi signal resulting from a logic AND operation of the IN<1> and IN<0> bitstreams.

[0032] In operation, the boost control circuit 410 provides an active BoostHi signal (e.g., active when a high logic level) when the current data represented by the IN<1> and IN<0> bitstreams is "11", which causes the signal driver 300 to provide the output signal OUT having the voltage of the high supply voltage (e.g., current data of the IN<1> and IN<0> bitstreams is "11"). That is, with the IN<1> a "1" and the IN<0> a "1", the high logic level of the IN<1> bitstream is provided to the line drivers of the

20

first driver section 320 to cause the pull-up transistors to be activated and the high logic level of the IN<0> bitstream is provided to the line drivers of the second driver section 330 to cause the pull-up transistors to be activated. As a result, the common node to which the first and second driver sections 320 and 330 are coupled is pulled up to the voltage of the high supply voltage. Additionally, the high logic levels of the IN<1> and IN<0> bitstreams are provided to the AND logic circuit of the boost control circuit 410 and a logical AND operation is performed to provide an active (e.g.. a high logic level) BoostHi signal. The pull-up transistor of the boost circuit 346 is activated by the active BoostHi signal to provide additional drive to further pull up the common node to the voltage of the high supply voltage. Thus, as illustrated by the example operation, the pull-up transistor of the boost circuit 346 is activated to assist in pulling up the common node when the output signal OUT is to be provided having the voltage of the high supply voltage.

[0033] Figure 4B is a schematic diagram of a boost control circuit 420 according to an embodiment of the disclosure. The boost control circuit 420 may be included in the boost control circuit 344 of the signal driver 300 of Figure 3 in some embodiments of the disclosure. The boost control circuit 420 may control the boost circuit 346 to provide additional drive capability to the driver sections 320 and 330 drive the common node to provide a voltage level of the low supply voltage (e.g., when the IN<1> and IN<0> bitstreams represent "00" data). The boost control circuit 420 includes an exclusive OR (XOR) logic circuit 430 that receives the IN<1> and IN<0> bitstreams and an inverter circuit 440 that receives the IN<0> bitstream. The signals provided by the XOR logic circuit 430 and the inverter circuit 440 are provided to an AND logic circuit 450 which provides the BoostLo signal resulting from a logic AND operation of the signals provided by the XOR logic circuit 430 and the inverter circuit 440.

[0034] In operation, the boost control circuit 420 provides an active BoostLo signal (e.g., active when a high logic level) when the current data represented by the IN<1> and IN<0> bitstreams is a "00", which causes the signal driver 300 to provide the output signal OUT having the voltage of the low supply voltage (e.g., current data of the IN<1> and IN<0> bitstreams is "00"). That is, with the IN<1> a "0" and the IN<0> a "0", the low logic level of the IN<1> bitstream is provided to the line drivers of the first driver section 320 to cause the pull-down transistors to be activated and the low logic level of the IN<0> bitstream is provided to the line drivers of the second driver section 330 to cause the pull-down transistors to be activated. As a result, the common node to which the first and second driver sections 320 and 330 are coupled is pulled up to the voltage of the low supply voltage. Additionally, the low logic levels of the IN<1> and IN<0> bitstreams are provided to the XOR logic circuit 430 of the boost control circuit 420 and the IN<0> bitstream is provided to the inverter circuit 440. The outputs of the XOR logic circuit 430 and the inverter circuit 440 are provided to the AND

logic circuit 450, and a logical NAND operation is performed to provide an active (e.g., a high logic level) BoostLo signal. The pull-down transistor of the boost circuit 346 is activated by the active BoostLo signal to provide additional drive to further pull down the common node to the voltage of the low supply voltage. Thus, as illustrated by the example operation, the pull-down transistor of the boost circuit 346 is activated to assist in pulling down the common node when the output signal OUT is to be provided having the voltage of the low supply voltage.

[0035] Figure 5A is a diagram showing operation of the first and second driver sections 320 and 330, and the boost circuit 346, of the signal driver 300 for driving a load that is terminated to a high supply voltage (e.g., VDDQ) according to an embodiment of the disclosure. In such a situation, a typical signal driver may not fully drive an output signal OUT to a low supply voltage (e.g., VSSQ, as shown as "w/o Boost"). The high supply voltage may represent a high logic level (e.g., "11") output signal OUT and the low supply voltage may represent a low logic level (e.g., "00") output signal OUT in some embodiments of the disclosure. The inability for the signal driver to fully drive the output signal OUT to the high supply voltage may be due to, for example, variations in circuit performance. The variation in circuit performance may be due to variations in the process when fabricating the circuits, variations in the supply voltages powering the circuits, and/or operating temperature of the circuits. As a result, actual circuit performance may deviate from ideal circuit performance. By not fully driving the output signal OUT to the low supply voltage, the voltage margin between the different voltage levels representing the different data is reduced, which may be more susceptible to data errors.

[0036] As shown in Figure 5A (as shown as "w/Boost"), the boost circuit 346 may be used to assist driving the output signal OUT. In particular, the pull-down transistor of the boost circuit 346 may be used to provide additional drive to fully drive the output signal OUT to the low supply voltage when the signal driver 300 provides an output signal OUT having a low logic level. As previously described, the pull-down transistor of the boost circuit 346 may be activated by an active BoostLo signal, which may be provided by boost control circuit (e.g., boost control circuit 344). The BoostLo signal may be active when the signal driver 300 is driving a low logic level output signal OUT.

[0037] Figure 5B is a diagram showing operation of the first and second driver sections 320 and 330, and the boost circuit 346, of the signal driver 300 for driving a line terminated load according to an embodiment of the disclosure. In such a situation, a typical signal driver may not fully drive an output signal OUT to either a high or low supply voltage (e.g., VDDQ or VSSQ, as shown as "w/o Boost"). The high supply voltage may represent a high logic level (e.g., "11") output signal OUT and the low supply voltage may represent a low logic level (e.g.,

55

15

20

"00") output signal OUT in some embodiments of the disclosure. As previously described, the inability for the signal driver to fully drive the output signal OUT to the high supply voltage may be due to, for example, variations in circuit performance. The variation in circuit performance may be due to variations in the process when fabricating the circuits, variations in the supply voltages powering the circuits, and/or operating temperature of the circuits. As a result, actual circuit performance may deviate from ideal circuit performance. As further described, by not fully driving the output signal OUT to either of the high or low supply voltages, the voltage margin between the different voltage levels representing the different data is reduced, which may be more susceptible to data errors.

[0038] As shown in Figure 5B (as shown as "w/Boost"), the boost circuit 346 may be used to assist driving the output signal OUT. In particular, the pull-down transistor of the boost circuit 346 may be used to provide additional drive to fully drive the output signal OUT to the low supply voltage when the signal driver 300 provides an output signal OUT having a low logic level. Additionally, the pullup transistor of the boost circuit 346 may be used to provide additional drive to fully drive the output signal OUT to the high supply voltage when the signal driver 300 provides an output signal OUT having a high logic level. As previously described, the pull-down transistor of the boost circuit 346 may be activated by an active BoostLo signal and the pull-up transistor of the boost circuit 346 may be activated by an active BoostHi signal. The BoostLo and BoostHi signals may be provided by a boost control circuit (e.g., boost control circuit 344). The BoostLo signal may be active when the signal driver 300 is driving a low logic level output signal OUT and the BoostHi signal may be active when the signal driver 300 is driving a high logic level output signal OUT.

**[0039]** Figure 5C is a diagram showing operation of the first and second driver sections 320 and 330, and the boost circuit 346. of the signal driver 300 for driving a load that is terminated to a low supply voltage (e.g., VSSQ) according to an embodiment of the disclosure. In such a situation, a typical signal driver may not fully drive an output signal OUT to a high supply voltage (e.g., VDDQ. as shown as "w/o Boost"). The high supply voltage may represent a high logic level (e.g., "11") output signal OUT and the low supply voltage may represent a low logic level (e.g., "00") output signal OUT in some embodiments of the disclosure.

**[0040]** As shown in Figure 5C (as shown as "w/Boost"), the boost circuit 346 may be used to assist driving the output signal OUT. In particular, the pull-up transistor of the boost circuit 346 may be used to provide additional drive to fully drive the output signal OUT to the high supply voltage when the signal driver 300 provides an output signal OUT having a high logic level. As previously described, the pull-up transistor of the boost circuit 346 may be activated by an active BoostHi signal, which may be provided by boost control circuit (e.g., boost control circuit

344). The BoostHi signal may be active when the signal driver 300 is driving a high logic level output signal OUT. [0041] In some embodiments of the disclosure, the boost circuit 346 may provide additional drive for data corresponding to just one of the supply voltages. For example, in some embodiments of the disclosure, data corresponding to the low supply voltage is boosted, but data corresponding to the high supply voltage is not. The pull-up transistor of the boost circuit 346 may be disabled, circuits for providing signals to activate a pull-up transistor of the boost circuit 346 may not be included in the boost control circuit, circuits for providing signals to activate a pull-up transistor of the boost circuit 346 may not be enabled, or other approaches may be used to not provide boost for data corresponding to the high supply voltage. In other embodiments of the disclosure, the pulldown transistor of the boost circuit 346 may be disabled, so that data corresponding to the high supply voltage is boosted, but data corresponding to the low supply voltage is not. The pull-down transistor of the boost circuit 346 may be disabled, circuits for providing signals to activate a pull-down transistor of the boost circuit 346 may not be included in the boost control circuit, circuits for providing signals to activate a pull-down transistor of the boost circuit 346 may not be enabled, or other approaches may be used to not provide boost for data corresponding to the low supply voltage. In some embodiments of the disclosure, the boost circuit 346 is activated to provide additional drive for data corresponding to both the high supply voltage and the low supply voltage. In such embodiments, the boost control circuit 410 and the boost control circuit 420 may be included together.

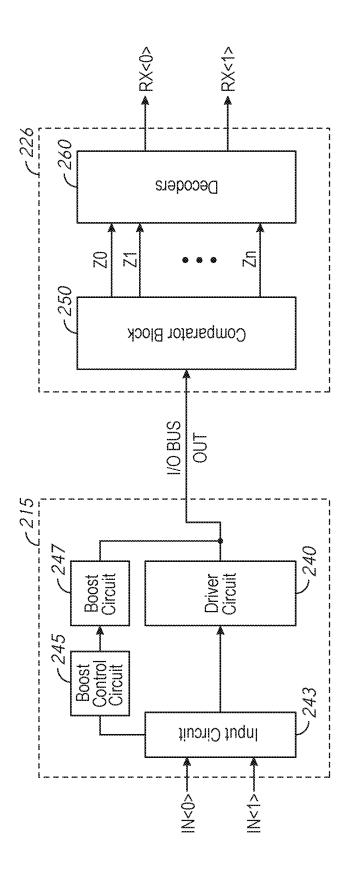

**[0042]** Figure 2B is a block diagram of an apparatus for a multilevel communication architecture according to an embodiment of the disclosure. The apparatus of Figure 2B is similar to the apparatus of Figure 2A, and consequently, the same reference numbers are used in Figure 2B as in Figure 2A to identify the same components as previously described. In contrast to the apparatus of Figure 2A, the apparatus of Figure 2B includes a signal driver 215 coupled to the receiver 226 via an I/O bus. The receiver 226 may be as previously described with reference to the apparatus of Figure 2A.

[0043] The signal driver 215 may be implemented in the signal driver 114 and/or the signal driver 124 of Figure 1 and the receiver 226 may be implemented in the receiver and decoder circuit 116 and/or the receiver and decoder circuit 126 of Figure 1. The signal driver 215 may include an input circuit 243 that receives bit-streams IN<1> and IN<0> and provides output signals to a boost control circuit 245 and a driver circuit 240. The driver circuit 240 may be as previously described with reference to the apparatus of Figure 2A. The boost control circuit 245 provides control signals to control the boost circuit 247 according to the output signals from the input circuit 243. The boost circuit 247 may be controlled to provide increased pull-down capability and/or

45

50

increased pull-down capability for the driver circuit 240 based on current data of the IN<0> and IN<1> bitstreams. **[0044]** In operation, the signal driver 215 may receive the IN<0> and IN<1> bitstreams, and during each data period, the driver circuit 240 may drive the signal line of the I/O bus with a voltage that will be used by the receiver 226 to provide the RX<0> and RX<1> bitstreams. The multilevel signal may be used to represent data of the IN<0> and IN<1> bitstreams using fewer signal lines than one signal line per bitstream. Although Figure 2B illustrates operation with bitstreams IN<0> and IN<1> for providing bitstreams RX<0> and RX<1>, the number of bitstreams may be different in other embodiments of the disclosure. For example, in some embodiments of the disclosure, a third bitstream IN<2> may also be provided to the signal driver 215 in addition to the IN<0> and IN<1> bitstreams and a multilevel signal may be provided over the I/O bus representing the data from the IN<0>, IN<1>, and IN<2> bitstreams. Such embodiments are within the scope of the present disclosure.

[0045] Figure 6 is a schematic diagram of an input circuit 600 according to an embodiment of the disclosure. The input circuit 600 may be included in the input circuit 243 of Figure 2B in some embodiments of the disclosure. The input circuit 600 includes D flip-flop circuits 610 and 620, and D flip-flop circuits 640 and 660. The D flip-flop circuit 610 receives the IN<1> bitstream and the D flipflop circuit 640 receives the IN<0> bitstream. The D flipflop circuit 610 and the D flip-flop circuit 640 are clocked by a clock signal CLK, and the D flip-flop circuit 620 and the D flip-flop circuit 660 are clocked by a clock signal CLKF, which is the complement to the CLK signal. That is, a rising edge of the CLK signal corresponds to a falling edge of the CLKF signal, and a falling edge of the CLK signal corresponds to a rising edge of the CLKF signal. In some embodiments of the disclosure, the CLK signal may be a system clock signal or a clock signal derived from the system clock signal. The system clock signal may be a clock signal provided to different circuits of a larger system in order to synchronize operations, for example, for providing data between the different circuits. The D flip-flop circuits 610, 620, 640, and 660 may be reset to provide an output having a known logic level when an active reset signal RST is provided to the D flipflop circuits. The D flip-flop circuits 610, 620, 640, and 660 may be reset, for example, upon reset of the semiconductor device, as part of a power up sequence, etc.

[0046] In operation, the D flip-flop circuit 610 latches a current logic level of the IN<1> bitstream responsive to a rising edge of the CLK signal and provides an output signal D<1> having the same logic level as the latched logic level. The D flip-flop circuit 620 latches the logic level of the D<1> signal responsive to a rising edge of the CLKF signal and provides an output signal IND<1> having the same logic level as the latched logic level. Likewise, the D flip-flop circuit 640 latches a current logic level of the IN<0> bitstream responsive to a rising edge of the CLK signal and provides an output signal D<0> having

the same logic level as the latched logic level. The D flip-flop circuit 660 latches the logic level of the D<0> signal responsive to a rising edge of the CLKF signal and provides an output signal IND<0> having the same logic level as the latched logic level. With reference to the CLK signal, the IN<1> and IN<0> bitstreams are latched and the D<1> and D<0> signals provided responsive to a rising edge of the CLK signal, and the D<1> and D<0> signals are latched and the IND<1> and IND<0> signals are provided responsive to a falling edge of the CLK signal (i.e., the rising edge of the CLKF signal). Thus, the IND<1> and IND<0> signals have the logic levels of the D<1> and D<0> signals delayed by one-half a clock period of the CLK signal.

[0047] Figure 7A is a schematic diagram of a pull-up logic circuit 700 according to an embodiment of the disclosure. The pull-up logic circuit 700 may be included in the boost control circuit 245 of Figure 2B in some embodiments of the disclosure. The pull-up logic circuit 700 includes a NAND logic circuit 710 that receives the D<1> and D<0> signals, for example, from the input circuit 600, and provides an output signal IN\_11F that results from a NAND logic operation of the D<1> and D<0> signals. The pull-up logic circuit 700 further includes a NAND logic circuit 720 that receives the IND<1> and IND<0> signals, for example from the input circuit 600. The NAND logic circuit 720 provides an output signal IND 11F resulting from a NAND logic operation on the IND<1> and IND<0> signals to an inverter circuit 730. The inverter circuit 730 provides an output signal IND 11 that is the complement of the IND\_11F signal. A NOR logic circuit receives the IN\_11F signal from the NAND logic circuit 710 and the IND\_11 signal from the inverter circuit 730 and provides an output signal PREPU that resulting from a NOR logic operation.

[0048] In operation, the logic circuit 700 provides an active PREPU signal (e.g., active high logic level) when the data of the IN<1> and IN<0> bitstreams changes from a previous value to a current data of "11". That is, where the previous data represented by the IN<1> and IN<0> bitstreams is "00", "01", or "10", and the data changes to a current data of "11", the logic circuit 700 provides an active PREPU signal. The logic circuit 700 provides and inactive PREPU signal for other changes from a previous data to a current data represented by the IN<1> and IN<0> bitstreams. That is, the logic circuit 700 provides an inactive PREPU signal for the IN<1> and IN<0> bitstreams changing from a previous data to current data of "00", "01", or "10". The active PREPU signal provided by the logic circuit 700 may be used to activate a boost circuit, for example, the boost circuit 346 of the signal driver 300, to provide additional drive to assist driving the common node to the high supply voltage to provide an OUT signal having a voltage of the high supply voltage. As will be described in more detail below, the PREPU signal is active for a portion of the data period of the OUT signal. For example, in some embodiments of the disclosure, the PREPU signal is limited to being active

55

to assist the driving of the common node to the high supply voltage.

[0049] The NAND logic circuit 710 provides a low logic level IN 11F signal when D<1> and D<0> are both a high logic level (i.e., resulting from the IN<1> and IN<0> bitstreams representing a current data of "11"). The inverter circuit 730 coupled to the NAND logic circuit 720 to receive the IND\_11F signal provides a low logic level IND 11 when IND<1> and IND<0> are both a high logic level (i.e., resulting from D<1> and D<0> both a high logic level). Recall that the IND<1> and IND<0> are delayed relative to D<1> and D<0>, for example, by one-half a clock period of the CLK signal. The NOR logic gate provides an active PREPU signal (e.g. active high logic level) when the IN 11F and IND 11 signals have low logic levels. As a result, the PREPU signal is active when D<1> and D<0> are both at a high logic level, and for onehalf a clock cycle of the CLK signal following a rising edge of the CLK signal. The PREPU signal is active for one-half a clock cycle of the CLK signal because the one-half clock cycle delay of the IND<1> and IND<0> relative to D<1> and D<0> will result in the IND\_11 signal being at a low logic level while the IN\_11F signal is at a low logic level (from D<1> and D<0> both being a high logic level), but for one-half a clock cycle of the CLK signal before both IND<1> and IND<0> also become a high logic level (resulting from the D<1> and D<0> both being at the high logic level). As a result, the PREPU signal is active for one-half a clock cycle of the CLK signal.

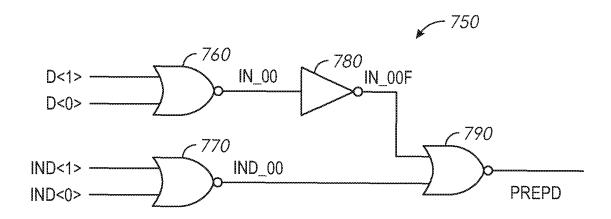

[0050] Figure 7B is a schematic diagram of a pull-down logic circuit 750 according to an embodiment of the disclosure. The pull-down logic circuit 750 may be included in the boost control circuit 245 of Figure 2B in some embodiments of the disclosure. The pull-down logic circuit 750 includes a NOR logic circuit 760 that receives the D<1> and D<0> signals, for example, from the input circuit 600, and provides an output signal IN 00 that results from a NOR logic operation of the D<1> and D<0> signals. The IN 00 signal is provided to an inverter circuit 780. The inverter circuit 780 provides an output signal IN\_00F that is the complement of the IN\_00 signal. The pull-down logic circuit 750 further includes a NOR logic circuit 770 that receives the IND<1> and IND<0> signals, for example from the input circuit 600, and provides an output signal IND\_00 resulting from a NOR logic operation on the IND<1> and IND<0> signals. A NOR logic circuit receives the IN\_00F signal from the inverter circuit 780 and the IND 00 signal from the NOR logic circuit 770 and provides an output signal PREPD that resulting from a NOR logic operation.

**[0051]** In operation, the logic circuit 750 provides an active PREPD signal (e.g., active high logic level) when the data of the IN<1> and IN<0> bitstreams changes from a previous value to a current data of "00". That is, where the previous data represented by the IN<1> and IN<0> bitstreams is "01", "10", or "11", and the data changes to a current data of "00", the logic circuit 750 provides an active PREPD signal. The logic circuit 750 provides

and inactive PREPD signal for other changes from a previous data to a current data represented by the IN<1> and IN<0> bitstreams. That is, the logic circuit 750 provides an inactive PREPD signal for the IN<1> and IN<0> bitstreams changing from a previous data to current data of "01", "10", or "11". The active PREPD signal provided by the logic circuit 750 may be used to activate a boost circuit, for example, the boost circuit 346 of the signal driver 300. to provide additional drive to assist driving the common node to the low supply voltage to provide an OUT signal having a voltage of the low supply voltage. As will be described in more detail below, the PREPD signal is active for a portion of the data period of the OUT signal. For example, in some embodiments of the disclosure, the PREPD signal is limited to being active to assist the driving of the common node to the low supply voltage.

[0052] The inverter circuit 780 coupled to the NOR logic circuit 760 provides a low logic level IN 00F signal when D<1> and D<0> are both a low logic level. (i.e., resulting from the IN<1> and IN<0> bitstreams representing a current data of "00"). The NOR logic circuit 770 provides a high logic level IND\_00 signal when IND<1> and IND<0> are both a low logic level (i.e., resulting from D<1> and D<0> both a low logic level). Recall that the IND<1> and IND<0> are delayed relative to D<1> and D<0>, for example, by one-half a clock period of the CLK signal. The NOR logic gate 790 provides an active PREPD signal (e.g. active high logic level) when the IN\_00F and IND\_00 signals have low logic levels. As a result, the PREPD signal is active when D<1> and D<0> are both at a low logic level, and for one-half a clock cycle of the CLK signal following a rising edge of the CLK signal. The PREPD signal is active for one-half a clock cycle of the CLK signal because the one-half clock cycle delay of the IND<1> and IND<0> relative to D<1> and D<0> will result in the IND 00 signal being at a low logic level while the IN 00F signal is at a low logic level (from D<1> and D<0> both being a low logic level), but for onehalf a clock cycle of the CLK signal before both IND<1> and IND<0> also become a low logic level (resulting from the D<1> and D<0> both being at the low logic level) and the NOR logic circuit 770 provides a high logic level IND 00. As a result, the PREPD signal is active for one-half a clock cycle of the CLK signal.

[0053] In some embodiments of the disclosure, the boost circuit 346 of the signal driver 300 is activated to provide additional drive for data corresponding to both the high supply voltage and the low supply voltage. In such embodiments, the boost control circuit 700 and 750 may be used together to control the boost circuit 346.

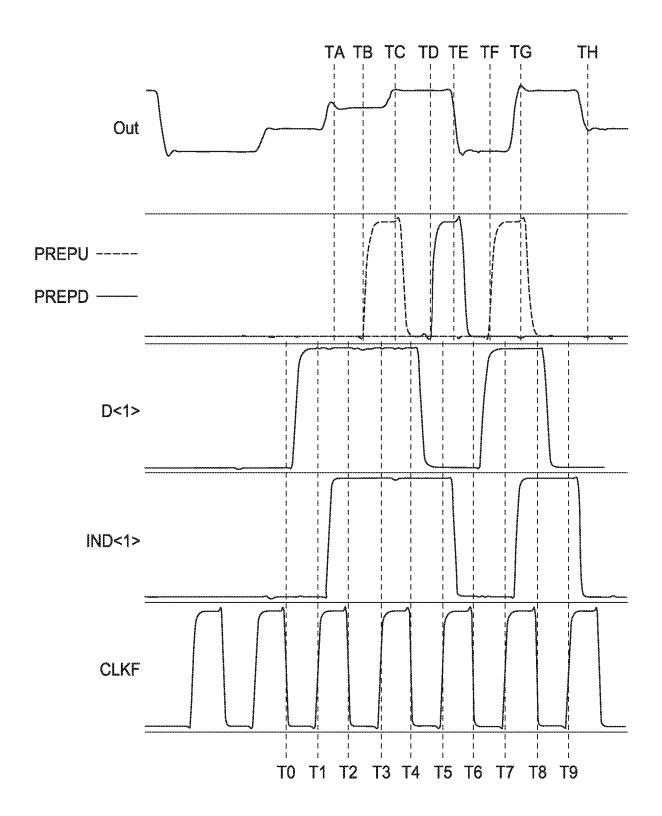

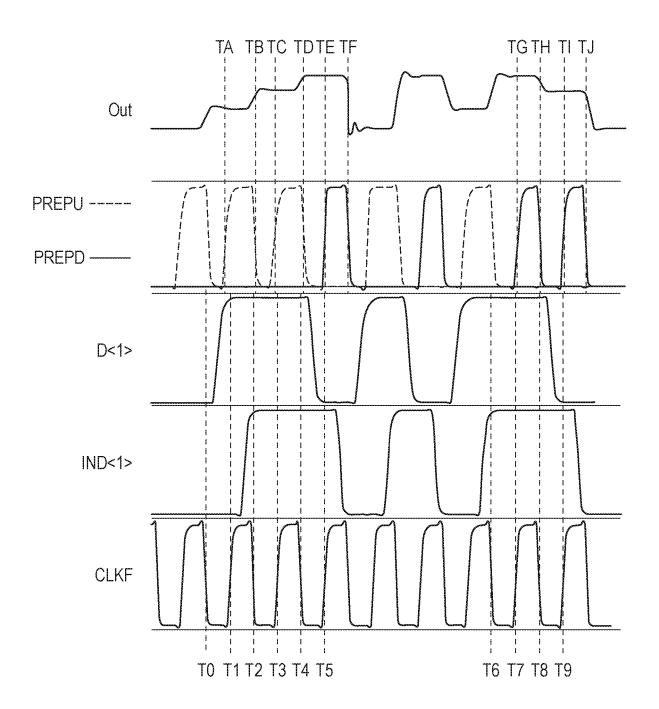

[0054] Figure 8 is a timing diagram showing various signals during operation of signal driver 300 with the input circuit 600 and pull-up and pull-down logic circuits 700 and 750 according to an embodiment of the disclosure. In the present example, the IND<1> signal is provided to the first driver section 320 instead of the IN<1> bitstream and the IND<0> signal is provided to the second driver section

45

50

330 instead of the IN<0> bitstream. The PREPU and PREPD signals are provided to the boost circuit 346 instead of the BoostHi and BoostLo signals. In the example of Figure 8, the output is terminated to a high supply voltage, resulting in "11" data represented by 1.2 V, "10" data represented by 1.0 V, "01" data represented by 0.8 V, and "00" data represented by 0.6 V. Other embodiments of the disclosure may use other voltage levels to represent the data values.

[0055] At time T0 the D flip-flops 610 and 640 of the input circuit 600 are clocked by a rising edge of the CLK signal (shown in Figure 8 as corresponding to a falling edge of the CLKF signal) and the data of the IN<1> and IN<0> bitstreams is latched to provide the D<1> and D<0> signals. In the present example, the data at time T0 is "10". The D flip-flop 610 provides a high logic level D<1> signal and the D flip-flop 640 provides a low logic level D<0> signal (not shown in Figure 8) shortly after time T0, At time T1, the D flip-flops 620 and 660 of the input circuit 600 are clocked by a rising edge of the CLKF signal (corresponding to a falling edge of the CLK signal). The high logic level of the D<1> signal is latched by the D flip-flop 620 to provide a high logic level IND<1> signal and the low logic level of the D<0> signal is latched by the D flip-flop 660 to provide a low logic level IND<0> signal (not shown in Figure 8) shortly after time T1. The IND<1> and IND<0> signals are provided to the driver circuit 300 to cause the pull-up transistors of the first driver section 320 to be activated and to cause the pull-down transistors of the second driver section 330 to be activated, resulting in providing an OUT signal having an intermediate-high voltage (corresponding to output data of "10") at time TA. Neither the pull-up nor pull-down transistors of the boost circuit 346 are activated by the current data of "10".

[0056] At time T2 the D flip-flops 610 and 640 of the input circuit 600 are clocked by a rising edge of the CLK signal and the data of the IN<1> and IN<0> bitstreams is latched to provide the D<1> and D<0> signals. The data at time T2 is "11". The D flip-flop 610 maintains a high logic level D<1> signal and the D flip-flop 640 provides a high logic level D<0> signal (not shown in Figure 8) shortly after time T2. The NAND logic circuit 710 of the pull-up logic circuit 700 provides a low logic level IN 11F signal due to the high logic levels of the D<1> and D<0> signals. With the IND\_11 signal provided by the inverter circuit 730 still at a low logic level from the previous data of "10", the XOR logic circuit 740 provides an active PREPU signal at time TB. The active PREPU signal activates the pull-up transistor of the boost circuit 346 to provide additional drive to pull up the common node in providing the OUT signal.

[0057] At time T3, the D flip-flops 620 and 660 of the input circuit 600 are clocked by a rising edge of the CLKF signal. The high logic level of the D<1> signal is latched by the D flip-flop 620 to maintain a high logic level IND<1> signal and the high logic level of the D<0> signal is latched by the D flip-flop 660 to provide a high logic level IND<0> signal (not shown in Figure 8) shortly after time

T3. The IND<1> and IND<0> signals are provided to the signal driver 300 to cause the pull-up transistors of the first driver section 320 to be activated and to cause the pull-up transistors of the second driver section 330 to be activated, along with the activated pull-up transistor of the boost circuit 346 that provides additional drive to the common node. As a result, an OUT signal is provided having a voltage of the high supply voltage (corresponding to output data of "11") at time TC.

[0058] After the IND<1> and IND<0> signals propagate through the NAND logic circuit 720 and the inverter circuit 730 of the pull-up logic circuit 700, the IND\_11 signal switches to a high logic level, which causes the XOR logic circuit 740 to provide an inactive PREPU signal. The change of the PREPU signal to inactive deactivates the pull-up transistor of the boost circuit 346. Thus, when the present data represented by the IN<1> and IN<0> bitstreams is "11", the boost circuit 346 provides additional drive to pull up the common node to the high supply voltage for a portion of the data period of the OUT signal, for example, during the transition of the OUT signal to the high supply voltage. The voltage of the OUT signal changes during the transition from one voltage level to another.

[0059] At time T4 the D flip-flops 610 and 640 of the input circuit 600 are clocked by a rising edge of the CLK signal and the data of the IN<1> and IN<0> bitstreams is latched to provide the D<1> and D<0> signals. The data at time T4 is "00". The D flip-flop 610 provides a low logic level D<1> signal and the D flip-flop 640 provides a low logic level D<0> signal (not shown in Figure 8) shortly after time T4. The inverter circuit 780 of the pull-down logic circuit 750 provides a low logic level IN\_00F signal when the NOR logic circuit 760 receives low logic level D<1> and D<0> signals. At this time, the IND 00 signal provided by the NAND logic circuit 770 is still at a low logic level from the previous data of "11", which results in the NOR logic circuit 790 providing an active PREPD signal at time TD. The active PREPD signal activates the pulldown transistor of the boost circuit 346 to provide additional drive to pull down the common node in providing the OUT signal.

[0060] At time T5, the D flip-flops 620 and 660 of the input circuit 600 are clocked by a rising edge of the CLKF signal. The low logic level of the D<1> signal is latched by the D flip-flop 620 to provide a low logic level IND<1> signal and the low logic level of the D<0> signal is latched by the D flip-flop 660 to provide a low logic level IND<0> signal (not shown in Figure 8) shortly after time T5. The IND<1> and IND<0> signals are provided to the signal driver 300 to cause the pull-down transistors of the first driver section 320 to be activated and to cause the pulldown transistors of the second driver section 330 to be activated, along with the activated pull-down transistor of the boost circuit 346 that provides additional drive to the common node. As a result, an OUT signal is provided having a voltage of the low supply voltage (corresponding to output data of "00") at time TE.

55

[0061] After the IND<1> and IND<0> signals propagate through the NOR logic circuit 770 of the pull-down logic circuit 750. the IND\_00 signal switches to a high logic level, which causes the XOR logic circuit 790 to provide an inactive PREPD signal. The change of the PREPD signal to inactive deactivates the pull-down transistor of the boost circuit 346. Thus, when the present data represented by the IN<1> and IN<0> bitstreams is "00", the boost circuit 346 provides additional drive to pull down the common node to the low supply voltage for a portion of the data period of the OUT signal, for example, during the transition of the OUT signal to the low supply voltage. As previously described, the voltage of the OUT signal changes during the transition from one voltage level to another.

**[0062]** At time T6 the D flip-flops 610 and 640 of the input circuit 600 are clocked by a rising edge of the CLK signal and the data of the IN<1> and IN<0> bitstreams is latched to provide the D<1> and D<0> signals. The data at time T6 is "11". The D flip-flop 610 provides a high logic level D<1> signal and the D flip-flop 640 provides a high logic level D<0> signal (not shown in Figure 8) shortly after time T6. The pull-up logic circuit 700 responds by providing an active PREPU signal at time TF to activate the pull-up transistor of the boost circuit 346 to provide additional drive to pull up the common node in providing the OUT signal.

[0063] At time T7, the D flip-flops 620 and 660 of the input circuit 600 are clocked by a rising edge of the CLKF signal. The high logic level of the D<1> signal is latched by the D flip-flop 620 to provide a high logic level IND<1> signal and the high logic level of the D<0> signal is latched by the D flip-flop 660 to provide a high logic level IND<0> signal (not shown in Figure 8) shortly after time T7. The pull-up transistors of the first and second driver sections 320 and 330 of the signal driver circuit 300 are activated, along with the activated pull-up transistor of the boost circuit 346 to drive the common node to the voltage of the high supply voltage and provide an OUT signal having a voltage of the high supply voltage (corresponding to output data of "11") at time TG. After the IND<1> and IND<0> signals propagate through the NAND logic circuit 720 and the inverter circuit 730 of the pull-up logic circuit 700, the IND 11 signal switches to a high logic level and the XOR logic circuit 740 provides an inactive PREPU signal. The inactive PREPU signal deactivates the pull-up transistor of the boost circuit 346.

**[0064]** At time T8 the D flip-flops 610 and 640 of the input circuit 600 are clocked by a rising edge of the CLK signal and the data of the IN<1> and IN<0> bitstreams is latched to provide the D<1> and D<0> signals. The data at time T0 is "01". The D flip-flop 610 provides a low logic level D<1> signal and the D flip-flop 640 provides a high logic level D<0> signal (not shown in Figure 8) shortly after time T8. At time T9, the D flip-flops 620 and 660 of the input circuit 600 are clocked by a rising edge of the CLKF signal. The low logic level of the D<1> signal is latched by the D flip-flop 620 to provide a low logic level

IND<1> signal and the high logic level of the D<0> signal is latched by the D flip-flop 660 to provide a high logic level IND<0> signal (not shown in Figure 8) shortly after time T9. The IND<1> and IND<0> signals are provided to the signal driver 300 to cause the pull-down transistors of the first driver section 320 to be activated and to cause the pull-up transistors of the second driver section 330 to be activated, resulting in providing an OUT signal having an intermediate-low voltage (corresponding to output data of "01") at time TH. Neither the pull-up nor pull-down transistors of the boost circuit 346 are activated by the current data of "01".

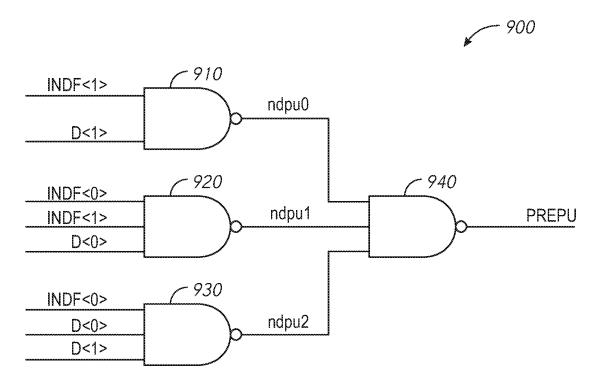

[0065] Figure 9A is a schematic diagram of a pull-up logic circuit 900 according to an embodiment of the disclosure. The pull-up logic circuit 900 may be included in the boost control circuit 245 of Figure 2B in some embodiments of the disclosure. The pull-up logic circuit 900 includes a NAND logic circuit 910 that receives the D<1> and INDF<1> signals. The input circuit 600 may provide the D<1> signal, and the input circuit 600 may further provide an IND<1> signal. The INDF<1> signal is the complement of the IND<1> signal, and may be provided by an inverter circuit (not shown) that receives the IND<1> signal from the input circuit 600 and provides the INDF<1> signal. The NAND logic circuit 910 provides an output signal ndpu0 that results from a NAND logic operation of the D<1> and INDF<1> signals. The pullup logic circuit 900 further includes NAND logic circuits 920 and 930. The NAND logic circuit 920 receives the D<0>, INDF<1>, INDF<0> signals. The input circuit 600 may provide the D<0> signal, and the input circuit 600 may further provide a IND<0> signal. The INDF<0> signal is the complement of the IND<0> signal, and may be provided by an inverter circuit (not shown) that receives the IND<0> signal from the input circuit 600 and provides the INDF<0> signal. The NAND logic circuit 920 provides an output signal ndpu1 that results from a NAND logic operation of the D<0>, INDF<1>, and INDF<0> signals. The NAND logic circuit 930 receives the D<1>, D<0>, and INDF<0> signals. The NAND logic circuit 930 provides an output signal ndpu2 that results from a NAND logic operation of the D<1>, D<0>, and INDF<0> signals. A NAND logic circuit 940 receives the ndpu0, ndpul, and ndpu2 signals from the NAND logic circuits 910. 920, and 930 and provides an output signal PREPU that results from a NAND logic operation. The PREPU signal may be used to control the pull-up transistor of the boost circuit 346.

[0066] In operation, the pull-up logic circuit 900 provides an active PREPU signal (e.g., active high logic level) when the data of the IN<1> and IN<0> bitstreams changes from a previous data to a current data that is represented by a higher voltage than the previous data. That is, where the previous data represented by the IN<1> and IN<0> bitstreams is "00", the pull-up logic circuit 900 provides an active PREPU signal for a current data of "01", "10", and "11", where the previous data represented by the IN<1> and IN<0> bitstreams is

"01", the pull-up logic circuit 900 provides an active PREPU signal for a current data of "10" and "11": and where the previous data represented by the IN<1> and IN<0> bitstreams is "10", the pull-up logic circuit 900 provides an active PREPU signal for a current data of "11". The active PREPU signal provided by the logic circuit 900 may be used to activate a boost circuit, for example, the boost circuit 346 of the signal driver 300. to provide additional drive to assist driving the common node to a higher voltage to provide an OUT signal. As will be described in more detail below, the PREPU signal is active for a portion of the data period of the OUT signal. For example, in some embodiments of the disclosure, the PREPU signal is limited to being active to assist the driving of the common node during a transition to a higher voltage when changing to current data that is represented by a higher voltage than the previous data. That is, the voltage of the OUT signal changes during the transition from one voltage level to another.

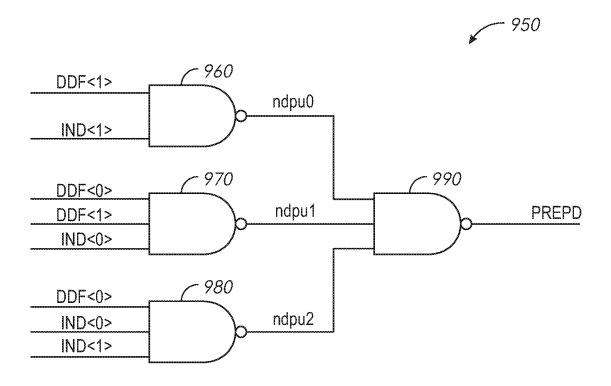

[0067] Figure 9B is a schematic diagram of a pull-down logic circuit 950 according to an embodiment of the disclosure. The pull-down logic circuit 950 may be included in the boost control circuit 245 of Figure 2B in some embodiments of the disclosure. The pull-down logic circuit 950 includes a NAND logic circuit 960 that receives the IND<1> and DDF<1> signals. The input circuit 600 may provide the IND<1> signal, and the input circuit 600 may further provide a D<1> signal. The DDF<1> signal is the complement of the D<1> signal, and may be provided by an inverter circuit (not shown) that receives the D<1> signal from the input circuit 600 and provides the DDF<1> signal. The NAND logic circuit 960 provides an output signal ndpd0 that results from a NAND logic operation of the DDF<1> and IND<1> signals. The pull-down logic circuit 950 further includes NAND logic circuits 970 and 980. The NAND logic circuit 970 receives the IND<0>, DDF<1>, DDF<0> signals. The input circuit 600 may provide the IND<0> signal, and the input circuit 600 may further provide a D<0> signal. The DDF<0> signal is the complement of the D<0> signal, and may be provided by an inverter circuit (not shown) that receives the D<0> signal from the input circuit 600 and provides the DDF<0> signal. The NAND logic circuit 970 provides an output signal ndpd1 that results from a NAND logic operation of the IND<0>, DDF<1>, and DDF<0> signals. The NAND logic circuit 980 receives the IND<1>, IND<0>, and DDF<0> signals. The NAND logic circuit 980 provides an output signal ndpd2 that results from a NAND logic operation of the IND<1>, IND<0>, and DDF<0> signals. A NAND logic circuit 990 receives the ndpd0. ndpd1. and ndpd2 signals from the NAND logic circuits 960, 970, and 980 and provides an output signal PREPD that results from a NAND logic operation. The PREPD signal may be used to control the pull-down transistor of the boost circuit 346. [0068] In operation, the pull-down logic circuit 950 provides an active PREPD signal (e.g., active high logic level) when the data of the IN<1> and IN<0> bitstreams

changes from a previous data to a current data that is represented by a lower voltage than the previous data. That is, where the previous data represented by the IN<1> and IN<0> bitstreams is "11", the pull-down logic circuit 950 provides an active PREPD signal for a current data of "00", "01", and "10"; where the previous data represented by the IN<1> and IN<0> bitstreams is "10", the pull-down logic circuit 950 provides an active PREPD signal for a current data of "01" and "00": and where the previous data represented by the IN<1> and IN<0> bitstreams is "01", the pull-up logic circuit 950 provides an active PREPD signal for a current data of "00". The active PREPD signal provided by the logic circuit 950 may be used to activate a boost circuit, for example, the boost circuit 346 of the signal driver 300, to provide additional drive to assist driving the common node to a lower voltage to provide an OUT signal. As will be described in more detail below, the PREPD signal is active for a portion of the data period of the OUT signal. For example, in some embodiments of the disclosure, the PREPD signal is limited to being active to assist the driving of the common node during a transition to a lower voltage when changing to current data that is represented by a lower voltage than the previous data. That is, the voltage of the OUT signal changes during the transition from one voltage level to another.

[0069] Figure 10 is a timing diagram showing various signals during operation of signal driver 300 with the input circuit 600 and pull-up and pull-down logic circuits 900 and 950 according to an embodiment of the disclosure. In the present example, the IND<1> signal is provided to the first driver section 320 instead of the IN<1> bitstream and the IND<0> signal is provided to the second driver section 330 instead of the IN<0> bitstream. The PREPU and PREPD signals are provided to the boost circuit 346 instead of the BoostHi and BoostLo signals. In the example of Figure 10, the output is terminated to a high supply voltage, resulting in "11" data represented by 1.2 V, "10" data represented by 1.0 V, "01" data represented by 0.8 V, and "00" data represented by 0.6 V. Other embodiments of the disclosure may use other voltage levels to represent the data values.

[0070] At time T0 the D flip-flops 610 and 640 of the input circuit 600 are clocked by a rising edge of the CLK signal (shown in Figure 10 as corresponding to a falling edge of the CLKF signal) and the data of the IN<1> and IN<0> bitstreams is latched to provide the D<1> and D<0> signals. In the present example, the previous data prior to time T0 is "01" and the current data at time T0 is "10". Latching of the current data "10" results in the D flipflop 610 providing a high logic level D<1> signal and the D flip-flop 640 providing a low logic level D<0> signal (not shown in Figure 10) shortly after time T0. With reference to the pull-up logic circuit 900, the INDF<1> is at a high logic level and the INDF<0> signal is at a low logic level based on the previous data due to the D flip-flops 620 and 660 of the input circuit not yet clocked by a rising edge of the CLKF signal. As a result, the NAND logic circuit 940

55

20

provides an active PREPU signal at time TA. The active PREPU signal activates the pull-up transistor of the boost circuit 346 to provide additional drive to pull up the common node in providing the OUT signal. As previously described, the boost circuit 346 is activated to assist with driving the common node to a higher voltage when the data of the IN<1> and IN<0> bitstreams changes from a previous data to a current data that is represented by a higher voltage than the previous data, such as in the present example where the previous data was "01" and the current data is "10".

[0071] At time T1, the D flip-flops 620 and 660 of the

input circuit 600 are clocked by a rising edge of the CLKF

signal (corresponding to a falling edge of the CLK signal).

The high logic level of the D<1> signal is latched by the D