#

#### EP 4 564 407 A1 (11)

## (12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication: 04.06.2025 Bulletin 2025/23

(21) Application number: 24216097.6

(22) Date of filing: 28.11.2024

(51) International Patent Classification (IPC):

B33Y 80/00 (2015.01) H01L 21/48 (2006.01) C08F 301/00 (2006.01) H01Q 21/28 (2006.01) H01Q 25/00 (2006.01) H01L 23/498 (2006.01) H01Q 9/04 (2006.01) H01Q 1/22 (2006.01) C08F 222/10 (2006.01) C08F 2/48 (2006.01) C08F 2/50 (2006.01) C08F 271/02 (2006.01) C08G 73/10 (2006.01) C08G 73/12 (2006.01)

(52) Cooperative Patent Classification (CPC):

H01L 21/4867; B33Y 80/00; C08F 2/48; C08F 2/50; C08F 222/102; C08F 271/02; C08G 73/1014; C08G 73/1039; C08G 73/1067; C08G 73/12; H01L 21/4846; H01L 21/486; H01L 23/498;

H01L 23/49827; H01Q 1/2283;

(Cont.)

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC ME MK MT NL NO PL PT RO RS SE SI SK SM TR

**Designated Extension States:**

BA

**Designated Validation States:**

**GE KH MA MD TN**

(30) Priority: 30.11.2023 KR 20230170852

(60) Divisional application:

24218377.0

24218381.2

24218382.0

24218385.3

24218387.9

(71) Applicant: UNIST (Ulsan National Institute of **Science** and Technology) Ulsan 44919 (KR)

(72) Inventors:

KWON, Jimin 44919 Ulsan (KR)

· JUNG, Haksoon Ulsan (KR)

(74) Representative: Dantz, Jan Henning et al

Loesenbeck - Specht - Dantz Patent- und Rechtsanwälte Am Zwinger 2

33602 Bielefeld (DE)

#### (54)SUBSTRATE FOR ELECTRICAL SUBSTRATE FOR ELECTRICAL CONNECTION BETWEEN **ELECTRONIC COMPONENTS AND ELECTRONIC DEVICE**

According to various embodiments, a substrate for electrical connection between electronic components may include: a body having a single layer structure; and at least one interconnect having a conductivity formed inside the body, wherein the at least one interconnect includes one side and the other side exposed to the outside of the body, and a line connecting the one side and the other side, and wherein the line is crossed in a transverse direction or a longitudinal direction through the inside of the body of the single layer structure, and may be implemented to have a specific curvature in some sections. Other various embodiments are possible.

(52) Cooperative Patent Classification (CPC): (Cont.) H01Q 9/0471; H01Q 21/28; H01Q 25/00

#### Description

#### **BACKGROUND**

#### 5 1. Field

**[0001]** Various embodiments of the present invention relate to apparatus, server, system, and method of operating the same for customized semiconductor packaging based on 3D printing.

## 2. Description of Related Art

**[0002]** The semiconductor industry has become more lightweight, miniaturized, multifunctional, and high performance at low prices.

**[0003]** The semiconductor process includes wafer manufacturing, a preprocess for generating chips, and a postprocess for packaging chips, and braking the system speed of improvement through semiconductor miniaturization technology based on Moore's law, and the postprocess, semiconductor packaging, is attracting attention as a key technology for making new added values.

**[0004]** Semiconductor packaging is a technology for electrical connection and protection between semiconductor parts, and chip performance can be greatly improved by increasing the electrical connection distance and number between semiconductor parts.

**[0005]** Recently, as various types of application products are developed, the need for development of packaging technology to provide customized packaging structures for demands of semiconductor customers that are diversified is increased.

## 25 SUMMARY

20

30

50

**[0006]** Semiconductor packaging is a technology for electrical connection and protection between semiconductor parts, and is a technology that can significantly improve chip performance by increasing the electrical connection distance and number between semiconductor parts. However, in the related art, costs of interconnection processes occupy most of the costs of semiconductor packaging, costs of interconnection structures of various patterns are increased, and as the structure becomes complicated, the costs are increased sharply. In addition, because semiconductor is used not only in the IT product but also in the AI, vehicle, and smart factory, various kinds of customer-customized semiconductor chips are needed, but it is difficult to solve this with the related art constructed semiconductor production facilities.

**[0007]** According to various embodiments, the apparatus, server, system, and methods for 3D printing-based customer-customized semiconductor packaging can simplify interconnection processes and reduce the costs of interconnection processes through the formation of interconnection structures using 3D printing. In addition, the apparatus, server, system, and methods for 3D printing-based customer-customized semiconductor packaging can create a substrate having a shape (e.g., suitable for the shape of the empty space in the product) suitable for the purpose and form interconnection structures of various patterns, and thus can optimize process cost items by excluding a separate interconnection process from the semiconductor package process.

**[0008]** In addition, in the case of a semiconductor substrate, it is also necessary to improve a material so as to lower the dielectric constant and CTE according to the use of a semiconductor, and to solve this problem, a polymer and an oligomer in combination with a specific monomer may be used to improve the above-described problem.

**[0009]** According to various embodiments, there may be provided a substrate for electrical connection between electronic components, the substrate including: a body having a single layer structure; and at least one interconnect having conductivity formed inside the body, wherein the at least one interconnect includes one side and the other side exposed to the outside of the body, and a line connecting the one side and the other side, and wherein the line intersects in a transverse direction or a longitudinal direction through the inside of the body of the single layer structure and is implemented to have a specific curvature in some sections.

**[0010]** According to various embodiments, there may be provided an electronic apparatus including: a plurality of electronic components; and a substrate including a body having a single layer structure, and at least one interconnect having conductivity formed inside the body, wherein the at least one interconnect includes one side and the other side exposed to the outside of the body, and a line connecting the one side and the other side, and wherein the line intersects in a transverse direction or a longitudinal direction through the inside of the body of the single layer structure and is implemented to have a specific curvature in some sections, and wherein a first electronic component and a second electronic component among the plurality of electronic components are electrically connected by the at least one interconnect.

[0011] According to various embodiments, the apparatus, server, system, and methods for 3D printing-based con-

sumer-customized semiconductor packaging, can simplify the interconnection process and reduce the cost of the interconnection process by forming an interconnection structure using 3D printing.

**[0012]** According to various embodiments, the apparatus, server, system, and methods for 3D printing-based consumer-customized semiconductor packaging, create a shape suitable for purpose (e.g., suitable for the shape of an empty space inside the product) and form an interconnection structure of various patterns, thereby excluding a conventional separate interconnection process from the semiconductor package process and optimizing the process cost item.

[0013] In particular, according to various embodiments, the oligomer including the monomer represented by Chemical Formula 1 has a structure that is mostly comprised of a polyimide component known to have a low dielectric constant and a low CTE, and thus may have a desired dielectric constant value and a CTE value, and has a structure having a very large number of (meth)acrylate functional groups per unit volume, and when the (meth)acrylate functional groups are sensitive to light, the oligomer is interconnected to form a very dense polymer network, and since the structural structure has a low CTE value due to a lower expansion rate due to heat.

**[0014]** In addition, the oligomer including the monomer represented by Chemical Formula 1 has a structure having a very large number of methacrylate functional groups per unit volume, and thus has a very low free volume that is not sensitive to light, and thus achieves a very high resolution (10  $\mu$ m or less) required in semiconductor packaging.

**[0015]** According to various embodiments, the technical solutions are not limited to the above-described solutions, and the solutions that are not mentioned may be clearly understood by those skilled in the art from the specification and the accompanying drawings.

#### 20 BRIEF DESCRIPTION OF THE DRAWINGS

## [0016]

10

50

- FIG. 1 is a diagram illustrating an example of a component of a customized printing system according to various embodiments.

- FIG. 2 is a diagram for describing an example of an application product of a structure produced by a customized printing system according to various embodiments.

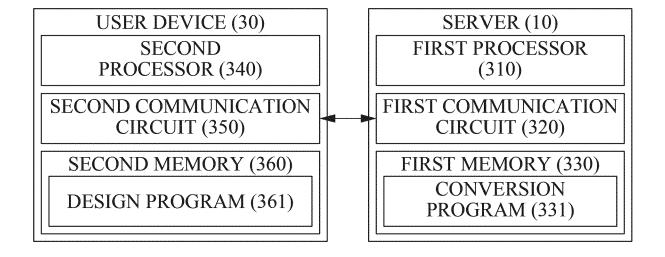

- FIG. 3 is a diagram for describing an example of a configuration of a server and a user device according to various embodiments.

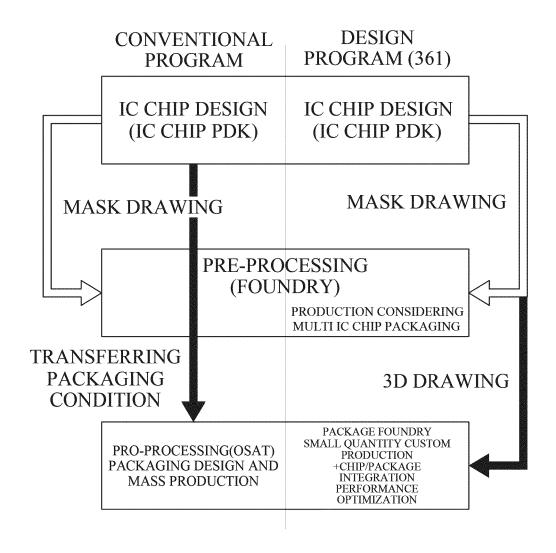

- FIG. 4 is a diagram for describing an example of a design program according to various embodiments.

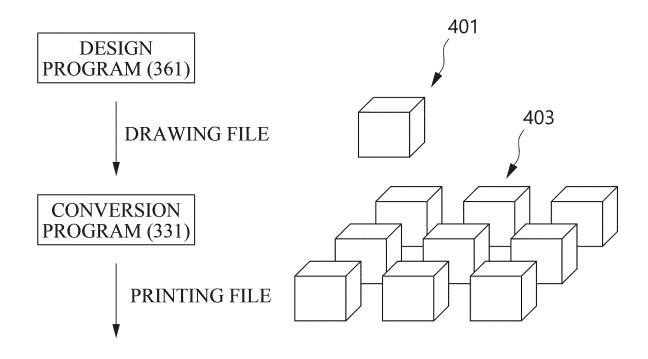

- FIG. 5 is a diagram for describing an example of a conversion program according to various embodiments.

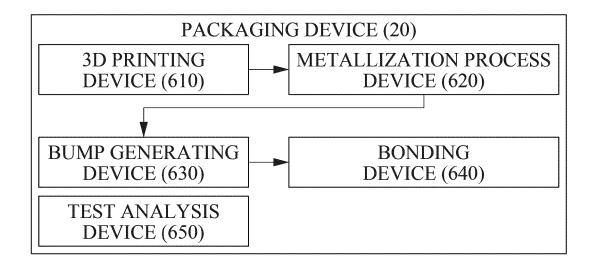

- FIG. 6 is a diagram for describing an example of a configuration of a package device according to various embodiments.

- FIG. 7 is a diagram for describing an example of an implementation of a packaging device according to various embodiments.

- FIG. 8 is a flowchart illustrating an example of a process according to various embodiments.

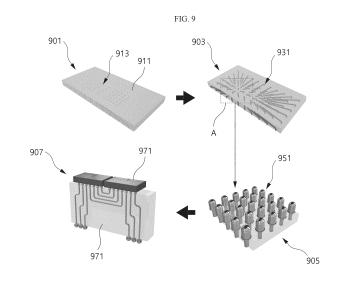

- FIG. 9 is a diagram for describing an example of a substrate formation process, a metallization process, a bump formation process, and a bonding process according to various embodiments.

- FIG. 10A is a flowchart illustrating an example of a formation process of a 3DP-based substrate according to various embodiments.

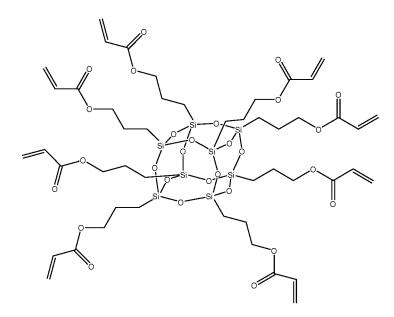

- FIG. 10B is a diagram for describing an example of a material of a substrate including Chemical Formula 1 according to various embodiments.

- FIG. 10C is a diagram for describing an example of a material of a substrate including Chemical Formula 2 according to various embodiments.

- FIG. 11A is a flowchart illustrating an example of a formation process of a 3DP-based substrate according to various embodiments.

5

10

15

20

25

30

35

40

55

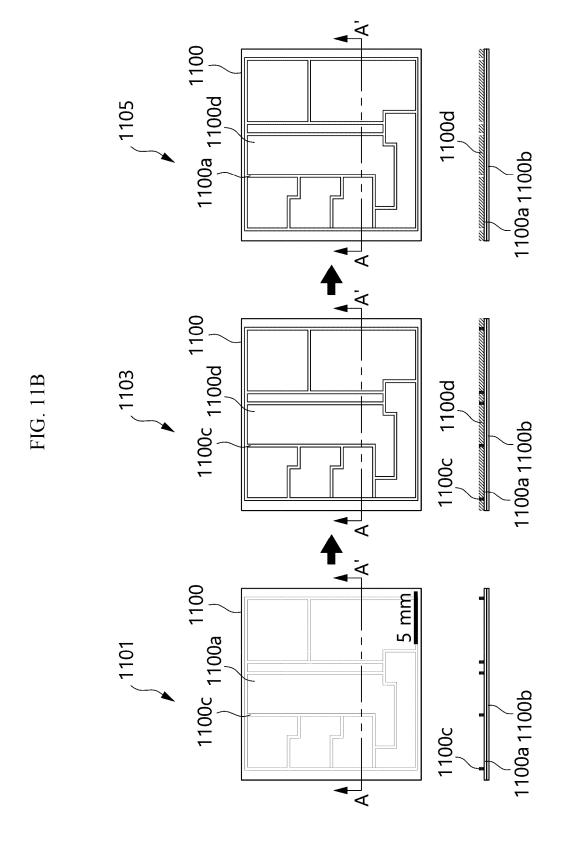

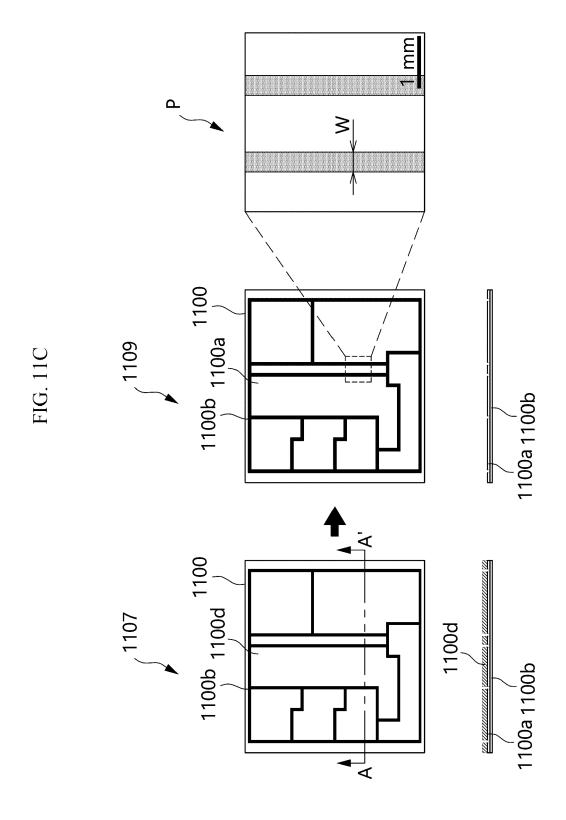

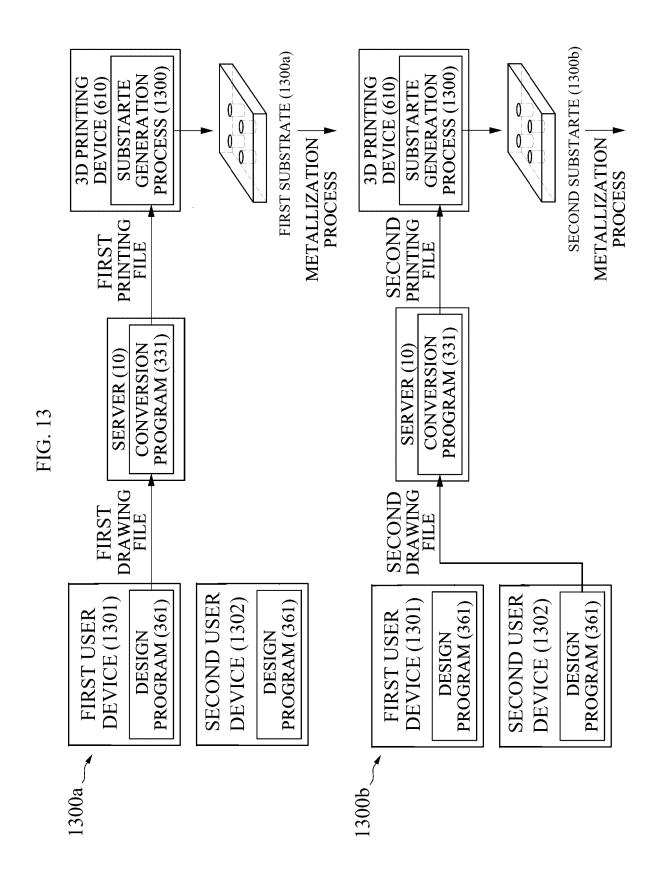

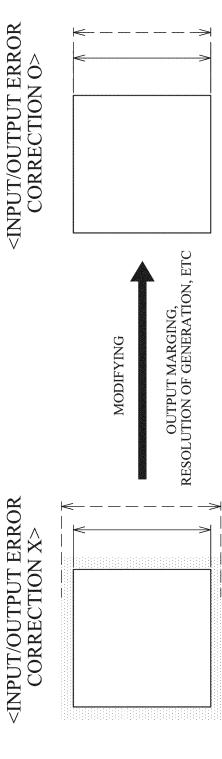

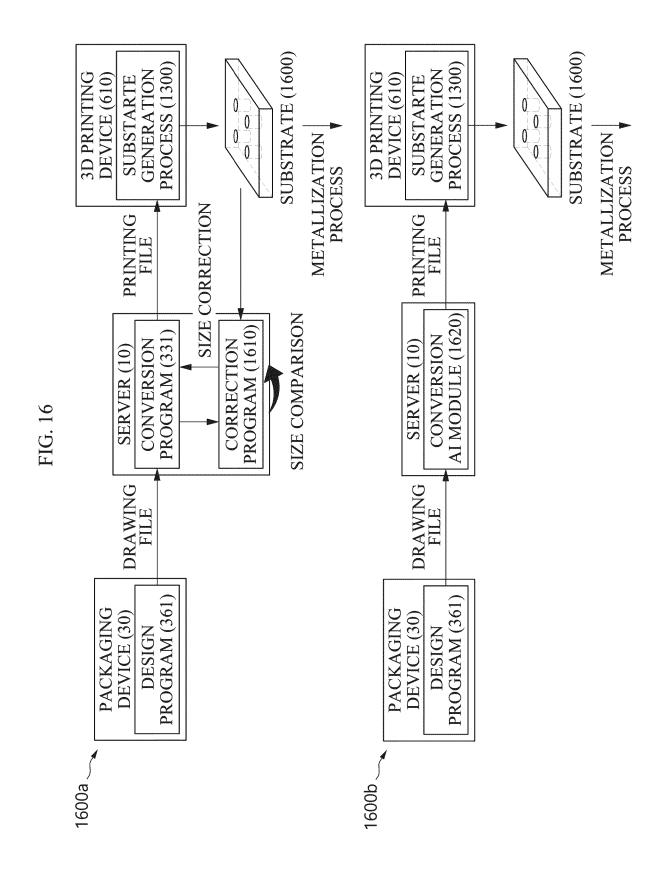

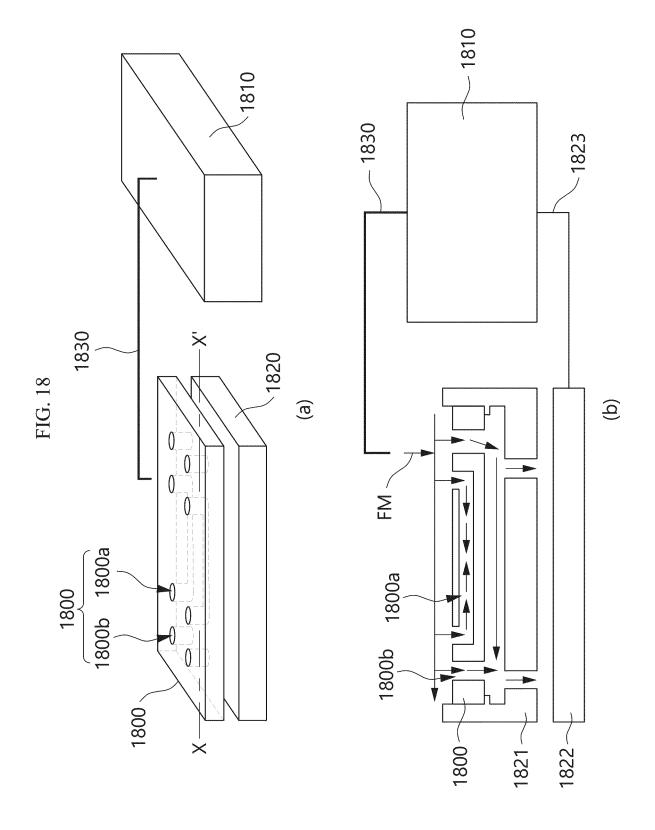

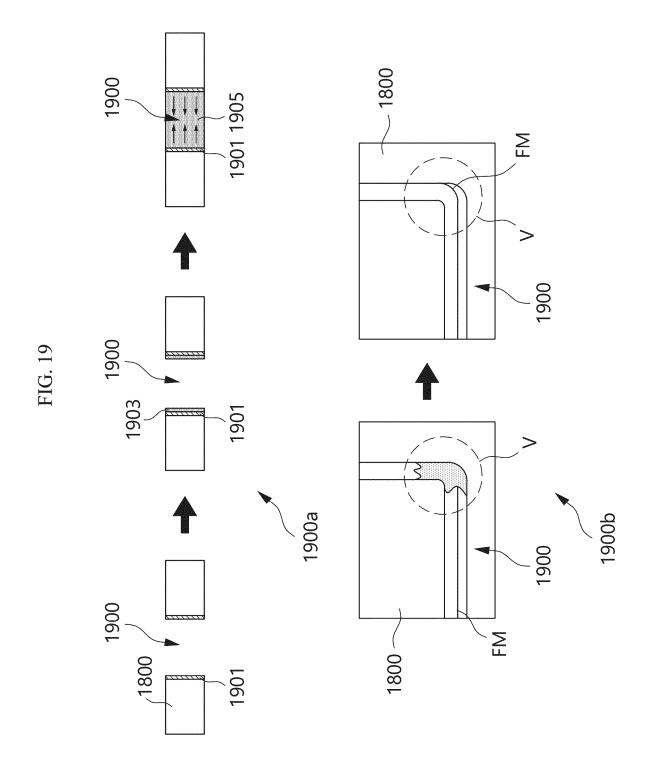

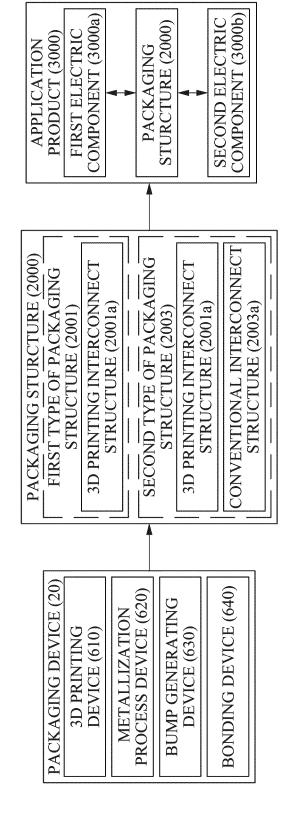

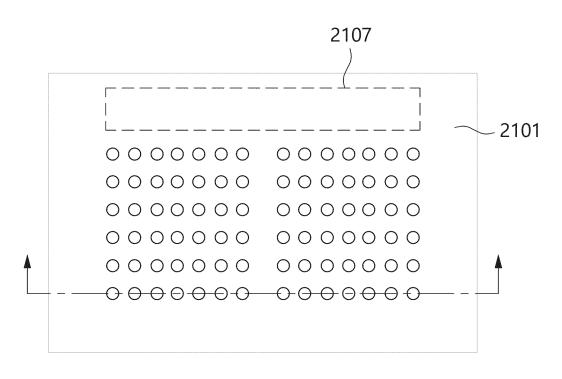

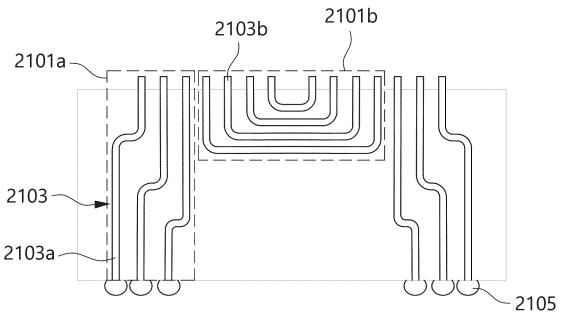

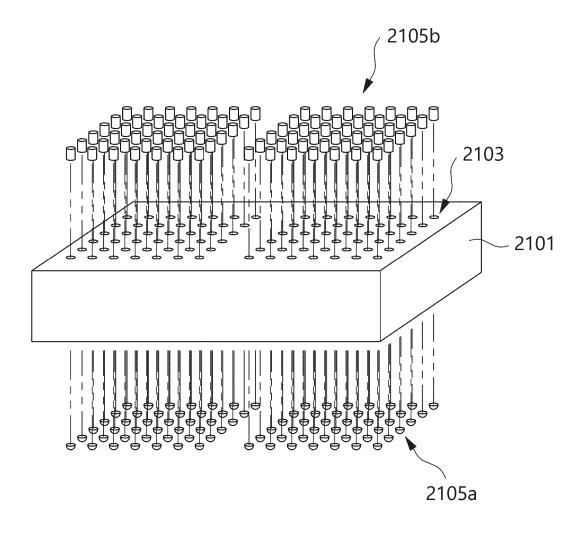

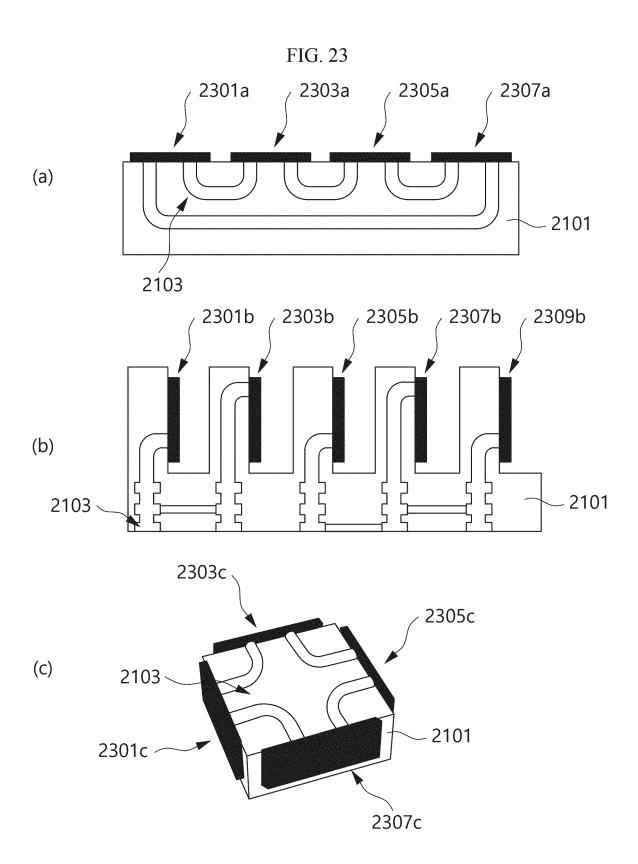

- FIG. 11B is a diagram for describing an example of a process of forming an external structure of a substrate according to various embodiments. FIG. 11C is a diagram for describing an example of a process of forming an external structure of a substrate according to various embodiments. FIG. 12 is a flowchart illustrating an example of an operation for generating a substrate based on a drawing file received from user devices according to various embodiments. FIG. 13 is a diagram for describing an example of an operation of generating different substrates according to a drawing file received from user devices according to various embodiments. FIG. 14 is a flowchart illustrating an example of an operation of correcting a size of a substrate with at least a part of a 3DP-based substrate formation operation according to various embodiments. FIG. 15 is a diagram for describing an example of an operation of correcting a size according to various embodiments. FIG. 16 is a diagram for describing examples of an operation of correcting a size of a server according to various embodiments. FIG. 17 is a flowchart illustrating an example of a metallization process according to various embodiments. FIG. 18 is a diagram for describing an example of a metallization device for a metallization process according to various embodiments. FIG. 19 is a diagram for describing an example of an operation of removing internal defects formed in a through structure of a substrate during a metallization process according to various embodiments. FIG. 20 is a diagram for describing an example of a packaging structure and an application product according to various embodiments. FIG. 21 is a diagram for describing an example of a first type of a packaging structure according to various embodiments. FIG. 22 is an exploded perspective view of an example of a first type packaging structure according to various embodiments.

- FIG. 23 is a diagram for describing various examples of a first type packaging structure according to various embodiments.

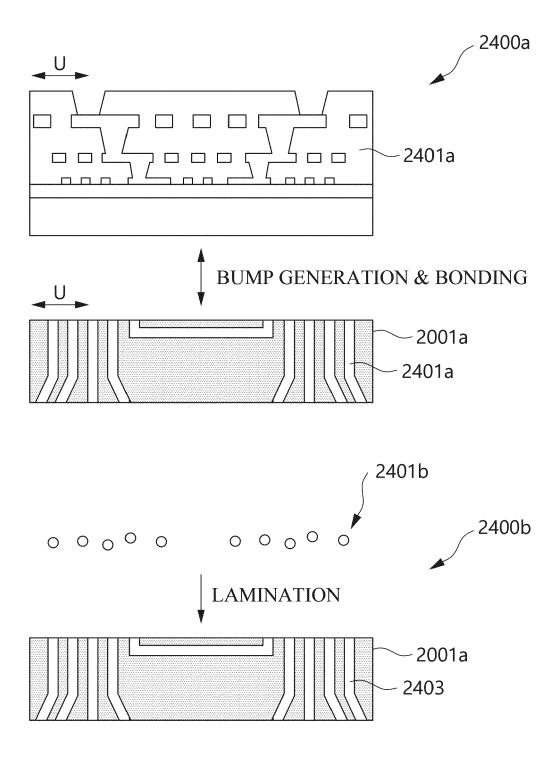

- FIG. 24 is a diagram for describing various examples of a second type packaging structure according to various embodiments.

- FIG. 25 is a diagram for describing an example of a packaging structure used in an application product according to 45 various embodiments.

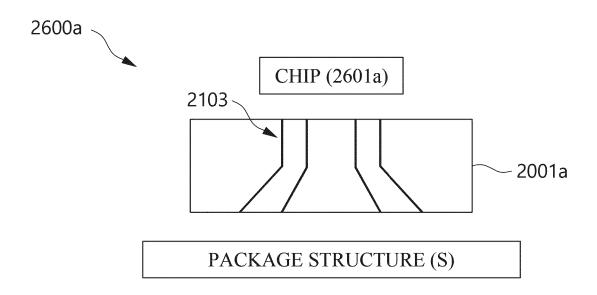

- FIG. 26 is a diagram for describing an example of a first type packaging structure used in a chip package according to various embodiments.

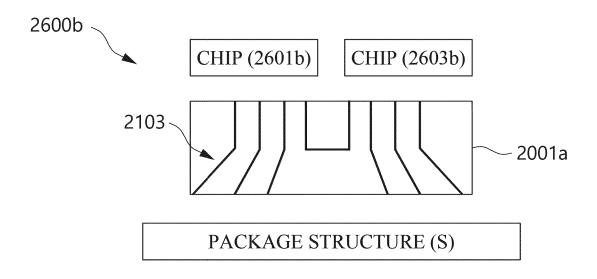

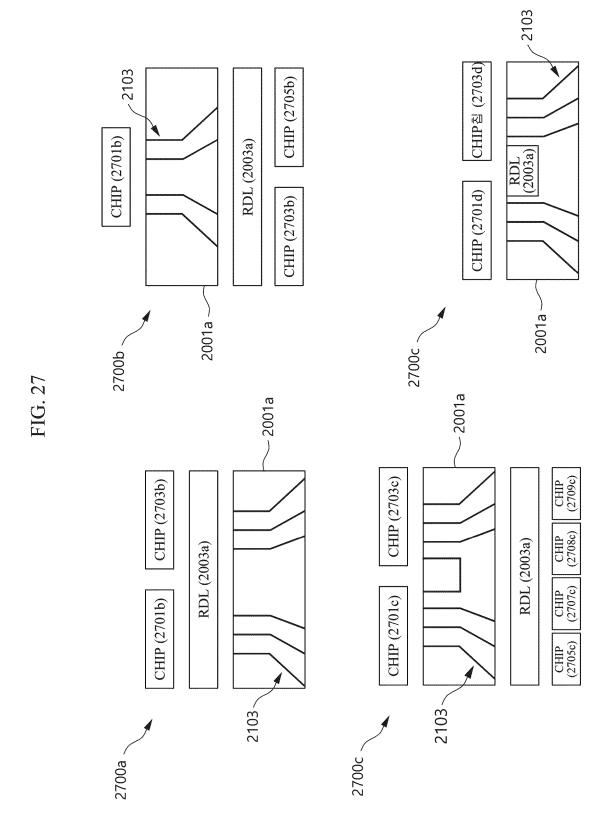

- 50 FIG. 27 is a diagram for describing an example of a second type packaging structure according to various embodiments.

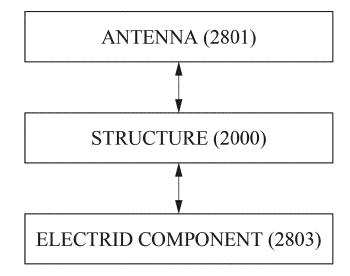

- FIG. 28 is a diagram for describing an example of a packaging structure used in an antenna in package according to various embodiments.

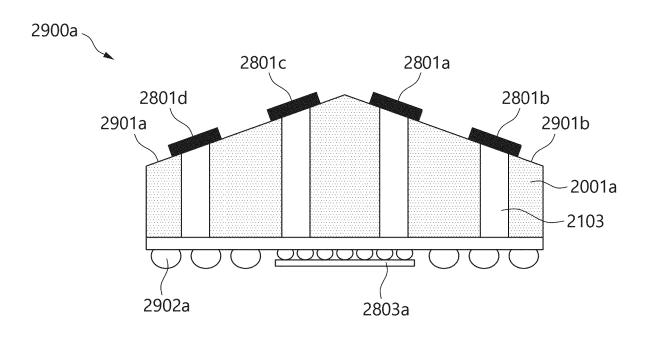

- FIG. 29 is a diagram for describing an example of a packaging structure used in an antenna in package according to various embodiments.

#### **DETAILED DESCRIPTION**

10

20

30

40

50

**[0017]** The electronic device according to various embodiments disclosed in the present disclosure may be various types of devices. The electronic device may include, for example, a portable communication device (e.g., a smartphone), a computer device, a portable multimedia device, a portable medical device, a camera, a wearable device, or a home appliance. The electronic device according to the embodiment of the present disclosure is not limited to the above-described devices.

[0018] It should be understood that various embodiments of the present disclosure and the terms used in the same are not intended to limit the technical features described in the present disclosure to particular embodiments, but to include various changes, equivalents, or alternatives to the corresponding embodiment. With regard to the description of the drawings, similar reference numerals may be used for similar or related components. The singular form of a noun corresponding to an item may include one or more of the items unless the relevant context clearly indicates otherwise. In the present document, each of the phrases such as "a or b," "at least one of a and b," "at least one of a or b," "a, b, or c," "at least one of a, b, and c," and "at least one of a, b, or c" may include any one of the items listed together in the corresponding phrase among the phrase, or any combination thereof. The terms "first," "second," or "first" may be used to simply distinguish the corresponding component from other corresponding components, and the corresponding components are not limited in other aspects (e.g., importance or order). When a (e.g., first) component is referred to as "coupled" or "connected" with or without the term "functionally" or "communicatively" in another (e.g., second) component, it means that the component may be connected to the other component directly (e.g., wiredly), wirelessly, or through a third component. [0019] The term "module" used in various embodiments of the present disclosure may include a unit implemented in hardware, software, or firmware, and may be used interchangeably with terms such as logic, logic block, component, or circuit. The module may be an integrated component or a minimum unit of the component or a part thereof that performs one or more functions. For example, according to an embodiment, the module may be implemented in the form of an application-specific integrated circuit (ASIC).

[0020] Various embodiments of the present disclosure may be implemented as software (e.g., a program) including one or more instructions stored in a storage medium (e.g., internal memory) or external memory that can be read by a machine (e.g., an electronic device). For example, a processor (e.g., processor) of a machine (e.g., an electronic device) may invoke at least one instruction from the storage medium and execute it. This enables the machine to perform at least one function in accordance with the at least one invoked instruction. The one or more instructions may include code generated by a compiler or code executable by an interpreter. The machine-readable storage medium may be provided in the form of non-transitory storage medium. Here, "non-transitory" is a device in which a storage medium is tangible and does not include a signal (e.g., electromagnetic wave), and this term does not distinguish between a case where data is semi-permanently stored in a storage medium and a case where data is temporarily stored.

**[0021]** According to an embodiment, a method according to various embodiments disclosed in this document may be included and provided in a computer program product. The computer program product may be traded between a seller and a buyer as a product. The computer program product may be distributed in the form of a storage medium (e.g., compact disc read only memory (CD-ROM)) readable by a device, or may be distributed (e.g., downloaded or uploaded) online through an application store (e.g., Play StoreTM), or directly between two user devices (e.g., smart phones). In the case of online distribution, at least a part of the computer program product may be temporarily stored or generated in a storage medium readable by a device such as a server of a manufacturer, a server of an application store, or a memory of a relay server.

**[0022]** According to various embodiments, each component (e.g., module or program) of the above-described components may include a single entity or a plurality of entities, and some of the plurality of entities may be separated from other components. According to various embodiments, one or more components or operations among the above-described corresponding components may be omitted, or one or more other components or operations may be added. Alternatively or additionally, a plurality of components (e.g., modules or programs) may be integrated into one component. In this case, the integrated component may perform one or more functions of each component of the plurality of components in the same or similar manner as that performed by the corresponding component among the plurality of components before the integration. According to various embodiments, operations performed by a module, a program, or another component may be sequentially, parallelly, repeatedly, or heuristically, one or more of the operations may be executed in a different order, omitted, or one or more other operations may be added.

**[0023]** According to various embodiments, a substrate for electrical connection between electronic components may include a body having a single layer structure; and at least one interconnect having conductivity formed inside the body, wherein the at least one interconnect includes one side and the other side exposed to the outside of the body and a line connecting the one side and the other side, and wherein the line is implemented to have a specific curvature in some sections through the inside of the body in the single layer structure.

**[0024]** According to various embodiments, the at least one interconnect may include a first interconnect and a second interconnect, wherein the specific slope of the first interconnect is a first slope, and the specific slope of the second

interconnect is a second slope different from the first slope.

10

20

30

35

40

45

50

55

**[0025]** According to various embodiments, the body may be implemented to correspond to the shape of an empty space inside an electronic product in which the substrate is placed on the basis on the 3D printing process.

**[0026]** According to various embodiments, the one side of the at least one interconnect is connected to a first electronic component of the electronic device, and the other side is connected to a second electronic component of the electronic device.

**[0027]** According to various embodiments, the at least one interconnect may include a plurality of conductive members, and the first density of the plurality of conductive members in a first region adjacent to the first electronic component of the substrate may be implemented to be different from the second density of the plurality of conductive members in a second region adjacent to the second electronic component of the substrate.

**[0028]** According to various embodiments, the body may be provided with a substrate implemented to include at least one structure and/or at least one member in a portion other than the portion in which the at least one interconnect is disposed.

**[0029]** According to various embodiments, the at least one structure may include an empty space structure for emitting heat generated from the substrate.

[0030] According to various embodiments, the substrate may be connected to an additional structure including at least one interconnect.

**[0031]** According to various embodiments, the density of the at least one interconnect of the substrate may be implemented to be lower than the density of the other at least one interconnect of the additional structure.

**[0032]** According to various embodiments, the substrate and the additional substrate may be connected to each other in a way that the substrate and the additional substrate are bonded to each other, or a substrate may be provided in a way that the substrate and the additional substrate are laminated on the substrate.

**[0033]** According to various embodiments, an electronic device may include: a plurality of electronic components; and a substrate including a body having a single-layer structure, and at least one interconnect having a conductivity formed inside the body, wherein the at least one interconnect includes one side and the other side exposed to the outside of the body, and a line connecting the one side and the other side, wherein the line intersects the inside of the body of the single-layer structure in a transverse direction or a longitudinal direction, and has a specific curvature in some sections, and wherein a first electronic component and a second electronic component among the plurality of electronic components are electrically connected by the at least one interconnect.

[0034] According to various embodiments, as a material for a substrate, at least one monomer that can be cured by a 3D printing process may be provided, wherein the at least one monomer has a resolution of um by the 3D printing process.

[0035] According to various embodiments, there is provided a material for a substrate for electrical connection between electronic components including a first composition including an oligomer including a monomer represented by the following Chemical Formula 1;

a compound including at least two acrylate functional groups; and a photoinitiator as a material for a substrate, or a cured product thereof. In Chemical Formula 1,

R1 to R4 are the same as or different from each other, and are each independently a substituted or unsubstituted C1 to C40 alkyl group,

Ar1 and Ar2 are the same as or different from each other, and are each independently a (meth)acrylate functional group-containing substituent, and n1 is an integer of 1 or more and 50 or less.

## <Formula 1>

[0036] According to various embodiments, the at least one monomer may be provided with a material for a substrate,

which may be implemented with a surface roughness of 0.5 um or less when cured.

**[0037]** According to various embodiments, a material for a substrate for electrical connection between electronic components is provided in which a weight ratio of an oligomer including a monomer represented by Chemical Formula 1 to a compound including at least two acrylate functional groups is 40:30 to 75:10.

**[0038]** According to various embodiments, a material for a substrate for electrical connection between electronic components is provided, further comprising a second composition comprising an oligomer comprising a monomer represented by the following Chemical Formula 2; a compound comprising at least two acrylate functional groups; and a photoinitiator; or a cured product thereof.

<Formula 2>

10

15

20

30

40

45

50

[0039] In Chemical Formula 2, n2 and n3 are an integer of 30 to 60, and n4 is an integer of 3 to 100.

**[0040]** According to various embodiments, a process method may be provided, and the process method may comprise: generating a substrate including at least one penetration structure based on 3D printing; hydrophilizing an inner surface of the at least one penetration structure; providing a fluid metal to the inner surface of the hydrophilized at least one penetration structure; and forming a metal inside the at least one penetration structure based on the fluid metal.

**[0041]** According to various embodiments, the process method may be provided, wherein forming a metal inside the at least one penetration structure may comprise: forming a metal surface of an atomic unit on the inner surface of the at least one penetration structure; and growing the metal on the metal surface based on the fluid metal after the metal surface is formed

**[0042]** According to various embodiments, a semiconductor packaging structure may be provided, and the semiconductor packaging structure may comprise: a substrate having at least one first interconnect structure having a conductivity formed based on a 3D printing process; and a structure having at least one second interconnect structure disposed on the substrate, wherein the at least one first interconnect structure is electrically connected to the at least one second interconnect structure, and a first density of the at least one first interconnect structure is lower than a second density of the at least one second interconnect structure.

**[0043]** According to various embodiments, a semiconductor packaging module may be provided, and the semiconductor packaging module may comprise: a single first semiconductor chip; and a substrate including a first surface facing a lower surface of the first semiconductor chip, a second surface facing the first surface, and at least one first interconnect structure inside between the first surface and the second surface, wherein the at least one first interconnect structure comprises a first portion exposed through the first surface, a second portion exposed through the second surface, and a line connecting between the first portion and the second portion, wherein the first portion is electrically connected to the first semiconductor chip, and the second portion is electrically connectable to another electronic component, wherein the line is transverse to the body of the single layer structure, and is formed with a specific slope in at least some sections.

**[0044]** According to various embodiments, an antenna packaging module may be provided, and the antenna packaging module may comprise: a substrate comprising a plurality of antennas; and a substrate comprising a first surface and a second surface having different slopes, at least one first conductive member exposed through the first surface, and at least one second conductive member exposed through the second surface, wherein the substrate is formed based on a 3D printing process, wherein the first surface and the second surface are facing different directions, and the at least one first conductive member is electrically connected to a first antenna group disposed on the first surface of the plurality of antennas, and the at least one second conductive member is electrically connected to a second antenna group disposed on the second surface of the plurality of antennas.

## 1. Customized 3D printing system

**[0045]** The customized 3D printing system 1 according to various embodiments is an optimized (or efficient) process based on the 3D printing technology, and may be a system implemented to produce products suitable for various types of devices (or devices) required by consumers.

**[0046]** For example, the customized 3D printing system 1 may be implemented to produce a packaging structure that includes an ultra-fine interconnect structure (or metal line structure, pipeline structure, or conductive member) for a semiconductor chip (e.g., processor, antenna chip, etc.). The ultra-fine interconnect structure may be formed suitable for various kinds of devices based on 3D printing. The customized 3D printing system 1 can reduce the operating burden of the

packaging process for implementing high-performance semiconductors provided for each electronic device based on the 3D printing technology.

**[0047]** As another example, the customized 3D printing system 1 may be implemented to produce a structure that has a shape corresponding to the shape of a narrow internal space within an electronic device and provides electrical connections between other electronic components. For example, the structure for providing the electrical connection may include a socket.

**[0048]** In addition to the described example, the customized 3D printing system 1 may provide a service for producing products corresponding to various types of electronic devices (or various consumer demands) based on an optimal process.

**[0049]** Hereinafter, for convenience of explanation, a customized 3D printing system 1 that provides a production service for a packaging structure will be described as an example. However, it is apparent to those skilled in the art that the various embodiments described may be applied to the customized 3D printing system 1 for the production of other various structures.

## 2. Component of a customized 3D printing system

10

20

30

45

50

**[0050]** Hereinafter, examples of components of the aforementioned customized 3D printing system 1 according to various embodiments will be described.

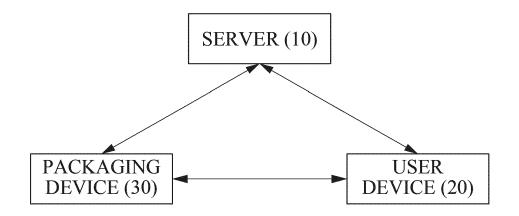

**[0051]** FIG. 1 is a diagram illustrating an example of a component of a customized printing system 1 according to various embodiments. Hereinafter, FIG. 1 will be further described with reference to FIG. 2.

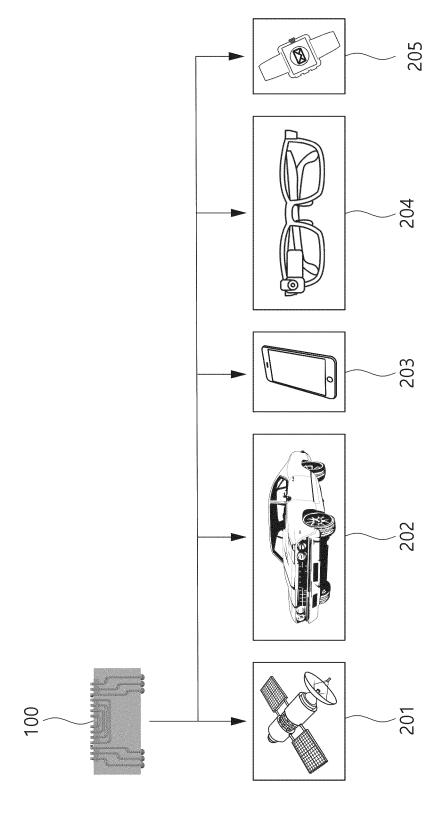

**[0052]** FIG. 2 is a diagram for describing an example of an application product of a structure produced by the customized printing system 1 according to various embodiments.

**[0053]** According to various embodiments, referring to FIG. 1, the customized 3D printing system 1 may include a server 10, a packaging device 20, and a user device 30. Meanwhile, the customized 3D printing system 1 may be implemented to include more components and/or fewer components, without being limited to the described and/or illustrated examples. For example, the server 10 may not be implemented, and the packaging device 20 may be implemented to perform all functions of the server 10. In addition, the server 10 may be provided as an add-on type device and connected to the packaging device 20.

[0054] According to various embodiments, the server 10 is at least one electronic device of an administrator for providing a production service for a packaging structure, and may be implemented to manage the overall structure production service. For example, the server 10 may receive information from the consumer's user device 30 and/or transmit information to the user device 30. For example, the server 10 may receive a drawing file for a structure to be produced from the user device 30. In addition, the server 10 may transmit information about the structure produced by the packaging device 20 to the user device 30. In addition, the server 10 may control the packaging device 20. For example, the server 10 may convert the drawing file received from the user device 30 into a print file and control the packaging device 20 based on the print file, thereby allowing the packaging structure to be produced by the packaging device 20.

[0055] According to various embodiments, the packaging device 20 may include at least one device (or facility) for producing the packaging structure 100 including a fine interconnection structure and connecting the packaging structure to at least one semiconductor chip (or at least one electronic part), as illustrated in FIG. 2. The packaging device 20 will be described in more detail below with reference to FIGS. 6 to 7. Referring to FIG. 2, the packaging structure 100 may be implemented to be provided in various types of devices 201, 202, 203, 204, and 205 based on 3D printing technology. [0056] According to various embodiments, the user device 30 may be a consumer's device that requests a production service for a packaging structure. The user device 30 may be various types of electronic devices available to consumers (or users), such as at least one PC, tablet, smartphone, head mounted display (HMD) device, etc. The user device 30 may acquire the drawing file generated by the consumer and transmit the drawing file to the server 10 as described above.

## 2.1 Details of each component

[0057] Hereinafter, an example of a component of the customized 3D printing system 1 according to various embodiments will be further described.

#### 2.1.1 Server and user device

**[0058]** FIG. 3 is a diagram for describing the configuration of the server 10 and user device 20 according to various embodiments. Hereinafter, FIG. 3 will be described with reference to FIGS. 4 to 5.

**[0059]** FIG. 4 is a diagram for describing an example of a design program 361 according to various embodiments. FIG. 5 is a diagram for describing an example of a conversion program 331 according to various embodiments.

[0060] According to various embodiments, referring to FIG. 3, the server 10 may include a first processor 310, a first

communication circuit 320, and a first memory 330 that stores the conversion program 331, and the user device 30 may include a second processor 340, a second communication circuit 350, and a second memory 360 that stores the design program 361. Meanwhile, the server 10 and/or the user device 30 may be implemented to include more devices and/or less devices, without being limited to the described and/or illustrated examples. For example, the server 10 and/or the user device 30 may further include a speaker (not shown), a microphone (not shown), a touch screen (not shown), a display (not shown), and the like.

**[0061]** According to various embodiments, the first processor 310 and the second processor 340 may control at least one other component (e.g., hardware or software component) connected to the first processor 310 and the second processor 340 by executing software (or computer code, program, instructions, or module), and may be implemented to perform various data processing or calculations. According to an embodiment, as at least a part of the data processing or calculation, the first processor 310 and the second processor 340 may load a command or data received from another component into a volatile memory, process the command or data stored in the volatile memory, and store the resultant data in a non-volatile memory. According to an embodiment, the first processor 310 and the second processor 340 may include a main processor (e.g., a central processing unit or an application processor) and an auxiliary processor (e.g., a graphic processing device, an image signal processor, a sensor hub processor, or a communication processor) that is operable independently or together with the main processor. Additionally or alternatively, the auxiliary processor may be configured to use lower power than the main processor or to be specialized to a specified function. The auxiliary processor may be implemented separately from the main processor or as a part thereof.

10

20

30

45

50

**[0062]** According to various embodiments, the first communication circuit 320 and the second communication circuit 330 may support the establishment of a wireless communication channel between devices and communication performance through the established communication channel. The communication circuit (e.g., the first communication circuit 320 and/or the second communication circuit 330) may be implemented to include one or more communication processors that are operated independently from the processor (e.g., the first processor 310 and/or the second processor 340) and support wireless communication, but is not limited to the described examples.

**[0063]** According to various embodiments, the first memory 330 and the second memory 360 may store various data used by at least one component (e.g., the first processor 310 and the second processor 340) of the server 10 and the user device 20. For example, the first memory 330 may store the conversion program 331, and the second memory 360 may store the design program 361. Based on the execution of the programs (e.g., the conversion program 331 and the design program 361) by the above by the processor (e.g., the first processor 310 and the second processor 340), the server 10 and the user device 20 may provide functions corresponding to the program.

[0064] According to various embodiments, the design program 361 may be implemented to generate drawing files for the packaging structure. As an example, the drawing file may be a cad file including the design of the packaging structure, but is not limited to the examples described, and may have various types of formats for including the design of a threedimensional structure for the design of the structure. For example, as shown in FIG. 4, the design program 361 may be implemented to provide a function so that both the design of the chip and the design of the package are possible. For example, in the related art, as the chip design program for designing the chip and the package design program for designing the package are separately implemented, each of the chip and the package may not be designed in a form considering each other, resulting in a resource burden for the design. The design program 361 according to various embodiments may be implemented to provide an integrated interface for the integrated design of the chip and the packaging structure, an integrated rule (or integrated parameter) for the design of the chip and the package, and an integrated tool. The integrated interface may mean a graphic user interface for the integrated tool (e.g., drawing tool or the like) consumer (or user) to drawing the chip and the package. The integrated rule (or integrated parameter) may mean physical characteristics, material characteristics, and electrical characteristics such as size, and the like, which are applied to the chip and the packaging designed based on the design program 361. For example, the design program 361 may be implemented to generate a mask drawing file for the chip and a 3D drawing file for the packaging structure. The consumer may be able to design the chip and the packaging structure corresponding to the chip on the integrated interface based on the integrated rule by using the design program installed in the user device 30. Accordingly, as the design of each of the chip and the package may be considered each other, the resources for the design are reduced, and the connectivity (e.g., electrical connectivity, physical connectivity) between the produced chip and the produced packaging structure may be improved, so that high-quality semiconductor packaging may be performed.

**[0065]** According to various embodiments, the conversion program 331 may be implemented to generate a print file corresponding to the drawing file. As an example, the print file may be a STL file including the design of the packaging structure, but is not limited to the examples described, and may be a file having various types of formats for 3D printing. Based on the print file, the packaging device 20 described below may produce the packaging structure. Referring to FIG. 5, according to an embodiment, the conversion program 331 may be implemented to generate a print file including a plurality of packaging structures 403 based on the packaging structure 401 included in the drawing file. At this time, the conversion program 331 may be implemented to determine the number of the plurality of packaging structures included in the print file based on the number of the packaging structures required by the consumer. Accordingly, the productivity of the packaging

structure 100 produced when the process is performed in the process of the packaging device 20 is improved, and accordingly, the process operation burden may be reduced by performing an optimal process in the consumer's production demand.

**[0066]** According to various embodiments, the conversion program 331 may generate a print file corresponding to the packaging structure including at least one through structure (or a a hole structure). That is, the conversion program 331 may generate a print file for the outer appearance of the structure except the interconnect of the interconnect of the metal material. This may be implemented by the 3D printing device 610 to determine the number of the plurality of packaging structures included in the

**[0067]** On the other hand, the aforementioned conversion program 331 is not limited to the described and/or illustrated example, and the customized 3D printing system 1 may be implemented in a form in which the print file stored in the user device 30 and converted by the user device 30 is provided to the server 10, or the design program 361 is authored to the server 10 and the user device 30 is connected to the server 10 to use the design program 361.

#### 2.1.1 Packaging device

10

15

20

30

45

50

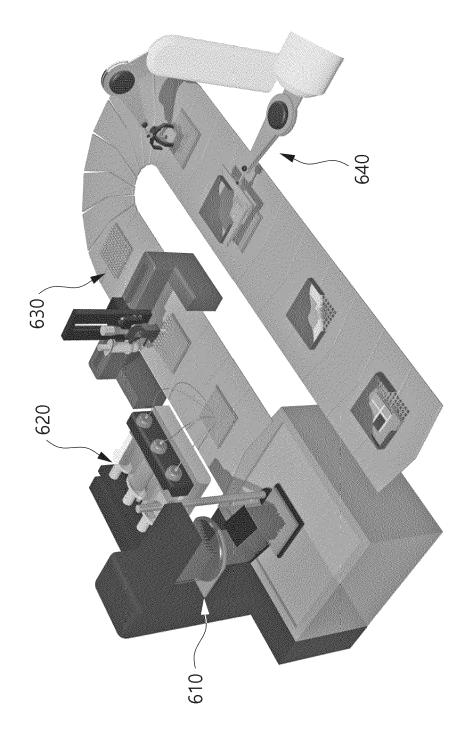

**[0068]** FIG. 6 is a diagram for describing an example of a configuration of the packaging device 20 according to various embodiments. Hereinafter, FIG. 6 will be further described with reference to FIG. 7.

**[0069]** FIG. 7 is a diagram for describing an example of an implementation of the packaging device 20 according to various embodiments.

**[0070]** According to various embodiments, referring to FIG. 6, the packaging device 20 may include a printing device 610, a metallization process device 620, a bump generating device 630, a bonding device 640, and a test analysis device 650 to generate a packaging structure. Referring to FIG. 7, the aforementioned devices (or facilities) of the packaging device 20 may be provided in a form capable of a continuous process. For example, each device may be implemented in a form of being connected for a process based on at least one trailer, and the process for a packaging structure moving on the trailer may be performed by the aforementioned devices 610, 620, 630, 640, and 650. The packaging structure may mean at least one of a substrate (or dielectric layer) generated by the printing device 610, a substrate including an interconnect generated by the metallization process device 620, a substrate where a bump is formed by the bump generating device 630, or a structure including another electronic component (e.g., a chip and/or a packaging substrate) and a substrate physically connected to another electronic component by the bonding device 640. On the other hand, the packaging device 20 may be implemented to include more devices (or facilities) or fewer devices (or facilities), without being limited to the described and/or illustrated examples. For example, the packaging device 20 may be implemented to include only the 3D printing device 610 and the metallization process device 620 to generate a structure (or substrate) including various types of fine interconnects, but is not limited to the described examples.

[0071] According to various embodiments, the 3D printing device 610 may be implemented to form a substrate including at least one empty space structure (or hole structure) based on the 3D printing process and the print file. The 3D printing apparatus may be implemented as a device that performs a 3D printing process based on at least one of a material extrusion type method such as fused deposition modeling (FDM) and fused filament fabrication (FFF), a photopolymerization type method such as stereolithography (SLA), digital light processing (DLP), continuous liquid interface production technology (CLIP), liquid crystal display (LCD), and projection micro streolithopraphy (PuSL), a powder sintering method such as stereolithography (SLS), selective laser melting (SLM), direct metal laser sintering (DMLS), and multi-jet printing (MJP), a binder spraying method such as color jet printer (CJP), and inkjet printer (IJP), a sheet amination method such as laminated object manufacturing (LOM), selective deposition lamination (SDL), and viscous lithography manufacturing (VLM), or a directional energy deposition method such as laser-aided direct metal tooling (DMT), laser metal deposition (LMD), and laser engineered net shaping (LENS), and the like, and the 3D printing method is well-known and thus a detailed description thereof will be omitted. Accordingly, the material of the substrate generated by the 3D printing apparatus 610 may be selected as at least one of a light (e.g., ultraviolet, infrared, visible light) curable material or a thermally curable material based on the 3D printing method described above.

**[0072]** According to various embodiments, the 3D printing apparatus 610 may be implemented to generate the substrate at a resolution (or resolution) in  $\mu$ m. The resolution may include  $2\mu$ m,  $10\mu$ m, and  $25\mu$ m, but is not limited to the described example.

**[0073]** According to various embodiments, the metallization process apparatus 620 may be implemented to generate at least one interconnect (or at least one metal line) inside the substrate generated by the 3D printing apparatus 610. For example, as shown in FIG. 7, the metallization process apparatus 620 may fill and grow a conductive material (e.g., metal) in at least one through structure inside the substrate (or may fill with a metal).

**[0074]** According to various embodiments, the bump generation apparatus 630 may generate a bump for electrically connecting to other electronic components (e.g., chips, packaging substrates, and the like) on the surface of the substrate. The bump may include at least one of a pillar of copper material and a bump of lead material (Cu pillar+Solder bump) disposed on the pillar, a bump of stud-shaped lead material, or a bump of ball-shaped lead material, but is not limited to the

described example, and the bump may be formed in various materials and in various shapes, and a detailed description thereof will be omitted because of well-known techniques. Meanwhile, before forming the bump, the bump generation apparatus 630 may form under bump metallurgy (UBM) in a portion where the interconnect is exposed.

**[0075]** According to various embodiments, the bonding apparatus 640 may physically connect other electronic components (e.g., chips, packaging substrates, and the like) with the substrate where the bump is generated, and a detailed description thereof will be omitted because of well-known techniques.

**[0076]** According to various embodiments, the test analysis apparatus 650 may be implemented to perform test analysis on the packaging structure generated by the packaging apparatus 20. The type of test analysis may include electromagnetic simulation, thermal durability, pulse response, optical non-destructive testing, etc., and test analysis for detecting defects between processes.

#### 3. Process

10

20

30

45

50

[0077] Hereinafter, an example of the process based on the packaging device 20 according to various embodiments will be described.

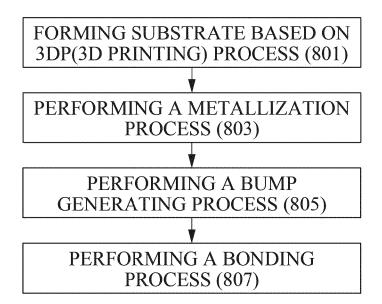

**[0078]** FIG. 8 is a flowchart illustrating an example of a process according to various embodiments. Operations may be performed regardless of the order of the operations shown and/or described, and more operations may be performed and/or fewer operations may be performed. Hereinafter, FIG. 8 will be further described with reference to FIG. 9.

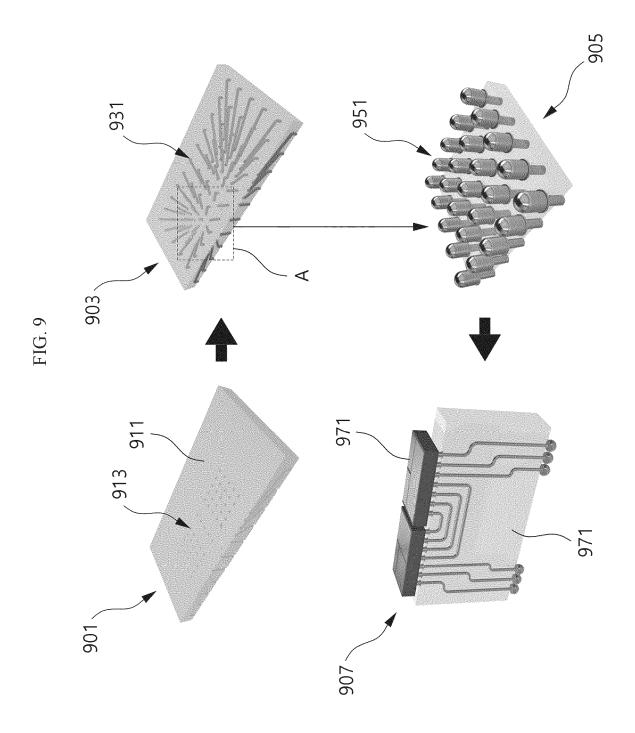

**[0079]** FIG. 9 is a diagram for describing an example of a substrate formation process, a metallization process, a bump formation process, and a bonding process according to various embodiments.

**[0080]** According to various embodiments, the packaging device 20 (e.g., the 3D printing device 610) may form a 3DP(3D printing) based substrate in operation 801. For example, the packaging device 20 may form a substrate including at least one internal structure based on the 3DP. For example, the at least one internal structure may include a penetration structure. As shown in 901 of FIG. 9, the packaging device 20 (e.g., the 3D printing device 610) may generate a substrate 911 having at least one penetration structure 913 formed inside a printed file based on the 3D printing. At this time, as the substrate 911 is formed in a shape suitable for consumer demand (or suitable for various kinds of electronic devices) based on the 3DP, the space inside the electronic device may be optimized, and the quality of the form factor of the electronic device may be improved.

[0081] For example, the packaging device 20 may form a substrate including at least one external structure based on the 3DP.

**[0082]** According to various embodiments, the packaging device 20 (e.g., the metallization process device 620) may perform a metallization process in operation 803. For example, as shown in 903 of FIG. 9, the packaging device 20 (e.g., the metallization process device 620) may metalize the at least one penetration structure 913 inside the substrate 911, thereby forming at least one interconnect 931 (or metal line) inside the substrate 911.

**[0083]** According to various embodiments, the packaging device 20 (e.g., the bump generating device 630) may perform the bump generating process in operation 805. For example, as shown in 905 of FIG. 9, the packaging device 20 (e.g., the bump generating device 630) may form a bump 951 on the substrate 911. Each bump 951 may be formed on a portion of the at least one interconnect 931 exposed to the outer surface of the substrate 911, and may be electrically connected.

**[0084]** According to various embodiments, the packaging device 20 (e.g., the bonding device 640) may perform the bonding process in operation 807. For example, as shown in 907 of FIG. 9, the packaging device 20 (e.g., the bonding device 640) may physically connect at least one electronic component (e.g., a chip) 973) different from the bump 951 formed on the substrate 911, and may electrically connect the at least one electronic component (e.g., a chip) 973) different from the substrate 911. Electrical connections may be established between electronic components that are physically (or electrically) connected to the substrate 911 based on at least one connector 931 formed inside the substrate 911. In this case, since the interconnect 931 may be implemented in various forms by the above-described 3DP substrate forming process 801, the interconnect 931 may be formed with a simpler and more efficient electrical connection structure without a complicated electrical connection structure compared to conventional packaging members (e.g., redistribution layer (RDL) and through silicon via (TSV)), thereby improving product quality and reducing electrical energy loss.

[0085] According to various embodiments, the semiconductor packaging process may be simplified based on the above-described processes 801, 803, 805, and 807. For example, a process for forming the existing interconnect structure (e.g., redistribution layer (RDL) and through silicon via (TSV)) may include forming a dielectric layer (e.g., substrate), forming a photomask process (hole forming process), filling a conductive material, forming a metal seed layer, forming a photoresist, forming a rewiring layer, and etching. The packaging device 20 according to various embodiments may reduce the process steps and efficient the packaging process by performing only a single process for forming the 3DP-based substrate 801 instead of a multi-step process for forming a hole based on the photomask after forming the dielectric layer. In addition, the packaging device 20 may reduce the process steps and efficient the packaging process by performing a microfluidic metal-based metallization process on the substrate 801 having the penetration structure instead of a multi-step process including forming a metal seed layer, forming a photoresist, forming a rewiring layer,

and etching.

5

10

20

30

40

45

50

55

[0086] Hereinafter, examples of each process according to various embodiments will be described in detail.

## 3.1 3DP-based substrate forming process

3.1.1 Substrate forming process and material of the substrate

**[0087]** FIG. 10A is a flowchart illustrating an example of a 3DP-based substrate 911 forming process according to various embodiments. Operations may be performed regardless of the order of the operations shown and/or described, and more operations may be performed and/or fewer operations may be performed. Hereinafter, FIG. 10 will be further described with reference to FIG. 11.

**[0088]** FIG. 10B is a diagram for describing an example of a material of a substrate including Chemical Formula 1 according to various embodiments. FIG. 10C is a diagram for describing an example of a material of a substrate including Chemical Formula 2 according to various embodiments.

**[0089]** According to various embodiments, the packaging device 20 (e.g., the 3D printing device 610) may provide a material for generating the substrate 911 (or dielectric layer) in operation 1001.

**[0090]** According to various embodiments, the material can be a material having at least one of characteristics that can be processed based on 3D printing or characteristics for semiconductor packaging. Material may be implemented to have at least one of processable characteristics or characteristics for semiconductor packaging, described by way of example below.

**[0091]** For example, as the processable characteristic, the material may have characteristics that can be cured based on the above-described various types of 3D printing schemes. For example, the material may have thermal curing and/or photocuring characteristics.

[0092] Hereinafter, the material will be described in more detail.

**[0093]** According to various embodiments, the term "substituted" means that a hydrogen atom bonded to a carbon atom of a compound is changed into another substituent, and the substituted position is not limited as long as it is a position at which a hydrogen atom is substituted, that is, a position at which a substituent is substituted, and when two or more substituents are substituted, two or more substituents may be the same as or different from each other.

[0094] In the present specification, "substituted or unsubstituted" means that it is unsubstituted or substituted with one or more substituents selected from the group consisting of deuterium; a halogen group; a cyano group; a C1 to C60 alkyl group; a C2 to C60 alkenyl group; a C2 to C60 alkynyl group; a C3 to C60 cycloalkyl group; a C2 to C60 heterocycloalkyl group; a C6 to C60 aryl group; a C2 to C60 heterocycloalkyl group; a phosphine oxide group; and an amine group, or a substituent linked to two or more substituents selected from the among the exemplified substituents.

35 3.1.1.1 first composition or a cured product thereof

**[0095]** According to various embodiments, the substrate material includes a first composition including an oligomer including a monomer represented by the following Chemical Formula 1; a compound including at least two acrylate functional groups; and a photoinitiator; or a cured product thereof.

[Chemical Formula 1]

13

**[0096]** In this case, the first composition may be directly or may include a cured product thereof, and the cured product of the first composition may be a photosensitive polyimide photocurable resin.

**[0097]** According to various embodiments, R1 to R4 may be the same as or different from each other, and may each independently be a substituted or unsubstituted C1 to C40 alkyl group.

**[0098]** According to various embodiments, R1 to R4 may be the same as or different from each other, and may each independently be a substituted or unsubstituted C1 to C30 alkyl group.

**[0099]** According to various embodiments, R1 to R4 may be the same as or different from each other, and may each independently be a substituted or unsubstituted C1 to C10 alkyl group.

**[0100]** According to various embodiments, R1 to R4 may be the same as or different from each other, and may each independently be a substituted or unsubstituted C1 to C10 alkyl group.

**[0101]** According to various embodiments, R1 to R4 may be the same as or different from each other, and may each independently be a substituted or unsubstituted C1 to C10 alkyl group.

**[0102]** According to various embodiments, R1 to R4 may be the same as or different from each other, and may each independently be a trifluoromethyl group. According to various embodiments, R1 to R4 may be the same.

**[0103]** According to various embodiments, Ar1 and Ar2 may be the same as or different from each other, and may each independently be a substituent including a (meth)acrylate functional group.

**[0104]** In the present specification, the (meth)acrylate includes both acrylate and methacrylate. The (meth)acrylate-based resin may be, for example, a copolymer of a (meth)acrylic acid ester-based monomer and a crosslinkable functional group-containing monomer.

**[0105]** According to various embodiments, Ar1 and Ar2 are the same as or different from each other, and are each independently a substituent including a (meth)acrylate functional group, and may be represented by the following structural formula.

[0106] In the structural formula,

5

10

20

30

35

40

45

50

55

means a position linked to a monomer.

[0107] According to various embodiments, the oligomer including the monomer represented by Chemical Formula 1 has

a structure in which most of the structure is formed of a polyimide component known to have a low dielectric constant and a low CTE, and thus the oligomer may have a desired dielectric constant value and a CTE value, and has a structure in which the number of (meth)acrylate functional groups per unit volume is very large, and when the (meth)acrylate functional groups are sensitive to light, the oligomer may be interconnected to form a very dense polymer network, and thus the structure may have a characteristic in which the expansion rate due to heat is lowered, and thus the oligomer may have a low CTE value.

**[0108]** In addition, the oligomer including the monomer represented by Chemical Formula 1 has a structure in which the number of methacrylate functional groups per unit volume is very large, and thus the free volume which is not sensitive to light is extremely small, and thus the oligomer may achieve a very high resolution (10  $\mu$ m or less) required in semiconductor packaging.

**[0109]** In various embodiments, the compound including at least two acrylate functional groups may be trimethylol-propane triacrylate.

**[0110]** The compound including the at least two acrylate functional groups assists the connectivity between the monomers of Formula 1 to be further deepened, thus enabling low CTE values, and assists the monomers of Formula 1 in a solid state to be dissolved in a solution state capable of 3D printing.

**[0111]** In various embodiments, the photoinitiator may be substituted with one or two or more substituents selected from the group consisting of a triazine-based compound, a biimidazole compound, an acetophenone-based compound, an O-acyloxime-based compound, a thioxanthone-based compound, a phosphine oxide-based compound, a coumarin-based compound, and a benzophenone-based compound.

[0112] Specifically, the photoinitiator may be a triazine-based compound such as 2,4-trichloromethyl-(4'-methoxyphenyl)-6-triazine, 2,4-trichloromethyl-(4'-methoxystyryl)-6-triazine, 2,4-trichloromethyl-(picolinyl)-6-triazine, 2,4-trichloromethyl-(become thyl-(a'-methoxystyryl)-6-triazine, 2,4-trichloromethyl-(become thyl-(a'-methoxystyryl)-6-triazine, 2,4-trichloromethyl-(become thyl-(a'-methoxystyryl)-6-triazine, 2,4-trichloromethyl-(become thyl-(become thyl-(becom methyl-(3 '-(4'-dimethoxyphenyl)-6-triazine, 3-{4-[2,4-bis(trichloromethyl)-s-triazine-6-yl]phenylthio}propanoic acid, 2,4-trichloromethyl-(4'-ethylbiphenyl)-6-triazine, or 2,4-trichloromethyl-(4'-methylbiphenyl)-6-triazine; a biimidazolebased compound such as 2,2'-bis(2-chlorophenyl)-4,4',5,5'-tetraphenyl biimidazole or 2,2'-bis(2,3-dichlorophenyl) nyl)-4,4',5,5'-tetraphenyl biimidazole; an acetophenone-based compound such as 2-hydroxy-2-methyl-1-phenylpropan-1-one, 1-(4-isopropylphenyl)-2-hydroxy-2-methylpropan-1-one, 4-(2-hydroxyethoxy)-phenyl(2-hydroxy)propyl ketone, 1-hydroxcyclohexyl phenyl ketone, 2,2-dimethoxy-2-phenyl acetophenone, 2-methyl-(4-methylthiophen-2-yl)-2morpholino-1-propan-1-one (Irgacure-907), or 2-benzyl-2-dimethylamino-1-(4-morpholinophenyl)-butan-1-one (Irgacure-369); an O-acyloxime-based compound such as Irgacure OXE 01, Irgacure OXE 02 from Ciba Geigy Co; 4,4'bis(dimethylamino)benzophenone or 4,4'-bis(diethylamino)benzophenone; the thioxanthone-based compound such as 2,4-diethyl thioxanthone, 2-chloro thioxanthone, isopropyl thioxanthone or diisopropyl thioxanthone; the phosphine oxidebased compound such as 2,4,6-trimethylbenzoyl diphenylphosphine oxide, bis(2,6-dimethoxybenzoyl)-2,4,4-trimethylpentyl phosphine oxide or bis(2,6-dichlorobenzoyl) propyl phosphine oxide; the coumarin-based compound such as 3,3'carbonylvinyl-7-(dimethylamino)coumarin, 3-(2-benzothiazolyl)-7-(dimethylamino)coumarin, 3-benzoyl-7-(dimethylamino)coumarin, 3-benzoyl-7-(dimethylamino)coumar no)coumarin, 3-benzoyl-7-methoxy-coumarin or 10,10'-carbonylbis[1,1,7,7-tetramethyl-2,3,6,7-tetrahydro-1H,5H,11H-CI]-benzopyrano[6,7,8-ij]-quinolizin-11-one may be used alone or in combination with two or more thereof, but the present invention is not limited thereto.

[0113] Specifically, the photoinitiator may be 2-hydroxy-2-methylpropiophenone.

**[0114]** In various embodiments, the weight ratio of the oligomer including the monomer represented by Chemical Formula 1 to the compound including at least two acrylate functional groups may satisfy a ratio of 40:30 to 75: 10, specifically 50:50 to 65:5.

**[0115]** The CTE and the dielectric constant of the substrate including the above-described ranges are appropriate and may have a resolution in units of um according to the 3D printing process.

**[0116]** In this case, the cured product of the first composition may have a dielectric constant of 2.5 to 3.0, a coefficient of thermal expansion (CTE) of 10 ppm K-1 or more and 20 ppm K-1, and may have a resolution in units of um according to the 3D printing process.

**[0117]** Hereinafter, a preparation example in which a photosensitive polyimide photocurable resin is prepared by curing a first composition is described.

50 preparation example>

10

20

30

1) Preparation of an oligomer including a monomer represented by Chemical Formula 1.

[0118] To 4 g of 2,2'-bis(3-amino-4-hydroxyphenyl) hexafluoropropane dissolved in 25 mL of methylpyrrolidone, 4.041 g of 2,2'-bis(3,4-dicarboxy-phenyl) hexafluoropropane dianhydride was added gradually at 0° C under an argon atmosphere.

**[0119]** The mixture was stirred at 0° C for 6 hours, and 0.357 g of maleic anhydride was added thereto, and the mixture was further stirred for 1 hour to obtain a pale brown solution.

**[0120]** The temperature was raised to 60° C for 2 hours, and then again raised to 110° C for 2 hours, and finally raised to 205° C for 4 hours to form a polyimide oligomer.

**[0121]** After cooling to 30° C., 3.093 g of glycidyl methacrylate, 30 mg of triethylamine, 50 mg of tetraethylammonium bromide, and 50 mg of hydroquinone were added to the obtained solution, and the mixture was stirred at 100° C for 4 hours.

**[0122]** After cooling to room temperature, the solution was poured into 100 mL of distilled water to precipitate. The precipitated powder was filtered, and dried in a vacuum state at 40° C for 12 hours or more to obtain an oligomer including a monomer represented by Chemical Formula 1.

2) preparation of a photocurable resin according to curing

10

15

20

30

35

40

55

[0123] The oligomer containing the monomer represented by Chemical Formula 1 prepared above, trimethylolpropane triacrylate, and methylpyrrolidone were mixed at a weight ratio of 60:10:30, and then 2-hydroxy-2-methylpropiophenone was added at a weight ratio of 2 of the mixture.

[0124] Here, the weight ratio of monomer A and monomer B may be 50:50 to 65:5.

3.1.1.2 Second composition or a cured product thereof.

**[0125]** According to various embodiments, a material for a substrate for electrical connection between electronic components is provided, further comprising a second composition comprising an oligomer comprising a monomer represented by the following Chemical Formula 2; a compound comprising at least two acrylate functional groups; and a photoinitiator; or a cured product thereof.

# [Chemical Formula 2]

$$\left\{\left\{\begin{matrix} s_{i} \\ s_{i} \end{matrix}\right\}_{n2}^{S_{i}} \right\}_{n4}^{N} \right\}_{n4}^{N} \left\{\left\{\begin{matrix} s_{i} \\ s_{i} \end{matrix}\right\}_{n4}^{N} \left\{\left\{\begin{matrix} s_{i} \\ s_{i} \end{matrix}\right\}_{n4}^{N} \right\}_{n4}^{N} \left\{\left\{\begin{matrix} s_{i} \\ s_{i} \end{matrix}\right\}_{n4}^{N} \left\{\begin{matrix} s_{i} \\ s_{i} \end{matrix}\right\}_{n4}^{N} \left\{\begin{matrix}$$

<sup>45</sup> **[0126]** In various embodiments, the oligomer including the monomer represented by Chemical Formula 2 may be the following structural formula.

[0127] In the structural formula, the definitions of n2 to n4 are the same as those in Chemical Formula 2.

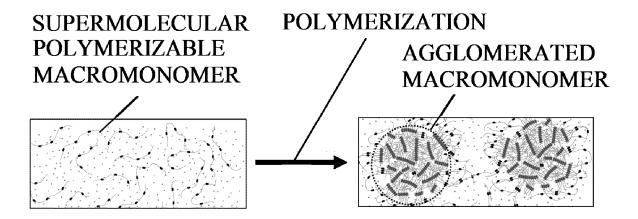

**[0128]** When the second composition of the present application is cured, the cured product may be a POSS photocurable resin including a supermolecular polymerizable crosslinking agent.

**[0129]** In the case of the substrate according to the present application, the substrate may include the second composition together with the aforementioned first composition.

[0130] In this case, as can be seen from FIG. 10C, supermolecular polymerization occurs between the 4,4'-methylene

diphenyl diurea functional group included in the monomer represented by Chemical Formula 2, thereby allowing the methacrylate functional group located at the end of the monomer represented by Chemical Formula 2 to be aggregated at a high density.

[0131] Due to the effect of the aggregated methacrylate functional group, the photocurable resin including Chemical Formula 2 may be 3D printed at a high resolution, and accordingly, achieves a very high resolution (10 μm or less) required in semiconductor packaging.

**[0132]** In addition, due to the effect of the aggregated methacrylate functional group, the network between the monomers of Chemical Formula 2 after photosensitization is induced to have a dense structure, thereby having a low CTE and a low dielectric loss.

**[0133]** In various embodiments, the compound including at least two acrylate functional groups may be POSS acrylate and may be expressed by the following structural formula.

**[0134]** As described above, the second composition may include POSS acrylate and, when the second composition includes POSS acrylate, the second composition may include a silica (SiO2) component known to have a low dielectric constant and a low CTE, thereby allowing the second composition to have a desired dielectric constant value and a CTE value.

**[0135]** The photoinitiator included in the second composition may be applied as the description of the photoinitiator included in the first composition described above.

**[0136]** In various embodiments, the weight ratio of the oligomer including the monomer represented by Formula 2 to the compound including at least two acrylate functional groups may be 60:40 to 60:40, and specifically, 50:50 to 60:40.

**[0137]** In various embodiments, the cured product of the second composition may have a dielectric constant of 3.3 to 3.6, a coefficient of thermal expansion (CTE) of 5 ppm K-1 to 10 ppm K-1, and a resolution of um according to a 3D printing process.

**[0138]** In various embodiments, the substrate material may include the cured product of the first composition (photosensitive polyimide photocurable resin) and the cured product of the second composition (POSS photocurable resin including a supermolecular polymerizable crosslinking agent) simultaneously, and in this case, the weight ratio of the two cured products may be 60:40 to 60:40.

**[0139]** Hereinafter, a preparation example in which a photosensitive polyimide photocurable resin is prepared by curing a second composition is described.

cpreparation example>

10

15

20

25

30

35

40

50

1) Preparation of an oligomer including a monomer represented by Chemical Formula 2

[0140] To a flask containing 10 g of aminopropyl-terminated polydimethylsiloxane, 50 mL of chloroform was added, and 0.7 mL of triethylamine was added.

**[0141]** 0.375 g of 4,4'-methylene diphenyl diisocyanate was dissolved in 15 mL of chloroform, and the solution was dropped into a flask by one drop at room temperature over 90 minutes, so that 4,4'-methylene diphenyl diurea functional

group was formed between the polydimethylsiloxane polymers.

[0142] At this time, the reaction was carried out under an argon atmosphere without moisture.

**[0143]** Next, 1.1 mL of methacryloyloxyethyl isocyanate was added to the reaction solution, and then the reaction was carried out at room temperature for 2 hours to bind to both ends of the monomers.

**[0144]** Next, 500 mL of methanol was added to the finished solution, and a suspension solution was discarded, and the precipitated solid material was dried at room temperature, thereby obtaining an oligomer including the monomer of Formula 2.

## 2) preparation of photocurable resin

10

20

30

35

45

50

**[0145]** The oligomer including the monomer of Chemical Formula 2 and the POSS acrylate compound were mixed at a weight ratio of 10:90 and then 2-hydroxy-2-methylpropiophenone was added as much as 2 weight ratio of the mixture. **[0146]** At this time, tetrahydrofuran may be added at a weight ratio of 0 or more and less than 50 weight ratio of the mixture to control the viscosity of the photocurable resin.

**[0147]** As characteristics for the semiconductor packaging, the material may have characteristics (or characteristics capable of curing) capable of performing a process in units of  $\mu$ m based on the semiconductor packaging. In other words, the material may have a resolution in units of  $\mu$ m. The unit of  $\mu$ m may include a range of 2  $\mu$ m or more and 25  $\mu$ m or less, and may preferably be 2  $\mu$ m, 10  $\mu$ m, and 25  $\mu$ m. Accordingly, the material may be formed in units of  $\mu$ m having a width of a through structure formed in the substrate 911, and a width of an interconnect (or a metal line) formed by a metallization process may be formed in units of  $\mu$ m, thereby providing an optimal electrical connection between electronic components (e.g., chips).

**[0148]** Meanwhile, the material is not limited to the described example, and as characteristics for the semiconductor packaging, the material may be implemented to have characteristics capable of performing a process in units of nm. In other words, the material may have a resolution in units of nm.

**[0149]** For example, as characteristics for the semiconductor packaging, the material may have dielectric constant characteristics as shown in Table 1 below depending on a type of an electronic product (e.g., a substrate) provided (or physically connected) with the substrate 911 after being cured based on a 3D printing process, but is not limited to the described example, and may be implemented to have dielectric constants exceeding the described range depending on the type of the product.

## <Table 1>

| Type of Substrate                                | Dielectric constant                                                                                               |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Normal substrate (or chip-let package substrate) | In the range of 2.4 GHz to 3.6 GHz, less than or equal to 3.9, or preferably, less than or equal to 3.3 in 3 GHz. |

| Substrate for antenna having coaxial structure   | In the range of 2.4 GHz to 3.6 GHz, 4.9 or less, or preferably 3.9 or less in the range of 3 GHz.                 |

40 [0150] Accordingly, the loss rate of the electrical connection signal through the interconnect may be reduced. In addition, for example, as a characteristic for the semiconductor packaging, the material may be implemented to have a loss tangent of 0.01 or less after being cured based on the 3D printing process, but is not limited to the described example, and may be implemented to have a loss tangent that exceeds the range described according to the type of product, such as the dielectric constant described above.

[0151] In addition, for example, as a characteristic for the semiconductor packaging, the material may be implemented to have a roughness of  $0.7~\mu m$  or less, or preferably  $0.5~\mu m$  or less after being cured based on the 3D printing process, but is not limited to the described example, and may be implemented to have a roughness that exceeds the range described according to the type of product described above. Accordingly, the roughness of the inner surface of the through structure (e.g., hole) formed inside the substrate 911 may be implemented to be  $0.7~\mu m$  or less, or preferably  $0.5~\mu m$  or less, as described above. As the roughness of the inner surface of the through structure is implemented to the above range, the growth of metal based on the metallization process may be smoothed, and electrical connectivity may be improved. In addition, for example, as a characteristic for the semiconductor packaging, the thermal expansion coefficient may be 41 ppm/°C or less, or preferably 35 ppm/°C or less, but is not limited to the described example, and may be implemented to have a thermal expansion coefficient that exceeds the range described according to the type of product. As the substrate 911 is implemented to have the thermal expansion coefficient in the above range, even if heat is applied to the electronic products provided with the substrate 911, the strain rate due to heat may be limited, and physical connection quality with other electronic products (e.g., substrates and chips) physically connected to the substrate 911 may be improved.

[0152] According to various embodiments, the material may be implemented to include at least one monomer, as

illustrated in FIG. 10B. The at least one monomer may be implemented to have a characteristic of being cured based on the above 3DP methods. Meanwhile, the material may be a material such as glass, ceramic, or plastic, but is not limited to the illustrated and/or described example.

[0153] According to various embodiments, the packaging device 20 (e.g., the 3D printing device 610) may perform 3D printing process in operation 1003, and generate a substrate having at least one internal structure (e.g., a through structure) in operation 1005. For example, the 3D printing may include light curing and thermal curing. Preferably, the 3D printing may be performed based on UV. In this case, after forming the substrate based on UV having a first intensity, a processing process for removing a material remaining on the substrate based on UV having a second intensity higher than the first intensity may be continuously performed. For example, when the 3D printing method is the PuSL method, the packaging device 20 (e.g., the 3D printing device 610) may cure the material in a layer unit with precision at the CNC level, and generate the substrate 911 (or a dielectric layer) having at least one through structure as a result of the process.

**[0154]** According to various embodiments, the unit of the width of the at least one internal structure (e.g., the through structure) may be in  $\mu$ m.

**[0155]** According to various embodiments, the aspect ratio of the at least one internal structure (e.g., the through structure) may be 10 or more, but is not limited to the described example.